Изобретение относится к вычис71Ительной технике и может применяться в цифровых устройствс1Х в качестве модуля для построения узла умножения и деления произвольной разрядности, причем для построения N-разрядного узла, где N m-n (п - разрядность модуля; m - натуральное число), требуется m таких модулей без использования дополнительного обррудования. , Изобретение может быть реашизовано в любом исполнении, включая исполнение в виде отдельной большой интегральной схемы (БИС). В устройстве используются :интерационные сшго.-. ритмы умножения на два разряда и ;Деления без восстановления остатка с получением на каждом шаге одного разряда частного.

Известно устройство, реализованное в виде БИС и содержащее матрицу сумматоров, на вход которой по двум независимым магистралям подгиотся множимое и множитель, а результат снимается с ее выхода на третью магистраль 1 .

Однако данная .схема -не выполняет операцию деления, а для построения N-разрядного узла умножаниЛ требуется в зависимости от способа реализации

по т таких БИС, а также дополнительное оборудование для формирования окончательного результата по произведениям, вычисленным в каждой БИС; Применение такой БИС в небольших устройствах, например в микро-ЭВМ, где необходимо иметь универсальный : набор операций при небольшом объеме оборудования, неэффективно.

10

На1Иболее близким к предлагаемо у fio технической сущности является устройство, содержащее блок приема и выдачи, блок суммирования, регистр,

15 мультиплексор и блок управления, причем первый информационный вход , блока приема и выдачи соединен с инФоЕ 1ационной шиной первого операнда, первый информационный выход регистра

20 соединен с первым информационным входом мультиплексора, выход которо го соединен с первым информационньм входом блока суммирования, первый выход которого соединен с первым вхо25дом блока управления, первый и второй выходы которого соединены соответственно с первым и вторим управляющими входами блока приема и выдачи, третий, четвертый и пятый вы30ходы блока управления соединены соответственно с первым, вторым и третьим управляющими входамимультиплексора, шестой -и седьмой выходы блока управления соединены соответственно о первым и вторьлм управляющими входами блока суммирования. Нелостатки известного ,устройства одномагистральность структуры, вслед ствие чего исходные операнды загружаются в устройство по очереди, что в конечном счете увеличивает общее время выполнения операций; получение по п-разрядным операндам только п старших разрядов произведения или п разрядов частного, что вообще недопустимо при выполнении- операций целЕлх .числах и весьма ограничива:ет вычислительные возможности устройства в режимах работы с фиксированной или плавающей запятой, организации вычислений с двойной точностью и т.д.; отсутствие свойства модульности, Т.е. при заданной разрядности устройства нельзя простым соединением нескольких таких устройств без дополнительного оборудования получить устройства большей разрядности Цель изобретения - повышение быст родействия и .расширение функциональных возможностей за счет выполнения операций над целыми числами и числами с плавающей запятой и обеспечения свойства модульности. Поставленная цель достигается тем что в устройство введены два элемента И и коммутатор, причем второй информационный вход блока приема и выдачи соединен с информационной шиной (п-Г)-го старшего разряда первого операнда устройства, третий информационный вход блока- приема и выдачи соединен с информационной шиной нулевого разряда первого операнда устройства, вторым входом блока управления и выходом первого элемента И, информационный вход регистра соединен с информационной-шиной второго операнда устройства и первым выходом блока суммирования, третий выход которого является .выходом переноса из {п-1)-го cTapiuero разряда устройства а четвертый выход - выходом двух младших разрядов устройства, третий вход блока управления соединён с информационной шиной страшего разряда очередной пары разрядов первого операнда устройства и выходом второго элемента И, первый и второй выходы блока приема и выдачи соединен соответственно с первыми входами первого и второго элементов И, вторые входы которых, объединены и подключены к восьмому выходу блока управления, второй выход регистра сое динен с первым входом коммутатора, второй вход которого соединен с чет вертым входом блока управления и является входом управления коммута;аией устройства, а третий вход - с первым управляющим входом мультиплексора, второй информационный вход которого является входом нулевого разряда второго операнда устройства, пятый, шестой и седьмой входы блока управления соединены соответственно с шинами запуска, завершения операции и счета устройства, восьмой вход блока управления является входом синхронизации устройства, девятой вход блока управления соединен с тре.тьим управляющим входом блока суммирования и третьим управляющим входом блока приема и вьщачи и является входом сброса устройства,четвертый вход блока приема и выдачи является входом (п-2)-го старшего разряда первого операнда устройства, второй информационный вход блока суммирования соединен с информационной шиной двух младших разрядов устройства, третий информационный вход блока суммирования соединен с информационной шиной {11-1)-го старшего разряда второго операнда устройства, четвертый и пятый информационные входы блока суммирования являются соответственно входами .(п-2)-го старшего разряда второго операнда и переноса в младший разряд устройства, выход коммутатора является выходом переноса из (п-1)-го старшего разряда устройства. В устройстве блок управления содержит узел формирования признака активности, дешифратор, узел выработки управляющих сигналов, счетчик, триггер, элемент НЕ, восемь элементов И, два элемента ИЛИ,, причем первый вход узла формировани-я признака активнос тисоединен с первыми входами узла выработки управляющих сигналов, первого, второго, третьего и четвертого элементов И и первым выходом дешифратора, второй выход которого соединен с первыми входами пятого, шестого и седьмого элементов И, вторыми входами узла выработки управляющих сигналов и узла формирования признака активности и является шестым вьлходом блока управления, выход узла формирования признака активности соединен с управляющим входЪм счетчика, вторыми входами первого и седьмого элементов И и является восьмым выходом блока управления, выходы первого и седьмого элементов И являются соответственно первым и вторьзм выходами блока управления, третий вход узла формирования признака активности соединен со входом элемента НЕ, вторыми входами третьего, че.тверТого, пятого элементов И и первым входом восьмого элемента И и является четвертым входом блока управления, четвертый вход узла формирова- i

ния признака активнрсти соединен со счетным входом счетчика и третьим входомузлавыработки управляющих сигналов и является ВОСЬМЕЛМ входом (блока управления, пятый вход узла .формирования признака активности соединен с прямым выходом триггера и третьим входом третьего элемента шестой вход узла формирования признака активности является девятым вхдом блока управления и соединен с иформационным входом триггера, входом сброса счетчика, входом дешифратора и четвертым входом узла выработки управляющих сигналов, пятый вход которого является шестым входо блока управления, а шестой вkoд соединен с выходом восьмого элемента И и является вторым входом блока управления , седьмой вход узла выработки управляющих сигналов является третьим входом блока управления, первый, второй, третий ,и четвертый выходы узла выработки управляющих сигналов являются соответственно третьим, четвертым, пятым и седьмым выходами блока управления, выход старшего разряда счетчика соединен со входом сброса триггера, выход (k-2)-ro разряда счетчика соединен с седьмьом входом узла формирования признака активности, вторым входом второго элемента И и третьим входом четвертого элемента И, выход (k-l)разряда счетчика соединен со вторым входом шестого элемента И и восьмым входом узла формирования признака активности, девятый вход которого является пятым входом блока управления и соединен с выходом шестого элемента И, выход элемента НЕ соединен с третьим входом второго элемента И, выход которого соединен с первым входом элемента ИЛИ, второй вход которого соединен с выходом третьего элемента И, а выход - с третьим входом пятого элемента И и десятым входом узла формирования признака активности, и является седьмым входом блока управления, выход четвертого .элемента И соединён, с первым входом второго элемента И, второй вход которого соединен с выходом пятого элемента И, а выход с пятым входом узла выработки управляющих сигналов.

Узел формирования признака активности содержит элемент НЕ, два элемента ИЛИ, триггер и пять элементов И, причем первые входы пяти элементов И объединены и являются четвертым входом узла формирования признака активности, вторые входы первого и второго элементов И объединены и являются первым входом узла формирования признака активности, третий вход первого элемента И является девятым входом узла

формирования признака активности, вход элемента НЕ соединен со вторым входом третьего элемента И и является третьим входом узла формирования признака активности, а выход со вторым входом четвертого элемента И, выход которого соединен с первым входом первого элемента И, второй и третий входы которого соединены соответственно с выходами

0 первого и третьего элементов И, а ;выход - с информационным входом триггера, вход сброса которого соединен с выходом второго элемента ИЛИ, первый и второй входы которого сое5динены соответственно с выходами пятого и второго элементов И, третий вход второго элемента ИЛИ является шестым входом узла формирования признака активности, второй вход пятого элемента И является седьмым входом

0 узла формирования признака активности, третьи входы третьего, .четвертого и пятого элементов И объединены и являются вторым входом узла формирования Признака активности, чет5вертый вход третьего элемента И является пятым входом узла формирования признака активности, третий вход второго элемента И является,восьмым входом узла формирования признака

0 активности, четвертый вход четверто- го элемента И является десятым входом узла формирования признака активности, единичный выход триггера явл-яется выходом узла формирования

5 признака активности.

Узел выработки управляющих сигнаjiOB содержит два элемента НЕ, три триггера, четыре элемента ИЛИ и тринадцать элетлентов. И, причем вход

0 первого элемент НЕ соединен с пер.выми входами первого, второго, третьего, четвертого и пятого элементов И и информационным входом .первого триггера и является шестым

5 входом узла выработки управляющих сигналов, первые входы шестого, седьмого, восьмого, девятого и десятого элементов И объединены и соединены со входами третьего, четвертого и пятого элементов И и

0 являются первым входом узла выработки -управляющих сигналов, первые входы одиннадцатого, двенадцатого |И. тринадцатого элементов И объединеныи являются вторым входом узла

5 выработки управляклцих сигналов, входы синхронизации первого и второго триггеров объединены и являются третьим входом узла выработки управляющих сигналов , входы сброса перво0го, второго и третьего триггеров объединены и являются девятым входом узла выработки управляющих сиг-налов, информационный вход второго триггера соединен с выходом первого

5 элемента. ИЛИ, первый и второй входы

которого соединены соответственно с выходами первого и второго элемен .тон И, второй вход первого элемента И соединен с прямым выходом второго триггера, вторыми входами седьмого, девятого и десятого элемента И и третьим входом четвертого элемента четвертый вход которого соединен с третьими входами седьмого и пятого элементов И, выходом второго элемента НЕ, вход которого соединен со .вторым входом второго элемента И и является седьмым входом узла выработки управляющих сигналов, информационный вход третьего триггера является пятым входом узла выработк управляющих сигналов, прямой выход первого триггера соединен со вторым входами восьмого и одиннадцатого элментов И, инверсный выход первого триггера соединен-со вторым входом двенадцатого и третьим входом девятого элементов И, прямой выход третего триггера соединен с третьим входом восьмого и четвертым входом девятого элементов И, инверсный выход третьего триггера соединен со вторыми входами шестого и двенадцатого элементов И, третьими входами третьего, десятого и одиннадцатого элементов И четвертыми входами пятого и седьмого элементов И и пятым входом четвертого элемента И, четвертый вход третьего элемента И соединен с третьим входом шестого, четвертым входом десятого элементов И и входом второго элемента НЕ, пятый вход третьего элемен та И соединен с инверсным выходом второго триггера, четвертыми входами пятого,, шестого и восьмого элементов И, выход первого элемента НЕ соединен с пятыми входами шестого, седьмого и десятого элементов И, выходы одиннадцатого, третьего и четвертого элементов И соединены соответственно с первым, вторым и третьим входами первого элемента ИЛИ, выход которого является первым ВЕЖОДОМ узла выработки управляквдих сигналов выходы шестого, седьмого, восьмого, де:вятого и двенадцатого элементов И соединены соответственно с первым, вторым, третьим, четвертым и пятым входами второго элемента ИЛИ, выход которого является вторьм выходом узла выработки управляющих сигналов , выходы пятого и десятого элементов И соединены соответственно с первым и вторьм входами третьего элемента ИЛИ, выход которого является третьим выходом узла выработки управляющих сигналов, выход тринадцатого элемента И является четвертым выходом узла выработки управляющих сигналов.

Блок суммирования содержит сумматор, регистр, два элемента И,

1.руппу элементов И, причем входы суммирования сумматора являются соответственно первыми входами блока суммирования, вход переноса младшего разряда сумматора является пятым входом блока суммирования, выходы сумматора соединены соответственно с информационными входами регистра, второй информационный вход которого является третьим входом блока суммирования и соединен с выходом первого элемента И, вход нулевого jjasряда регистра является вторым входом блока суммирования и соединен с выходом второго элемента И,

5 первый вход которого соединен с выходом нулевого разряда регистра, выход (n-l)-ro разряда которого соединен с первым входом первого элемен.та И, второй вход которого соединен

0 со входом управления сдвигом влево регистра и является вторым управляющим входом блока суммирования, второй вход второго элемента И соединен со входом управления сдвигом

5 вправо регистра и является первым управляющим входом блока суммирования, третий информационный вход регистра является четвертые входом блока суммирования, выходы регистра

соединены соответственно с первыми

входами элементов И группы и входами переноса сумматора, выход (n-l)-ro разряда которого является третьим выходом блока суммирования, выход первого младшего разряда регистра является четвертым выходом блока суммирования, выход второго младшего разряда является первым выходом блока суммирования, вторые входы элементов И группы объединены и явля0 ютея третьим управляющим входом блока суммирования, выходы элементов И группы являются вторым выходом блока суммирования.

5 Блок приена и выдачи содержит регистр и элемент И, группу элементов И, причем информационные входы регистра .являются первым входом блока приема и вьщачи и соединены соответственно

д с выходами элементов И группы, первые входы которых соединены соответственно с выходами регистра, выход {п-1)-го разряда которого соединен с первым входом элемента И, второй вход которого соединен со входом управления сдвигом вправо регистра и является первым управляющим входом блока приема и выдачи, выход элемента И соединен со входом (п-1)-го разряда регистра и является вторым

0 входом блока приема и вьщачи, вход .управления сдвигом влево регистра является вторым управлякициМ входом блока приема и выдачи вход (п-2)-го разряда регистра является четвертым

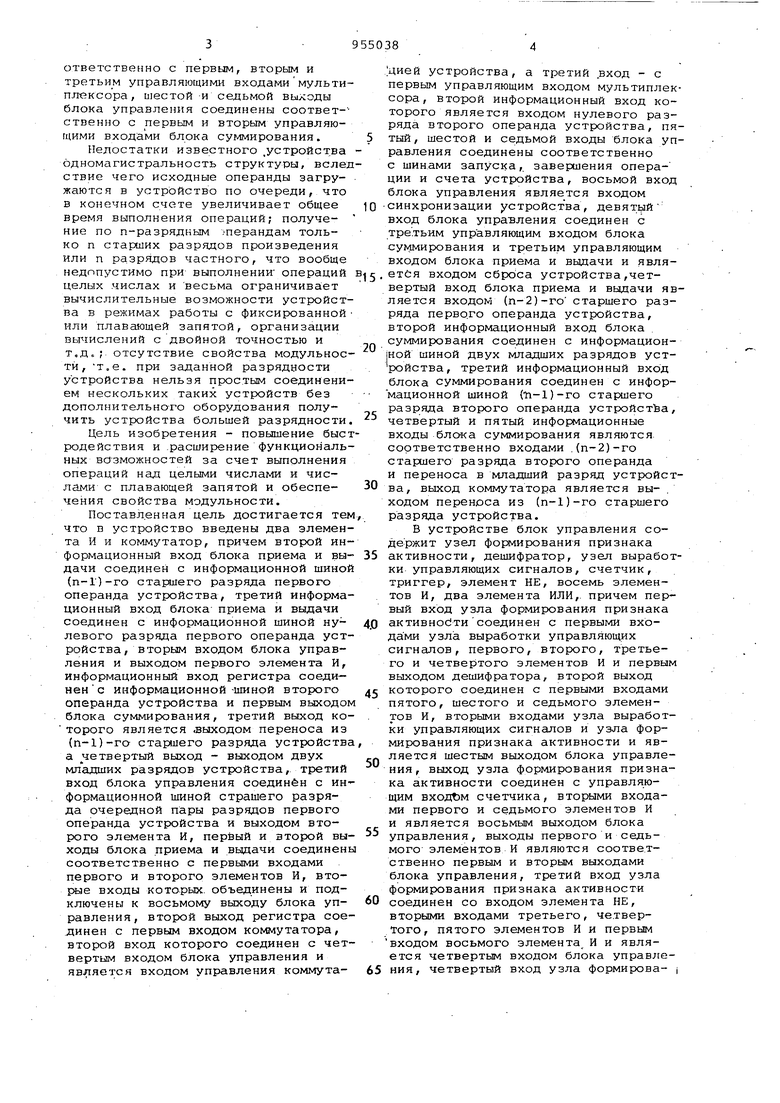

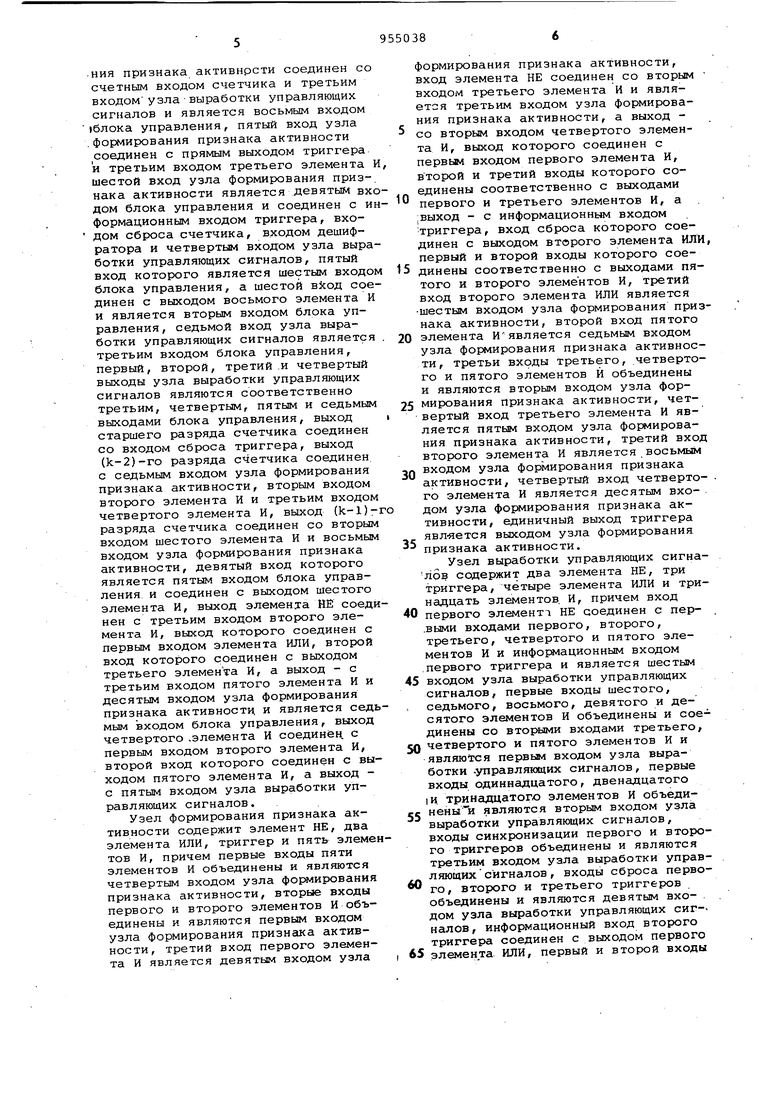

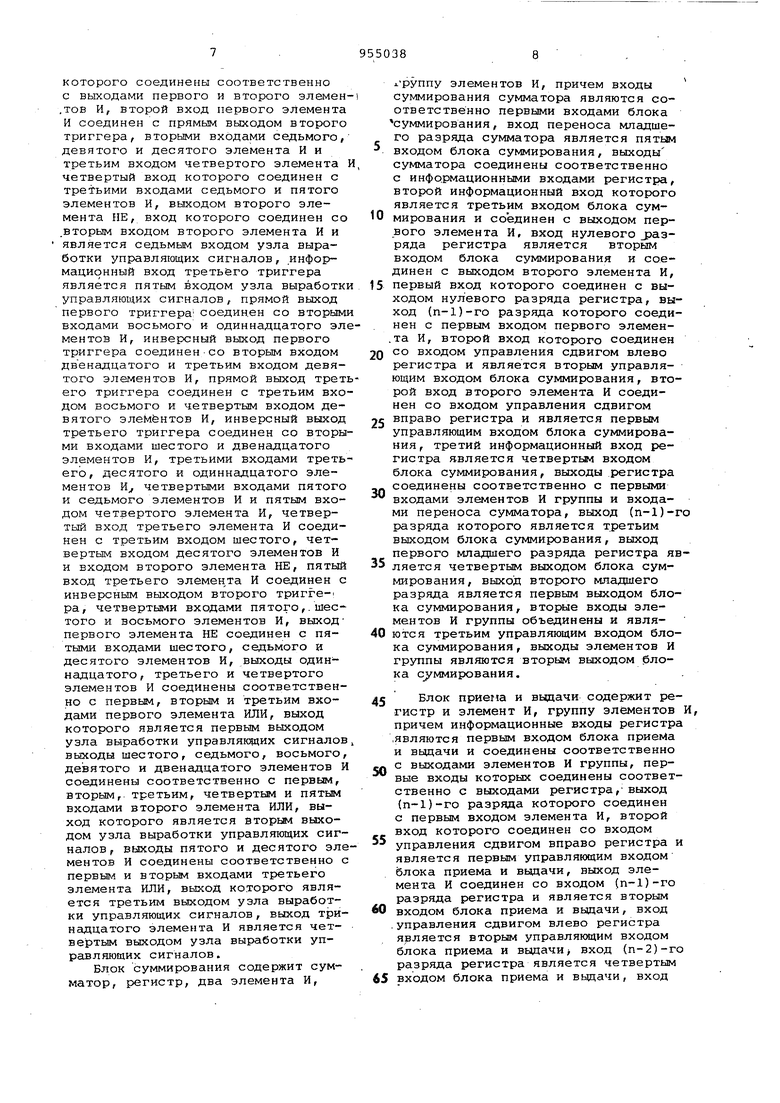

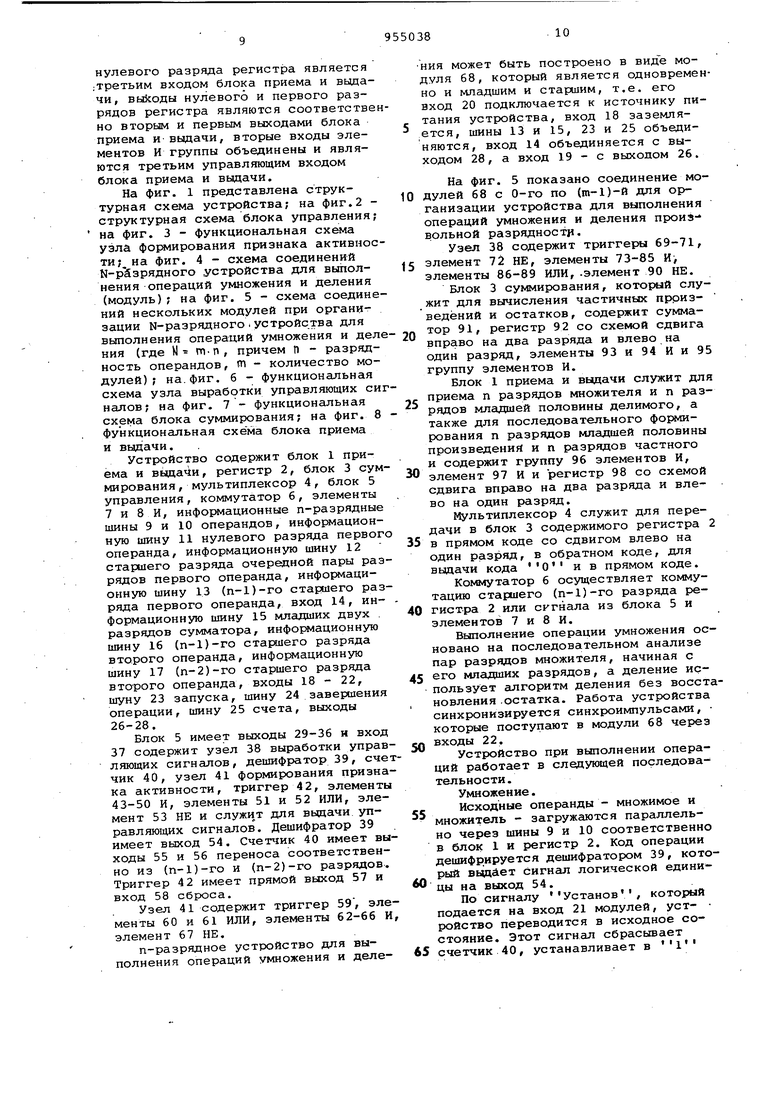

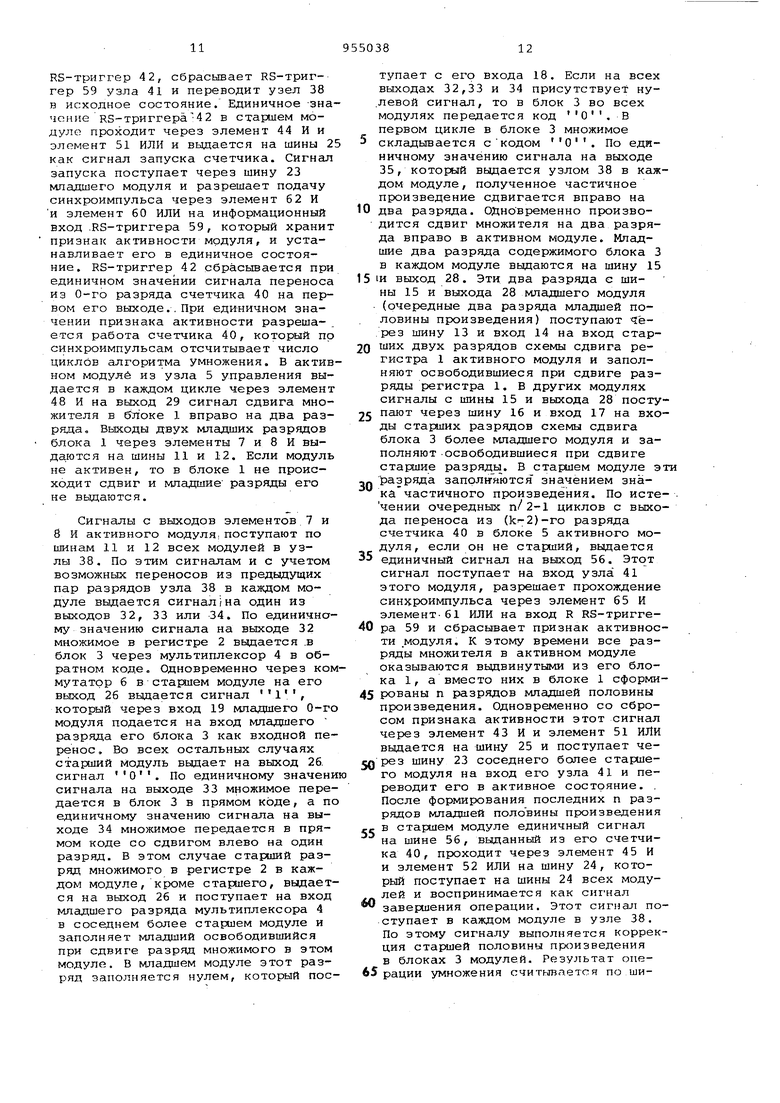

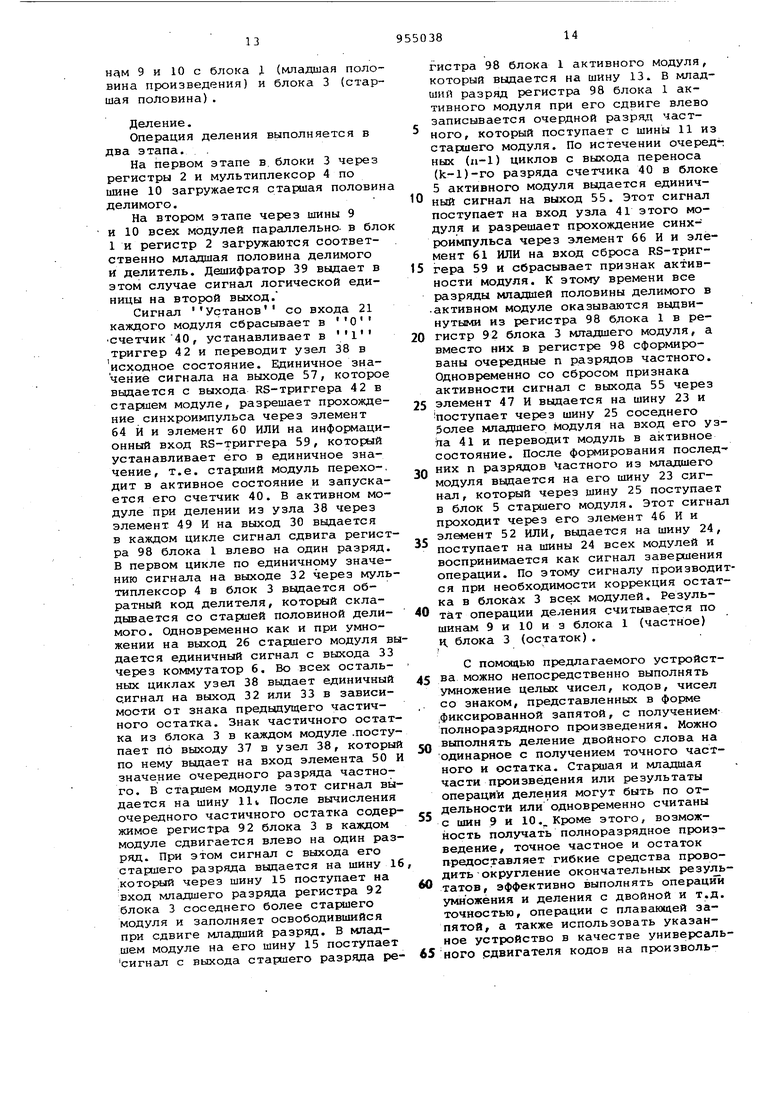

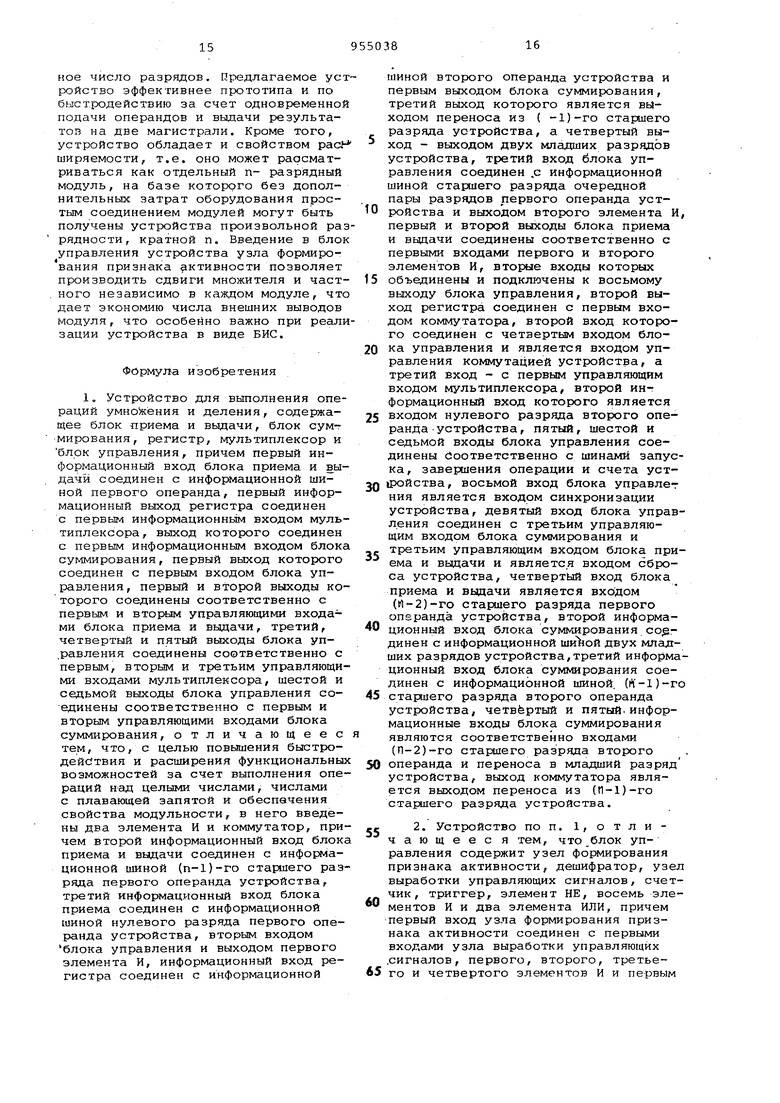

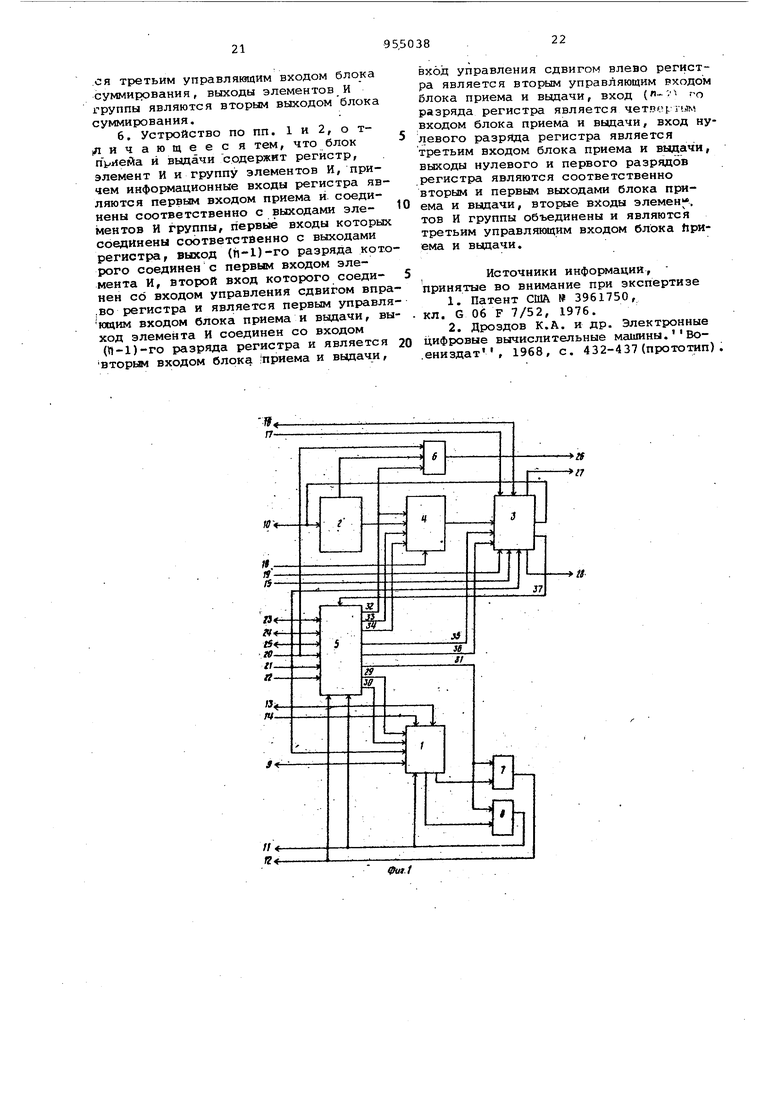

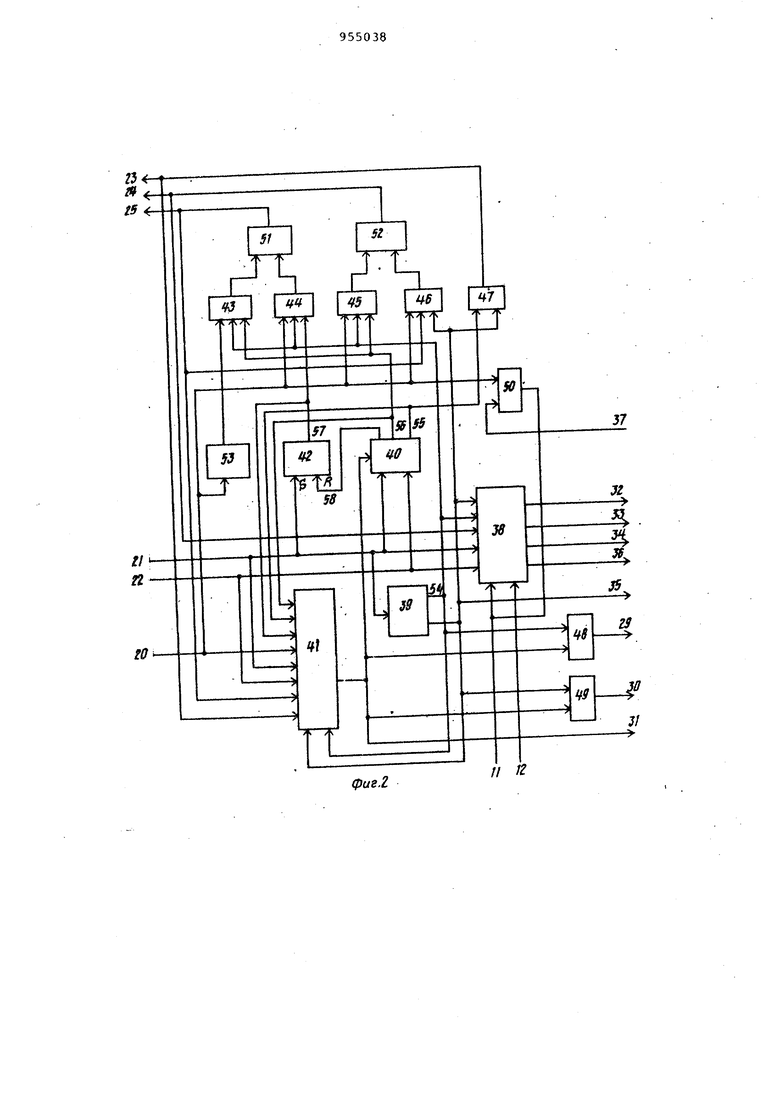

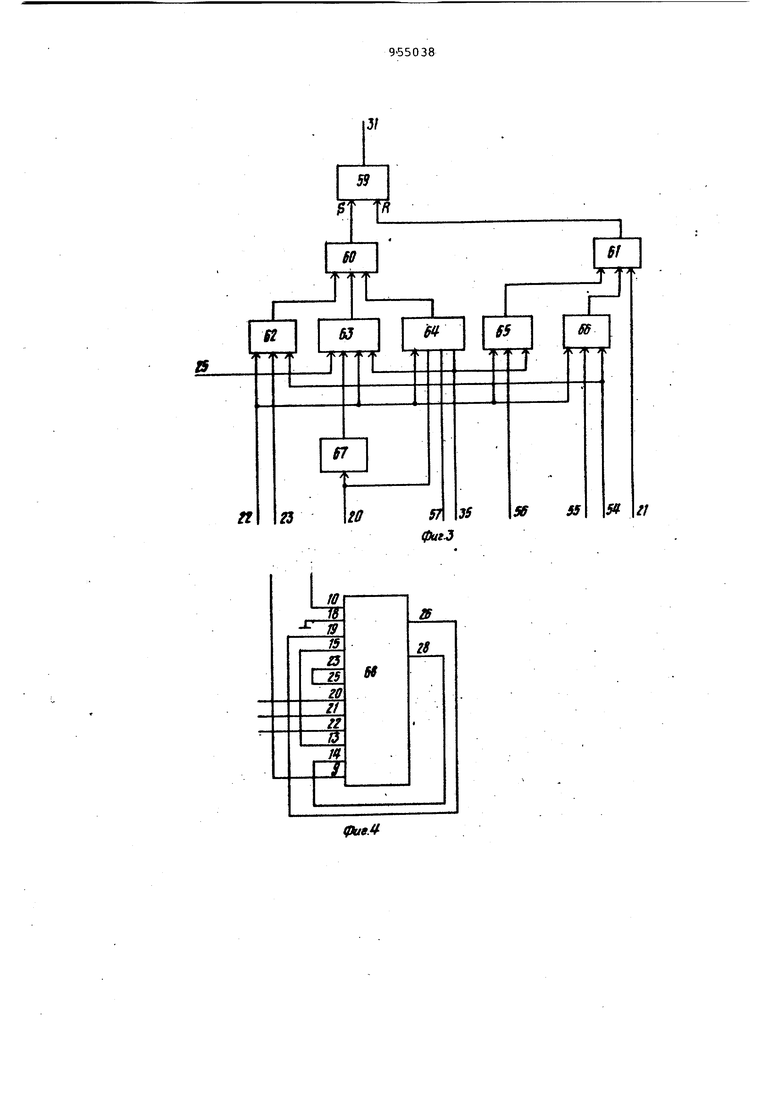

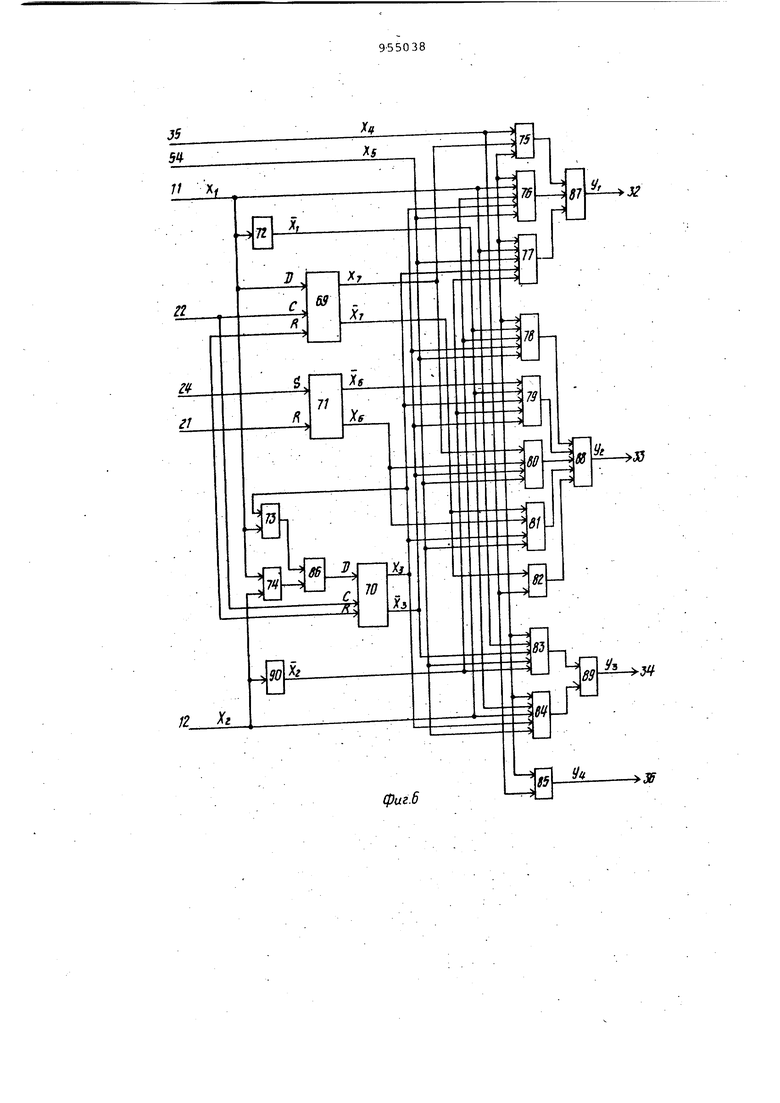

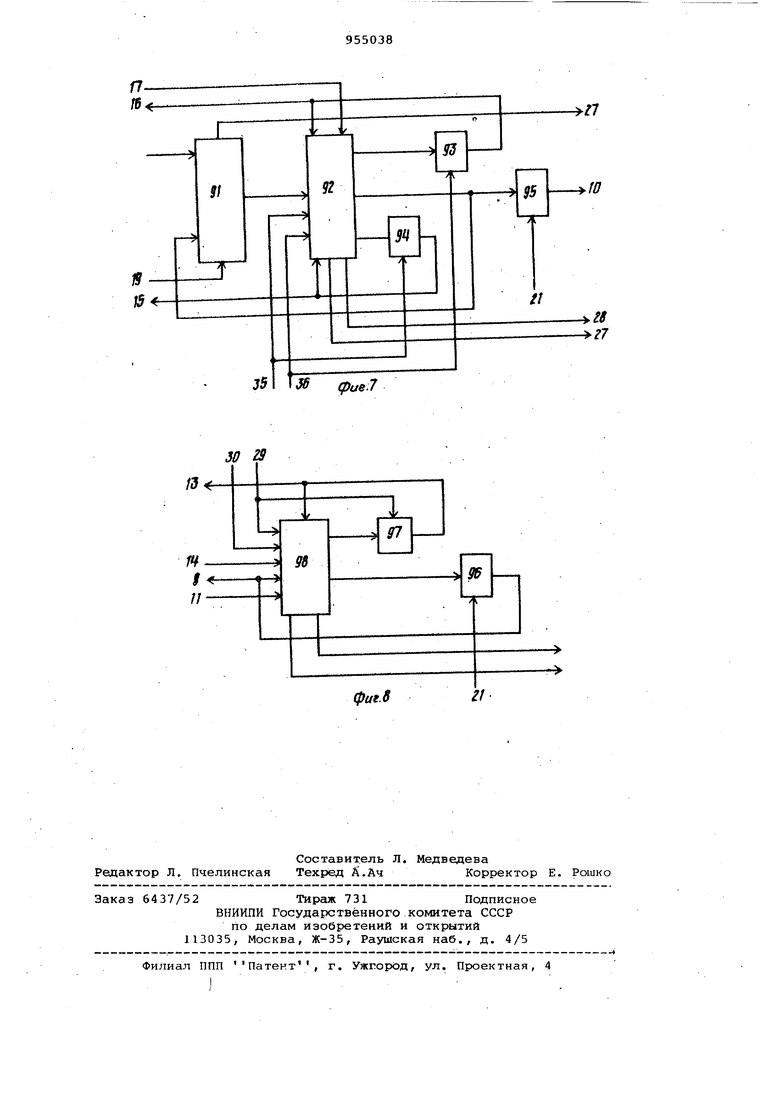

5 входом блока приема и вьщачи, вход нулевого разряда регистра является ;Третьим входом блока приема и выда чи, выkoды нулевого и первого разрядов регистра являются соответств но вторым и первым выходами блока приема и вьвдачи, вторые входы элементов И группы объединены и являются третьим управляющим входом блока приема и вьщачи. На фиг. 1 представлена структурная схема устройства; на фиг.2 структурная схема блока управления на фиг. 3 - функциональная схема узла формирования признака активно ти; на фиг. 4 - схема соединений Ы-р 5зрядного устройства для выполнения операций умножения и деления (модуль); на фиг. 5 - схема соедин ний нескольких модулей при организации N-разрядного устройства для выполнения операций умножения и де ния (где N m-n, причем И - разряд ность операндов, m - количество мо дулей) ; на.фиг. 6 - функциональная схема узла выработки управляющих с налов; на фиг. 7 - функциональная схема блока суммирования; на фиг. функциональная схема блока приема и выдачи. Устройство содержит блок 1 приема и выдачи, регистр 2, блок 3 сум мирования, мультиплексор 4, блок 5 управления, коммутатор 6, элементы 7 и 8 И, информационные п-разрядные шины 9 и 10 операндов, информационную шину 11 нулевого разряда первог операнда, информационную шину 12 старшего разряда очередной пары ра рядов первого операнда, информационную шину 13 (n-l)-ro старшего ра ряда первого операнда, вход 14, информационную шину 15 младших двух . разрядов сумматора, информационную шину 16 (n-l)-ro стариего разряда второго операнда, информационную шину 17 (п-2)-го старшего разряда второго операнда, входы 18 - 22, шуну 23 запуска, шину 24 завершения операции, шину 25 счета, выходы 26-28. Блок 5 имеет выходы 29-36 и вход 37 содержит узел 38 выработки управ ляющих сигналов, дешифратор 39, сче чик 40, узел 41 формирования призна ка активности, триггер 42, элемент 43-50 И, элементы 51 и 52 ИЛИ, элемент 53 НЕ и служат для вьщачи управляющих сигналов. Дешифратор 39 имеет выход 54. Счетчик 40 имеет вы ходы 55 и 56 переноса соответственно из (n-l)-ro и (п-2)-го разрядов. Триггер 42 имеет прямой выход 57 и вход 58 сброса. Узел 41 содержит триггер 59, эле менты 60 и 61 ИЛИ, элементы 62-66 И элемент 67 НЕ. п-разрядное устройство для выполнения операций умножения и деления может быть построено в виде модуля 68, который является одновременно и младшим и старшим, т.е. его вход 20 подключается к источнику питания устройства, вход 18 заземля,ется, шины 13 и 15, 23 и 25 объединяются, вход 14 объединяется с выходом 28, а вход 19 - с выходом 26. На фиг. 5 показано соединение модулей 68 с 0-го по (т-1)-й для организации устройства для выполнения операций умножения и деления произ- вольной разрядности. Узел 38 содержит триггеры 69-71, элемент 72 НЕ, элементы 73-85 И, элементы 86-89 ИЛИ, -элемент 90 НЕ. Блок 3 суммирования, который служит для вычисления частичных произведений и остатков, содержит сумматор 91, регистр 92 со схемой сдвига вправо на два разряда и влево на один разряд, элементы 93 и 94 И и 95 группу элементов И. Блок 1 приема и вьщачи служит для приема п разрядов множителя и п разрядов младшей половины делимого, а также для последовательного формирования п разрядов младшей половины произведения и п разрядов частного и содержит группу 96 элементов И, элемент 97 И и регистр 98 со схемой сдвига вправо на два разряда и влево на один разряд. Мультиплексор 4 служит для передачи в блок 3 содержимого регистра 2 в прямом коде со сдвигом влево на один разряд, в обратном коде, для и в прямом коде, вьдачи кода Коммутатор 6 осуществляет коммутацию старшего (п-1)-го разряда регистра 2 или сигнала из блока 5 и элементов 7 и 8 И. Вьшолнение операции умножения основано на последовательном анализе пар разрядов множителя, начиная с его младших разрядов, а деление использует алгоритм деления без восстановления .остатка. Работа устройства синхронизируется синхрюимпульсами, которые поступают в модули 68 через входы 22. Устройство при выполнении операций работает в следующей последовательности. Умножение. Исходные операнды - множимое и множитель - загружаются параллельно через шины 9 и 10 соответственно в блок 1 и регистр 2. Код операции дешифрируется дешифратором 39, который в14Дс1ет сигнал логической единицы на выход 54. По сигналу Установ , который подается на вход 21 модулей, уст- ройство переводится в исходное состояние. Этот сигнал сбрасывает счетчик 40, устанавливает в

RS-триггер 42, сбрасьшает RS-триггер 59 узла 41 и переводит узел 38 в исходное состояние. Единичное -значоние кз-триггера.42 в старшем модуле проходит через элемент 44 И и элемент 51 ИЛИ и выдается на шины 2 как сигнал запуска счетчика. Сигнал запуска поступает через шину 23 младшего модуля и разрешает подачу синхроимпульса через элемент 62 И и элемент 60 ИЛИ на информационный вход .RS-триггера 59, который хранит признак активности модуля, и устанавливает его в единичное состояние. RS-триггер 42 сбрасывается при единичном значении сигнала переноса из 0-го разряда счетчика 40 на первом его выходе..При единичном значении признака активности разреша- . ется работа счетчика 40, который по синхроимпульсам отсчитывает число циклов алгоритма умножения. В активном модуле из узла 5 управления выдается в каждом цикле через элемент 48 И на выход 29 сигнал сдвига множителя в блоке 1 вправо на два разряда. Выходы двух младших разрядов блока 1 через элементы 7 и 8 И выдаются на шины 11 и 12. Если модуль ие активен, то в блоке 1 не происходит сдвиг и младшие разряды его не выдаются.

Сигналы с выходов элементов 7 и 8 и активного модулЯ: поступают по шинам 11 и 12 всех модулей в узлы 38. По этим сигналам и с учетом возможных переносов из предыдущих пар разрядов узла 38 в каждом модуле выдается сигнал на один из выходов 32, 33 или 34. По единичному значению сигнала на выходе 32 множимое в регистре 2 вьщается .в блок 3 через мультиплексор 4 в обратном коде. Одновременно через коммутатор б в старцем модуле на его выход 26 выдается сигнал , который через вход 19 младшего 0-го модуля подается на вход младшего разряда его блока 3 как входной перенос. Во всех остальных случаях старший модуль вьщает на выход 26. сигнал О . По единичному значени сигнала на выходе 33 множимое передается в блок 3 в прямом коде, а по единичному значению сигнала на выходе 34 множимое передается в прямом коде со сдвигом влево на один разряд. В этом случае старший разряд множимого в регистре 2 в каждом модуле, кроме старшего, выдается на выход 26 и поступает на вход младшего разряда мультиплексора 4 в сосе,днем более старшем модуле и заполняет младший освободившийся при сдвиге разряд множимого в этом модуле. В млад1.аем модуле этот разряд заполняется нулем, который поступает с его входа 18. Если на всех выходах 32,33 и 34 присутствует ну.левой сигнал, то в блок 3 во всех модулях передается код О. В первом цикле в блоке 3 множимое

складьшается скодом . По единичному значению сигнала на выходе 35, который выдается узлом 38 в каждом модуле, полученное частичное произведение сдвигается вправо на

0 два разряда. ОДновременно производится сдвиг множителя на два разряда вправо в активном модуле. Младшие два разряда содержимого блока 3 в каждом модуле выдаются на шину 15

5 1и выход 28. Эти два разряда с шины 15 и выхода 28 младшего модуля (очередные два разряда младшей половины произведения) поступают через шину 13 и вход 14 на вход старших двух разрядов схемы сдвига регистра 1 активного модуля и заполняют освободившиеся при сдвиге разряды регистра 1. В других модулях сигналы с шины 15 и выхода 28 поступают через шину 16 и вход 17 на входы старших разрядов схемы сдвига блока 3 более младшего модуля и заполняют -освободившиеся при сдвиге старшие разряды. В старшем модуле эти

разряда заполняются значением знака частичного произведения. По истечении очередных n/2-l циклов с выхода переноса из (k-2)-ro разряда счетчика 40 в блоке 5 активного модуля, если он не старший, выдается

5 единичный сигнал на выход 56. Этот сигнал поступает на вход узла 41 этого модуля, разрешает прохождение синхроимпульса через элемент 65 И элемент-61 ИЛИ на вход Н RS-тригге0 ра 59 и сбрасывает признак активности модуля. К этому времени все разряды множителя в активном модуле оказываются выдвинутыми из его блока 1 , а вместо них в блоке 1 сформированы п разрядов младшей половины произведения. Одновременно со сбросом признака активности этот сигнал через элемент 43 И и элемент 51 ИЛИ выдается на шину 25 и поступает чея рез шину 23 соседнего более старшего модуля на вход его узла 41 и переводит его в активное состояние. . После формирования последних п разрядов младшей половины произведения в старшем модуле единичный сигнал на шине 56, вьвданный из его счетчика 40, проходит через элемент 45 И и элемент 52 ИЛИ на шину 24, который поступает на шины 24 всех модулей и воспринимается как сигнал

завершения операции. Этот сигнал поступает в каждом модуле в узле 38. По этому сигналу выполняется коррекция старшей половины произведения в блоках 3 модулей. Результат операции умножения считывается по 9 и 10 с блока i (младшая половина произведения) и блока 3 (старшая половина) .

Деление.

Операция деления выполняется в два этапа.

На первом этапе в. блоки 3 через регистры 2 и мультиплексор 4 по шине 10 загружается старшая половин делимого.

На втором этапе через шины 9 и 10 всех модулей параллельно- в бло 1 и регистр 2 загружгиотся соответственно младшая половина делимого и делитель. Дешифратор 39 выдает в этом случае сигнгш логической единицы на второй выход.

Сигнал Установ со входа 21 каждого модуля сбрасывает в О счетчик40, устанавливает в i триггер 42 и переводит узел 38 в исходное состояние. Единичное значение сигнала на выходе 57, которое вьщается с выхода RS-триггера 42 в старшем модуле, разрешает прохождение синхроимпульса через элемент 64 И и элемент 60 ИЛИ на информационный вход RS-триггера 59, который устанавливает его в единичное значение, т.е. старший модуль перехо-, дит в активное состояние и запускается его счетчик 40. В активном модуле при делении из узла 38 через элемент 49 И на выход 30 выдается в каждом цикле сигнал сдвига регистра 98 блока 1 влево на один разряд. В первом цикле по единичному значению сигнала на выходе 32 через мультиплексор 4 в блок 3 вьадается обратный код делителя, который складывается со старшей половиной делимого. Одновременно как и при умножении на выход 26 старшего модуля выдается единичный сигнал с выхода 33 через коммутатор 6. Во всех остальных циклах узел 38 выдает единичный сигнал на выход 32 или 33 в зависимости от знака предыдущего частичного остатка. Знак частичного остатка из блока 3 в модуле .поступает по выходу 37 в узел 38, который по нему вьщает на вход элемента 50 И значение очередного разряда частного. В старшем модуле этот сигнал выдается на шину Ilk После вычисления очередного частичного остатка содержимое регистра 92 блока 3 в каждом модуле сдвигается влево на один разряд. При этом сигнал с выхода его старшего разряда вьадается на шину 16 который через шину 15 поступает на вход младшего разряда регистра 92 блока 3 соседнего более старшего модуля и заполняет освободившийся при сдвиге младший разряд. В младшем модуле на его шину 15 поступает сигнсш с выхода старшего разряда регистра 98 блока 1 активного модуля, который выдается на шину 13. В младший разряд регистра 98 блока 1 активного модуля при его сдвиге влево записывается очердной разряд частного, который поступает с шины 11 из старшего модуля. По истечении очередг ных (п-1) циклов с выхода переноса (k-l)-ro разряда счетчика 40 в блоке 5 активного модуля выдается единич 0 ный сигнал на выход 55. Этот сигнал поступает на вход узла 41 этого модуля и разрешает прохождение синхроимпульса через элемент 66 И и элемент 61 ИЛИ на вход сброса RS-триг15 гера 59 и сбрасывает признак активности модуля. К этому времени все разряды младшей половины делимого в активном модуле оказываются выдвинутыми из регистра 98 блока 1 в регистр 92 блока 3 мяадшего модуля, а вместо них в регистре 98 сформированы очередные п разрядов частного. Одновременно со сбросом признака активности сигнгш с выхода 55 через

25 элемент 47 И выдается на шину 23 и поступает через шину 25 соседнего 5олее младшего Модуля на вход его узпа 41 и переводит модуль в активное состояние. После формирования последQ них п разрядов Частного из младшего модуля выдается на его шину 23 сигнал, который через шину 25 поступает в блок 5 старшего модуля. Этот сигнал проходит через его элемент 46 И и элемент 52 ИЛИ, вьщается на шину 24, поступает на шины 24 всех модулей и воспринимается как сигнал завершения операции. По этому сигналу производится при необходимости коррекция остатка в блоках 3 всех модулей. Результат операции деления считывается по шинам 9 и 10 и 3 блока 1 (частное) И. блока 3 (остаток) .

С помощью предлагаемого устройства можно непосредственно выполнять умножение целых чисел, кодов, чисел со знаком, представленных в форме .фиксиргаванной запятой, с получениемполноразрядного произведения. Можно j выполнять деление двойного слова на одинарное с получением точного частного и остатка. Ставшая и младшая части произведения или результаты операции деления могут быть по отдельности или одновременно считаны

5 с шин 9 и 10. Кроме этого, возможность получать полноразрядное произведение, точное частное и остаток предоставляет гибкие средства проводить -округление окончательных резуль0

татов, эффективно выполнять операции

умножения и деления с двойной и т.д. точностью, операции с плавающей запятой/ а также использовать указанное устройство в качестве универсалького рдвигателя кодов на произвольное число разрядов. Предлагаемое устройство эффективнее прототипа и по быстродействию за счет одновременной подачи операндов и выдачи результатов на две магистрали. Кроме того, устройство обладает и свойством pacf ширяемости, т.е. оно может рассматриваться как отдельный п- разрядный модуль, на базе которого без дополнительных затрат оборудования простым соединением модулей могут быть получены устройства прхэизвольной разрядности, кратной п. Введение в блок управления устройства узла формирования признака активности позволяет производить сдвиги множителя и частного независимо в каждом модуле, что дает экономию числа внешних выводов модуля, что особейно важно при реализации устройства в виде БИС.

Формул а изобретения

1, Устройство для выполнения операций умножения и деления, содержащее блок приема и выдачи, блок сум мирования, регистр, мультиплексор и блок управления, причем первый информационный вход блока приема и выдачи соединен с информационной шиной первого операнда, первый информационный выход регистра соединен с первым информационньзм входом мультиплексора, выход которого соединен с первым информационным входом блока суммирования, первый выход которого соединен с первым входом блока управления, первый и второй выходы которого соединены соответственно с первым и вторым управляющими входами блока приема и выдачи, третий, четвертый и пятый выходы блока уп.равления соединены соответственно с первым, вторым и третьим управляющими входами мультиплексора, шестой и седьмой выходы блока управления соединены соответственно с первым и вторым управляющими входами блока суммирования, отличающеес тем, что, с целью повышения быстродействия и расширения функциональных возможностей за счет выполнения операций над целыми числами, числами с плавающей запятой и обеспечения свойства модульности, в него введены два элемента И и коммутатор, причем второй информационный вход блока приема и выдачи соединен с информационной шиной (n-l)-ro старшего разряда первого операнда устройства, третий информационный вход блока приема соединен с информационной шиной нулевого разряда первого операнда устройства, вторым входом блока управления и выходом первого элемента И, информационный вход регистра соединен с информационной

шиной второго операнда устройства и первым выходом блока суммирования, третий выход которого является выходом переноса из ( -1)-го старшего разряда уотрюйства, а четвертый выход - выходом двух младших разрядов устройства, третий вход блока управления соединен .с информационной шиной старшего очередной пары разрядов первого операнда устO ройства и выходом второго элемента И, первый и второй выходы блока приема и вьдачи соединены соответственно с первыми входами первого и второго элементов И, вторые входы которых

5 объединены и подключены к восьмому выходу блока управления, второй выход регистра соединен с первым входом коммутатора, второй вход которого соединен с четвертым входом блока управления и является входом управления коммутацией устройства, а третий вход - с первым управляющим входом мультиплексора, второй информационный вход которого является

5 входом нулевого разряда второго операнда устройства, пятый, шестой и седьмой входы блока управления соединены Соответственно с шинами запуска, завершения операции и счета уст0 1Ройства, восьмой вход блока управлег ния является входом синхронизации устройства, девятый вход блока управления соединен с третьим управляющим входом блока суммирования и третьим управляющим входом блока приема и вьодачи и является входом сброса устройства, четвертЬй вход блока приема и выдачи является входом (И-2)-гр старшего разряда первого операнда устройства, второй информационный вход блока суммирования соддинен с информационной двух млацгших разрядов устройства,третий информационный вход блока суммирования соединен с информационной шиной, (ii-l)-ro

5 старшего разряда второго операнда устройства, четвёртый и пятый, информационные входы блока суммирования являются соответственно входами (П-2)-го старшего разряда второго

0 операнда и переноса в младший разряд устройства, выход коммутатора является выходом переноса из (fl-l)-ro CTajxaero разряда устройства.

2. Устройство по п. 1,отличающеес я тем, управления содержит узел формирования признака активности, дешифратор, узел выработки управляющих сигналов, счетчик, триггер, элемент НЕ, восемь элементов И и два элемента ИЛИ, причем первый вход узла формирования признака активности соединен с первыми входами узла выработки управляющих .сигналов, первого, второго, третьего и четвертого элементов И и первым

выходом дешифратора., второй выход которого соединен с первыми входами пятого, шестого и седьмого элементов И и вторыми входами узла выработки управляющих сигналов и узла формирования признака активности и является шестым выходом блока управления , выход узла формирования признака активности соединен с управляющим входом счетчика и вторыми входами первого и седьмого элементов И и является восьмым выходом блока управления, выходы первого и седьмого элементов И являются соответственно первым и зторым выходами блока управления, третий вход узла формирования признака активности Соединен со входом элемента НЕ, .13ТО1Ж1МИ входами третьего, четвертого., пятого элементов И и первым входом восьмого элемента И и является четвертьм входом блока управления, четвертый вход узла формирования признака активности соединен со сченым входом счетчика и третьим входом узла выработки управляющих сигналов и является восьмьии входом бло управления, пятый вход узла формирования признака активности соединен с прямым выходом триггера и третьим входом третьего элемента И, шестой вход узла формирования признака активности является девятым входом блка управления и соединен с информационным вводом триггера, входом сбрса счетчика, входом дешифратора и четвертым входом узла выработки управляющих сигналов, пятый вход которого является шестым входом блока управления, а шестой вход соединен с выходом восьмого элемента И и является вторым входом блока управления, седьмой вход узла выработки управляющих сигналов является третьим входом блока управления, первый, второй, третий и четвертый выходы узла выработки управляющих сигналов являются соответственно третьим, четвертым, пятым и седьмым выходами блока управления, выход старшего разряда счетчика :соединен со входом сброса триггера, выход (k-2)-ro разряда счетчика соединен с седьмым входом узла формирования признака активности, вторым входом второго элемента И и третьим входом четвертого элемента И, выход (k.-l)-ro разряда счетчика соединен со вторым входом шестого элемента И и восьмым входом узл.а формирования признака .активности, девятый вход которого является пятым входом блока управления и соединен с выходом шестого элемента И, выход элемента НЕ соединен с третьим входом второго элемента И выход которого соединен с первым входом элемента ИЛИ, второй вход

которого соединен с выходом третьего элемента И, а выход - с третьим входом пятого элемента И, десятым входом узла формирования признака активности и является седьмым Твходом блока управления, выход четвертого элемента И соединен с первым входом второго элемента И, второй вход которого соединен с выходом пятого элемента И, а выход - с пятым

0 входом узла выработки управляющих сигналов.

3. Устройство по п. 2, отличающееся тем, что узел формирования признака активности содер5жит элемент НЕ, два элемента ИЛИ, триггер и пять элементов И, причем первые входы пяти элементов И объёди нены и являются четвертым входом .узла Формирования признака активнос0ти, вторые входы первого и второго элементов И объединены и являются первым входом узла формирования признака активнос-ти, третий вход первого элемента И является девятым входом узла формирования признака

5 активности, вход элемента НЕ соединен со вторым входом третьего элемента И и является третьим входом узла формирования признака активности, а выход - со вторым входом чет0вертого элемента И, выход которого соединен с первым входом первого элемента И, второй и третий входы которого соединены соответственно с выходами первого и ТЕ етьего элементов

5 И, а выход - с информационным входом триггера, вход сброса которого соединен с выходом второго элемента ИЛИ, первый и второй входы которого соединены соответственно с вы0ходами пятого и второго элемента И, третий вход второго элемента ИЛИ .является шестым входом узла формирования признака активности, второй эход пятого элемента И является

5 седьмым входом узла формирования признака активности, третьи входы третьего, четвертого и пятого элементов И объединены и являются вторым входом узла формирования призна0ка актив.ности, четвертый вход третьего элемента И является пятым входом узла формирования признака активности, третий вход второго элемента И является восьмым входом узла формирования признака активности, четвер5тый вход четвертого элемента И является десятым входом узла формирования признака активности, единичный выход триггера является выходом узла формирования признака актив1ГОСТИ.

4. Устройство по п. 2, отличающеес я тем, что узел выработки управляющих сигналов содержит два элемента НЕ, три триггера,

р. элемента ИЛИ и тринадцать элементов И, причем вход первого элемента НЕ соединен с первыми входами первого, второго, третьего, четвертого и пятого .элементовИ и информационным входом первого триггера и является шестым входом узла выработки управляющих сигналов, первые входы шестого, седьмого, восьмого, девятого и десятого элементов И объединены и соединены со вторыми входами третьего, четвертого и пятого элементов И и являются первым входом узла выработки управляющих сигналов, первые входы одиннадцатого, двенадцатого и тринадцатого элементов И объединены и являются вторым входом узла выработки управляющих сигналов,входы синхронизации первого и второго триггеров объединены и являются третьим входом узла выработки управляющих сиг.налов, входы сброса первого, второго и третьего триггеров объединены и являются девятым входом узла выработки управляющих сигналов, информационный вход второго триггера соединен с выходом первого элемента ИЛИ первый и второй входы которого соединены соответственно свыходами первого и второго элементов И, второй вход первого элемента И сбединен с прямым выходом второго триггера, вторыми входами седьмого, девятого и десятого элементов И, третьим входом четвертого элемента И, четвертый вход которого соединен с третьим входом седьмого и пятого элементов И, выходом второго элемента НЕ вход которого соединен со вторьлм входом второго элемента И и является седьмьм входом узлавыработки управляющих сигналов, информационный вход третьего триггера является пятым входом узла выработки управляющих сигналов, прямой выход первого триггера соединен со вторыми входами восьмого и одиннадцатого элементов И,инверсный (ВЫХОД первого триггера соединен со. вторым входом двенадцатого и третьим входом девятого элементов И, прямой выхйд третьего триггера соединен с третьим входом восьмого и четве1ртым входом девятого элементов Ц, инверс-ный выход третьего триггера соединен со вторыми входами шестого и двенадцатого элементов И, третьими входами третьего, десятого и одиннадцатого элементов И, четвертыми входами пятого и седьмого элементов И и пятым входом четвертого элемента И, четвертый вход третьего элемента И соединен с третьим входом шестого, четвертым входом десятого элементов И и входом второго элемента НЕ, пятый вход третьего элемента И соединен с инверсньйи выходом второго триггера четвертьзми входс1ми пятого, шестого и восьмого элементов И, выход первого

элемента НЕ соединен с пятыми входами шестого, седьмого и десятого элементов И, выходы одиннадцатого, третего и четвертого элементов И соединены соответственно с первым, вторым и третьим входами первого элемента ИЛИ, выход которого является первь4м выходом узла выработки управляющих сигналов, выходы шестого, седьмого, восьмого, девя-того и двенадцатого элементов И сое динены соответственно с первым, вторым, третьим, четвертым и пятым входами второго элемента ИЛИ, выход которого является вторым выходом узла выработки управляющих сигналов, выходы пятого и десятого элементов И соединены соответственно с первым и вторым входами третьего элемента ИЛИ, выход которого является третьим выходом узла выработки управляющих сигналов, выход тринадцатого элемента И является четвертым выходом узла выработки управляющих сигналов.

5, Устройство но пп, 1 и 2 о т личающеес я тем, что блок суммирования содержит сумматор, регистр, два элемента И и группу элементов И, причем входы суммирования сумматора являются соответственно первыми входами блока суммирования, эход переноса младшего разряда сумматора является пятым входом блока суммирования, выходы сумматора соединены соответственно с информационными входами регистра, второй информационный вход которого является третьим входом блока суммирования и соединен с выходом первого элемента И, вход нулевого разряда регистра является вторым входом блока суммирования и соединен с выходом второго элемента И, первый вход которого соединен с выходом нулевого разряда ре Гистра, выход (П-1).-го разряда которого соединен с первым входом первого элемента И, второй вход которого соединен со входом управления сдвигом влево регистра и является вторым управляющим входом блока суммирования, второй вход второго элемента И соединен со входом управления сдвигом вправо регистра и является первым управляющим входом блока суммирования, третий информационный вход регистра является четвертым входом блока суммирования, выходы регистра соединены соответственно с первыми входами элементов И группы и входами переноса сумматора, выход ()-ro разряда которого является третьим выходом блока суммирования, выход первого младшего разряда регистра является четвертым выходом блока суммирования, выход второго м.падшего разряда является первым выходом блока суммирования, вторйе входы элементов И группы объединены и являют.оя третьим управляющим входом блока суммирования, выходы элементов И группы являются вторым выходом блока суммирования,

6. Устройство по пп. 1 и 2, о т(Личающееся тем, что блок приейа и выдачи содержит регистр, элемент И и группу элементов И, причем информационные входы регистра являются первым входом приема и соединены соответственно с выходами элементов И группы, первые входы которых соединены соответстйенно с выходами регистра, выход (h-l)-ro разряда которого соединен с первым входом элемента И, второй вход которого соединен сб входом управления сдвигом впра.во регистра и является первым управляющим входом блока приема и выдачи, выход элемента И соединен со входом (V)-l)-ro разряда регистра и является вторым входом блока приема и вьадачи,

вход управления сдвигом влево регистра является вторым управляющим входом блока приема и выдачи, вход ( РО разряда регистра является четве. iLfli входом блока приема и выдачи, вход нулевого разряда регистра является третьим входом блока приема и выдачи, выходы нулевого и первого разрядов регистра являются соответственно вторым и первым выходами блока приема и выдачи, вторые входы элемен, тов И группы объединены и являются третьим управляющим входом блока (1риема и выдачи.

Источники информации, принятые во внимание при экспертизе

1.Патент США 3961750, КЛ. G 06 F 7/52, 1976.

2.Дроздов К.А. и др. Электронные цифровые вычислительные машины.Во.ениздат , 1968, с. 432-437 (прототип

fl К

фие.г

фиг.6

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для выполнения операций умножения и деления | 1986 |

|

SU1403061A1 |

| Микропроцессор | 1979 |

|

SU894715A1 |

| Арифметическое устройство с фиксированной точкой | 1984 |

|

SU1241230A1 |

| Микропрограммный процессор | 1980 |

|

SU868766A1 |

| Устройство для вычисления коэффициентов Фурье | 1985 |

|

SU1315999A1 |

| 8-Битный микропроцессор | 1982 |

|

SU1161950A1 |

| Процессор с микропрограммным управлением | 1983 |

|

SU1149273A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| Устройство для сбора данных о работе ЭВМ | 1982 |

|

SU1121679A1 |

| Арифметическое устройство | 1984 |

|

SU1236473A1 |

Авторы

Даты

1982-08-30—Публикация

1980-03-19—Подача