и одним из входов элемента И четности, другой вход которого соединен с инверсным выходом формирователя, а выход соединен с R-входом триггера сравнения, выходы элементов И вычитания соединены с входами сумматора, выходы которого соединены с входами дешифратора, подключенного через двухвходовые элементы И к S-входам триггеров уровня, вторые входы двухвходовых элементов И соединены с пря26

109

мым выходом введенного формирователя, первые входы элементов И уровней отпускания соединены с прямым выхо1ДОМ блока сравнения, вторые входы одних из них подключены к прямому выходу одного, а других - другого триггеров уровня, третьи входы элементов И уровней отпускания подключены к соответствующим выходам блока памяти.

| название | год | авторы | номер документа |

|---|---|---|---|

| Дискретный адаптивный дельта-модулятор | 1981 |

|

SU972661A1 |

| Арифметико-логическое устройство для сложения и вычитания чисел по модулю | 2017 |

|

RU2639645C1 |

| Арифметико-логическое устройство для вычитания чисел по модулю | 2016 |

|

RU2628175C1 |

| Суммирующий телеметрический счетчик | 1977 |

|

SU658744A1 |

| Преобразователь перемещений в код | 1983 |

|

SU1111188A1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ПРЕОБРАЗОВАТЕЛЬ ПЕРЕМЕННОГО НАПРЯЖЕНИЯ В ЦИФРОВОЙ КОД ОТКЛОНЕНИЯ | 1992 |

|

RU2074396C1 |

| Электронные часы с фиксацией и документированием времени | 1988 |

|

SU1552147A1 |

| Устройство для идентификации жил кабельных изделий | 1991 |

|

SU1762277A1 |

| АРИФМЕТИКО-ЛОГИЧЕСКОЕ УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ, ВЫЧИТАНИЯ И УМНОЖЕНИЯ ЧИСЕЛ ПО МОДУЛЮ | 2019 |

|

RU2711051C1 |

| ОХРАННОЕ КОДОВОЕ УСТРОЙСТВО | 1994 |

|

RU2084958C1 |

ПОРОГОВОЕ УСТРОЙСТВО, содержащее блок сравнения, соединенный прямым входом через первый ключ с шиной входного сигнала, прямым выходом через выходной формирователь с пшной выходного сигнала, отличающееся тем, что, с целью расширения его функциональных возможностей путем изменения порога срабатывания и отпускания в зависимости от скорости нарастания входного сигнала, в него введены п эле ментов И уровней срабатывания и п элементов И уровней отпускания, блок памяти, два триггера уровня, триггер сравнения, элемент задержки, входной ключ, аналого-цифровой преобразователь, ограничитель, тактовый генератор, ключ триггера четности, ключ сумматора, два элемента И вычитания, сумматор, триггер четности, элемент И четности, формирователь, два двухвходовых элемента И, дешифратор, причем первый вход аналого-цифрового преобразователя соединен с выходом тактового генератора, второй вход через входной ключ - с шиной входного сигнала, второй вход входного ключа соединен через элемент задержки с инверсным выходом блока сравнения, шина входного сигнала через ограничитель соединена с входом тактового генератора, инверсный выход блока сравнения соединен с S-входом триггера сравнения, R-входами триггеров уровня и с первыми входами элементов И уровней срабатывания, вторые входы одних из которых соединены с прямым выходом одного триггера G 45 уровня, а других - другого триггера уровня, третьи входы - с соответствующими выходами блока памяти, инверсный вход блока сравнения (;оединен с выхгщами элементов И уровней срабатывания и отпускания и вторым входом выходного формирователя, второй вход первого ключа соединен с О со инверсным выходом триггера сраврсения и S-входом триггера четности, прямой выход триггера сравнения соеСО динен с первыми входами ключа суммаto тора и ключа триггера четности, втоо рые входы которых соответственно соединены с выходами аналого-цифрового преобразователя и тактового генератора, а выходы - соответственно с первыми входами элементов И вычитания и счетным входом триггера четности, прямой выход триггера четности соединен с вторым входом одного из элементов И вычитания, а второй вход другого элемента И вычитания соедиисн с инверсным выходом трипера четшхти, входом введе 1ного (юрмироЕзателя

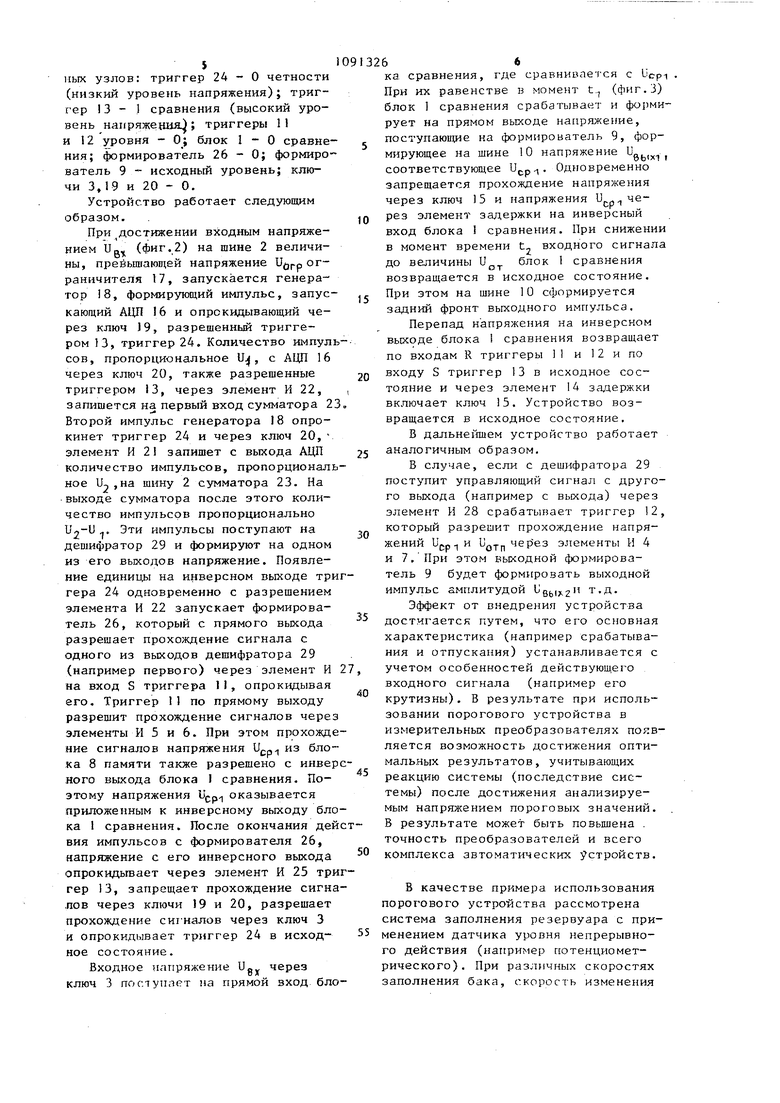

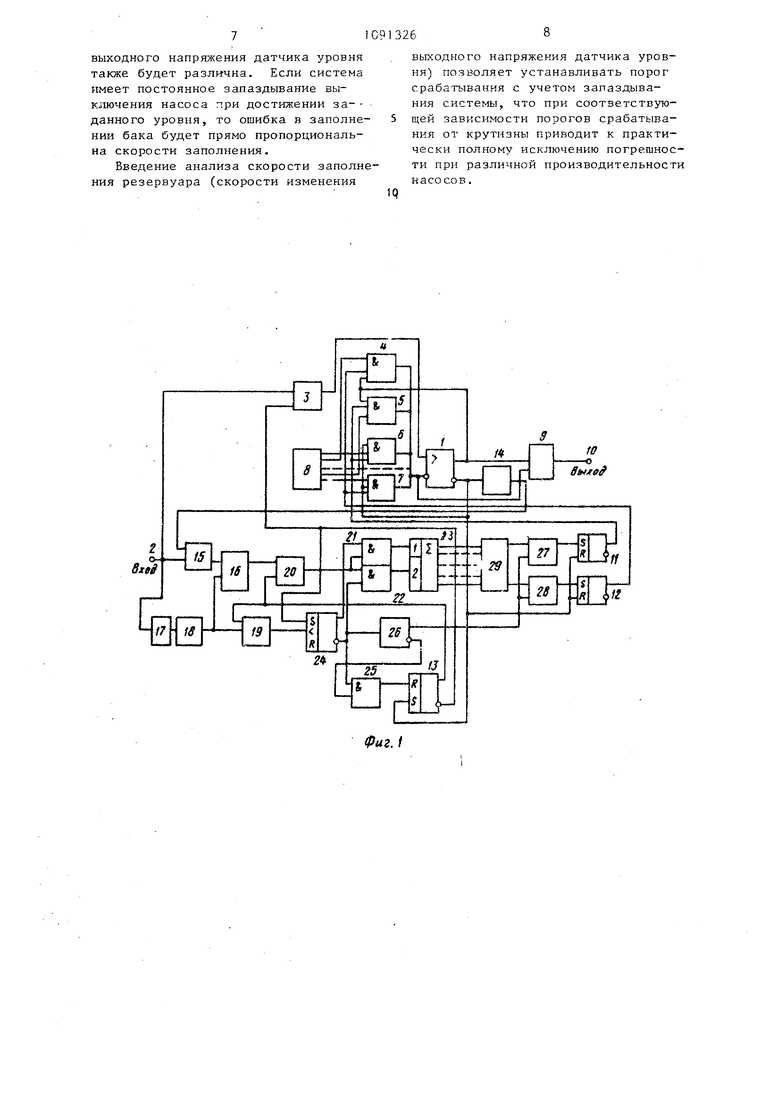

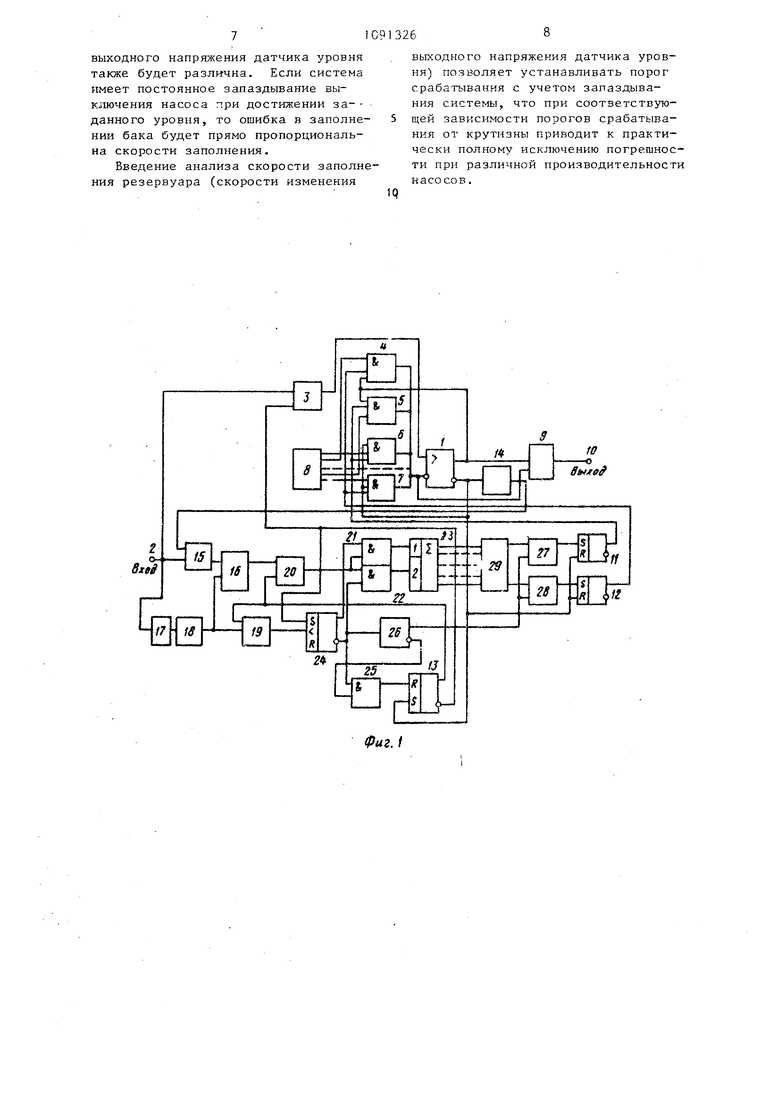

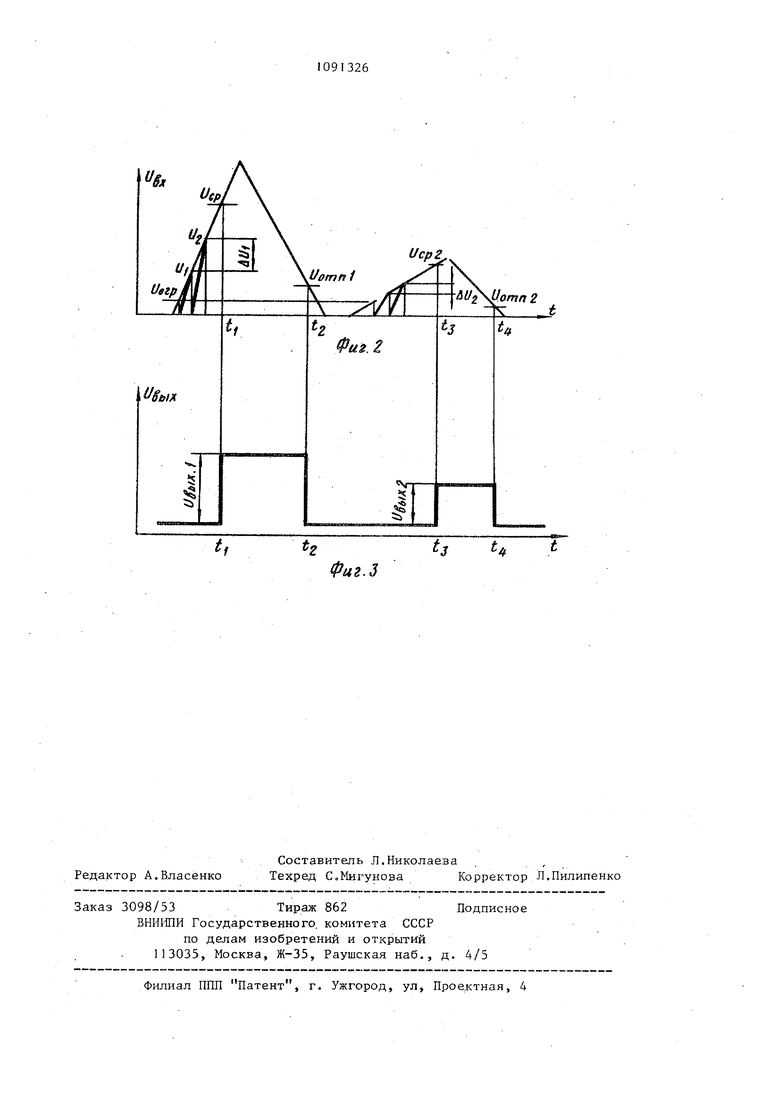

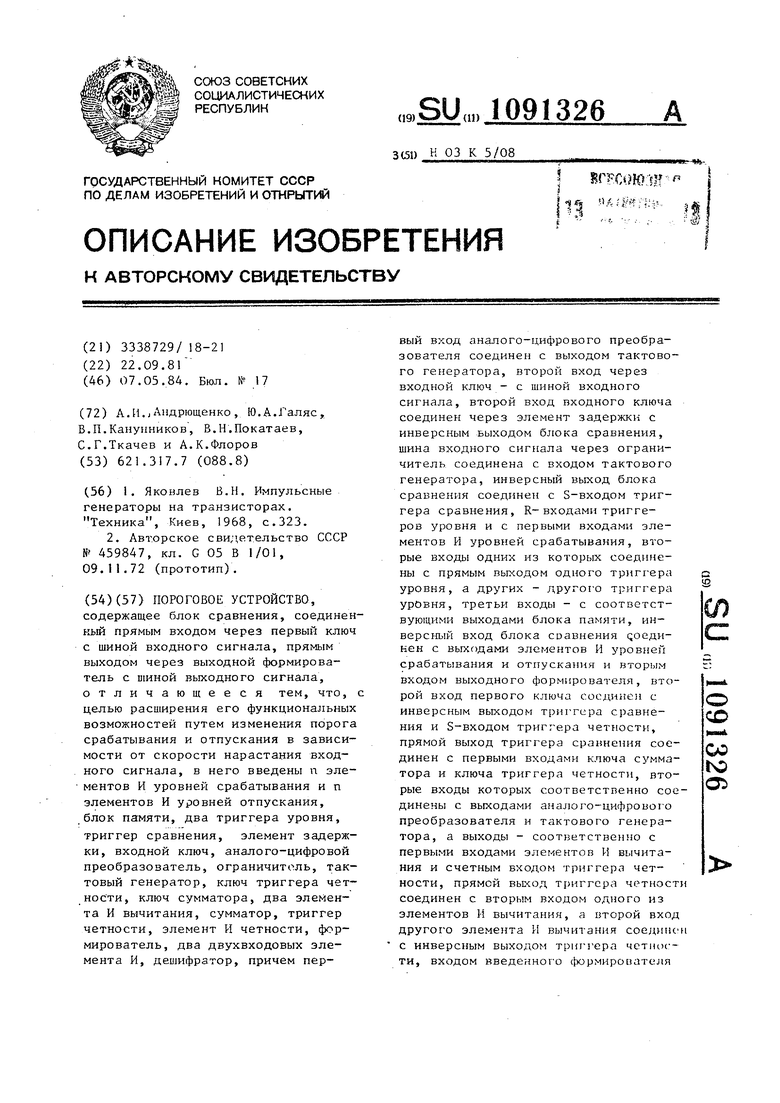

Изобретение относится к импульсной технике и может быть использова но, например в измерительных устройствах преобразования сигналов частотных датчиков, формирования пр моугольных импульсов на напряжения произвольной формы и т.д. Известны пороговые устройства, основанные на сравнении опорного напряжения с напряжением, действующим на входной шине, содержащие триггер Шмитта с эмиттерным повторителем . Недостатками указанных пороговых устройств являются фиксированные значения порогов срабатывания, что позволяет при работе учитывать особенности входного сигнала (например скорости нарастания входного напряжения) . Наиболее близким к предлагаемому является пороговое устройство, содержащее блок сравнения, соединенный прямым входом через первьй ключ с шиной входного сигнала, прямой выход которого через выходной форми рователь соединен с шиной выходного сигнала С2 . Недостатками известного порогового устройства являются фиксирован ные значения порогов его срабатывания и отпускания, что не позволяет процессе работы изменять (устанавливать) их в зависимости от особенностей входного сигнала (например, скорости его нарастания), т.е. огра чивает его функциональные возможности. Цель изобретения - расширение функциональных возможностей путем изменения порога срабатывания и отпускания устройства в зависимости от скорости нарастания входного сигнала. Поставленная цель достигается тем, что в пороговое устройство, содержащее блок сравнения, соединенный прямым входом через первый ключ с шиной входного сигнала, прямым выходом через выходной формирователь с пшной выходного сигнала, введены п элементов И уровней срабатывания и п элементов И уровней отпускания, блок памяти, два триггера уровня, триггер сравнения, элемент задержки, входной ключ, аналого-цифровой преобразователь, ограничитель, тактовый генератор, ключ триггера четности, ключ сумматора, дйа элемента И вы-читания, сумматор, триггер четности, элемент И четности, формирователь, два ДВ5ТСВХОДОВЫХ элемента И, дешифратор, причем первый вход аналогоцифрового преобразователя соединен с выходом тактового генератора, второй вход через входной ключ - с шиной входного сигнала, второй вход входного ключа соединен через элемент задержки с инверсным выходом блока сравнения, шина входного сигнала через ограничитель соединена с входом тактового генератора, инверсный выход блока сравнения соединен с S-входом триггера сравнения, R-BXOдами триггеров уровня и с первыми входами элементов И уровней срабатывания, вторые входы одних из которых соединены с прямым выходом одного триггера уровня, а других другого триггера уровня, третьи вхо3ды - с соответствующими выходами блока памяти, инверсный вход блока сравнения соединен с выходами элемен тов И уровней срабатывания и отпускания и вторым входом выходного фор)рователя,второй вход первого ключа соединен с инверсным выходом триггера сравнения и S-входом триггера четности, прямой выход триггера сра нения соединен с первыми входами ключа сумматора и ключа триггера четности, вторые входы которых соот ветственно соединены с выходами ана го-цифрового преобразователя и такт вого генератора, а выходы - соответ ственно с первыми входами элементов И вычитания и счетным входом триггера четности, прямой выход три гера четности соединен с вторым вхо дом одного из элементов И вычитания а второй вход другого элемента И вычитания соединен с инверсным выходом триггера четности, входом вве денного формирователя и одним из входов элемента И четности, другой вход которого соединен с инверсным выходом формирбвателя, а выход соед нен с R-входом триггера сравнения, выходы элементов И вычитания соединены с входами сумматора, выходы которого соединены с входами дешифратора, подключенного через двухвходовые элементы И к S-входам триг геров уровня, вторые входы двухвходовых элементов И соединены с прямы выходом введенного формирователя, первые входы элементов И- уровней от пускания соединены с прямым выходом блока сравнения, вторые входы одних из них подключены к прямому выходу одного, а других - другого триггеров уровня, третьи входы элементов уровней отпускания подключены к соответствующим выходам блока памяти. На фиг.1 показана структурная схема предлагаемого устройства; на фиг.2 - входной сигнал устройства; на фиг.З - выходной сигнал устройства. Предлагаемое устройство (фиг.1) содержит блок 1 сравнения (операционный усилитель), соединенньш пря мым, входом с шиной 2 входного сигна ла, через первый ключ 3, а по инвер ному входу через элементы И уровня срабатывания и отпускания 4 - 7 с блоком 8 памяти. Прямой вход блока сравнения соединен через выходной 6 формирователь 9 с шиной 10 выходного сигнала и двумя параллельно связанными входами элементов И 4 - 5, передающими порог отпускания устройства. Инверсньм выход блока 1 сравнения соединен с двумя параллельно связанными входами элементов И 6-7, передающими порог срабатывания устройства, входами двух триггеров 11 и 12 уровня, входом элемента И 5, триггера 13 сравнения и через элемент 14 задержки с одним из входов ключа 15, вход которого соединен с шиной 2, а выход с входом АЦП 6. Шина 2, кроме того, соединена через ограничитель 17 с тактовым генератором 18. Выход тактового генератора 18 связан с вторым входом А1Щ 16 и одним из входов ключа 19 триггера четности. Второй вход ключа 9 соединен с одним из входов ключа 20 сумматора и прямым выходом триггера 13 сравнения. Второй вход ключа 20 соединен с выходом АДП 16, а выход - с параллельно соединенными входами двух элементов И 21-22 вычитания, выходы которых подключены к входам сумматора 23, а вторые входы к прямому и инверсному выходам триггера 24 четности, счетный вход которого связан с выходом ключа 19, а вход S с инверсным выходом триггера 13 сравнения. Прямой выход триггера 24 четности соединен с входом элемен- . та И 21. Инверсный выход триггера 24 четности связан с входом элемента И 22, входом элемента И 25 четности и входом формирователя 26, прямой выход которого связан с параллельно вк тченными входами двухвходовых элементов И 27-28, вторые входы которых связаны с вьЕходами дешифратора 29, работающего от выходон сумматора 23. Элементь И 27-28 соединены с S-входами триггеров уровня 11-12. Элементы в схеме используются по прямому назначению, поэтому дополнительного пояснения цели их использования не требуют. Источник питания устройства на схеме условно не показан. Количество элементов И 4 - 7, 21-22, 27-28 может быть сколь угодно велико. Исходное состояние устройства (питание подано, входной сигнал отсутствует) соответствует следующему состоянию прямых выходов функциональмых узлов: триггер 24-0 четности (низкий уровень напряжения); триггер 3 - 1 сравнения (высокий уровень накрял ения ; триггеры 11 и 12 уровня - 0; блок I - О сравнения; формирователь 26-0; формиро ватель 9 - исходный уровень; ключи 3, 19 и 20 - О, Устройство работает следующим образом. При достижении входным напряжением Ug (фиг.2) на шине 2 величины, прейышающей напряжение ограничителя 17, запускается генератор 18, формирующий имлульс, запускающий АЦП 16 и опрокидывающий через ключ J9, разрешенный триггером 13, триггер 24. Количество импул сов, пропорциональное U., с АЦП 16 через ключ 20, также разрешенные триггером 13, через элемент И 22, запишется на первый вход сумматора 2 Второй импульс генератора 18 опрокинет триггер 24 и через ключ 20, элемент И 21 запишет с выхода АЦП количество импульсов, пропорционал ное и,,на шину 2 сумматора 23. На выходе сумматора после этого количество импульсов пропорционально 1 Эти импульсы поступают на дешифратор 29 и формируют на одном из его выходов напряжение. Появление единицы на инверсном выходе три гера 24 одновременно с разрешением элемента И 22 запускает формирователь 26, который с прямого выхода разрешает прохождение сигнала с одного из выходов дешифратора 29 (например первого) через злемент И на вход S триггера 11, опрокидывая его. Триггер 11 по прямому выходу разрешит прохождение сигналов через элементы И 5 и 6. При этом прохожде ние сигналов напряжения из блока 8 памяти также разрешено с инвер ного выхода блока 1 сравнения. Поэтому напряжения оказывается приложенным к инверсному выходу бло ка 1 сравнения. После окончания дей вия импульсов с формирователя 26, напряжение с его инверсного выхода опрокидывает через элемент И 25 три гер 13, запрещает прохождение сигна лов через ключи 19 и 20, разрешает прохождение сигналов через ключ 3 и опрокидывает триггер 24 в исходное состояние. Входное напряжение Ug через ключ 3 поглупеет на прямой вход бло 6 где сравнивае1ся с Ucpi ка сравнения. При их равенстве в момент t. (фиг.З) блок 1 сравнения срабатывает и формирует на прямом выходе напряжение, поступающие на формирователь 9, формирующее на шине 10 напряжение Ь соответствующее Ucp-i- Одновременно запрещается прохождение напряжения через ключ 15 и напряжения U. через элемент задержки на инверсный вход блока сравнения. При снижении в момент времени t, входного сигнала до величины U блок 1 сравнения возвращается в исходное состояние. При этом на шине 10 сформируется задний фронт выходного импульса. Перепад напряжения на инверсном выходе блока i сравнения возвращает по входам R триггеры 11 и 12 и по входу S триггер 13 в исходное состояние и через элемент 14 за,аержки включает ключ 15. Устройство возвращается в исходное состояние, В дальнейшем устройство работает аналогичным образом, В случае, если с дешифратора 29 поступит управляющий сигнал с другого выхода (например с выхода) через элемент И 28 срабатывает триггер 12, который разрешит прохождение напряжений Upp и Uflyp через элементы И 4 и 7. При этом вькодной формирователь 9 будет форм1гровать выходной импульс амплитудой т.д. Эффект от внедрения устройства достигается путем, что его основная характеристика (например срабатывания и отпускания) устанавливается с учетом особенностей действующего входного сигнала (например его крутизны). В результате при использовании порогового устройства в измерительньк преобразователях по :вляется возможность достижения оптимальных результатов, учитывающих реакцию системы (последствие системы) после достижения анализируемым напряжением пороговых значений. В результате может быть повътена . точность преобразователей и всего комплекса автоматических Устройств. В качестве примера использования орогового устройства рассмотрена истема заполнения резервуара с приенением датчика уровня непрерывноо действия (например г отенциометического). При различных скоростях аполнения бака, скорость изменения

выходного напряжения датчика уровня также будет различна. Если система имеет постоянное запаздывание выключения насоса ггри достижении за- данного уровня, то ошибка в заполнении бака будет прямо пропорциональна скорости заполнения.

Введение анализа скорости заполнения резервуара (скорости изменения

выходного напряжения датчика уровня) позволяет устанавливать порог срабатывания с учетом запаздывания системы, что при соответствующей зависимости порогов срабатывания от крутизны приводит к практически полному исключению погрешности при различной производительности насосов.

фиг. /

ч

Фиг.З

h х

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Яковлев В.Н | |||

| Импульсные генераторы на транзисторах | |||

| Техника, Киев, 1968, с.323 | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1984-05-07—Публикация

1981-09-22—Подача