соединена с входом ширютно-импульсного модулятора, дополнительный выход которого через формирователь импульса подключен к входу триггера, прямой выход которого соединен с управляющими входами первого и четвертого ключей, а инверсный выход -триггера соединен с управляющими входами второго и третьего ключей, вторая обкладка второго запоминающего конденсатора через четвертый повторитель напряжения подключена к вторым выводам пятого элемента с дискретно-управляемой проводимостью, четвертого дополнительного масштабирующего резистора и к входу второго фазоинвертора, выход которого соединен с вторым выводом второго масштабирующего резистора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Времяимпульсное множительно-делительное устройство | 1980 |

|

SU1277142A1 |

| Устройство для вычисления функции @ = @ | 1984 |

|

SU1167621A1 |

| Четырехквадрантный умножитель сигналов постоянного тока | 1982 |

|

SU1062725A1 |

| Вычислительное устройство для широтно- импульсных сигналов | 1978 |

|

SU763908A1 |

| Преобразователь широтно-модулированного сигнала в напряжение | 1988 |

|

SU1691951A1 |

| Элемент с управляемой проводимостью | 1984 |

|

SU1233178A2 |

| Аналоговое запоминающее устройство | 1983 |

|

SU1140178A1 |

| Устройство для вычисления функции @ | 1984 |

|

SU1231517A1 |

| Импульсный регулятор | 1984 |

|

SU1251025A1 |

| Устройство для решения нелинейныхзАдАч ТЕОРии пОля | 1979 |

|

SU809243A1 |

МНОЖИТЕ Л ЫЮ-ДЕЛИ ТЕЛЬНОЕ УСТРОЙСТВО ШИРОТНО-МОДУЛИРОВАННЫХ СИГНАЛОВ, содержащее широтно-импульсный модулятор, источник опорного напряжения, выход которого подключен к первым выводам первого и второго элементов с дискретно-управляемой проводимостью, второй вывод второго элемента с дискретно-управляемой проводимостью через третий элемент с дискретно-управляемой проводимостью соединен с шиной нулевого потенциала, второй вывод первого элемента с дискретно-управляетюй проводимостью через четвертьй элемент с дискретно-управляемой проводимостью и .через первый маештабируквдий резистор подключен к ши:не нулевого потенциала, пятый элемент с дискретно-управляемой прово.димостью, второму выводу первого .элемента с дискретно-управляемой проводимостью подключен первый вывод второго масштабирующего резистора, первый и второй запоминающие конденсаторы, первые обкладки которах соединены с шиной нулевого потенциала, выход широтно-импульсного модулятора является выходом устройства и соединен с управляющими входами четвертого и пятого элементов с дискретно-управляемой проводимостью, управляющие входы первого, третьего и второго элементов с дискретноуправляемой проводимостью являются соответственно входами первого и второго сигналов-сомножит.елей и входом сигнала-делителя, отличающееся тем, , с целью повышения быстродействия, в него введены два интегратора, четыре повторителя напряжения,-два фазоинвертора, четыре ключа, формирователь импульса, триггер и четыре дополнительных масштабирующих резистора, причем второй вывод второго элемента с дискретно-управляемой проводимостью соединен с входом первого повторителя напряжения, выход которого подключен к первому выводу первого дополнительного масштабирующего резистора, BTO-I (Л рой вывод которого соединен с первым выводом второго дополнительного масштабирующего резистора и через первый ключ - с входом первого интегратора, выход которого через второй ключ соединен с второй обкладкой перЬого запоминающего конденсатора,второй вывод первого элемента с дискрет(но-управляемой проводимостью подключен к входу второго повторителя ;о сд напряжения, выход которого соединен с первым выводом третьего дополнительного масштабирующего резистора и через первый фазоинверсо тор - с вторым выводом второго дополнительного масштабирующего ре05 зистора, второй вывод третьего дополнительного масштабирующего резистора с;оединен с первыми выводами пятого элемента с дискретно-управляемой проводимостью и четвертого дополнительного масштабирующего резистора, а через третий ключ подключен к входу второго интегратора, выход которого через четвертый ключ подключен к второй обкладке второго запоминающего конденсатора, вторая обкладка первого запоминающего конденсатора через третий повторитель напряжения

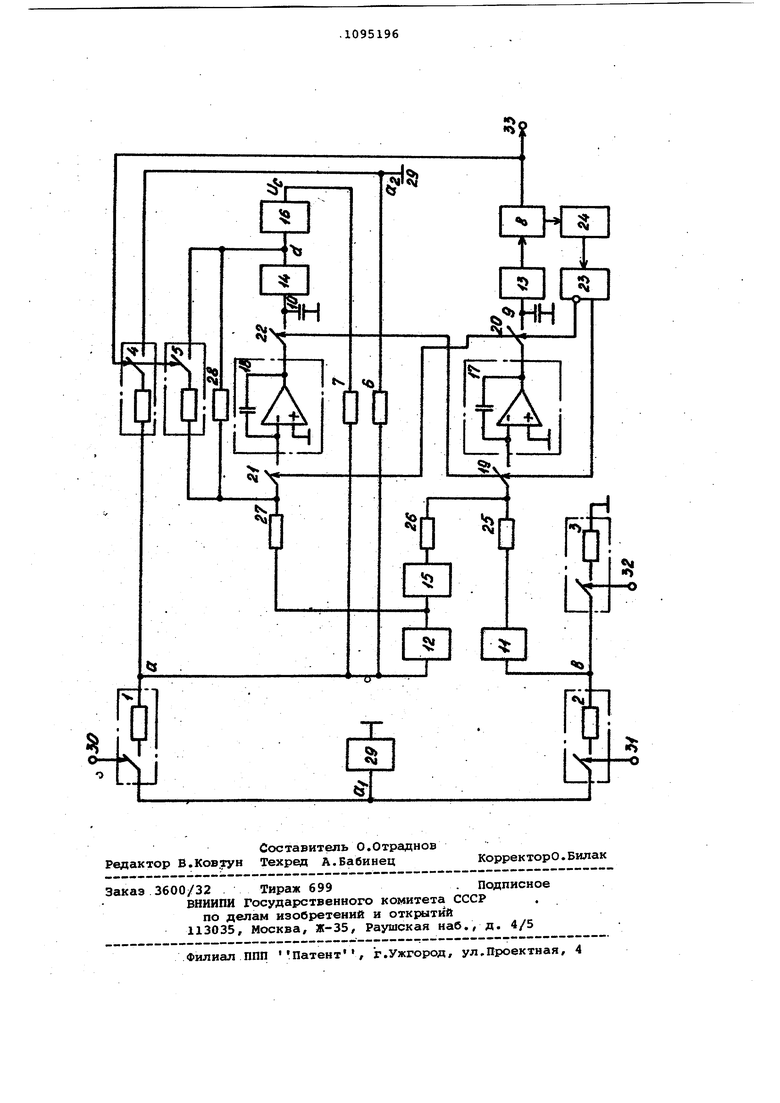

Изобретение относится к электрическим вычислительным устройствам и может быть использовано в аналоговы вычислительных машинах. Известно устройство, предназначе ное для умножения и деления широтно-модулированных сигналов, содержащее импульсные делители напряжения, масштабный усилитель и сумматор 1 . Недостаток устройства -г невысока точность работы. Наиболее близким к предлагаемому является множительное устройство ши ротно-модулированных сигналов, содержа11 Йё етыре дискретно-управляемые арйводимости, соединенные по мо товой схеме, к первым выходам перво и второй дискретно-управляемой проводимости подключен выход источника опорного напряжения, .второй вывод первой дискретно-управляемой провод мости соединен с шиной нулевого потенциала через первый сглаживающий конденсатор и через цепь, состоящую из параллельно соединенных первого масштабного резистора и последовательно соединенных второго масштабного резистора и ключа, второй вывод второй дискретно-управляемой проводимости соединен с шиной нулевого потенциала через второй сглажи вающий конденсатор, а также с первы входом дифференциального усилителя, второй вход которого соединен с втоилм выводом первой дискретно-управляемой проводимости, выход диф ференциального усилителя черев широтно-импульснйй модулятор подключе к управляющим входам четвертой дискретно-управляемой проводимости и ключа, управляющие входы первой, вто рой и третьей дискретно-управляемых проводимостей являйтея входами устройства, выходом которого является выход широтно-импульсного модулятора 2 . , Недостатком известного устройств является низкое быстродействие, свя ь занное с необходимостью фильтрации сигналов апериодическим звеном первого порядка. Цаль изобретения - повышение быстродействия. Цель достигается тем, что в известное множительно-делительное устройство широтно-модулированных сигналов, содержащее широтно-импульсный модулятор, источник опорного напряжения, выход которого подключен к первым выводам первого и второго элементов с дискретно-управляемой -проводимостью, второй вывод второго элемента с дискретно-управляемой проводимостью через третий элемент с дискретноуправляемой проводимостью соединен с шиной нулевого потенциала, второй вывод первого элемента с дискретно-управляемой проводимостью через четвертый элемент с дискретно-управ.ляемой проводимостью и первый масштабирующий резистор подключен к шине нулевого потенциала, пятый элемент с дискретно-управляемой проводимостью, второму выводу первого элемента с дискретно-управляемой проводимостью подключен первый вывод второго масштабирующего резистора, iпервый и второй запоминающие кон{денсаторы, первые обкладки которых соединены с шиной нулевого потенхщала, выходширотно-импульсного модулятора является выходом устройства и соединен с управлящими входами четвертого и пятого элементов с дискретно-управляемой проводимостью, управляющие входы первого, третьего и второго элементов с дискретно-управляемой проводимостью являются соответственно входами первого и второго сигналов-сомножителей и входом сигнала-делителя, введены два интегратора, четыре повторителя напряжения, два фазоинверхора, четыре- ключа, формирователь импульса, триггер и четыре дополнительных масштабирующих резистора, причем второй В1лвод второго элемента с дискретно-управляемой про водимостью соединен с входом первого повторителя напряжения, выход которого подключен к первому выводу первого дополнительного масштабирующего резистора, второй вьшод которого соединен с первым выводом второго дополнительного масштабирующего резистора и через первый ключ |с входом первого интегратора, выход которого через второй ключ соединен с второй обкладкой первого запоминающего конденсатора, второй вывод первого элемента с дискретно-управляемой проводимостью подключен к входу второго повторителя напряжения выход которого соединен с первым выводом третьего дополнительного масштабирующего резистора и через первый фазоинвертор - с вторым выводом второго дополнительного маештабирующего резистора, второй вывод третьего дополнительного масштабирующего резистора соединен с первыми выводами пятого элемента с дискретно-управляемой проводимостью и чет-. вертого дополнительного масштабирующего резистора, а через третий ключ подключен к входу второго интегратора, выход которого через четвертый ключ подключен к второй обкладке вто рого запоминающего конденсатора, вторая обкладка первого запоминающего конденсатора через третий повторитель напряжения соединена с входе широтно-импульсного модулятора,, дополнительный выход которого через формирователь импульса подключен к входу триггера, прямой выход которого соединен с управляющими входами первого и четвертого ключей а инверсный выход триггера соединен с управляющими входами второго и третьего ключей, вторая обкладка второго запоминающего конденсатора через четвертый повторитель напряжения псдключена к вторым выводам пятого элемента с дискретно-управляемой проводимостью, четвертогр дополнительного масштабирующего резистора и к вхрду второго фазоинвертора, выход которого соединен с вторым выводом второго масштабирующего резистора. На чертеже изображена функционал ная схема предложенного множительно-делительного устройства широтномодулированных сигналов, где обозна чены первый, второй, третий, четвер тый и пятый элементы с дискретноуправляемой проводимостью 1, 2, 3, и 5, первый и второй масштабирующие резисторы 6 и 7, широтно-импульсный модулятор 8, первый и второй запоми нающие конденсаторы 9 и 10, первый, второй, третий и четвертый повторители напряжения 11, 12, 13 и 14, пе вый и второй фазоинверторы 15 и 16, первый и второй интеграторы 17 и 18, первый, второй, третий и четвертый ключи 19, 20, 21 и 22, триггер 23, формирователь импульса 24, первый, второй, третий и четвертый дополнительные масштабирующие резисторы 25, 26, 27 и 28, шина нулевого потенциала 29, вход первого сигнала-сомножителя 30, вход сигнала-делителя 31, вход второго сигнала-сомножителя 32, выход 33, Множительно-делительное устройство широтно-модулированных сигналов работает следующим образом. 11реобразование сигналов производится циклически за два периода широтно-импульсного сигнала. В первом периоде производится определение разности средних значений напряжений, действующих на входах первого и второго повторителей напряжения 11 и 12, которое во втором периоде за-поминается и преобразуется в приращение относительной длительности выходных.импульсов, Кроме того, в первом периоде производится определение среднего значения напряжения, действующего на выходе второго повторителя 12, и его функциональное преобразование, которое во втором периоде запоминается. Первый, второй, третий и четвертый ключи 19, 20, 21 и 22 работают в противофазе по сигналам триггера 23, изменяющего свое состояние каждый период широтно-импульсного сигнала от формирователя импульса 24, функциональный состав которого определяется широтно-импульсным модулятором 8. Например, если в широтно-импульсном модуляторе 8 есть сигнал треугольной или пилообразной формы, то формирователь импульсов 24 выполняется в виде компаратора. На управляющие входы первого, второго и третьего элементов с дискретно-управляемой проводимостью 1, 2 и 3, каждый из которых может быть выполнен в виде последовательно соединенных ключа и резистора, поступают сигналы с входов 30, 31 и 32. Выходной сигнал широтно-импульсного .модулятора 8 управляет четвертым и пятым элементами с дискретно-управляемой проводимостью 4 и 5. Средние значения проводимостей пропорциональны относительным длительностям широтно-импульсных сигналов. При этом изменение длительности управляющих широтногимпульсных сигналов приводит к пропорциональному изменению проводимостей первого, второго и третьего плеч моста, что вызывает изменение средних значений напряжений на вторых выводах первого и второго элементов с дискретно;управляемой проводимостью 1 и 2.Эти напряжений соответственно через вто рой повторитель 12, первый фазоинве тор 15 и второй дополнительный масштабирующий резистор 26 и первый по торитель 11 и первый масштабирующий резистор 25 поступают через первый ключ 19 на вход первого интегратора 17. Выходное напряжение первого инте ратора 17 через второй ключ 20, пер вый запоминающий конденсатор 9 и третий повторитель напряжения 13 поступает на вход широтно-импульсного модулятора 8, выходной сигнал которого подается на управляющие вх ды четвертого и пятого элементов с управляемой проводимостью 4 и 5, обеспечивая автоматическое сведение его баланса, т.е. выравнивание средних постоянных составляющих напряжений на вторых выводах первого и второго элементов с дискретно-управляемой проводимостью 1 и 2 При этом на выходе 33 формируется широтно-импульсный сигнал, относит ная продолжительность которого рав(на - ( Л 82 ) где в , ©2 относительные про сигйалов с входов 3 должительности 31, 32. Предположим, что в установившемся режиме в первый период широтноимпульсного сигнала первый и четвертый 19 и 22 замкнуты, а второй и третий ключи 20 и 21 разомкнуты, тогда напряжение на выходе первого интегратора 17 у . J х. i среднее значение напряжения на втором выводе первого элемента с дискретно-управляемой пров од имос тью 1; среднее значение напряжения на втором выводе второго элемента с дискретно-управляемой проводимостью 2; выходное напряжение первого интегратора 17 в мо мент замыкания первого ключа 19; - значения сопротивлений первого и второго .дополнительных масштабирующих резисторов 25 и 26; С - величина емкости конденсатора первого интеграто- тора 17. Напряжение на выходе второго интегратора 18 постоялно, так как третий ключ 21 разомкнут. В конце первого интервала выходное напряжение первого интегратора 17 равно I 9cpt, Udcpi, R25C, где t - время периода широтно-импульсного сигнала. По условиям установившегося режи- . ма средние значения напряжений по выражению (3) равны между собой при условии равенства знаменателей первых двух членов этого напряжения, поэтому выходные напряжения первого интегратора 17 в конце первого интервала и в момент замыкания первого ключа 19 равны. Во втором периоде широтно-импульсного сигнала первый и четвертый ключи 19 и 22 разомкнуты, а второй и третий ключи 20. и 21 замкнуты, а значения выходного широтно-импульсного сигнала в первом и втором тактах равны между собой. Поэтому напряжение на выходе широтно-импульсного модулятора 8 постоянно, т.е. не имеет пульсаций, В переходном процессе предложенное множнтельно-делительное устройство широтно-мсдулированных каналов представляет собой следящую систе1уу, выходное напряжение которой изменяется в эавнсимости 6т изменения входных сигналов согласно формуле (1). В зависимости от выбора величины емкостей конденсаторов, входя- щих в состав первого и второго интеграторов 17 и 18, Может быть получен монотонный или колебательный переходный процесс с временем дости жения установившегося процесса при качкообразном изменении одного из ходных сигналов/ достигакодий нескольо периодов широтно-импульсного игнала. Таким образом, по сравненюо с устойством-прототипом предложенное устойство обладает более высоким быстодействием.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Смолов В.Б | |||

| .и др | |||

| Время-импульсные вычислительные устройства | |||

| Приспособление для контроля движения | 1921 |

|

SU1968A1 |

| рис, 2 | |||

| Мостовое множительно-делительное устройство для широтно- модулированных величин | 1976 |

|

SU579627A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-05-30—Публикация

1983-03-02—Подача