входом блока памяти и с выходом первого сумматора, второй тзкоц которого соединен с вторым выходом блока памяти; третий выход которого соединен с вторым входом второго сумматора, причем второй вход третьего сумматора соединен с четвертым выходом блока памяти, четвертые входы которого являются первыми входами формирователя кодов фазы, вторыми входами .которого являются синхронизирующий вход блока памяти и синхронизирующие входы первого, второго, третьего и четвертого с.умматоров, а выход четвертого сумматора является выходом формирователя кодов фазы.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой адаптивный фильтр | 1990 |

|

SU1837322A1 |

| Устройство для передачи и приема телеметрической информации | 1986 |

|

SU1397956A1 |

| Устройство для цифровой фильтрации на основе дискретного преобразования Фурье | 1990 |

|

SU1795475A1 |

| Радиолиния, защищенная от несанкционированного доступа | 2023 |

|

RU2820855C1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ ДИСКРЕТНОЙ ИНФОРМАЦИИ | 1987 |

|

SU1840226A1 |

| Цифровой синтезатор частотно-модулированных сигналов | 1988 |

|

SU1552345A1 |

| ЦИФРОВОЙ МНОГОФАЗНЫЙ ГЕНЕРАТОР | 1992 |

|

RU2066918C1 |

| РАДИОЛОКАЦИОННЫЙ ПРИЕМНИК С КАНАЛАМИ ВЫСОКОГО РАЗРЕШЕНИЯ | 2007 |

|

RU2344436C1 |

| ПРИЕМНО-ПЕРЕДАЮЩЕЕ УСТРОЙСТВО ДИСКРЕТНЫХ СИГНАЛОВ | 1990 |

|

RU2123761C1 |

| Устройство для временного сжатия входного сигнала | 1982 |

|

SU1100632A1 |

I. ЦИФРОВОЙ ФОРМИРОВАТЕЛЬ СИГНАЛА С ЛИНЕЙНОЙ ЧАСТОТНОЙ МОДУЛЯЦИЕЙ, содержащий блок сопряжения, первые выходы которого соединены с входами блока синхронизации, первые выходы которого подключены к входам блока сопряжения, вторые выходы которого соединены с первыми входами формирователя кодов фазы, вторые входы которого подключены к вторым выходам блока синхронизации, первьп и второй полосовые фильтры, выходы которых соединены с первьми входами соответственно первого и второго умножителей, выходы которых подключены к входам сумматора, выход которого через третий полосовой фильтр подключен к входу третьего умножителя, гетеродин, выход которого соединен с вторым входом второго умножителя и с входом фазовращателя, выход которого подключен к второму входу первого умножителя, отличающийся тем, что, с целью повышения точности фор1 3% tr t Л л ..ЦЛ мирования, введены первый и второй формирователи импульсов, первьй и второй регистры, первый и второй блоки записи и первьй и второй формирователи кода знака, выходы которых подключены к входам соответственно первого и второго блока записи, выходы которых соединены с входами соответственно первого и второго регистров, выходы которых подключены к входам соответственно первого и второго формирователей импульсов, выходы которых соединены с входами соответственно первого и второго полосовых фильтров, причем третьи выходы блока синхронизации подключены к синхронизирующим входам первого и сл второго формирователей кода знака, с к синхронизирующим входам первого и второго блоков записи, к синхронизирующим входам первого и второго регистров и к синхронизирующим входам первого и второго формирователей импульсов, а выход формирователя кодов со со фазы соединен с входами первого и второго формирователей кода знака. 4 2. Цифровой формирователь по п.1, отличающийся тем, что формирователь кодов фазы содержит первьй, второй, третий и четвертый сумматоры и блок памяти, первый выход которого соединен с первым входом первого сумматора и с первым входом второго сумматора, выход которого соединен с первым входом блока памяти и с первым входом третьего сумма-тора, выход которого соединен с вторым входом блока памяти и с первым входом четвертого сумматора, второй вход которого соединен с третьим

1

Изобретение относится к радиотехнике, автоматике и вычислительной технике и может быть использовано для формирования высокостабильных и высокоточных сигналов с перестраиваемыми параметрами.

Известно устройство для формирования сигнала с линейной частотной модуляцией, содержащее дисперсионные ультразвуковые линии задержки, вьшолненные на пьезокристаллах О.

Недостатком устройства является то, что оно не позволяет изменять девиацию частоты.

Наиболее близким техническим решением к изобретению является цифровой формирователь сигнала с линейной частотной модуляцией, содержащий блок сопряжения, первые выходы которого соединены с входами блока синхронизации, первые выходы которого подключены к входам блока сопряжения, вторые выходы которого соединены с первыми входами формирователя кодов фазы, вторые входы которого подключены к вторым выходам блока синхронизации, первьй и второй полосовые фильтры, выходы которых соединены с первмуи , входами соответственно первого и вто,рого умножителей, выходы которых подключены к входам сумматора, выход которого через третий полосовой фильтр подключен к входу третьего умножителя гетеродин, выход которого соединен с вторым входом второго умножителя и с входом фазовращателя, выход которого подключен к второму входу первого умножителя 12 .

Однако известный формирователь обладает недостаточной точностью формирования сигналов.

Цель изобретения - повышение точности формирования.

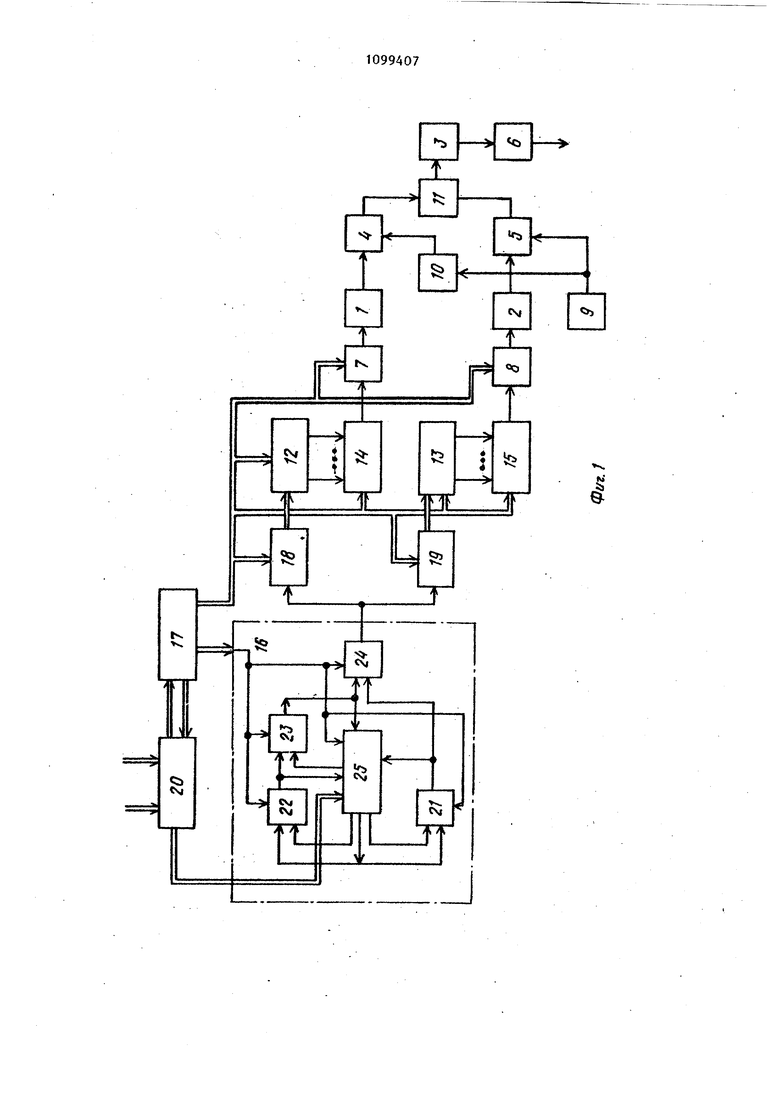

Поставленная цель достигается тем, что. в цифровой формирователь сигнала с линейной частотной модуляцией, содержащий блок сопряжения, первые выходы которого соединены с входами блока синхронизации, первые выходы которого подключены к входам блока сопряжения, вторые выходы которого соединены с первыми входами формирова теля кодов фазы, вторые входы которого подключены к вторым вькодам блока синхронизации, первьй и второй полосовые фильтры, выходы которых соединены с первыми входами соответственно первого и второго умножителей, выходы которых подключены к входам сумматора, выход которого через третий полосовой, фильтр подключен к входу третьего умножителя, гетеродин, выход которого соединен с вторым входом второго умножителя и с входом фазовращателя, выход которого подключен к второму входу первого умножителя, введены первый, и второй. фор -ирователи импульсов, первый и второй регистры, первый и второй блоки записи, первьй и второй формирователи кода знака, выходы которых подключены к входам соответственно первого и второго блоков записи, выходы которых соединены с входами соответственно первого и второго регистров, выходы которых подключены к входам соответственно первого и второго формирователей импульсов, выходы которых соединены с входами соответственно первого и второго полосовых фильтров, причем третьи выходы блока синхронизации подключены к синхронизирующим входам первого и второго формирователей кода знака, к синхронизирующим входам первого и второго блоков записи, к синхронизирующим входам первого и второго регистров и к синхронизирую щим входам первого и второго формир вателей импульсов, а выход формиров теля кодов фазы соединен с входами первого и второго формирователей ко да фазы. При этом формирователь кодов аз содержит первый, второй, третий и четвертый сумматоры и блок памяти, первый выход которого соединены с : первьп входом первого сумматора и с первым входом второго сумматора, вы ход которого соединен с первым вход блока памяти и с первым входом третьего сумматора, выход которого соединен с вторым входом блока памяти и с первым входом четвертого сумматора второй вход которого соединен с тре,тим входом блока памяти и с выходом первого сумматора, второй вход котор го соединен с вторым выходом блока памяти, третий выход которого соединен с вторым входом второго сумматора, причем второй вход третьего сумматора соединен с четвертым выходом блока памяти, четвертые входы которо го являются первыми входами формирователя кодов фазы, вторыми входами которого являются синхронизирующий вход блока памяти и синхронизирующие входы первого, второго, третьего и четвертого сумматоров, а вьсход четвертого является вьсходом формирователя кодов фазы. На фиг. 1 изображена структурная электрическая схема предлагаемого формирователя; на фиг. 2 - временные диаграммы. Цифровой формирователь сигнала с линейной частотой модуляции содержит первьй 1, второй 2 и третий 3 полосовые фильтры, первый 4, второй 5 и третий 6 умножители, первый 7 и .второй 8 формирователи импульсов, гетеродин 9, фазов1ращатель 10, сумматор 11, первый 12 и второй 13 блок записи, первый 14 и второй 15 регист ры, формирователь 16 кодов фазы, блок 17 синхронизации, первый 18 и второй 19 формирователи кода знака, блок 20 сопряжения. Формирователь кода фазы содержит первый 21, второй 22, третий 23 и четвертый 24 сумматоры, блок 25 памяти. Устройство работает следующим образом. До начала формирования импульсов, исходя из требуемых параметров сигнала, определяются частота временной дискретизации F. , число дискретов в импульсе N,константы К1 и К2, определяющие приращения частоты сигнала за интервал дискретизации и начальную частоту соответственно. -Эти данные через блок 20 сопряжения поступают на формирователь 16 кодов фазы и блок 17 синхронизации. Затем в соответствии с программой, заложенной в блоке 17 синхронизации, до начала формирования требуемого выходного импульса в формирователе 16 фазы последовательно формируются все N значений кодов фазы Ч- сигнала с девиацией Д f ц за счет работы трех дискретных накопителей, образованных первым 21, вторым 22 и третьим 23 сумматорами и блоками 25 памяти. « .2т2 кв 2jTf Tt ir+K2i , (1) Г 2 пкв г zTTdf т, V-Nf- Кб, а f - некоторая начальная частота, вводимая на этапе цифрового формирования сигнала. Первое слагаемое образуется на выходе двух последовательно включенных накопителей, образованных сумматорами 22 и 23 и блоком 25 памяти при поаче на вход первого накопителя в каждом такте константы К1. Второе слагаемое образуется на выходе третьего накопителя, образованного сумматором 21 и блоком 25 памяти. При этом на каждом временном такте на вход сумматора 21 третьего накопителя поступает константа К2 и число с выхода этого накопителя в предьдущем такте, которое хранится в общем для трех накопителей блоке 25 памяти. Последовательные коды фазы V- с формирователя 16 кода фазы поступают на формирователи 18 и 19 кода знака, где определяются знаки квадратурных составляющих сигнала (f.(cos4.| , . is ( g. - отсчеты на выходе косинус ного (синусного) квадрату ного канала. . , при прм X 0 Исходный непрерывньй сигнал для косинусного квадратурного канала /ft |2 U(tl cos4(t)co5(т„дискретные по времени выборки из него и , а также отсчеты знака этого g.j. представлены на фиг. 2 «,5 сигнала Последовательные коды знаков g, и g. поступают на входы блоков 12 и 13 записи, с помощью которых устанавливаются начальные коды N последних разрядов регистров 14 и 15,.Число разрядов в регистрах 14 и 15 ,onределяется максимально возможным чис лом временных выборок за длительност импульса при изменении параметров формируемого импульса и частоты временного квантования в заданных пределах. В остальные начальные N -N разрядов . . , ulCIX регистров 14 и 15 заносятся логические нули. По окончании записи начальных кодов во все разряды регистров 14 и 15 .схема готова к работе по формированию заданного сигнала.В момент,соответствующий началу сигнала,от блока 17 синхронизации на регистры 14 и 15 на чинают поступать импульсы сдвига с частотой F,.. Количество импульсов в пачке - N. При этом на выходе послед него разряда регистров 14 и 15 образуется сигнал, соответствующий с точностью до временной дискретизации двоично-квантованному сигналу (фиг.2

и Z..сА sin J I при tj,-fciSto- T 0 при ii ij, и -t tp-t-T . Длительность сигнала на выходах регистров 14 и 15 равна f . Этот сигнал поступает на формирователи 7 и 8 импульсов, состоящие, например, из формирователя двуполярных импульсов, двух ключей и сумматора. Формирователь двуполярных импульсов на каждом такте временного квантования в соответствии с импульсами синхронизации формирует два импульса одинаковой амплитуды положительной и отрицательной полярности, начало которых привязано к моменту временного квантования сигнала, а длительность tr-j; /2. При наличии на управляющем входе ключей с выхода регистра сдвига логической 1 открыт ключ для импульса положительной полярности, при О для отрицательной полярности. Оба ключа работают на общую нагрузку сумматор импульсов, сигнал на выходе которого имеет вид (фиг. 2i) N-t.. . ГС05 ) (Ч Ц a,v .il- rectjn f.f 0 ВЫХ;. , Спектр S,(t) сигнала g. содержит компоненты, соответствующие спектру исходного сигнала Uj, , компоненты, кратные исходному сигналу, и соответствующие сигналам f.L К|27Г + где К - нечетные числа 3, 5, 7 и т.д. до , а также некоторый спектральньй шумовой фон, обусловленный транс формацией спектральных составляющих сигнала . ut I slnFfn -T-JJ («). вьше частоты ® область низших, астот. Этот происходит за счет компонент с . Амплитудный спектр этот симметричен относительно нулевой частоты и повторяется с периодом F, ри выполнении условия f р- f щ, 3 - целая часть а спектры компонент сигнала Ug(,,x.p.CA(5) , соответствующие спектрам tJ,c(4) и (7), не перекрываются, что позволяет вьщелить компоненты, соответствующие спектру исходного сигнала (4), с помощью полосового фильтра. Для того, чтобы шумовой фон, обусловленный тран сформацией частот выше F,, , снизить до малых величин, обеспечивающих необходимый уровень боковых лепестков сжатого сигнала, необходимо выполнение второго условия Г (1Ю) Для упрощения реализации полосовых фильтров 1 и 2 можно использоват периодичность спектра сигнала (2) с периодом . Спектр сигнала (6) отличается от спектра сигнала (2) наличием огибающей периодического спектра вида , которая определяется длительностью импульса выходе формирователя 7(8) импульсов. Если, например, f -. ... , то на часА 2 тотах (2K+1),, компоненты спектра, соответствующие спектру непрерьт кого сигнала Uj., практически не искажены за счет модулирующей функции . Это позволяет настраивать полосовой фильтр 1(2) с полосой Af .Л не на частоту л, более высокую частоту (2K+1) + (f.-x-) и тем самым упростить его техническую реализацию. При fy можно выбрать f е .г . 4f Квадратурные составляющие сигнала на частоте f с девиацией 4f проходят в двух каналах через умножители 4 и 5, в которых взаимодействуют с сигналами гетеродина 9, образуют суммарные и разностные комбинационные частоты. После сумматора 11 сохраняется только сигнал разностной частоты, который дополнительно отфильтровывается от других комбинационных частот и их гармоник полосовым фильтром 3. Умножитель 6 доводит девиацию сигнала U до требуемого значения df.; М Af, где М - коэффициент умножения. Несущая частота сигнала на выходе умножителя 6 равна нес( Таким образом, введение новых блоков позволяет повысить точность формирования сигналов с линейной частотной модуляцией.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Ширман Я.Д | |||

| и др | |||

| Теория и техника обработки радиолокационной информации на фоне помех | |||

| М., Радио и связь, 1981, с | |||

| Говорящий кинематограф | 1920 |

|

SU111A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| ЕЬег L.O., Lonle Н.Н | |||

| Digital generation of wideband LFM waveforms | |||

| IEEE international radar conferetice Arlington, April 1975, p | |||

| Аппарат для передачи фотографических изображений на расстояние | 1920 |

|

SU170A1 |

Авторы

Даты

1984-06-23—Публикация

1982-04-26—Подача