Изобретение относится к цифровой обработке сигналов, в частности цифровой фильтрации, основанной на использовании дискретного преобразования Фурье (ДПФ), и может быть использовано в цифровых ра- диоприемных устройствах для решения задач распознавания сигналов, при оценивании параметров сигнала, при выделении полезных сигналов на фоне помех.

Известно устройство цифровой фильтрации, содержащее формирователь квадратур, зналого-цифровые преобразователи и схему коррекции искажений, вызванных неидеальностью формирователя квадратур. Формирователь квадратур состоит из набора фильтров промех уточной частоты, подключенных через коммутатор к сигнальным . входам двух фазовых детекторов, на выходах которых подключены фильтры нижних чзстот(ФНЧ). В качестве опорных напряжений для фазовых детекторов используются сдвинутые по фазе на л/2 гармонические колебания частоты, равной средней частоте полосы частот входного сигнала. На выходах ФНЧ выделяются синфазная и квадратурная составляющие комплексной огибающей входного сигнала, из которых с помощью аналого-цифровых преобразователей (АЦП)формируются последовательности цифровых отсчетов. Из-за нелинейности, разноканзльности по наклону амплитудных характеристик, а также из-за отклонения разности фаз квадратурных составляющих оттг/2 на выходе формироаа- теля квадратур возникают ложные сигналы, что ограничивает динамический диапазон.

N

ю

:сл

М

;сл

фильтруемого сигнала. Для увеличения динамического диапазона фильтруемых сигналов осуществляется цифровая коррекция амплитудных и фазовых искажений. Для этого в ОЗУ перекодировки и в ОЗУ фазового множителя, входящих в состав схемы коррекции, записываются соответственно корректирующая функция и фазовый множитель..

Недостатки известного устройства обусловлены переносом спектра входного сигнала на нулевую частоту в аналоговой части устройства, что приводит к увеличению искажений за счет дрейфа нуля, нелинейных эффектов и к росту уровня шумов. Кроме того, в процессе эксплуатации устройства из-за дестабилизирующих факторов (изменения температуры, питающих напряжений) записанные заранее значения корректирующей функции и фазового множителя не обеспечат полной коррекции возникающих разбалансов. Все это приводит к ограничению динамического диапазона фильтруемого сигнала и снижает точность цифровой фильтрации.

Прототипом заявляемого устройства является устройство цифровой фильтрации на основе ДПФ, которое содержит генератор тестового сигнала, переключатель, аналоговый формирователь квадратур, включающий два смесителя, гетеродин и фазовра- щатель на п/1, корректирующее устройство, содержащее исполнительный-элемент в виде четырех умножителей и двух сумматоров и преобразователь в виде четырех ключей, четырех регистров и четырех сумматоров, коммутатор; умножитель комплексных чисел, блок памяти, процессор БПФ и цифровой детектор. Возникающие в квадратурных.каналах разбалансы подвергаются коррекции. В качестве датчика разбалансов попутно с основным назначением используется процессор БПФ. сигналы на выходе которого служат исходным материалом, из которого преобразователь корректирующего устройства формирует корректирующие множители для умножителей исполнительного элемента.

В режиме коррекции входы смесителей с помощью переключателя отключаются от входа устройства и соединяются с выходом генератора гармонического тестового сигнала известной частоты &ь + Дат амплитуды АО; После преобразования в смесителях и АЦП тестовые сигналы в квадратурных каналах имеют вид дискретизации следующих выражений:,

X0(t) A0cos( АИД + уъ),

Y0(t) А0(1 + (За) Sin( ДО) t + f0 + ) (1)

где 3а и &р- амплитудный и фазовый разбалансы в квадратурных каналах.

р0 - начальная фаза тестового сигнала. Исполнительный элемент пропускает тестовый сигнал без искажений на вход коммутатора. При установленных единичных коэффициентах, поступающих с выхода бло- ка памяти, умножитель комплексных чисел и процессор БПФ реализуют алгоритм БПФ комплексной выборки (1). В преобразователе из действительной и мнимой частей комплексного сигнала (1) выделяются компоненты на частоте Aw и формируются

корректирующие множители ReFx, ImFy, ReFy, ImFx, где Fx . Fy -yA0(1+ 5a)

В рабочем режиме входы смесителей подключаются к входу устройства. Квадратурные составляющие после коррекции в исполнительном элементе имеют вид дискретизации следующих выражений:

xk(t) x(t) ReFy-y(t) Re FX.

Yk(t) у(0 Im Fx - x (t) I m Fy (2)

0

5

0

Режим коррекции проводится периодически с частотой, за период которой амплитудно-фазовые разбалансы меняются незначительно (обычно от единиц до сотен секунд). Результатом коррекции является отсутствие амплитудно-фазовых разбалансов квадратурных каналов и как следствие, подавление зеркальных гармоник в спектре сигнала, что позволяет увеличить точность цифровой фильтрации и расширить динамический диапазон устройства.

.Прототип обладает следующими недостатками.

1. Ограниченным динамическим диапазоном, что обусловлено формированием комплексного колебания z0(t) x0(t) + jyoCO и переносом его спектра на нулевую частоту аналоговым методом - с помощью двухка- нального синхронного детектирования. При этом в спектре z0(t) присутствуют спектрэль- . ные составляющие, вызванные дрейфом нуля, низкочастотными шумами аналоговых элементов, а также нелинейными продуктами смесителей, попадающими в полосу частот преобразованного колебания. Если Unap - суммарный уровень паразитного сигнала в е 2°(т) то динамический диапазон устройства .D 20lg(A0/Unap) ограничен за счет Unap.

2. Недостаточной помехоустойчивостью фильтрации при обработке сигналов разного вида с различной полосой, что обусловлено отсутствием на входе смесителей набора

5

0

полосовых фильтров, ограничивающих полосу частот обрабатываемого сигнала. Из- за нелинейных эффектов смесителей при воздействии на них даже неперекрывающих по полосе частот совокупности сигналов и помех могут образовываться интермодуляционные помехи, попадающие в полосу полезного сигнала, которые не могут быть отфильтрованы последующей процедурой БПФ.

3. Необходимостью наращивания производительности Veo процессора БПФ при повышении точности цифровой фильтрации (увеличении разрешающей способности цифрового спектрального анализа), что обусловлено следующей взаимосвязью, выражаемой формульной зависимостью

V6o - logrN (оп/с), (3)

I В Г .

где Тв - длительность выборки (интервал наблюдения);

N - число отсчетов в выборке;

г - основание алгоритма;

ПБПФ- число БПФ (в простейшем случае ПБЛФ 1).

С учетом, что Те N/fg, где fg - частота дискретизации, выражение (3) преобразуется к виду

Veo - logr N ( оп/с ) (4)

Увеличение разрешающей способности .цифрового спектрального анализа эквивалентно уменьшению полосы частот Af каждого из фильтров гребенки БПФ. Поскольку Af 1/TB fg/N и увеличение разрешающей способности сопряжено с ростом N, то при fg const производительность Убо должна расти пропорционально logrN при условии функционирования устройства в реальном масштабе времени. В практической ситуации производительность Veo ограничена. Поэтому существует предельное значение AfnpeA, ПРИ котором в устройстве еще обеспечивается режим реального масштаба времени, что соответствует ограничению точности фильтрации. .

4. Невозможностью непрерывной цифровой фильтрации поступающих колебаний в реальном масштабе времени, что обусловлено необходимостью периодически переключать устройство из основного режима фильтрации во вспомогательный режим коррекции.,

5. Усложнением спецпроцессора (СП) БПФ при введении процедуры коррекции.

разбаланса квадратурных каналов, что обусловлено необходимостью оперирования

вместо z0(t) с комплексным колебанием zK(t) xk(t) + jytc(t). разрядность представления слагаемых которого rk по отношению к разрядности представления слагаемых z0(t) rBx, как показано в (4), составляет гк гвх+3. Целью изобретения является повышение точности фильтрации, увеличение помехоустойчивости устройства и обеспечение режима реального масштаба времени.

Это достигается тем, что в устройство для цифровой фильтрации на основе дискретного преобразования Фурье, содержащее переключатель, аналого-цифровой преобразователь, умножитель комплексных чисел, блок памяти, блок быстрого преобразования Фурье и цифровой детектор, причем оход задания .коэффициентов умножителя комплексных чисел подключен к выходу блока памяти, а выходы умножителя комплексных чисел подключены ко входам блока БПФ, выходы которого

подключены ко входам цифрового детектора, выход которого является выходом устройства, согласн9 предлагаемому устройству, введены набор аналоговых полосовых фильтров, цифровой квадратурный

детектор (ЦКД), децмматор отсчетоо. шифратор и генератор тактовых частот, причем первая группа контактов переключатели объединена и подключена ко входу устройства, вторая и третья группы контактов подключены соответственно ко входу и выходу каждого из полосовых фильтров, входящих в набор, четвертая группа контактов объединена и подключена к информационному входу АПЦ, выход которого подключен ко входу

ЦКД, первый и второй выходы ЦКД подключены к первому и второму входам дециматора отсчетов, первый и второй выходы которого подключены соответственно к первому и второму входам умножителя комплексных чисел, третий вход дециматора отсчетов подключен к выходу шифратора, входы которого подключены к шестой группе контактов переключателя, пятая группа контактов которого объединена и имеет г,отенциал логического нуля, тактовые входы АЦП, ЦКД и дециматора отсчетов подключены к первому выходу генератора тактовых частот, второй выход которого подключен к тактовому входу блока 5ПФ, синхронизирующий выход дециматора отсчетов подключен к соответствующим входам умножителя комплексных чисел, блока памяти, блока БПФ и цифрового детектора.

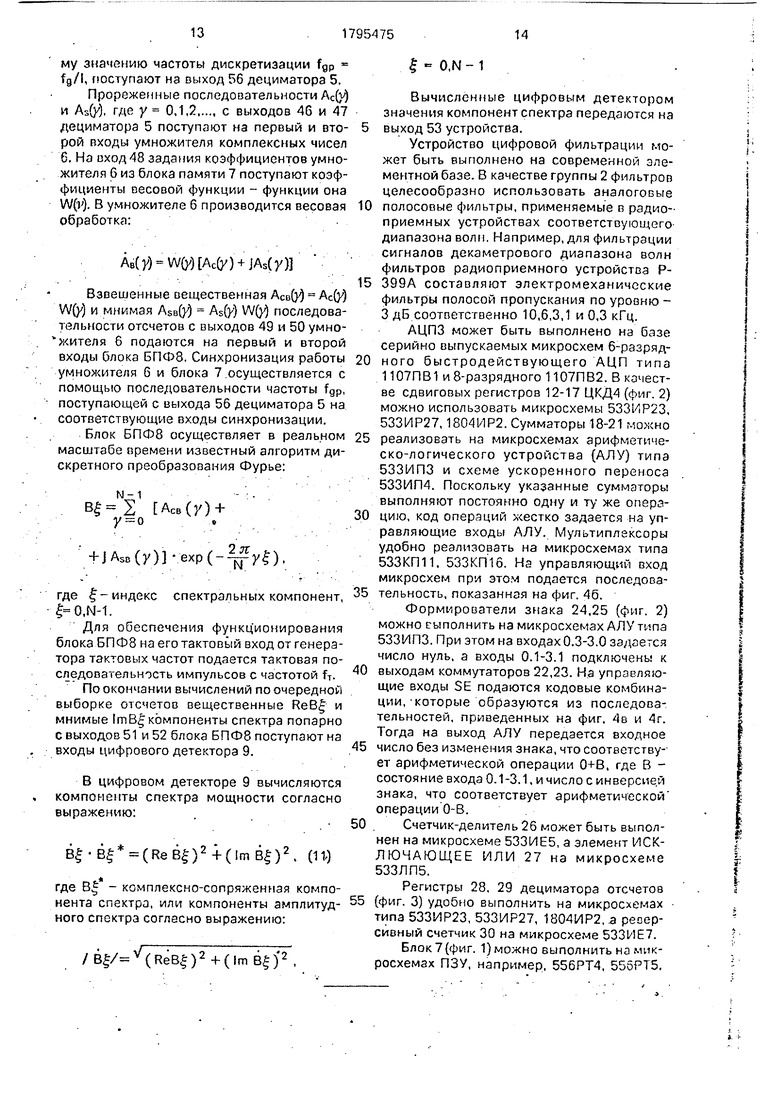

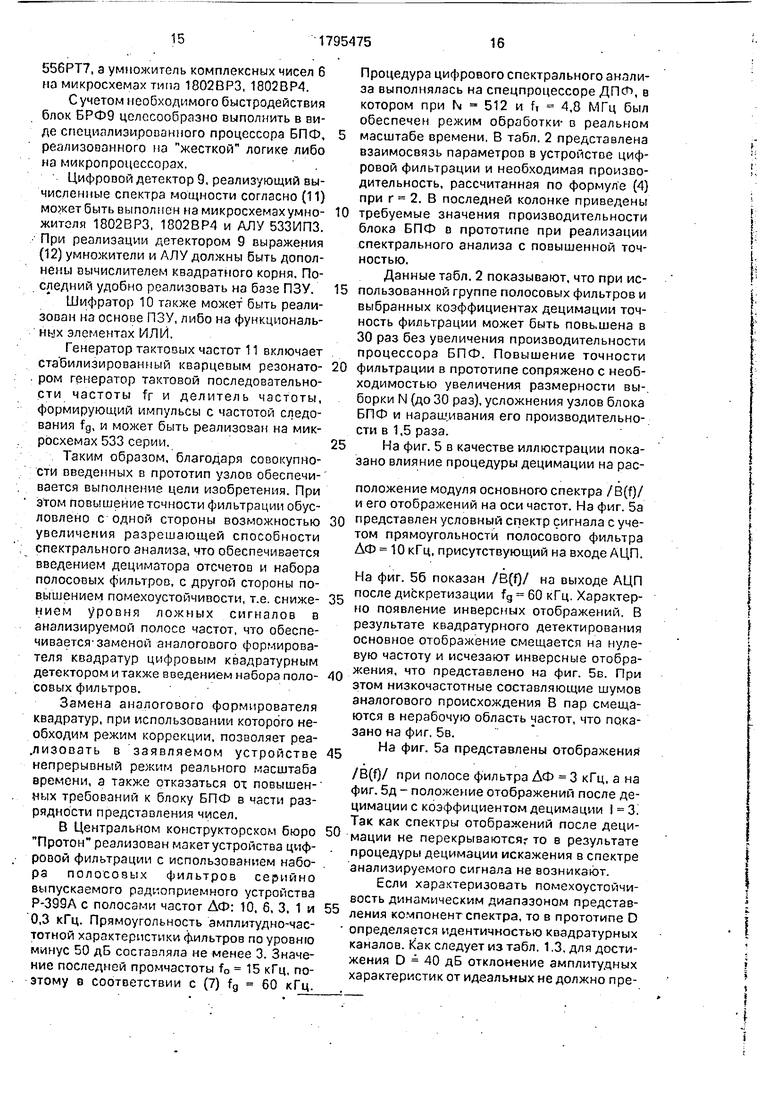

На фиг. 1 представлена структура устройства; на фиг. 2 - один из возможных

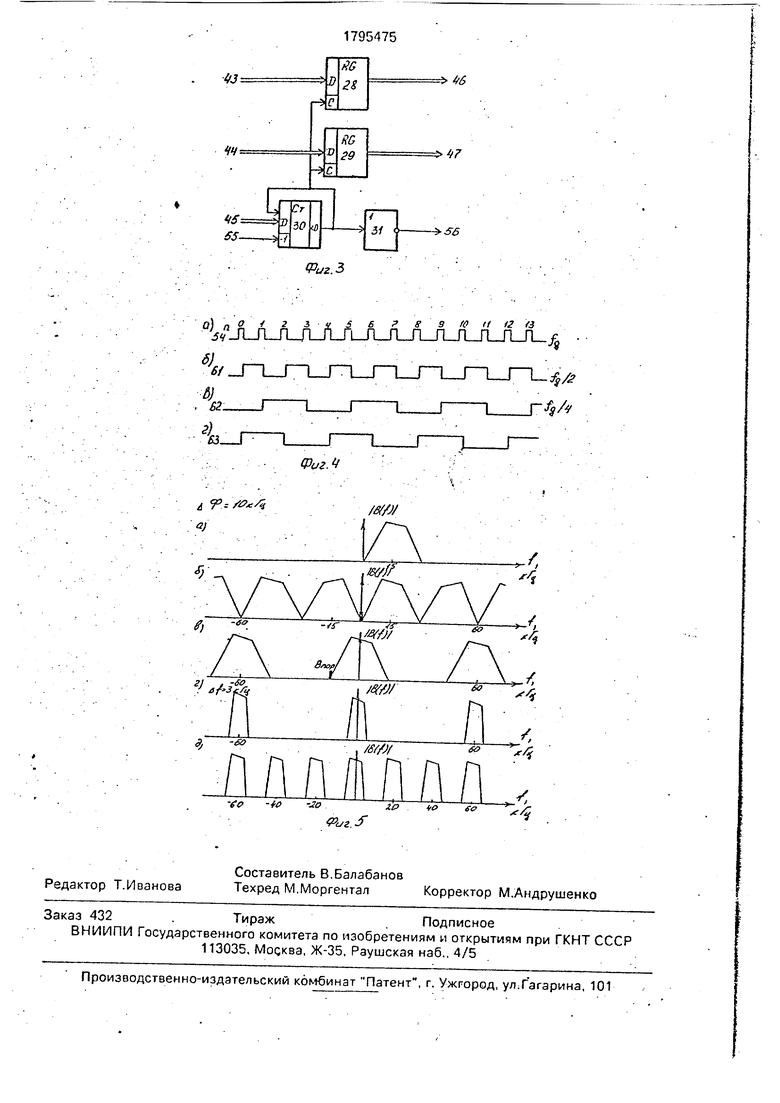

вариантов структуры ЦКД; на фиг. 3 - вариант построения дециматора отсчетов.

Устройство (фиг. 1) содержит переключатель 1, группу аналоговых фильтров 2, анэлого-цифровой преобразователь 3, циф- ровой квадратурный детектор 4, дециматор отсчетов 5, умножитель комплексных чисел G, блок хранения коэффициентов 7, блок быстрого преобразования Фурье 8, цифровой детектор 9, шифратор 10, генератор такто- вых частот 11, первый 12 (фиг. 2), второй 13, третий 14, четвертый 15, пятый 16 и шестой 17 регистры сдвига, первый 18, второй 19, третий 20 и четвертый 21 сумматоры, первый 22 и второй 23 коммутаторы, первый 24 и второй 25 формирователи знака, счетчик- делитель 26, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 27, первый 28 (фиг. 3) и второй 29 регистры, реверсивный счетчик импульсов 30, усилитель-инвертор 31, аналоговый вход 32(фиг. 1)устройства, первая группа контактов 33 переключателя 1а, вторая группа контактов 34 и 35 переключателя 1а, третья группа контактов 36 и 37 переключателя 16, четвертая группа контактов 30 переключа- теля 16, пятая 39 и шестая 40 и 41 группы контактов переключателя 1в, вход 42 ЦКД, первый 43 и второй 44 выходы ЦКД, третий вход 45 дециматора отсчетов, первый 46 и второй 47 выходы дециматора отсчетов, вход задания коэффициентов умножителя комплексных чисел 48, первый 49 и второй 50 выходы умножителя комплексных чисел, первый 51 и второй 52 выходы блока БПФ, выход 53 устройства, тактовый вход 54 ЦКД, тактовый вход 55 дециматорз отсчетов, синхронизирующий выход 56 дециматора отсчетов, выходы второго 57 (фиг. 2), третьего 58, четвертого 59 и шестого СО регистров сдвига, первый 61 и второй 62 выходы счет- чика-делителя, выход 63 схемы ИСКЛЮЧАЮЩЕЕ ИЛИ.

После прохождения соответствующего полосового фильтра из набора 2 сигнал на входе АЦП 3 может быть представлен в еле- дующем виде:

x(t) A(t) f($

Ac(t)cos СгЫ + A5(t)sin cool, (5)

где Ac(t)(t) COSf (tЈ - As{t) A(t) Sin0(t);

А(т) - амплитуда сигнала;

f(i} - фаза сигнала;

OJb - центральная круговая частота;

t - текущее время;

АЈ(г) - синусная квадратурная составющая;

Д t л/2 УО.

Ac(t) - косинусная квадратурная составляющая.

В соответствии с теоремой Когельнико- ва сигнал (5) может быть представлен дискретными отсчетами х (tn) x(n), где tn пД t, п- 1,2,..., если выбрать интервал дискретизации из условия

УО.

At 1/ДР

(6)

Д t л/2 УО.

где Д F - полоса частот, занимаемая сигналом x(t).

Цифровые алгоритмы вычисления квадратурных составляющих сигнала As(n) и Ас(п) и структура цифрового квадратурного детектора известны. Если выбрать интервал дискретизации из условия

(7)

Д t л/2 УО.

то по семи текущим отсчетам сигнала х(п). х(п-1), х(п-2), х(п-З), х(п-4), х(п-5), х(п-б) можно вычислить преобразованный по Гильберту отсчет сигнала, отнесенный к моменту времени (n-З) по формуле

2г(п-3) 1,(п-4) - х(п-2) +

+ 0,(п-6)-х(п)-(8) В четные такты п 2т, т 0,1,2,... значения квадратурных составляющих вычисляются

Ac(2m) (-1)m-x(2m);

Д t л/2 УО.

,m+1

As(2m) (-1)m+l -xr(2m)

(9)

В нечетные такты при п 2гп-И, m 0,1,2,... значения квадратурных составляющих вычисляются в виде

Ac(2m+1) (-i)m- xr (2rnM);

As(2m+1) (-1)m-x(2m-H)(10) Таким образом, при выборе интервала дискретизации в соответствии с выражением (7) нахождение синусной и косинусной квадратурных составляющих сводится к коммутации с соответствующим знаком согласно выражениям (9) и (10) значений оциф- рованных отсчетов сигнала х(п) и вычисленных согласно выражению (8) соответствующих им по времени значений преобразованных по Гильберту отсчетов х((п). При таком способе формирования отсчетов комплексного колебания, когдэ квадратурное детектирование, включающее формирование комплексного колебания и перенос его спектра на нулевую частоту, осуществляется одноканальиой цифровой схемой, отпадает необходимость во введении коррекции. Кроме того, спектральные составляющие, вызванные дрейфом нуля и

низкочастотными шумами аналоговых элементов, смещаются по частотной оси и не попадают в полосу частот комплексной огибаюа1ей A(t) Ac(t) + jAs(t). Отметим, что конкретное соотношение для вычисления хг(п) зависит от свойств сигнала x(t) и требуемой точности преобразования. Приведенное соотношение (8) обеспечивает точность 0,1% в относительной полосе частоты ±17% и 1 % в относительной полосе частот ±30%, что при соответствующем выборе разрядности АЦП может обеспечить динамический диапазон устройства соответственно 60 и АО дБ. Причем ошибка преобразования имеет монотонную зависимость от расстройки. . Таким образом, благодаря наличию г цифрового квадратурного детектора обеспечиваются предпосылки для повышения помехоустойчивости цифровой фильтрации за счет увеличения динамического диапазона устройства и перенесения по частоте в нерабочую область спектральных компонент паразитного сигнала.

Условие (7) выбора интервала дискретизации является более жестким по сравнению с достаточным условием (6) и, кроме того, оно прямо не связано с полосой частот AF сигнала x(t). Как правило, в реальных устройствах (л)0 const, поэтому при уменьшении полосы частот AF сигнала дискретные отсчеты Ас(п) и As(n), следующие через интервал At, выбранный из условия (7), из-, быточно представляют сигнал x(t). При децимации отсчетов - прореживании в I раз, так что приведенный интервал дискретизации составляет Atp |Дг, и при выполнении при этом условия (6) для Atp, точность представления исходного сигнала . x(t), как известно. не ухудшается. Благодаря введению децимации отсчетов при ограничении полосы частот входного сигнала за счет подключения соответствующего полосового фильтра из набора 2 создается возможность увеличения точности цифровой фильтрации без наращивания при этом производительности блока БПФ.

В отличие от прототипа в предлагаемом устройстве число отсчетов в выборке зафиксировано N const, а приведенное значение частоты дискретизации составляет после децимации fgp fg/l. Поэтому необходимая производительность процессора БПФ даже уменьшается согласно выражению (4) при одновременном увеличении разрешающей способности цифрового спектрального анализа Af Afgp/N.

Устройство для цифровой фильтрации на основе ДПФ функционирует следующим образом. В соответствии с видом сигнала

y(t), подлежащим фильтрации, выбирается положение переключателя 1 так. чтобы полоса частот, занимаемая сигналом, была в наибольшей степени согласована с полосой

пропускания одного из фильтров набора 2, Аналоговый сигнал у(с) со входа устройства 32 через первую 33 и вторую 34, 35 группы контактов переключателя 1 поступает на вход выбранного к-го фильтра из групры 2. Ограниченный по полосе в соответствии с амплитудно-частотной характеристикой к-го фильтра сигнал x(t) через третью 36,37 и четвертую 38 группы контактов переключателя 1 поступает на вход

АЦПЗ. Одновременно в соответствии с положением переключателя 1 на входе шифратора 10 присутствует позиционный код, согласно которому на выходе шифратора 10 образуется двоичный код, однозначно определяющий коэффициент децимации отсчетов I.

С помощью АЦПЗ сигнал x(t) представляется кодированными отсчетами х(пД t), n 1,2,..;, следующими через интервал дискретизации At, длительность которого выбрана согласно выражению (7). Соответствующая последовательность импульсов подается на тактовый вхЪд АЦПЗ с первого выхода генератора тактовых частот 11.

Последовательность отсчетов x(nAt) поступает на вход 42 ЦКД4.

Цифровой квадратурный детектор (фиг. 2} содержит последовательно соединенные первый 12, второй 13, третий 14, четвертый

15, пятый 16 и шестой 17 регистры, а также первый 18, второй 19, третий 20 и четвертый 21 сумматоры, коммутаторы 2 2и 23, первый 24 и второй 26 формирователи знака, счетчик-делитель 26 и элемент 27, информационный вход первого регистра 12 подключен

ко входу 42 ЦКД, а также к первому входу

сумматора 19. ко второму входу которого

подключен выход 60 регистра 17, выходы 57

регистра 13 и 59 регистра 15 подключены

соответственно.к первому и второму входам сумматора 18. выход которого подключен к первым входам сумматоров 20 и 21, выход сумматора 19 подключен ко второму входу сумматора 20, выход которого подключен ко

второму входу сумматора 21, выход 58 регистра 14 подключен к первому входу кем му-, татора 22 и второму входу коммутатора 23, выход сумматора 21 подключен ко второму входу коммутатора 22 и к первому зходу

коммутатора 23, выходы коммутаторов 22 и 23 подключены соответственно ко входам формирователя знаков 24 и 25, выходы которых подключены соответственно к выходам 43 и 44, тактовый вход 54 подключен к

тактовым входам регистров с 12 по 17 и к тактовому входу счетчика-делителя 26, пер- пый выход 6 которого подключен к тактовым входам коммутаторов 22 и 23 и к первому входу элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 27, второй выход 62 счетчика-делителя 26 подключен ко второму входу элемента 27 и к управляющему входу формирователя знака 25, а выход 63 элемента 27 подключен к управляющему входу формирователя знака 24. .

Рассмотрим установившийся режим работы ЦКД4. В регистрах сдвига 12-17 записаны значения шести отсчетов АЦПЗ:

-соответственно в регистре 12 - х(п-1), в регистре 13 - х(п-2) и так далее вплоть до регистра 17 - х(п-6). С учетом текущего выходного значения АЦПЗ х(п) вычисление 2хг(п-3) в соответствии с формулой (8) происходит следующим образом. Обозначим для простоты х(п-г) х(т), где т- задержка, ,6.

Выражение (8) эквивалентно представлению

2хг(3) х(4) - х(2) + 0,(4) - х(2) + х(6)-х(0)}.

Вычитание отсчетов х(4) - х(2), образуемых на выходах 59 и 57, производится сумматором 18, а вычитание отсчетов х(6) - х(0) образованных на выходе 60 и входе 42, производится сумматором 19. В сумматоре 20 происходит сложение двух разностей, представленных в фигурных скобках. Передача выходного значения сумматора 20 на вход

сумматора 21 производится со сдвигом на 3 двоичных разряда, что соответствует умножению в . С помощью сумматора 21 вычисляется значение. 2хг(3), которое передается на второй вход коммутатора 22 и первый вход коммутатора 23 со сдвигом на один разряд, что соответствует делению на 2. Одновременно на первый вход коммутатора 22 и второй вход коммутатора 23 с выхода 58 регистра 14 поступает значение х(3).

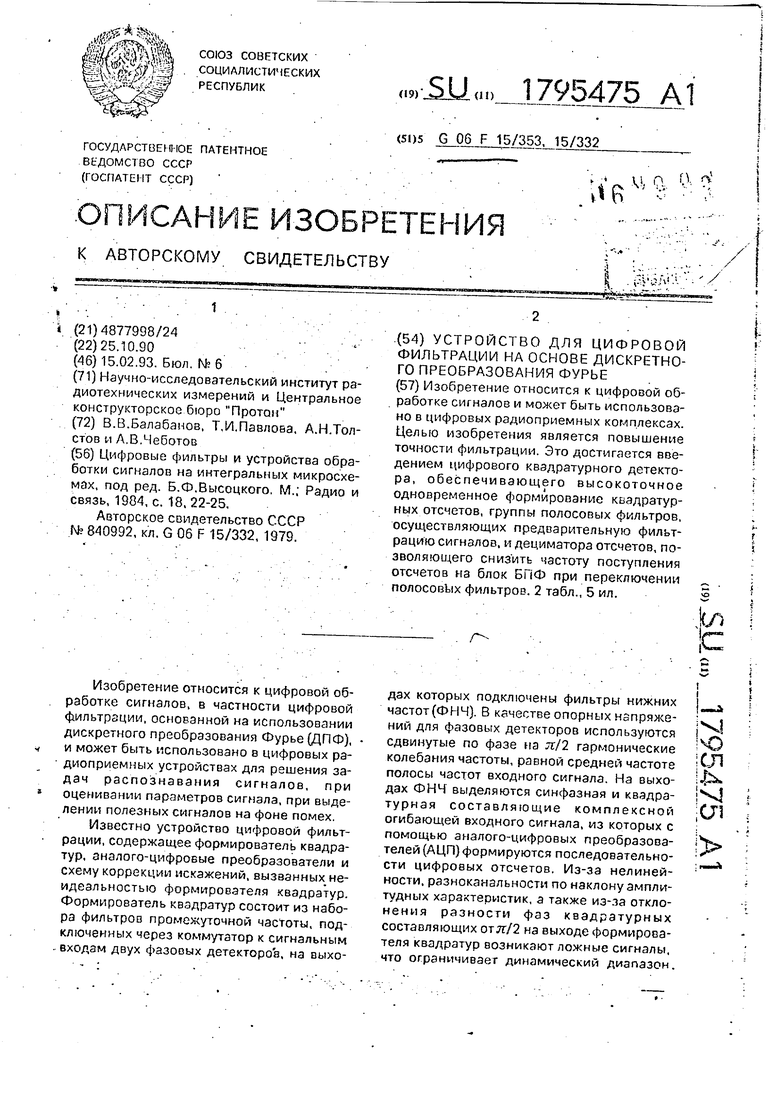

Потактовый сдвиг значений отсчетов х(п). осуществляется с помощью последовательности импульсов частоты fg, поступающих на тактовый вход 54 ЦКД4. На фиг. 4а представлена последовательность импульсов частоты. fg, которая поступает на вход счетчика-делителя 26.-На первом выходе 61 счетчика 26 вырабатывается меандр частоты fg/2, представленный на фиг, 46. Последовательностью импульсов частоты fg/2, подаваемых на тактовые входы коммутаторов 2 и 23, осуществляется управление прохождением отсчетов х(п) и хг(п) па выходы коммутатороа.

0

5

0

5

0

5

0

5

0

5

С выходов коммутаторов 22 и 23 соответствующие значения отсчетов поступают на входы формирователей знака 24 и 25. Управление работой формирователя 25 осуществляется меандровой последовательностью частоты fg/4 - фиг. 4в, формируемой на .втором выходе 62 счетчика-делителя 26 и поступающей на вход управления форрми- рователя 25.

Управляющая последовательность для формирователя знака 24 формируется из последовательностей частоты fg/2 и fg/4 с помощью элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 27. Сформированная последовательность (фиг. 4г) подается с выхода 63 элемента 27 на управляющий вход формирователя 24. В соответствии с управляющими последовательностями формирователями знака осуществляется умножение отсчетов на (-1)171 и (-1)m+1 согласно формулам (9) и (10).

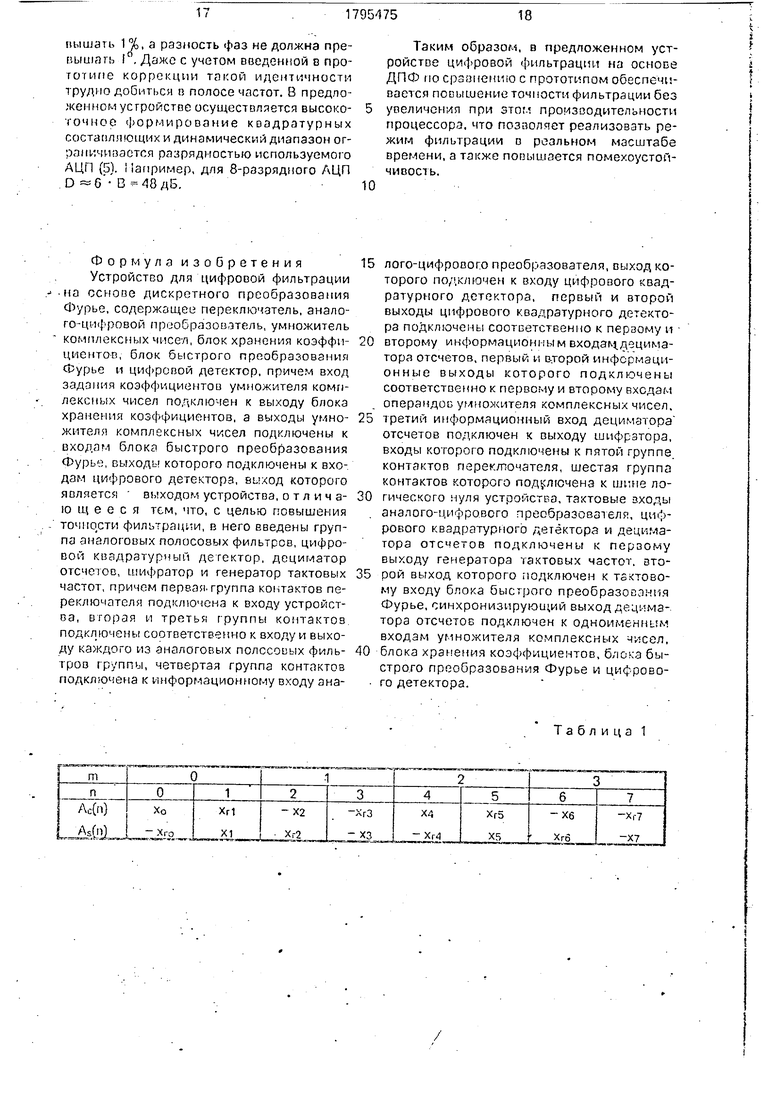

В табл. 1 представлены текущие значения синфазного Ас и квадратурного отсчетов As на выходах 43 и 44 с учетом последовательностей, представленных на фиг, 46,в,г, и нумерации импульсов частоты дискретизации для восьми тактов,

С первого 43 и второго 44 выходов ЦКД 4 отсчеты Ас(п) и As(n) в гемпе, определяемом tg/поступают на первый и второй входы дециматора отсчетов 5 (фиг. 2). Дециматор отсчетов 5 (фиг. 3) содержит перывй 28 и второй 29 регистры, реверсивный счетчик импульсов 30 и усилитель-инвертор 31, D- входы реверсивного счетчика 30 подключены к третьему входу 45 дециматора, вход -1 счетчика 30 подключен к тактовому входу 55 дециматора, выход реверсивного счетчика О подключен к своему входу записи, тактовым входам регистров 28 и 29 и входу усилителя-инвертора 31, выход 56 которого подключен к синхронизирующему выходу дециматора, а выходы регистров 28 и 29 подключены к выходам 46 и 47 дециматора.

На входе 45 дециматора 5 присутствует код децимации, поступающий с выхода шифратора 10. На тактовый вход 55 децима- тора от генератора тактовых частот 11 поступают импульсы частоты fg. Запись отсчетов Ас(п) и As(n) в регистры 28 и 29 осуществляется импульсами, вырабатываемыми на выходе 0 счетчика 30. Эти импульсы образуются, когда число поступивших на вход 55 импульсов частоты fg сравняется с числом, соответствующим коду децимации. Одновременно этими импульсами каждый раз производится перезапись кода децимации в счетчике 30.

Через усилитель-инвертор 31 прореженные импульсы, соответствующие новому значению частоты дискретизации fgp fg/l, поступают на выход 56 дециматора 5. Прореженные последовательности Ас() и As(x). где у 0,1,2...., с выходов 46 и 47 дециматора 5 поступают на первый и второй входы умножителя комплексных чисел 6. На вход 48 задания коэффициентов умножителя 6 из блока памяти 7 поступают коэффициенты весовой функции - функции она W(i ). В умножителе б производится весовая обработка:

AB(y) W(x)Ac(x) + JAs(y)

Взвешенные вещественная АсвЭД Ас(} W(x) и мнимая ASB(} Asfr) W последовательности отсчетов с выходов 49 и 50 умно- жителя 6 подаются на первый и второй входы блока БПФ8. Синхронизация работы умножителя 6 и блока 7 .осуществляется с помощью последовательности частоты fgp, поступающей с выхода 56 дециматора 5 на соответствующие входы синхронизации.

Блок БПФ8 осуществляет в реальном масштабе времени известный алгоритм дискретного преобразования Фурье:

АСВ(У) +

у-о...

4jA(y);:exp(),

где Ј-индекс спектральных компонент, ,N-1.

Для обеспечения функционирования блока БПФ8 на его тактовый вход от генератора тактовых частот подается тактовая последовательность импульсов с частотой fT.

По окончании вычислений по очередной выборке отсчетов вещественные ReBЈ и мнимые lmBЈкомпоненты спектра попарно с выходов 51 и 52 блока БПФ8 поступают на входы цифрового детектора 9.

В цифровом детекторе 9 вычисляются компоненты спектра мощности согласно выражению:

B| BЈ(ReBЈ)2+(lmBЈ)2. (U)

где В| - комплексно-сопряженная компонента спектра, или компоненты амплитудного спектра согласно выражению:

,V

/ (ReBf )2 +(lm BЈ)2 ,

Ј - 0,N - 1

Вычисленные цифровым детектором значения компонент спектра передаются на 5 выход 53 устройства.

Устройство цифровой фильтрации может быть выполнено на современной элементной базе. В качестве группы 2 фильтров целесообразно использовать аналоговые

0 полосовые фильтры, применяемые в радиоприемных устройствах соответствующего диапазона волн. Например, для фильтрации сигналов декаметрового диапазона волн фильтров радиоприемного устройства Р5 399А составляют электромеханические фильтры полосой пропускания по уровню - 3 дБ соответственно 10,6,3,1 и 0,3 кГц.

АЦПЗ может быть выполнено на базе серийно выпускаемых микросхем 6-рззряд0 ного быстродействующего АЦП типа 1107ПВ1 и 8-разрядного 1107ПВ2. В качестве сдвиговых регистров 12-17 ЦКД4 (фиг. 2) можно использовать микросхемы 533ИР23, 533ИР27,1804ИР2. Сумматоры 18-21 можно

5 реализовать на микросхемах арифметиче- ско-логического устройства (АЛУ) типа 533ИПЗ и схеме ускоренного переноса 533ИП4. Поскольку указанные сумматоры выполняют постоянно одну и ту же оперэ0 цию, код операций жестко задается на управляющие входы АЛУ. Мультиплексоры удобно реализовать на микросхемах типа 533КП11, 533КП16. На управляющий вход микросхем при этом подается последова5 тельность, показанная на фиг. 46.

Формирователи знака 24,25 (фиг. 2) можно еыполнить на микросхемах АЛУ типа 533ИПЗ. При этом на входах 0.3-3.0 задается число нуль, а входы 0.1-3.1 подключены к

0 выходам коммутаторов 22,23. На управляющие входы SE подаются кодовые комбинации,-которые образуются из последовательностей, приведенных на фиг. 4в и 4г. Тогда на выход АЛУ передается входное

5 число без изменения знака, что соответствует арифметической операции 0+В, где В - состояние входа 0.1-3.1, и число с инверсией знака, что соответствует арифметической операции О-В..

0 . Счетчик-делитель 26 может быть выполнен на микросхеме 533ИЕ5, а элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 27 на микросхеме 533ЛП5.

Регистры 28, 29 децимзтора отсчетов

5 (фиг. 3) удобно выполнить на микросхемах типа 533ИР23, 533ИР27, 1804ИР2, з реоер- сивный счетчик 30 на микросхеме 533ИЕ7. Блок 7(фиг. 1) можно выполнить на микросхемах ПЗУ, например, 556РТ4, 555РТ5.

1

556РТ7, а умножитель комплексных чисел 6 на микросхемах типа 1802ВРЗ, 1802ВР4.

С учетом необходимого быстродействия блок БРФ9 целесообразно выполнить в виде специализированного процессора БПФ, 5 реализованного на жесткой логике либо на микропроцессорах.

Цифровой детектор 9, реализующий вычисленные спектра мощности согласно (11) может быть выполнен на микросхемах умно- 10 жителя 1802ВРЗ, 1802ВР4 и АЛ У 533ИПЗ. При реализации детектором 9 выражения (12) умножители и АЛУ должны быть дополнены вычислителем квадратного корня. Последний удобно реализовать на базе ПЗУ. 15

Шифратор 10 также может быть реализован на основе ПЗУ, либо на функциональных элементах ИЛИ.

Генератор тактовых частот 11 включает . стабилизированный кварцевым резонато- 20 ром генератор тактовой последовательности частоты fr и делитель частоты, формирующий импульсы с частотой следования fg, и может быть реализован на микросхемах 533 серии.25

Таким образом, благодаря совокупности введенных в прототип узлов обеспечивается выполнение цели изобретения. При этом повышение точности фильтрации обусловлено с одной стороны возможностью 30 увеличения разрешающей способности спектрального анализа, что обеспечивается введением дециматора отсчетов и набора полосовых фильтров, с другой стороны повышением помехоустойчивости, т.е. сниже- 35 нием уровня ложных сигналов в анализируемой полосе частот, что обеспечивается заменой аналогового формирователя квадратур цифровым квадратурным детектором и также введением набора поло- 40 совых фильтров.

Замена аналогового формирователя квадратур, при использовании которого необходим режим коррекции, позволяет реа- лизосать в заявляемом устройстве 45 непрерывный режим реального масштаба времени, а также отказаться от повышен- ных требований к блоку БПФ в части разрядности представления чисел.

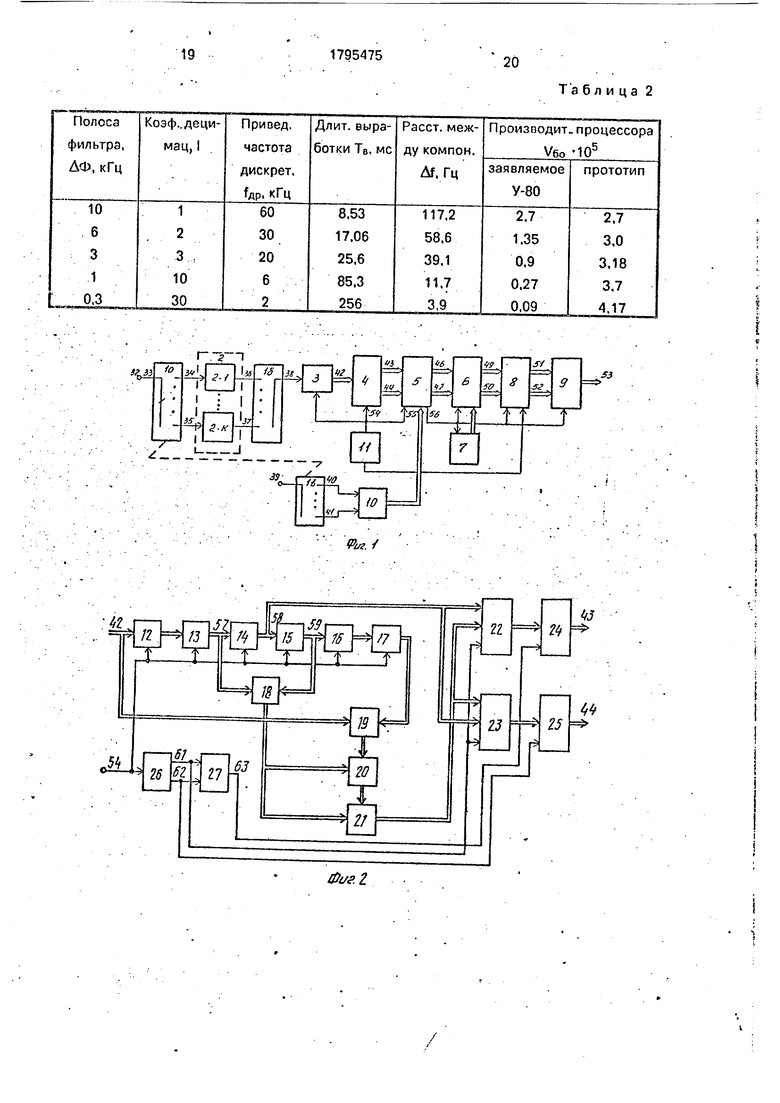

В Центральном конструкторском бюро 50 Протон реализован макет устройства циф- . ровой фильтрации с использованием набора полосовых фильтров серийно выпускаемого радиоприемного устройства Р-399А с полосами частот ДФ: 10. 6, 3. 1 и 55 0,3 кГц. Прямоугольность амплитудно-частотной характеристики ф.ильтров по уровню минус 50 дБ сосгазляла не менее 3. Значение последней промчастоты f0 15 кГц, поэтому в соответствии с (7) fg 60 кГц.

Процедура цифрового спектрального анализа выполнялась на спецпроцессоре ДПФ, в котором при N 512 и fr 4,8 МГц был обеспечен режим обработки- в реальном масштабе времени. В табл. 2 представлена взаимосвязь параметров в устройстве цифровой фильтрации и необходимая производительность, рассчитанная по формуле (4) при г 2. В последней колонке приведены требуемые значения производительности блока БПФ в прототипе при реализации спектрального анализа с повышенной точностью.

Данные табл. 2 показывают, что при использованной группе полосовых фильтров и выбранных коэффициентах децимации точность фильтрации может быть повышена в 30 раз без увеличения производительности процессора БПФ. Повышение точности фильтрации в прототипе сопряжено с необходимостью увеличения размерности выборки N (до 30 раз), усложнения узлов блока БПФ и наращивания его производительности в 1,5 раза.

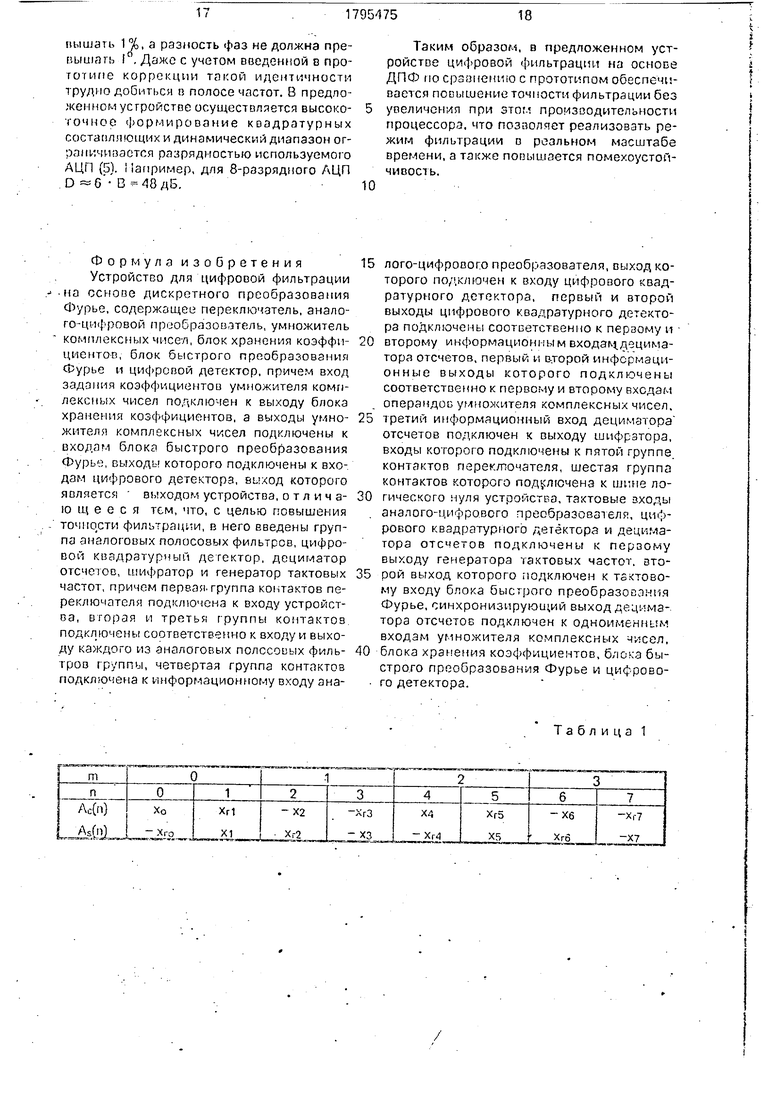

На фиг. 5 в качестве иллюстрации показано влияние процедуры децимации на расположение модуля основного спектра /B(f)/ и его отображений на оси частот. На фиг. 5а представлен условный спектр сигнала с учетом прямоугольности полосового фильтра ДФ 10 кГц, присутствующий на входе АЦП.

На фиг. 56 показан /B(f)/ на выходе АЦП после дискретизации fg 60 кГц. Характерно появление инверсных отображений. В результате квадратурного детектирования основное отображение смещается на нулевую частоту и исчезают инверсные отображения, что представлено на фиг. 5в. При этом низкочастотные составляющие шумов аналогового происхождения В пар смещаются в нерабочую область частот, что показано на фиг. 5в.

На фиг. 5а представлены отображения

/B(f)/ при полосе фильтра ДФ 3 кГц, а на фиг. 5д - положение отображений после децимации с коэффициентом децимации I 3. Так как спектры отображений после децимации не перекрываютсяг то в результате процедуры децимации искажения в спектре анализируемого сигнала не возникают.

Если характеризовать помехоустойчивость динамическим диапазоном представления компонент спектра, то в прототипе D определяется идентичностью квадратурных каналов. Как следует из табл. 1.3, для достижения D 40 дБ отклонение амплитудных характеристик от идеальных не должно пре

пышать 1 %, а разность фаз не должна превышать I . Даже с учетом введенной в прототипе коррекции такой идентичности трудно добиться п полосе частот. В предложенном устройстве осуществляется высокоточное формирование квадратурных составляющих и динамический диапазон ограничивается разрядностью используемого А ЦП (5). апример, для 8-рззрядного ЛЦП D .

Таким образом, в предложенном устройстве цифровой фильтрации на основе ДПФ по сравнению с прототипом обеспечивается повышение точности фильтрации без увеличения при зтом производительности процессора, что позволяет реализовать режим фильтрации о реальном масштабе времени, а также повышается помехоустойчивость.

| название | год | авторы | номер документа |

|---|---|---|---|

| МНОГОКАНАЛЬНЫЙ ПЕРЕПРОГРАММИРУЕМЫЙ ЦИФРОВОЙ ПРИЕМНЫЙ ТРАКТ | 2004 |

|

RU2289202C2 |

| СПОСОБ ФОРМИРОВАНИЯ КВАДРАТУРНЫХ КАНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО РЕАЛИЗАЦИИ (ВАРИАНТЫ) | 1999 |

|

RU2168281C2 |

| Нерекурсивный цифровой фильтрдециматор | 1984 |

|

SU1195420A2 |

| Нерекурсивный цифровой фильтр-дециматор | 1982 |

|

SU1109890A1 |

| Нерекурсивный цифровой фильтр-дециматор | 1986 |

|

SU1354394A1 |

| Устройство формирования и обработки широкополосных сигналов | 2018 |

|

RU2691733C1 |

| Устройство для цифровой фильтрацииНА OCHOBE диСКРЕТНОгО пРЕОбРАзОВА-Ния фуРьЕ | 1979 |

|

SU840922A1 |

| Цифровой квадратурный преобразователь | 1981 |

|

SU1104643A1 |

| Устройство для цифровой фильтрации на основе дискретного преобразования Фурье | 1988 |

|

SU1640710A1 |

| Устройство измерения составляющих вектора путевой скорости | 2019 |

|

RU2715740C1 |

Изобретение относится к цифровой обработке сигналов и может быть использовано в цифровых радиоприемных комплексах. Целью изобретения является повышение точности фильтрации. Это достигается введением цифрового квадратурного детектора, обеспечивающего высокоточное одновременное формирование квадратурных отсчетов, группы полосовых фильтров, осуществляющих предварительную фильтрацию сигналов, и дециматора отсчетов, позволяющего снизить частоту поступления отсчетов на блок БПФ при переключении полосовУх фильтров. 2 табл., 5 ил. . Г .to с

Формула изобретения Устройство для цифровой фильтрации на основе дискретного преобразования Фурье, содержащее переключатель, анало- ro-цифровой преобразователь, умножитель комплексных чисе-л, блок хранения коэффициентов, блок быстрого преобразования Фурье и цифровой детектор, причем вход задания коэффициентов умножителя комплексных чисел подключен к выходу блока хранения коэффициентов, а выходы умножителя комплексных чисел подключены к входам блока быстрого преобразования Фурье, выходы которого подключены к входам цифрового детектора, выход которого является выходом устройства, отличающееся тем, что, с целью повышения точности фильтрации, в него введены группа аналоговых полосовых фильтров, цифровой квадратурный детектор, дециматор отсчетов, шифратор и генератор тактовых частот, причем первая, группа контактов переключателя подключена к входу устройства, вторая и третья группы контактов подключены соответственно к входу и выходу каждого из аналоговых полосовых фильтров группы, четвертая группа контактов подключена к информационному входу аналого-цифрового преобразователя, выход которого подключен к входу цифрового квадратурного детектора, первый и второй выходы цифрового квадратурного детектора подключены соответственно к первому и

второму информационным входандецима- тора отсчетов, первый и второй информационные выходы которого подключены соответственно к первому и второму входам операндов умножителя комплексных чисел.

третий информационный вход децимзтора отсчетов подключен к выходу шифратора, входы которого подключены к пятой группе. контактов переключателя, шестая группа контактов которого подключена к шине логического нуля устройства, тактовые входы аналого-цифро.вого преобразователя, цифрового квадратурного детектора и децима- тора отсчетов подключены к первому выходу генератора тактовых частот, зторой выход которого подключен к тактовому входу блока быстрого преобразования Фурье, синхронизирующий выход децима- тора отсчетов подключен к одноименным входам умножителя комплексных чисел,

блока хранения коэффициентов, блока быстро/о преобразования Фурье и цифрово- го детектора.

Таблица 1

Таблица 2

43

JLjUUJlMAAjULrLAJL 4

Ь6

| Цифровые фильтры и устройства обработки сигналов на интегральных микросхемах, под ред | |||

| Б.Ф.Высоцкого, М.; Радио и связь, 1984, с | |||

| Способ использования делительного аппарата ровничных (чесальных) машин, предназначенных для мериносовой шерсти, с целью переработки на них грубых шерстей | 1921 |

|

SU18A1 |

| Преобразователь угла поворотаВАлА B КОд | 1979 |

|

SU840992A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Видоизменение прибора для получения стереоскопических впечатлений от двух изображений различного масштаба | 1919 |

|

SU54A1 |

Авторы

Даты

1993-02-15—Публикация

1990-10-25—Подача