00 СП

со

Изобретение относится к автоматике и вычислительной технике и может бнлть использовано в системах распознавания и классификации, а также в устройствах технической и медицинской диагностики.5

Известны устройства распознавания сигналов, выполненные на ЭЛТ типа гюлитрон 1 и 2.

Однако в этих устройствах процесс Обучения трудоемок и требует больших Q нременных затрат.

Наиболее близким к предлагаемому lie технической сущности является устройство, содержащее масштабный усилитель, блок управления и интег- |5 раторы, входы которых являются входом устройства, выход масштабного усилителя соединен с-горизонтально отклоняквдими пластинами ЭЛТ типа политрон, а функциональные пластины трубки соединены через формирователи импульсов и интеграторы с входами устройства индикации, выход блока управления соединен с управляющими входами интеграторов, вертикально отклоняющие пластины трубки подключе- 5 ны к источнику смещения 3.

Однако недостатком известного устройства является невозможность прово-, дить автоматически процесс обучения и экзамена, поскольку в нем невозмож-яо но производить сравнение двух функций плотности распределения в автома--тическом режиме , что снижает быстро- действие устройства.

Пелбю изобретения является повыше- ЗЗ ние его быстродействия.

Указанная цель достигается тем, что в устройстве для распознавания сигналов,содержащем функциональный преобразователь, выполненный на эле- 40 Ктронно-лучевой трубке (ЭЛТ)типа политрон , пластины горизонтального отклонения которой подключены к выходу масштабного усилителя, вход которого является входом устройства, пластины вертикального отклонения ЭЛТ соеди- 5 нены с выходом источника смещения, функциональные пластины ЭЛТ подключены к входам формирователей импульсов интеграторы и блок управления, оно содержит три блока ключей, блок па- 50 мяти и последовательно соединенные блок cyN iaTopoB, коммутатор и блок анализа, выходы формирователей импульсов подключены к одним входам коммутатора и первого блока ключей,, дру-ек гие входы которого соединены с первым выходом блока управления, второй выход которого соединен с входами второго блока ключей, выходы которого подключены к одним входам интеграторов , другие входы которых соединены С с выходами первого блока ключей, а выходы - с одними входами третьего блока ключей, другие входы которых подключены к третьему выходу блока управления, а выходы - к входам бло- 5

ка памяти, выходы которого соединены с одними входами блока сумматоров, другие входы которых подключены к выходам интеграторов.

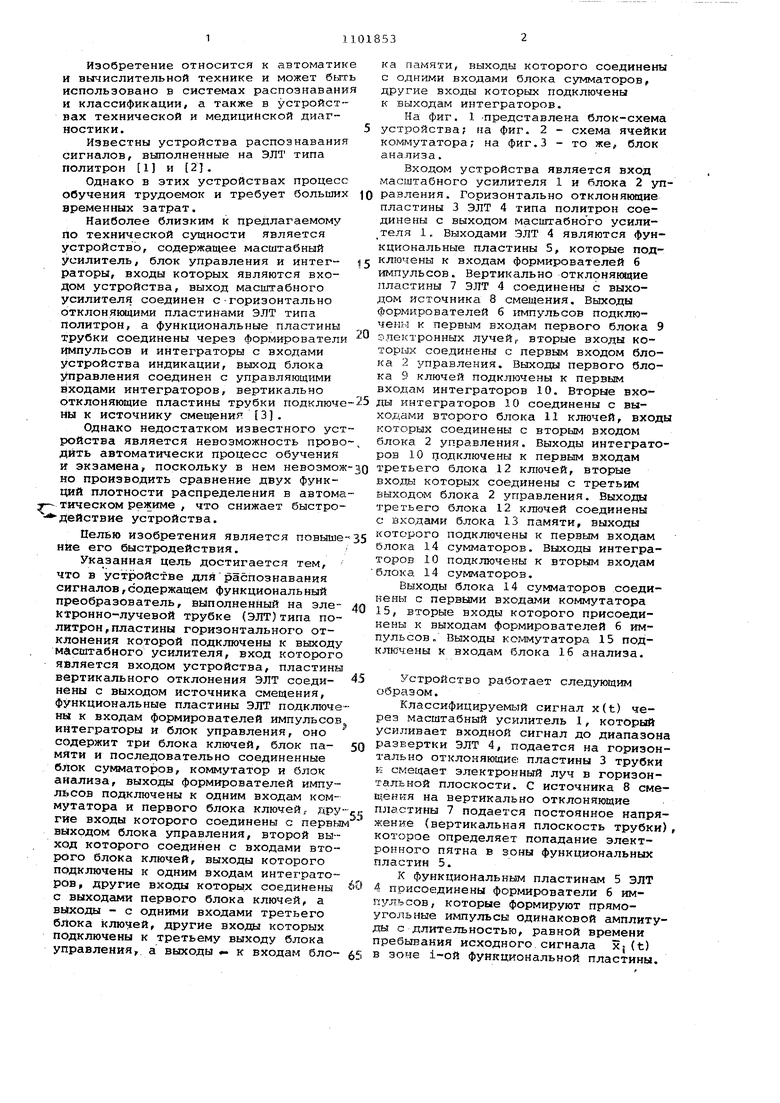

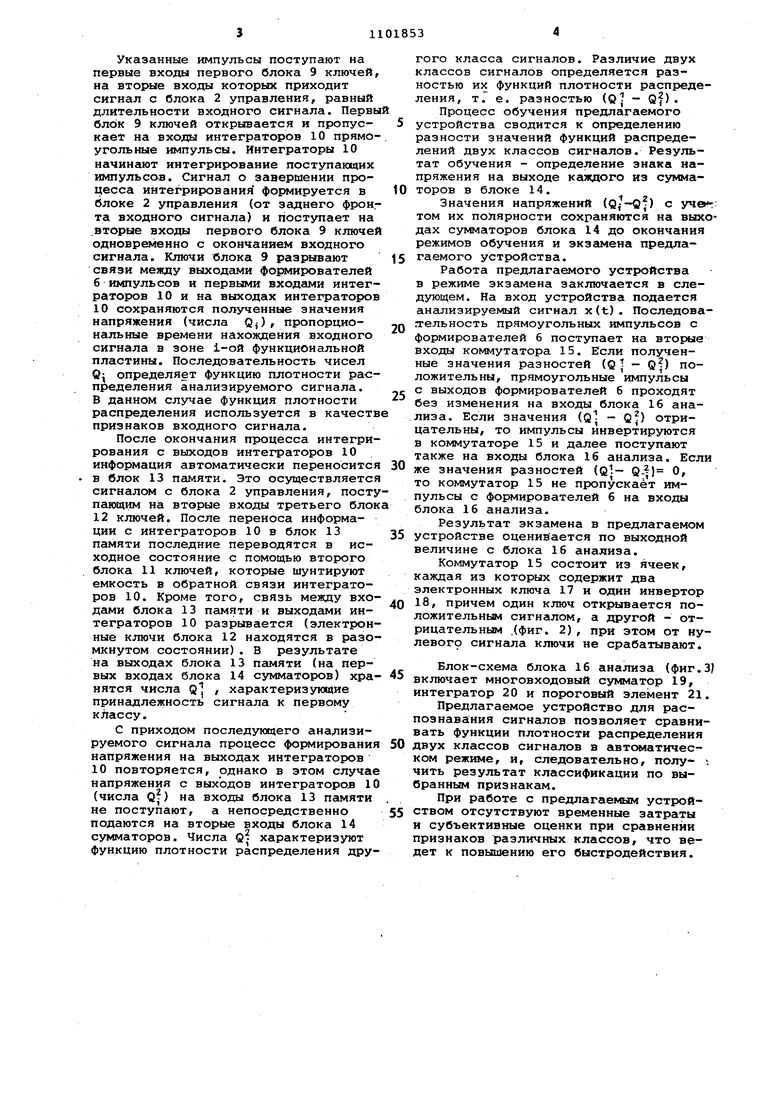

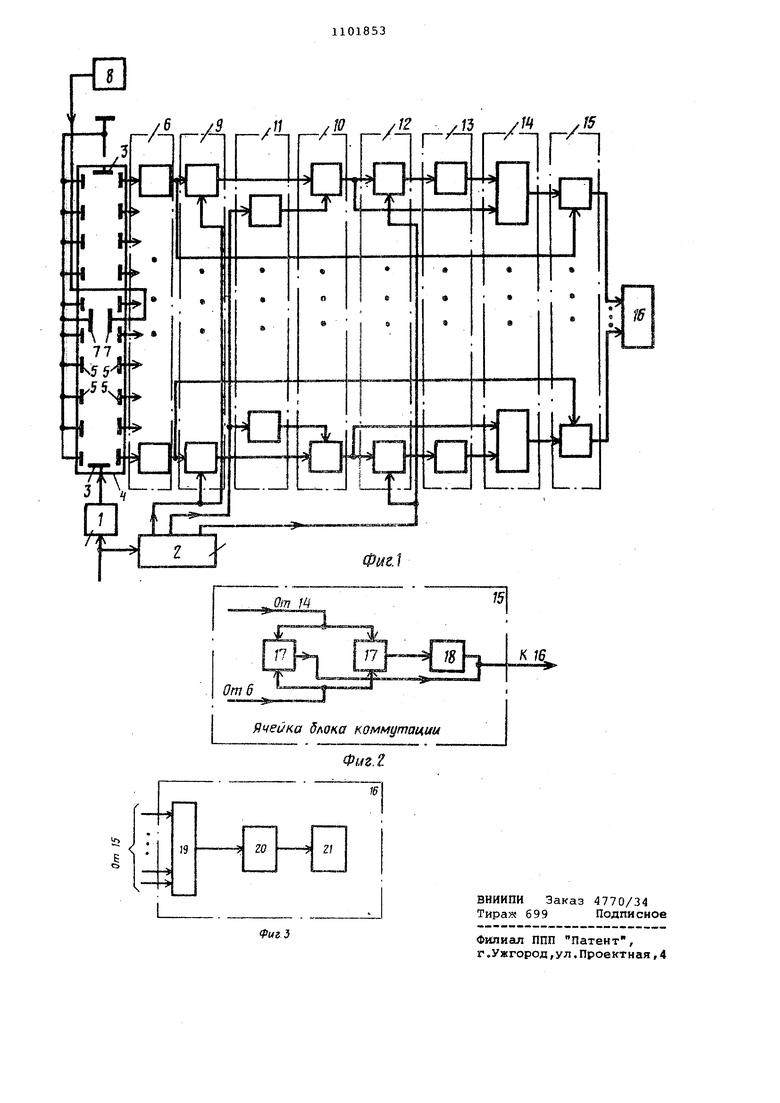

На фиг. 1 -представлена блок-схема устройства; на фиг. 2 - схема ячейки коммутатора; на фиг.З - то же, блок анализа.

Входом устройства является вход масштабного усилителя 1 и блока 2 управления. Горизонтально отклоняющие пластины 3 ЭЛТ 4 типа политрон соединены с выходом масштабного усили теля 1. Выходами ЭЛТ 4 являются функциональные пластины 5, которые подключены к входам формирователей б импульсов. Вертикально отклоняющие пластины 7 ЭЛТ 4 соединены с выходом источника 8 смещения. Выходы формирователей 6 импульсов подключены к первым входам первого блока 9 электронных лучей,, вторые входы которых соединены с первым входом блока 2 управления. Выходы первого блока 9 ключей подключены к первым входам интеграторов 10. Вторые входы интеграторов 10 соединены с выходами второго блока 11 ключей, вход которых соединены с вторым входом блока 2 управления. Выходы интеграторов 10 подключены к первым входам третьего блока 12 ключей, вторые входы которых соединены с третьим выходом блока 2 управления. Выходы третьего блока 12 ключей соединены с входами блока 13 памяти, выходы которого подключены к первым входам блока 14 сумматоров. Выходы интеграторов 10 подключены к вторьгм входам блока 14 сумматоров.

Выходы блока 14 сумматоров соединены с первыми входами коммутатора 15, вторые входы которого присоединены к выходам формирователей б импульсов/ Выходы коммутатора 15 подключены к входам блока 16 анализа.

Устройство работает следующим образом.

Классифицируемый сигнал x(t) через масштабный усилитель 1, который усиливает входной сигнал до диапазон развертки ЭЛТ 4, подается на горизонтально отклоняющие пластины 3 трубки к смещает электронный луч в горизонтальной плоскости. С источника 8 смещения на вертикально отклоняющие пластины 7 подается постоянное напряжение (вертикальная плоскость трубки которое определяет попадание электронного пятна в зоны функциональных пластин 5.

К функциональным пластинам 5 ЭЛТ 4 присоединены формирователи 6 импульсов, которые формируют прямоугольные ш-тульсы одинаковой амплитуды с длительностью, равной времени пребывания исходного сигнала Xj (t) в зоне 1-ой функциональной пластины. Указанные импульсы поступают на первые входы первого блока 9 ключей, на вторые входы которых приходит сигнал с блока 2 управления, равный длительности входного сигнала. Первы блок 9 ключей открывается и пропусKaet на входы интеграторов 10 прямоугольные импульсы. Интеграторы 10 начинают интегрирование поступающих импульсав. Сигнал о завершении процесса интегрирования формируется в блоке 2 управления (от заднего фрон.та входного сигнала) и поступает на вторые входы первого блока 9 ключей одновременно с окончанием входного сигнала. Ключи блока 9 разрывают связи между выходами формирователей б импульсов и первыми входами интеграторов 10 и на выходах интеграторов 10 сохраняются полученные значения напряжения (числа QJ), пропорциональные времени нахождения входного сигнала в зоне 1-ой функциональной пластины. Последовательность чисел Q определяет функцию плотности распределения анализируемого сигнала. В данном случае функция плотности распределения используется в качеств признаков входного сигнала. После окончания процесса интегрирования с выходов интеграторов 10 информация автоматически переносится в блок 13 памяти. Это осуществляетс сигналом с блока 2 управления, посту пающим на вторые входы третьего блок 12 ключей. После переноса информации с интеграторов 10 в блок 13 памяти последние переводятся в исходное состояние с помощью второго блока 11 ключей, которые шунтируют емкость в обратной связи интеграторов 10. Кроме того, связь между вхо дами блока 13 памяти и выходгили ин теграторов 10 разрывается (электрон ные ключи блока 12 находятся в разо мкнутом состоянии). В результате на выходах блока 13 пг1мяти (на первых входах блока 14 сумматоров) хра нятся числа Q , характеризующие принадлежность сигнала к первому классу. С приходом последующего анализируемого сигнала процесс формирования напряжения на выходах интеграторов 10 повторяется, однако в этом случае напряжения с выходов интеграторов 1 (числа Q) на входы блока 13 памяти не поступают, а непосредственно подаются на вторые входы блока 14 сумматоров. Числа Q характеризуют функцию плотности распределения дру гого класса сигналов. Различие двух классов сигналов определяется разностью их функций плотности распределения, т. е. разностью (Qj - Qf). Процесс обучения предлагаемого устройства сводится к определению разности значений функций распределений двух классов сигналов. Результат обучения - определение знака напряжения на выходе кгикдого из сумматоров в блоке 14. Значения напряжений (Q/-в) с том их полярности сохраняются на выходах сумматоров блока 14 до окончания режимов обучения и экзамена предлагаемого устройства. Работа предлагаемого устройства в режиме экзамена заключается в следующем. На вход устройства подается анализируемый сигнал x(t). Последоваггельность прямоугольных импульсов с формирователей б поступает на вторые входы коммутатора 15. Если полученные значения разностей (Q | - Q) положительны, прямоугольные импульсы с выходов формирователей б проходят без изменения на входы блока 16 анализа. Если значения (Q - Q) отрицательны, то импульсы инвертируются в коммутаторе 15 и далее поступают также на входы блока 16 анализа. Если же значения разностей (Ql- Q.) О, то коммутатор 15 не пропускает импульсы с формирователей 6 на входы блока 16 анализа. Результат экзамена в предлагаемом устройстве оценивается по выходной величине с блока 16 анализа. Коммутатор 15 состоит из ячеек, каждая из которых содержит два электронных ключа 17 и один инвертор 18, причем один ключ открывается положительньм сигналом, а другой - отрицательным .(фиг. 2) , при этом от нулевого сигнала ключи не срабатывают. Блок-схема блока 16 анализа (фиг.З) включает многовходовый сумматор 19, интегратор 20 и пороговый элемент 21. Предлагаемое устройство для распознавания сигналов позволяет сравнивать функции плотности распределения двух классов сигналов в автоматическом режиме, и, следовательно, полу- л чить результат классификации по выбранным признакам. При работе с предлагаемым устройством отсутствуют временные затраты и субъективные оценки при сравнении признаков различных классов, что ведет к повышению его быстродействия.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для распознавания сигналов | 1981 |

|

SU1012290A1 |

| Анализатор функций плотности распределения | 1981 |

|

SU987638A1 |

| Анализатор функций плотности распределения | 1978 |

|

SU752354A2 |

| Управляемый вероятностный преобразователь | 1979 |

|

SU868771A1 |

| Устройство для определения характеристик выбросов случайных процессов | 1985 |

|

SU1269160A2 |

| Устройство для классификации случайных процессов | 1984 |

|

SU1251121A1 |

| Анализатор функций плотностиРАСпРЕдЕлЕНия | 1979 |

|

SU813470A1 |

| Устройство для вычисления коэффи-циЕНТОВ РАзлОжЕНия фуНКций B Ряд | 1977 |

|

SU813457A1 |

| Генератор случайного процесса | 1978 |

|

SU781799A1 |

| Анализатор функций плотности распределения | 1981 |

|

SU982026A1 |

УСТРОЙСТВО ДЛЯ РАСПОЗНАВАНИЯ СИГНАЛОВ, содержащее функциональный преобразователь, выполненный на электронно-лучевой трубке (ЭЛТ) типа политрон, пластины горизонтального отклонения которой подключены к выходу масштабного усилителя, вход которого является входом устройства, пластины вертикального отклонения ЭЛТ соединены с выходом источника смещения, функциональные пластины ЭЛТ подключены к входам формирователей импульсов, интеграторы и блок управления, отличающееся тем, что, с целью повышения быстродействия, оно содержит три блока ключей, блок пг№1яти и последовательно соединенные блок сумматоров, коммутатор и блок анализа, выходы формирователей импульсов подключены к одним входам коммутатора и первого блока ключей, другие входы которого соединены с первым выходом блока управления, второй выход которого соединен с входами второго блока .ключей, выходы которого подключены к одним входам интеграторов, другие входы которых соединены с вы- S ходами первого блока ключей, а выходы - с одними входами третьего блока ключей, другие входы которых подключены к третьему выходу блока управления, а выходы - к входам блока памяти, выходы которого соединены i с одними входами блока сумматоров, другие входы которых подключены к выходам интеграторов.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для классификации случайных процессов | 1977 |

|

SU665307A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

Авторы

Даты

1984-07-07—Публикация

1983-04-04—Подача