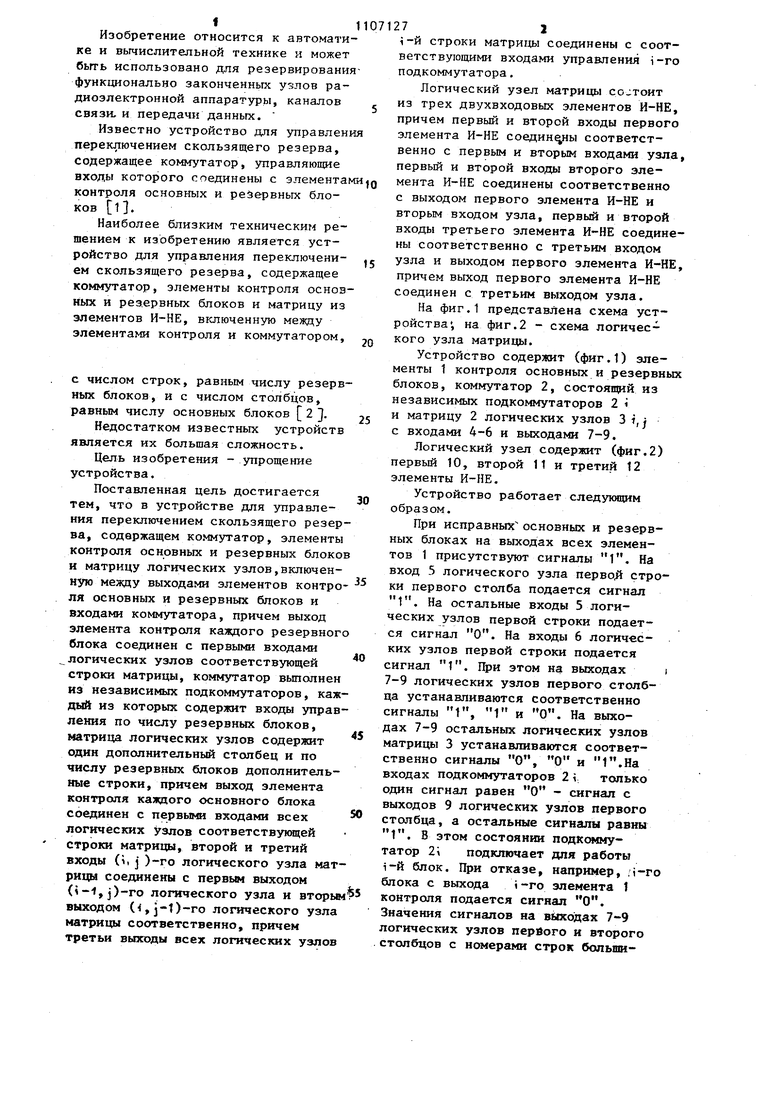

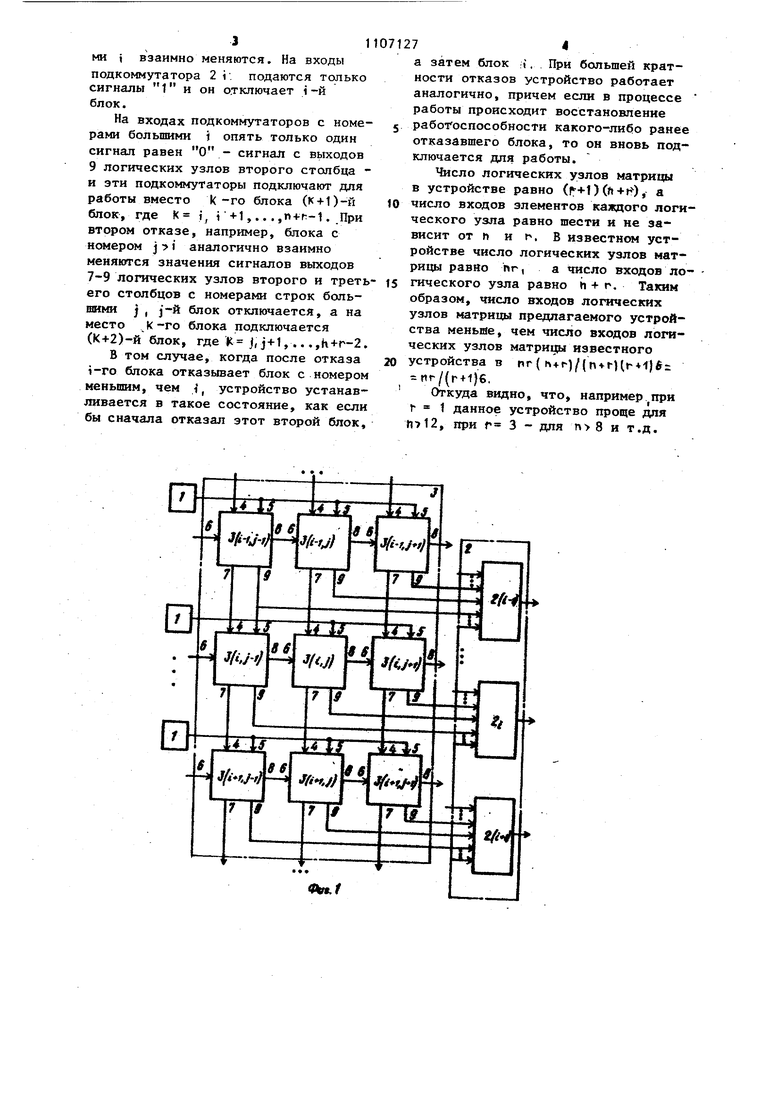

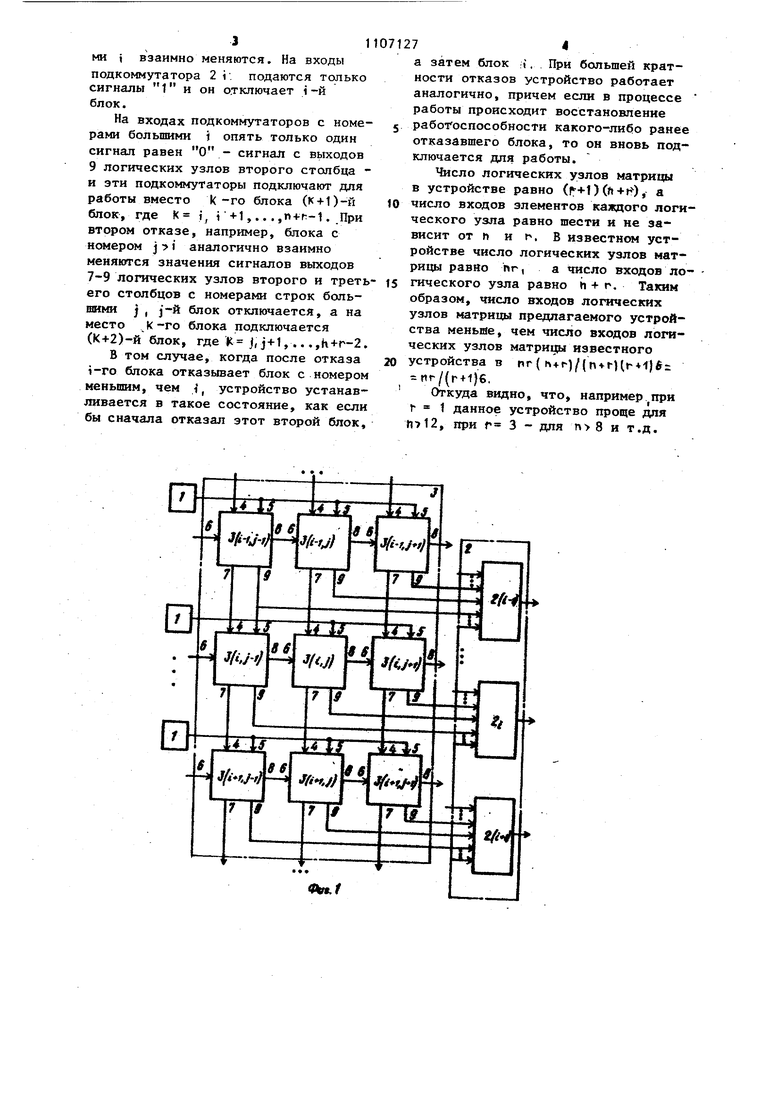

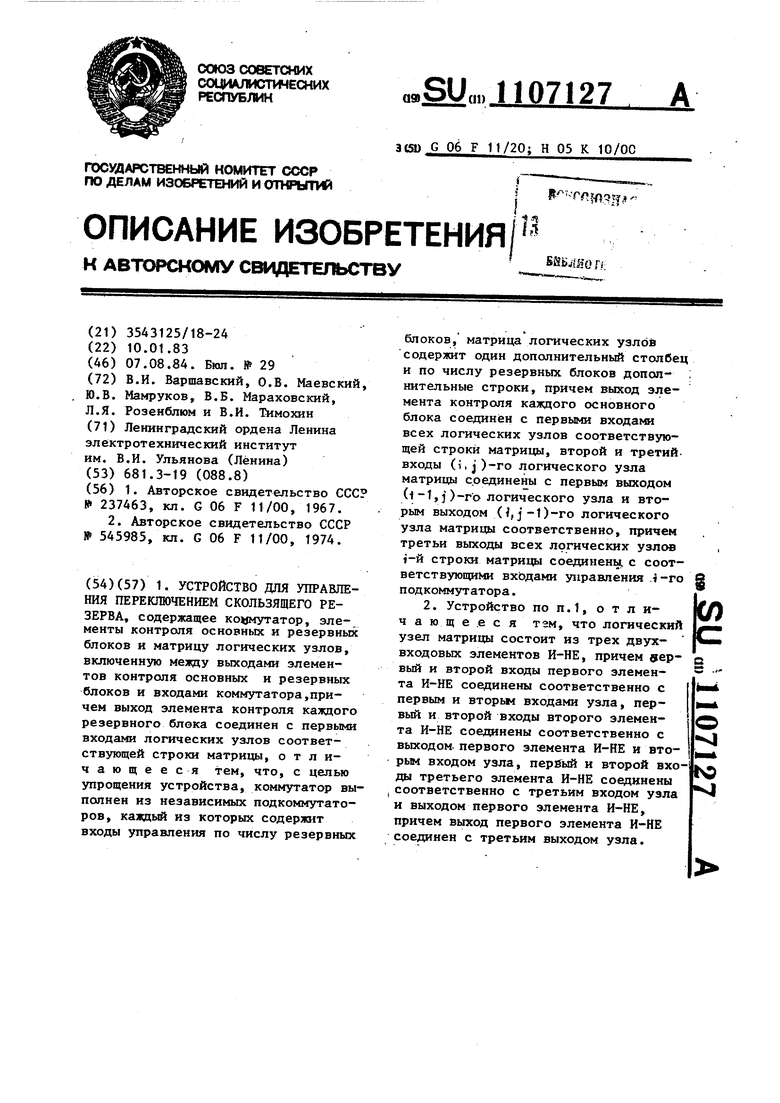

Изобретение относится к автоматике и вьгчислительной технике и может быть использовано для резервирования функционально законченных узлов радиоэлектронной аппаратуры, каналов связи, и передачи данных. Известно устройство для управлени переключением скользящего резерва, содержащее коммутатор, управляющие входы которого соединены с элементам контроля основных и резервных блоков 1 . Наиболее близким техническим решением к изобретению является устройство для управления переключением скользящего резерва, содержащее коммутатор, элементы контроля основ ных и резервных блоков и матрицу из элементов И-НЕ, включенную между элементами контроля и коммутатором, с числом строк, равным числу резерв ных блоков, и с числом столбцов, pasHbiH числу основных блоков 2 J. Недостатком известных устройств является их большая сложность. Цель изобретения - упрощение устройства. Поставленная цель достигается тем, что в устройстве для управления переключением скользящего резер ва, содержащем коммутатор, элементы контроля основных и резервных блоко и матрицу логических узлов.включенную меящу выходами элементов контро ля основных и резервных блоков и входами коммутатора, причем выход элемента контроля каждого резервног блока соединен с первыми входами логических узлов соответствующей строки матрицы, коммутатор вьшолнен из независимых подкоммутаторов, каж дый из которых содержит входы управ ления по числу резервных блоков, матрица логических узлов содержит один дополнительный столбец и по числу резервных блоков дополнительные строки, причем выход элемента контроля каждого основного блока соединен с первьо«1 входами всех логических узлов соответствующей строки матрицы, второй и третий входы (i. )-го логического узла мат рящА соединены с первым выходом (i-l,j)-ro логического узла и вторьм выходом (,j-t)-ro логического узла матрицы соответственно, причем третьи выходы всех логических узлов i-и строки матрихда соединены с соответствующими входами управления i-ro подкоммутатора. Логический узел матрицы состоит из трех двухвходовых элементов И-НЕ, причем первый и второй входы первого элемента И-НЕ соедин ы соответственно с первым и вторым входами узла, первьй и второй входы второго элемента И-НЕ соединены соответственно с выходом первого элемента И-НЕ и вторым входом узла, первый и второй входы третьего элемента И-НЕ соединены соответственно с третьим входом узла и выходом первого элемента И-НЕ, причем выход первого элемента И-НЕ соединен с третьим выходом узла. На фиг.1 представлена схема устройства; на фиг.2 - схема логического узла матрицы. Устройство содержит {фиг.1) элементы 1 контроля основных и резервных блоков, коммутатор 2, состоящий из независимых подкоммутаторов 2 i и матрицу 2 логических узлов 3 t, j с входами 4-6 и выходами 7-9. Логический узел содержит (фиг.2) первый 10, второй 11 и третий 12 элементы И-НЕ. Устройство работает следующим образом. При исправных основных и резервных блоках на выходах всех элементов 1 присутствуют сигналы 1. На вход 5 логического узла nepBO i строки первого столба подается сигнал 1. На остальные входы 5 логических узлов первой строки подается сигнал О. На входы 6 логических узлов первой строки подается игнал 1. При этом на выходах i 7-9 логических узлов первого столбца устанавливаются соответственно сигналы 1, 1 и О. На выхоах 7-9 остальных логических узлов матрицы 3 устанавливаются соответственно сигналы О, О и Г.На входах подкоммутаторов 2 i только один сигнал равен О - сигнал с выходов 9 логических узлов первого столбца, а остальные сигналы равны 1. В этом состоянии подкоммутатор 2i подключает для работы i-Й блок. При отказе, например, м-го блока с выхода i-ro элемента 1 контроля подается сигнал О. Значения сигналов на выходах 7-9 огических узлов первого и второго столбцов с номерами строк большими i взаимно меняются. На входы 2 г. подаются только подкоммутатора он отключает i-и 1 и сигналы блок. На входах подкоммутаторов с номерами большими j опять только один сигнал равен О - сигнал с выходов 9 логических узлов второго столбца и эти подкоммутаторы подключают для работы вместо k -го блока (к+1)-н блок, где К t, i -Hj-.-..При втором отказе, например, блока с номером j i аналогично взаимно меняются значения сигналов выходов 7-9 логических узлов второго и треть его столбцов с номерами строк большими j , j-й блок отключается, а на место К-го блока подключается (К+2)-йблок, где | j,j + 1, ...,h+r-2 В том случае, когда после отказа i-ro блока отказывает блок с номером меньшим, чем i, устройство устанавливается в такое состояние, как если бы сначала отказал этот второй блок 1 затем блок л . При большей кратаности отказов устройство работает аналогично, причем если в процессе работы происходит восстановление работоспособности какого-либо ранее отказавшего блока, то он вновь подключается для работы. Число логических узлов матрицы в устройстве равно (f+l)(ft+f), а число входов элементов каждого логического узла равно шести и не зависит от п и t. В известном устройстве число логических узлов матрицы равно hr, а число входов логического узла равно ii + г. Таким образом, число входов логических узлов матрицы предлагаемого устройства меньше, чем число входов логических узлов матрицы известного устройства в пг ( h+г)/(): пг/(г+1)в, Откуда видно, что, например при г 1 данное устройство проще для , при г 3 - для п 8 и т.д.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления переключением резерва | 1979 |

|

SU930319A1 |

| Устройство для управления переклю-чЕНиЕМ СКОльзящЕгО РЕзЕРВА | 1978 |

|

SU811264A1 |

| Устройство для управления переключением скользящего резерва | 1980 |

|

SU947864A2 |

| Устройство для управления переключением резерва | 1979 |

|

SU877548A1 |

| Устройство управления переключателем скользящего резерва | 1978 |

|

SU746926A1 |

| Устройство для управления подключением резервных блоков | 1980 |

|

SU947865A1 |

| Устройство для управления переключением скользящего резерва | 1977 |

|

SU703816A1 |

| Устройство для управления переключением скользящего резерва | 1974 |

|

SU545985A1 |

| Резервированная измерительная система | 1990 |

|

SU1781682A1 |

| Устройство для управления переключением скользящего резерва | 1978 |

|

SU922746A1 |

1. УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ПЕРЕКЛЮЧЕНИЕМ СКОЛЬЗЯЩЕГО РЕЗЕРВА, содержащее ко|р1утатор, элементы контроля основных и резервных блоков и матрицу логических узлов, включенную мелду выходами элементов контроля основных и резервных блоков и входами коммутатора,причем выход элемента контроля казвдого резервного блока соединен с первыми входами логических узлов соответствующей строки матрицы, о т л и- чающееся тем, что, с целью упрощения устройства, коммутатор выполнен из независимых подкоммутаторов, каждый из которых содержит входы управления по числу резервных блоков, матрица логических узлов содержит один дополнительный столбец и по числу резервных блоков допоп- . нительные строки, причем выход элемента контроля каждого основного блока соединён с первыми вxoдa 0l всех логических узлов соответствующей строки матрицы, второй и третийвходы (i,j)-ro логического узла матрицы соединены с первым выходом d-t,j)-го логического узла и вторым выходом (, j-1)-ro логического узла матрицы соответственно, причем третьи выходы всех логических узлов i-й строки матрицы соединен, с соответствующими вхЬдами управления .t -го подкоммутатора. 2. Устройство по П.1, о т л ичающе.еся тем, что логический узел матрицы состоит из трех двухвходовых элементов И-НЕ, причем «ервый и второй входы первого элемента И-НЕ соединены соответственно с первым и вторьи входами узла, первый и второй входы второго элемента И-НЕ соединены соответственно с выходом- первого элемента И-НЕ и вторым входом узла, и второй входы третьего элемента И-НЕ соединены соответственно с третьим входом узла и выходом первого элемента И-НЕ, причем выход первого элемента И-НЕ соединен с третьим выходом узла.

El

1 и. JdLM rio/,

гТЛТ

ef

J/v-/;

T

6

7 i

фг.Н

Fs;

l

t{t4

O

J

3(i.J

FE

i-ll-i fn

П1

i

ГО

rz

-о7Г

-еФиг.1

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| УСТРОЙСТВО для АВТОМАТИЧЕСКОГО ОБНАРУЖЕНИЯ | 0 |

|

SU237463A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для управления переключением скользящего резерва | 1974 |

|

SU545985A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-08-07—Публикация

1983-01-10—Подача