(54) УСТРОЙС«ГВО УПРАВЛЕНИЯ ПЕРЕКЛЮЧЕНИЕМ РЕЗЕРВА

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство управления переключением резерва | 1988 |

|

SU1617675A1 |

| Устройство для управления переключением резерва | 1979 |

|

SU930319A1 |

| Устройство для управления переключением скользящего резерва | 1978 |

|

SU922746A1 |

| Устройство для управления переключением скользящего резерва | 1980 |

|

SU947864A2 |

| Устройство управления переключателем скользящего резерва | 1978 |

|

SU746926A1 |

| Устройство для управления подключением резервных блоков | 1980 |

|

SU947865A1 |

| Устройство для управления переключением скользящего резерва | 1977 |

|

SU703816A1 |

| Устройство для управления переклю-чЕНиЕМ СКОльзящЕгО РЕзЕРВА | 1978 |

|

SU811264A1 |

| Устройство для управления переключением скользящего резерва | 1974 |

|

SU545985A1 |

| Устройство для управления переключением скользящего резерва | 1983 |

|

SU1107127A1 |

I

Изобретение относится к автоматике и вычислительной технике и может быть использовано для автоматического включения в работу элементов резервирЬванной системы. Резервируемыми- элементами могут быть функционально законченные узлы, блоки аппаратуры, тракты, каналы связи различного назначения и т.п. В автоматизированных системах управления каналы передачи данньк различного назначения можно считать направлениями работы каналов связи, которые в свою очередь являются резервируемы-. ми элементами системы передачи данных. Устройство может быть использовано для подключения более приоритетных абонентов к каналам связи лучшего качества.

Известно устройство для управления переключением скользящего резерва, содержащее коммутатор, соединенный с элементами контроля основных и резервных блоков через матрицу

элементов И-НЕ с числом столбцов, равным числу основных блоков и числом строк, равным числу резервных блоков. Устройство осуществляет включение в работу по данному направлению вместо отказавшего основного блока исправный резервный блок ГО.

Однако устройство не способно при исчерпании резерва включать в работу свободные основные блоки, что приводит к снижению надежности работы резервированной системы.

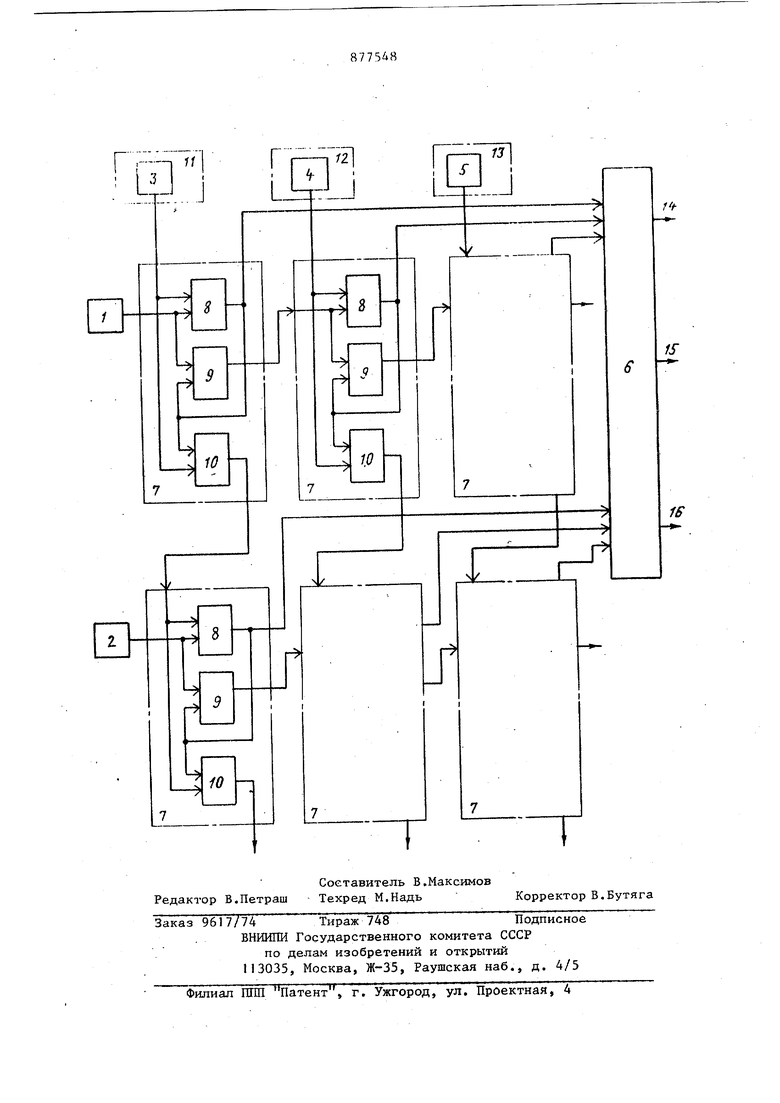

Наиболее близким по технической сущности к предлагаемому является устройство для управления переключением резерва, содержащее элементы управления подключением блоков, элементы контроля блоков, коммутаторы и матрицу логических ячеек с числом строк 1 , равным числу элементов управления подключением блоков и числом столбцов j , равным числу элементов контроля блоков. Каждая логическая ячейка матрицы содержит элемент И-НЕ, выход которого соединен с коммутатором. Выход V-ro элемента упра ления подключением блоков соединен с первым входом элемента И-НЕ логической ячейки -1 -и строки первого столбца матригды, выход j -го элемента контроля блоков соединен со вторым входом элемента .И-НЕ логической ячейки j -го столбца первой строки матрицы. Устройство может быть использовано для автоматического резервирования аппаратуры и способно при исчерпании резерва включать в работу вместо отказавшихся блоков сво бодные основные блоки 2. Недосгатком устройства является то, что оно не обеспечивает достаточ ную надежность резервированной систе мы., так как не способно различать блоки по степени их важности в обеспечении работоспособности системы и в зависимости от степени важности на правлений подключать более приоритет ные блоки для работы по более приоритетным направлениям. Это происходи потому, что номер включаемого в работу направления и номер подключаемо го блока определяются случайными пар метрами: чувствительностью элементов И-НЕ, помехами в соединительных цепя и т.д. Кроме того, в устройстве матрица логических ячеек рассчитана на работу с определенным количеством блоков и направлений и не позволяет увеличить их число, так как в этом случае необходимо вводить в матрицу новые связи и применять элементы И-Н с увеличенным количеством входов. Цель изобретения - повышение надежности и расширение области приме нения устройства. Поставленная цель достигается тем, что в устройстве управления пе .ключением резерва, содержащем элементы управления переключением блоков, элементы контроля блоков,коммутатор и матрицу логических ячеек числом строк, равным числу элементо управления подключением блоков, и числом столбцов, равным числу элеме тов контроля блоков, причем каждая ; логическая ячейка матрицы содержит элемент И-НЕ, выход которого соединен с коммутатором, выход -1 -го элемента управления подключением блоко соединен с первым входом элемента И-НЕ логической ячейки i -и строки первого столбца матрицы, выход j-го элемента контроля блоков соединен со вторым входом элемента И-НЕ логической ячейки j-ro столбца первой строки матрицы, каждая логическая ячейка матриць содержит два элемента И, первые входы которых соединены с выходом элемента И-НЕ, второй вход . первого элемента И соединен с первым входом элемента И-НЕ, второй вход которого соединен со вторым входом второго элемента И, выход первого элемента И (I, J)-й логической ячейки соединен с первым входом элемента И-НЕ следующей логической ячейки той же строки матрицы, выход второго элемента И (I, j)-илогической ячейки соединен со вторым входом элемента И-НЕ следующей логической ячейки того же столбца матрицы. На чертеже приведена блок-схема устройства для переключения резерва. Устройство содержит элементы 1 и 2 управления подключением блоков, элементы 3-5 контроля блоков, коммутатор 6 матрицы из логических ячеек 7, элементы И-НЕ 8, первый и второй элементы И 9 и 10 направления работы каналов 11-13, входы 14-16 резервируемых блоков. Элементы 1 и 2 управления осуществляют подключение блоков по направлениям 11-13. Элементы 3-5 контроля контролируют соответственно состояние блоков по входам 14-16. Показанные на чертеже направления 11-13 не входят в состав устройства и приведены лишь для пояснения принципа заявляемого устройства. Устройство работает следующим об разом. Назначим следующую приоритетность блоков и направлений: направление 1I более Приоритетно, чем направление 12, блок по входу 14 более приоритетен, чем блок по входу 15, который, в свою очередь, более приоритетен, чем блок по входу 16. При отсутствии требований на включение блоков в работу (исходное состояние) с выхода каждого элемента 1 и 2 управления сигналы логического О поступают на. первые входы элементов И-НЕ 8 соответствующих сигналов логических ячеек 7 первого столбца матрицы. ЕСЛИ все блоки исправны, то от каждого элемента 3-5 контроля поступает сигнал логической 1 на второй BXCW элемента И-НЕ 8 соответствующей-логической ячейки 7 первой строки матрицы. В этом случае на выходах всех элементов И-FIE 8 присут-г ствуют сигналы логической 1, которые поступают на вторые входы элементов И 9 и 10 в своих логических ячейках 7 и на коммутатор 6. На выхо дах всех первых элементов И 9 присут ствуют сигналы логического О, а на выходах всех вторых элементов И 10 сигналы логической 1. При появлении на выходе элемента 1 управления сигнала логической 1 (Запрос) и при наличии на втором входе элемента И-НЕ 8 сигнала логической 1 (Блок исправен)-на выхо де последнего появляется сигнал логического О, который поступает на коммутатор 6 и на первые входы элементов И 9. и 10 этой же логической ячейки 7. По этому сигналу исполнительное устройство коммутатора 6 включает в работу наиболее приоритетный блок по входу 14 по направлению 11, На выходе элементов И 9 и 10 первой логической ячейки 7 первой строки матрицы появляется сигнал логического О. С выхода первого элемента И 9 этот сигнал поступает одновременно на первый вход элемента И-НЕ 8 и на второй вход первого элемента И 9 второй логической ячейки 7 первой строки матрицы, далее через первый элемент И 9 второй логической ячейки 7 на первый вход элемента И-НЕ 8 третьей логической ячейки 7 и т.д. Сигнал логического О, поступа ющий на первые входы элементов И-НЕ 8 логических ячеек 7 мен.ее приоритет ных блоков, в данном случае блоков по входам 15 и 16, залрещает подключение их в работу по данному направлению 1J . С выхода второго элемента И 10 первой логической ячейки 7 первой строки матрицы сигнал логического О поступает на второй вход элемента- И-НЕ 8 менее приоритетного направления J2, т.е. на вторую логическую ячейку 7 первого столбца матрицы. Это приводит к запрету подключения более приоритетного блока по входу 4 в работу по менее приоритет ному направлению 12. На выходах элементов И 10 второй и третьей логичес ких ячеек 7 первой строки матрицы пр этом присутствуют сигналы логической J, которые поступают на вторые вхо ды элементов И-НЕ 8 соответственно второй и третьей логических ячеек 7 второй строки матрицы. Этот сигнал р решает подключение в работу свободных и .исправных блоков по входам 15 и 16 по менее приоритетному направлению, в данном случае направлению 12. При появлении на выходе элемента 2 управления сигнала логической 1 (Запрос) этот сигнал поступает иа первый вход элемента И-НЕ 8 второй логической ячейки 7 первого столбца матрИ15 1. Так как на втором входе элемента И-НЕ 8 данной логической ячейки 7 присутствует сигнал логического О, иа его выходе будет сигнал логической 1, который поступает на первый вход первого элемента И 9 данной логической ячейки 7. Вследствие этого сигнал логической 1 с элемеита 2 управления поступает на первый вход элемента И-НЕ 8 следующей в этой строке логической ячейки 7, Так как иа втором входе элемеита ИгНЕ 8 этой логической ячейки 7 присутствует сигнал логической 1, то на выходе элемеита И-НЕ 8 второй логической ячейки 7 второй матрицы появляется сигнал логического О, который поступает иа коммутатор 6, По этому сигналу исполнительное устройство коммутатора 6 включает в работу блок по входу J5 по направлению 12. Одновременно сигнал логического О с выхода элемента И-НЕ 8 второй логической ячейки 7 второй строки матрицы поступает на второй вход первого элемента И 9 данной логической ячейки 7, что запрещает прохождение сигнала Запрос в третью логическую ячейку 7 второй строки матрицы. При выходе из строя блока, подключенного к какому-либо из направлений (в данном случае к направлениям 11 и 12), на второй вход элемента И-НЕ 8 соответствующей логической ячейки 7 первой строки матрицы поступает сигнал логического О (Авария блока). При этом с помощью соединений между логическими ячейками 7 соответствующей данному направлению строки матрицы происходит автоматическое подключение в рая боту по этому направлению исправного менее приоритетного блока, незанятого в более приоритетном направлении (в данном случае блока по входу 16). Если этот исправный блок по входу 16 занят в менее приоритетном направлении, то он освобождается из работы и подключается в работу по более приоритетному направлению. При

этом по менее приоритетному напрае лению включается в,работу свободный и исправный блок, имеющий меньший приоритет, чем блок,переключенный на более приоритетное направление.

Аналогичное переключение происходит при поступлении сигналов логического О (Авария направления) от любого из элементов I и 2 управления, т.е. при выходе иэ строя одного из направлений 11 и 12.

Устройство позволяет, не меняя внутренних связей, путем простого добавления однотипных логических ячеек к матрице или соединением нескольких матриц логических ячеек увеличить количество обслуживаемых блоков и направлений. Для этого дополни- те льлые логические ячейки для новых блоков (новых столбцов матриц) подключаются к выходам первых элементов И последнего столбца матрицы, а дополнительные, логические ячейки для новых направлений (новых строк мат-. рицы) - к выходам вторых элементов И последней строки матрицы.

Таким образом, благодаря тому, что предлагаемое устройство для упраления переключением резерва позволяет подключать к более приоритетному направлению более приоритетный исправный блок и автоматически поддерживать данный режим подключения блоков в процессе работы, повьшается надежность работы резервированной системы, а внутренняя структура логических ячеек расширяет эксплуатациойные возможности устройства, так как позволяет использовать предлагаемое устройство для резервированных систем с неограниченным числом блоков и направлений.

Формула изобретения

Устройство управления переключением резерва, содержащее элементы

управления переключением блоков, элементы контроля блоков, коммутатор и матрицу логических ячеек с числом строк, равным числу элементов управления подключением блоков, и числом столбцовi равным числу элементов контроля блоков, каждая логическая ячейка матрицы содерлсит элемент И-НЕ, выход которого соединен с коммутатором,

выход -го элемента управления подключением блоков соединен с первым входом элемента И-НЕ логической ячейки 1 -и строки первого столбца матрицы, выход j -го элемента контроля блоков

соединен с вторим входом элемента И-НЕ логической ячейки j -го столбца первой строки матрицы, отличающееся тем, что, с целью повышения надежности и расширения области применения устройства, в немкаждая логическая ячейка содержит два элемента И, первые входы которых соединены с вьгходом элемента И-НЕ, второй вход первого элемента И соединен с

первым входом элемента И-НЕ, второй вход которого соединен с- вторым входом второго элемента И, выход первого элемента И (I, j)-й логической ячейки соединен с первым входом элёМента И-НЕ следующей логической ячейки той же строки матрицы, выход второго элемента И (, j)-й логической ячейки, соединен с вторым входом элемента И-НЕ следующей логической ячейки того же столбца.

Источники, информации, принятые во внимание при экспертизе

...Авторское свидетельство СССР № 703816, кл. G 06 F 11/00, 1977 (прототип),

Авторы

Даты

1981-10-30—Публикация

1979-12-29—Подача