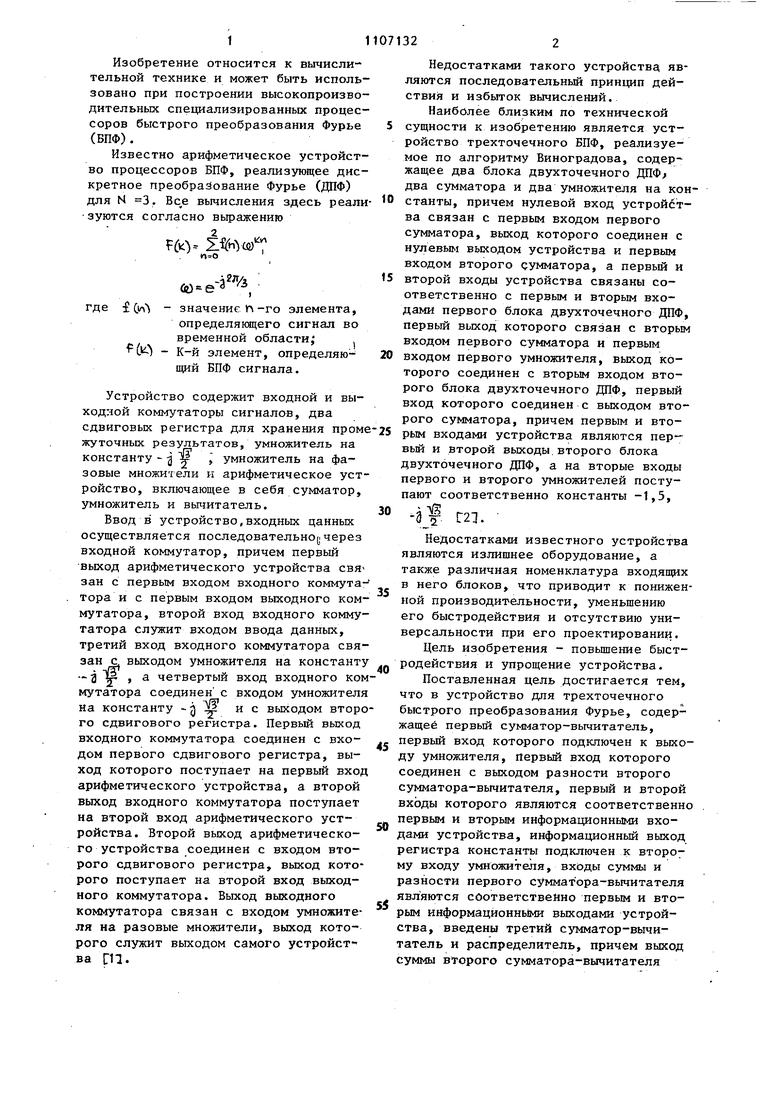

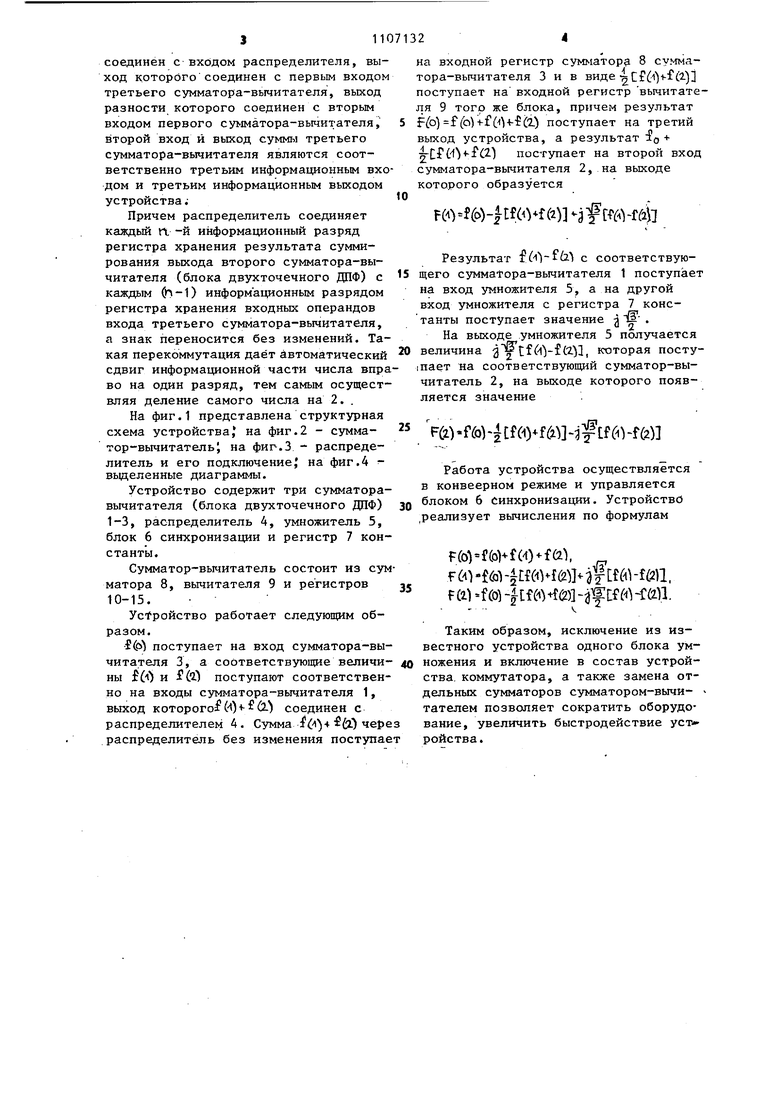

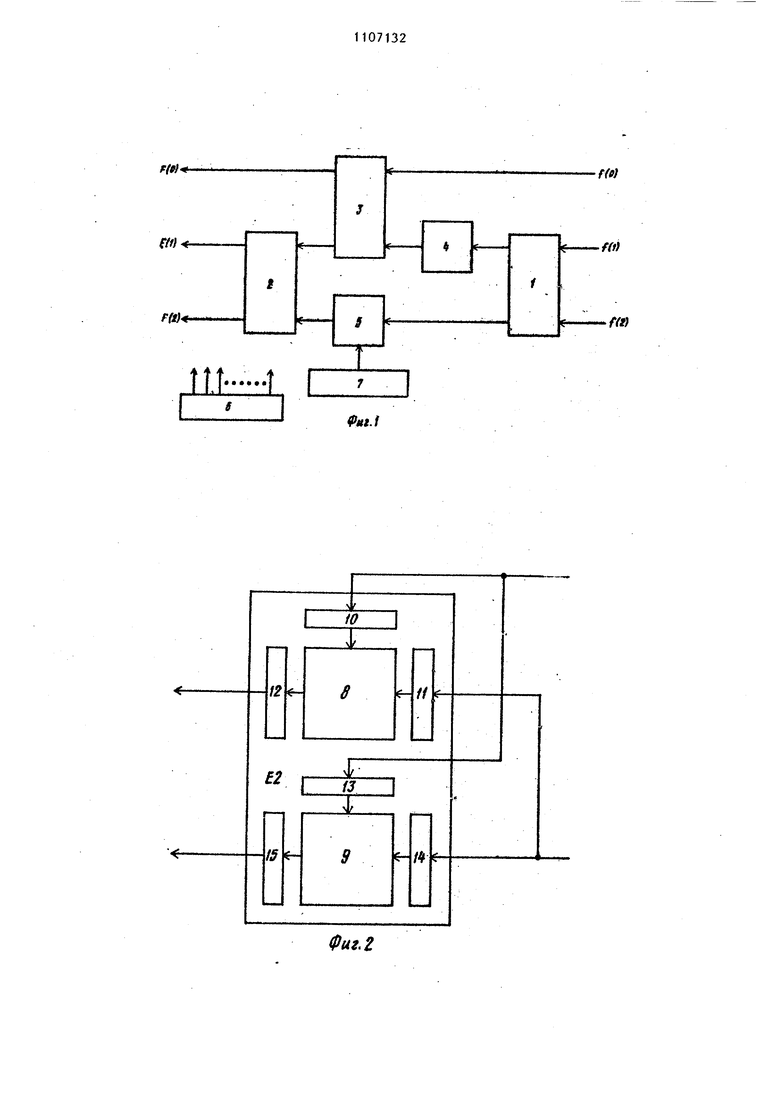

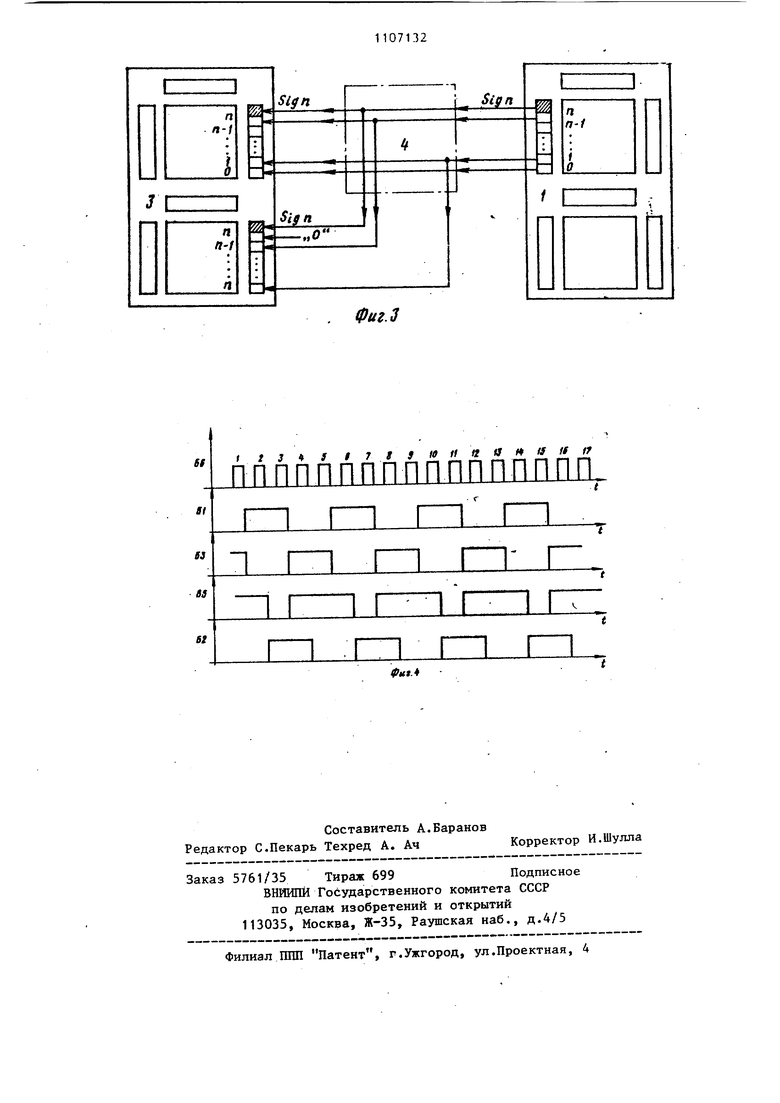

Изобретение относится к вычислительной технике и может быть использовано при построении высокопроизводительных специализированных процессоров быстрого преобразования Фурье (БПФ), Известно арифметическое устройство процессоров БПФ, реализующее дискретное преобразование Фурье (ДПФ) для N 3. Все вычисления здесь реали -зуются согласно выражению Р(к)- где f -значение n-го элемента, определякяцего сигнал во временной области; t -К-й элемент, определяю щий БПФ сигнала. Устройство содержит входной и выходной коммутаторы сигналов, два сдвиговых регистра для хранения проме жуточных результатов, умножитель на константу J умножитель на фазовые множители н арифметическое устройство, включающее в себя сумматор, умножитель и вьгаитатель. Ввод в устройство,входных данных осуществляется последовательно через входной коммутатор, причем первый выход арифметического устройства свя зан с первым входом входного коммутатора и с первым входом выходного коммутатора, второй вход входного коммутатора служит входом ввода данных, третий вход входного коммутатора связан а выходом умножителя на константу - ;д ТЩ , а четвертый вход входного ком мутатора соединен с входом умножителя на константу - 3 выходом второ го сдвигового регистра. Первый выход входного коммутатора соединен с входом первого сдвигового регистра, выход которого поступает на первый вход арифметического устройства, а второй выход входного коммутатора поступает на второй вход арифметического устройства. Второй выход арифметического устройства соединен с входом второго сдвигового регистра, выход которого поступает на второй вход выходного коммутатора. Выход выходного коммутатора связан с входом з ножителя на разовые множители, выход которого служит выходом самого устройства Р1. Недостатками такого устройства являются последовательный принцип действия и избыток вычислений. Наиболее близким по технической сущности к изобретению является устройство трехточечного БПФ, реализуемое по алгоритму Виноградова, содержащее два блока двухточечного ДПФ два сумматора и два умножителя на константы, причем нулевой вход устройбтва связан с первым входом первого сумматора, выход которого соединен с нулевым выходом устройства и первым входом второго сумматора, а первый и второй входы устройства связаны соответственно с первым и вторым входами первого блока двухточечного ДПФ, первый выход которого связан с вторым входом первого сумматора и первым входом первого умножителя, выход которого соединен с вторым входом второго блока двухточечного ДПФ, первый вход которого соединен с выходом второго сумматора, причем первым и вторым входами устройства являются пер- вьй и второй выходы.второго блока двухточечного ДПФ, а на вторые входы первого и второго умножителей поступают соответственно константы -1,5, . Г21. Недостатками известного устройства являются излишнее оборудование, а также различная номенклатура входящих в него блоков, что приводит к пониженной производительности, уменьшению его быстродействия и отсутствию универсальности при его проектировании. Цель изобретения - повьшение быстродействия и упрощение устройства. Поставленная цель достигается тем, что в устройство для трехточечного быстрого преобразования Фурье, содержащее первый сумматор-вычитатель, первый вход которого подключен к выходу умножителя, первый вход которого соединен с выходом разности второго сумматора-вычитателя, первый и второй входы которого являются соответственно первым и вторым информационными входами устройства, информационный выход регистра константы подключен к второму входу умножителя, входы суммы и разности первого сумматора-вычитателя являются соответственно первым и вторым информационными выходами устройства, введены третий сумматор-вычитатель и распределитель, причем выход суммы второго сумматора-вычитателя соединен с входом распределителя, выход которого соединен с первым входом третьего сумматора-вычитателя, выход разности которого соединен с вторым входом первого сумматора-вычитателя, второй вход и выход суммы третьего сумматора-вычитателя являются соответственно третьим информационным вхо дом и третьим информационным выходом устройства. Причем распределитель соединяет каждый п -и информационный разряд регистра хранения результата суммирования выхода второго сумматора-вычитателя (блока двухточечного ДПФ) с каждым () информационным разрядом регистра хранения входных операндов входа третьего сумматора-вычитателя, а знак переносится без изменений. Такая перекоммутация даёт автоматический сдвиг информационной части числа впра во на один разряд, тем самым осуществляя деление самого числа на 2. . На фиг.1 представлена структурная схема устройства, на фиг.2 - сумматор-вычитатель на фиг-.З - распределитель и его подключениеJ на фиг.4 вьщеленные диаграммы. Устройство содержит три сумматоравычитателя (блока дв5О1Точечного ДПФ) 1-3, распределитель 4, умножитель 5, блок 6 синхронизации и регистр 7 константы. Сумматор-вычитатель состоит из сум матора 8, вычитателя 9 и регистров 10-15. Уcfpoйcтвo работает следующим образом. f( поступает на вход сумматора-вычитателя 3, а соответствующие величины fW и S(f поступают соответственно на входы сумматора-вычитателя 1, выход которого (l) L соединен с распределителем 4. Сумма &-) чере распределитель без изменения поступае на входной регистр сумматору 8 сумматора-вычитателя 3 и в виде- Cf i -bf (2.)i поступает на входной регистр вычитатея 9 того же блока, причем результат F(t)) (b)-t-f(HECl) поступает на третий выход устройства, а результат ij,-i2 C C1 -:fC2.) поступает на второй вход сумматора-вычитателя 2, на выходе которого образуется F()(c)-|tf6Vf (2)1 -ЗГ Результат г iV с соответствующего cyMMatopa-вычитателя 1 поступает на вход умножителя 5, а на другой вход умножителя с регистра 7 константы поступает значение j На выходе умножителя 5 получается величина (}-i.ti}1, которая поступает на соответствующий сумматор-вычитатель 2, на выходе которого появляется значение V(:2).m-|cf :i f6t -iftfC vf(2) Работа устройства осуществляется в конвеерном режиме и управляется блоком 6 синхронизации. Устройство ,реализует вычисления по формулам f(((i)f(iX ГС)-Ш-|(1(, Ful f(o) itf( (bf йП. Таким образом, исключение из известного устройства одного блока умножения и включение в состав устройства, коммутатора, а также замена отдельных сумматоров сумматором-вычитателем позволяет сократить оборудование, увеличить быстродействие уст ройства.

nt--t

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления быстрого преобразования Фурье с основанием 6 | 1986 |

|

SU1334156A1 |

| Устройство для выполнения быстрого преобразования фурье | 1987 |

|

SU1520538A1 |

| Арифметическое устройство для выполнения быстрого преобразования Хартли-фурье | 1990 |

|

SU1795473A1 |

| Устройство для трехточечного быстрого преобразования Фурье | 1984 |

|

SU1206801A1 |

| ПРОЦЕССОР С МАКСИМАЛЬНО ВОЗМОЖНОЙ ПРОИЗВОДИТЕЛЬНОСТЬЮ ДЛЯ БЫСТРОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ | 2005 |

|

RU2290687C1 |

| Устройство для измерения фазовых сдвигов | 1984 |

|

SU1226341A1 |

| Каскадное устройство для быстрого преобразования Фурье | 1983 |

|

SU1265794A1 |

| Процессор быстрого преобразования Фурье | 1988 |

|

SU1667101A1 |

| Арифметическое устройство для выполнения быстрого преобразования Хартли-Фурье | 1990 |

|

SU1756902A1 |

| Устройство для реализации быстрого преобразования фурье | 1977 |

|

SU734708A1 |

УСТРОЙСТВО ДЛЯ ТРЕХТОЧЕЧНОГО БЫСТРОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ, содержащее первый cyммaтop-вьrчиtaтeль, первый вход которого подключен к выходу умножителя, первьй вход которого соединен с выходом разности второго сумматора-БЫчитателя, первый и второй входы которого являются соответственно первым и вторым информационными входами устройства информационный выход регистра константы подключен к второму входу умножителя, входы суммы и разности первого сумматора-вычитатеЛя являются соответственно первым и вторым информационными вьпсодами устройства, отличающееся тем, что, с целью повышения быстродействия и упрощения устройства, оно -содержит третий сумматор-вычитатель и распределитель, причем выход суммы второго сумматоравычитателя соединен с входом распределителя, выход которого соединен с первым входом третьего сумматора-вычитателя, выход разности которого (Л соединен с вторым входом первого сумматора-вычитателя, вт1ррой вход и выход суммы третьего сумматора-вычитателя являются соответственно третьим информационным входом и третьим информационным выходом устройства.

Фиг. г

. Фиг.З

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Патент США 3899667, Kji | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Сплав для отливки колец для сальниковых набивок | 1922 |

|

SU1975A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Кухарев Г.А., Новоселов Н.Д | |||

| Скорняков B.C | |||

| Структура процессорных элементов модульных БПФ-процессоров | |||

| - Изв | |||

| высш | |||

| учеб | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1984-08-07—Публикация

1983-04-08—Подача