ЧтРY ViVrVIJ Y

-J

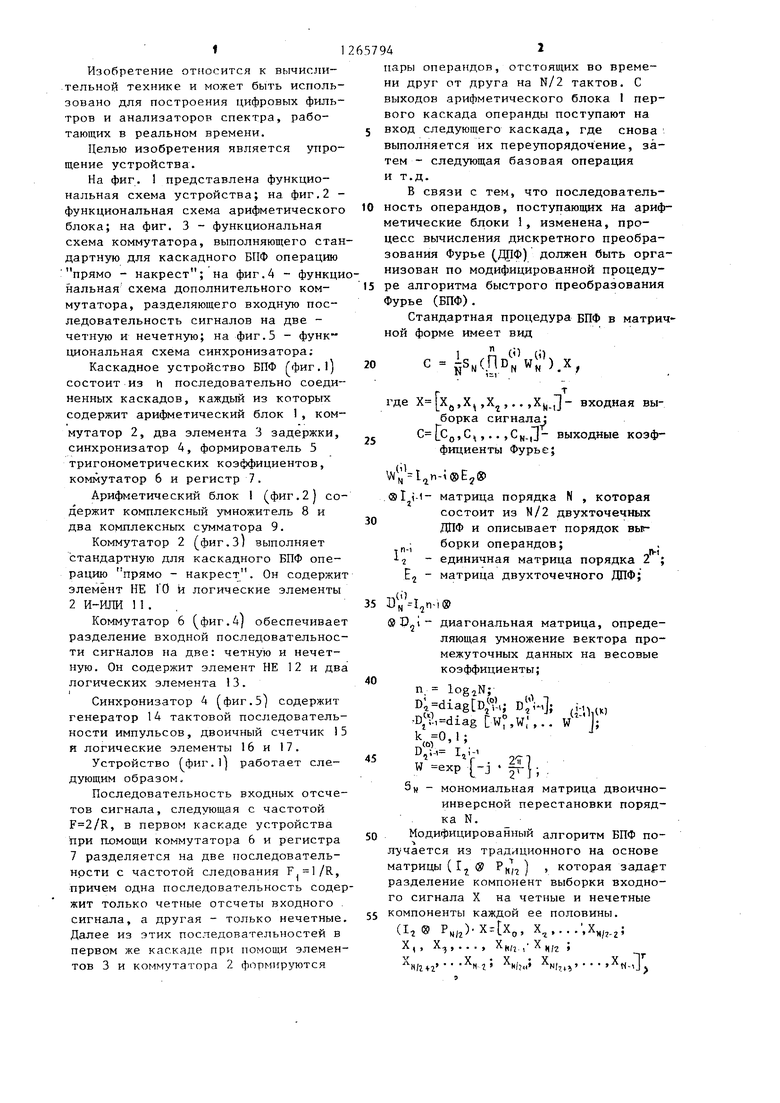

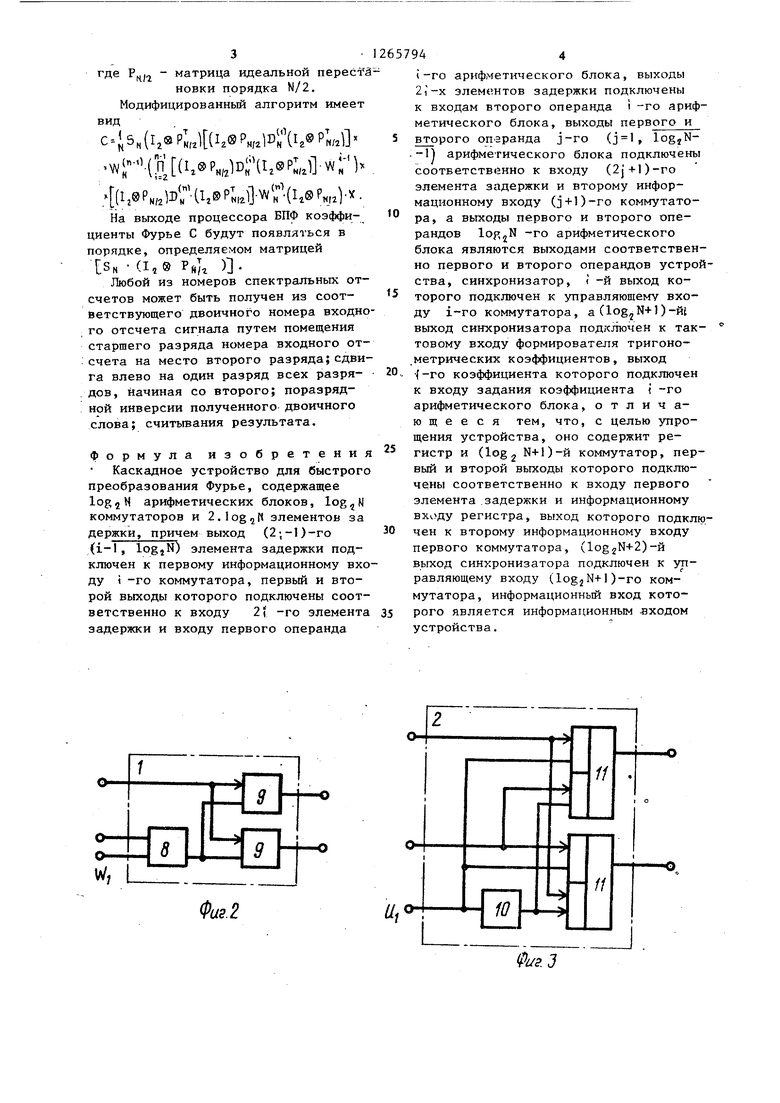

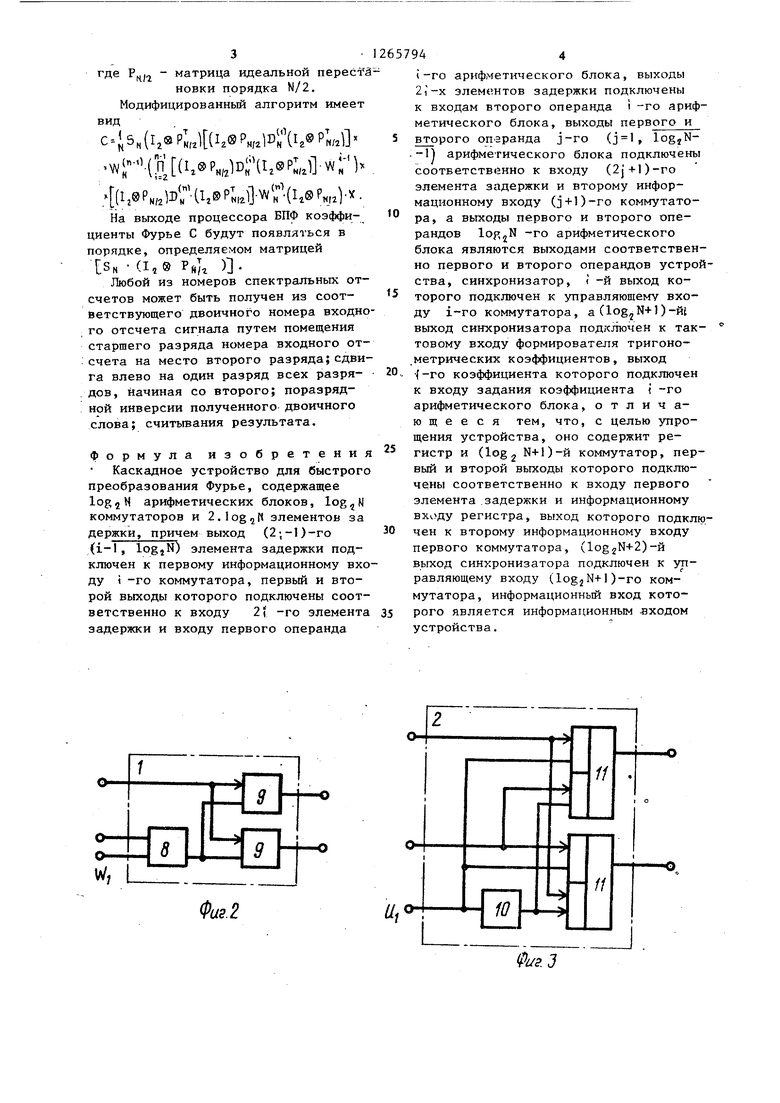

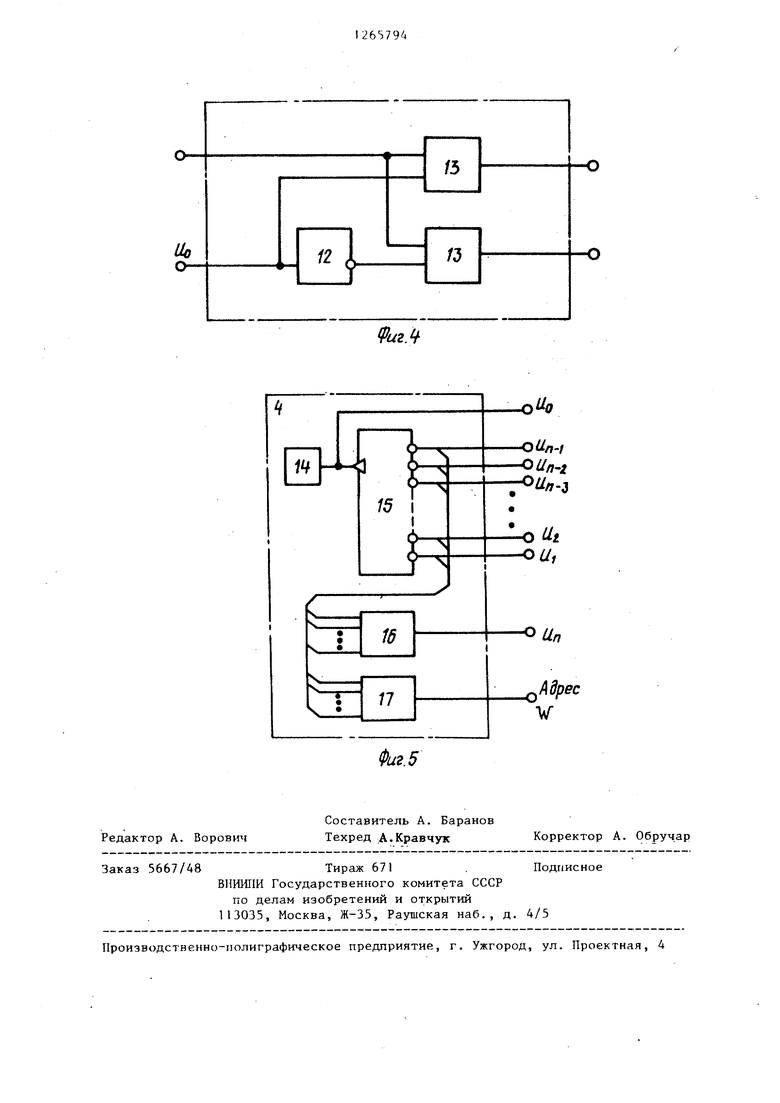

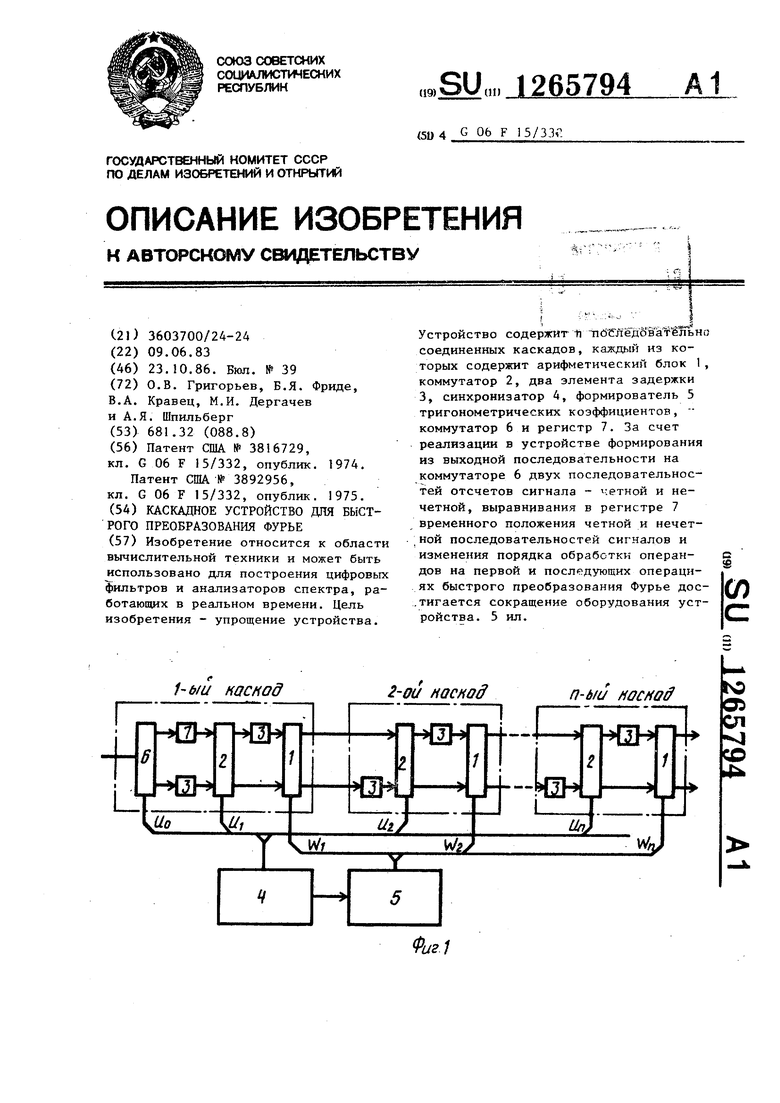

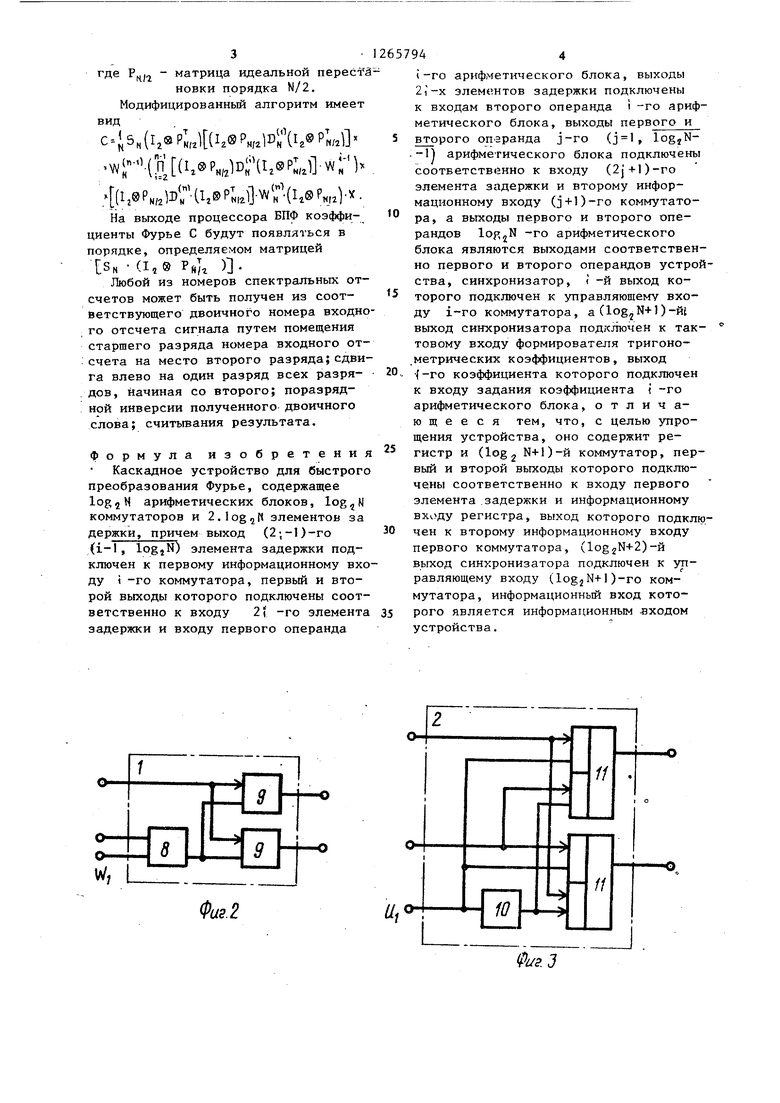

П-Ыи MOCHOff -f Изобретение относится к вычислительной технике и может быть использовано для построения цифровых фильтров и анализаторов спектра, работающих в реальном времени. Целью изобретения является упрощение устройства. На фиг. 1 представлена функциональная схема устройства; на фиг,2 функциональная схема арифметического блока; на фиг. 3 - функциональная схема коммутатора, выполняющего стан дартную для каскадного БПФ операцию прямо - накрест ; на фиг.4 - функци нальная схема дополнительного коммутатора, разделяющего входную последовательность сигналов на две четную и нечетную; на фиг.5 - функциональная схема синхронизатора; Каскадное устройство БПФ Гфиг.1) состоит из h последовательно соединенных каскадов, каждый из которых содержит арифметический блок 1, коммутатор 2, два элемента 3 задержки, синхронизатор 4, формирователь 5 тригонометрических коэффициентов, коммутатор 6 и регистр 7. Арифметический блок 1 (фиг.2) содержит комплексный умножитель 8 и два комплексных сумматора 9. Коммутатор 2 (фиг.З) выполняет стандартную для каскадного БПФ операцию прямо - накрест. Он содержит элемент НЕ ГО k логические элементы 2 И-ИЛИ 11., Коммутатор 6 (фиг.4) обеспечивает разделение входной последовательности сигналов на две: четную и нечетную. Он содержит элемент НЕ 12 и два логических элемента 13. Синхронизатор 4 (фиг.5) содержит генератор 14 тактовой последовательности импульсов, двоичный счетчик 15 я логические элементы 16 и 17. Устройство (фи1.1| работает следующим образом. Последовательность входных отсчетов сигнала, следующая с частотой , в первом каскаде устройства при помощи коммутатора 6 и регистра 7 разделяется на две последовательности с частотой следования , причем одна последовательность содер жит только четные отсчеты входного . сигнала, а другая - только нечетные Далее из этих последовательностей в первом же каскаде прн помощи элементов 3 и коммутатора 2 формируются 4 отстоящих во времепары операндов. ни друг от друга на N/2 тактов. С выходов арифметического блока 1 первого каскада операнды поступают на вход следующего каскада, где снова выполняется их переупорядочение, затем - следующая базовая операция и т.д. в связи с тем, что последовательность операндов, поступающих на арифетические блоки 1, изменена, процесс вычисления дискретного преобразования Фурье (ДПФ) должен быть организован по модифицированной процедуре алгоритма быстрого преобразования урье (БПФ). Стандартная процедура БПФ в матричной форме имеет вид С s.r..x, Г где ,X ,Х ,,. ,Хц., входная выборка сигнала: С Сц,С,.. ,С.,- выходные коэффициенты Фурье; , матрица порядка N , которая состоит из N/2 двухточечных ДПФ и описывает порядок выборки операндов; единичная матрица порядка 2 ; матрица двухточечного ДПФ; ,n-i® диагональная матрица, определяющая умножение вектора промежуточных данных на весовые коэффициенты; п, D; diagtD.; D;V.; н , -D;V-,diag CW°,W:,.. k 0,1; „ОД , DI- 21 W exp {-j . |f} ; : SH - мономиальная матрица двоичноинверсной перестановки порядка N. Модифицированный алгоритм БПФ получается из традиционного на основе матрицы ( Г ® n которая задарт разделение компонент выборки входного сигнала X на четные и нечетные компоненты каждой ее половины. ( Р,,,).х4Хо, Х,....,Х Н/г Nb,- , 3 где Р,г - матрица идеальной пересра новки порядка N/2, Модифицированный алгоритм имеет вид . С-15„(1г®Р«Д(1г®Рм,.1вЛ1,®Р«,а1 ,(;i;(i.®p.,,iD;Hi,®p;,j -w;- v Я(1г®Р«,2РГиа®Р,г)(1г®М На выходе процессора БПФ коэффициенты Фурье С будут появляться в порядке, определяемом матрицей SN (I,® PftK ) ТЬобой из номеров спектральных отсчетов может быть получен из соответствующего двоичного номера входно го отсчета сигнала путем помещения старшего разряда номера входного от:счета на место второго разряда; сдви га влево на один разряд всех разрядов, начиная со второго; поразрядной инверсии полученного двоичного слова; считьгеания результата. Формула изобретени Каскадное устройство для быстрог преобразования Фурье, содержащее logjH арифметических блоков, коммутаторов и Z. элементов за держки, причем выход (2;-1)-го (г-1, logiN) элемента задержки подключен к первому информационному вх ду i -го коммутатора, первый и второй выходы которого подключены соот ветственно к входу 2( -го элемент задержки и входу первого операнда 44 ( -го арифметического блока, выходы 2i-x элементов задержки подключены к входам второго операнда i -го арифметического блока, выходы первого и второго операнда j-ro (, logjN-1) арифметического блока подключень соответственно к входу (2j+l)-ro элемента задержки и второму информационному входу (j+l)-ro коммутатора, а выходы первого и второго операндов lopjN -го арифметического блока являются выходами соответственно первого и второго операндов устройства, синхронизатор, -и выход которого подключен к управляющему входу i-ro коммутатора, а(logjN+I)-й1 выход синхронизатора поддслючен к тактовому входу формирователя тригонометрических коэффициентов, выход (-го коэффициента которого подключен к входу задания коэффициента i -го арифметического блока, отличающееся тем, что, с целью упрощения устройства, оно содержит регистр и (log 2 М+1)-й коммутатор, первый и второй выходы которого подключены соответственно к входу первого элемента .задержки и информационному входу регистра, выход которого подключен к второму информационному входу первого коммутатора, (logгN+2)-й выход синхронизатора подключен к управляющему входу (logjN+l)-ro коммутатора, информационный вход которого является информационным входом устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для выполнения быстрого преобразования фурье | 1987 |

|

SU1520538A1 |

| Устройство для реализации двухмерного быстрого преобразования Фурье | 1982 |

|

SU1164730A1 |

| Устройство для выполнения быстрого преобразования Фурье | 1985 |

|

SU1337904A1 |

| Устройство для быстрого преобразования Фурье | 1985 |

|

SU1304034A1 |

| Устройство для выполнения быстрого преобразования Фурье по основанию два | 1984 |

|

SU1198534A1 |

| Процессор быстрого преобразования Фурье | 1988 |

|

SU1667101A1 |

| Устройство для реализации быстрого преобразования Фурье последовательности с нулевыми элементами | 1983 |

|

SU1119025A1 |

| Устройство для вычисления скользящего спектра | 1987 |

|

SU1418746A1 |

| Процессор быстрого преобразования Фурье | 1985 |

|

SU1247891A1 |

| Устройство для формирования адресов процессора быстрого преобразования Фурье | 1986 |

|

SU1324037A1 |

Изобретение относится к области вычислительной техники и может быть использовано для построения цифровых фильтров и анализаторов спектра, работающих в реальном времени. Цель изобретения - упрощение устройства. Устройство содержит ц Titfraeflofйт льно соединенных каскадов, каждый из которых содержит арифметический блок 1 , коммутатор 2, два элемента задержки 3, синхронизатор 4, формирователь 5 тригонометрических коэффициентов, коммутатор 6 и регистр 7. За счет реализации в устройстве формирования из выходной последовательности на коммутаторе 6 двух последовательностей отсчетов сигнала - ;етной и нечетной, выравнивания в регистре 7 временного положения четной и нечетной последовательностей сигналов и изменения порядка обработки операнс дов на первой и последующих операци(Л ях быстрого преобразования Фурье дос.тигается сокращение оборудования устройства. 5 ил.

Uo o

12

1Ъ

fe4

| Патент США № 3816729, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| ПРИБОР ДЛЯ ЗАПИСИ И ВОСПРОИЗВЕДЕНИЯ ЗВУКОВ | 1923 |

|

SU1974A1 |

| Патент США №3892956, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Сплав для отливки колец для сальниковых набивок | 1922 |

|

SU1975A1 |

Авторы

Даты

1986-10-23—Публикация

1983-06-09—Подача