Изобретение относится к измери- , телг: пой технике и может быть использовано для помехоустойчивого измерения сдвига фаз в радиотехнических и измерительных устройствах.

Цель изобретения - расширение частотного диапазона,, а также обеспечение возможности раздельного из-- мерения фазовых сдвигов основного сигнала и его гармонических составляющих .

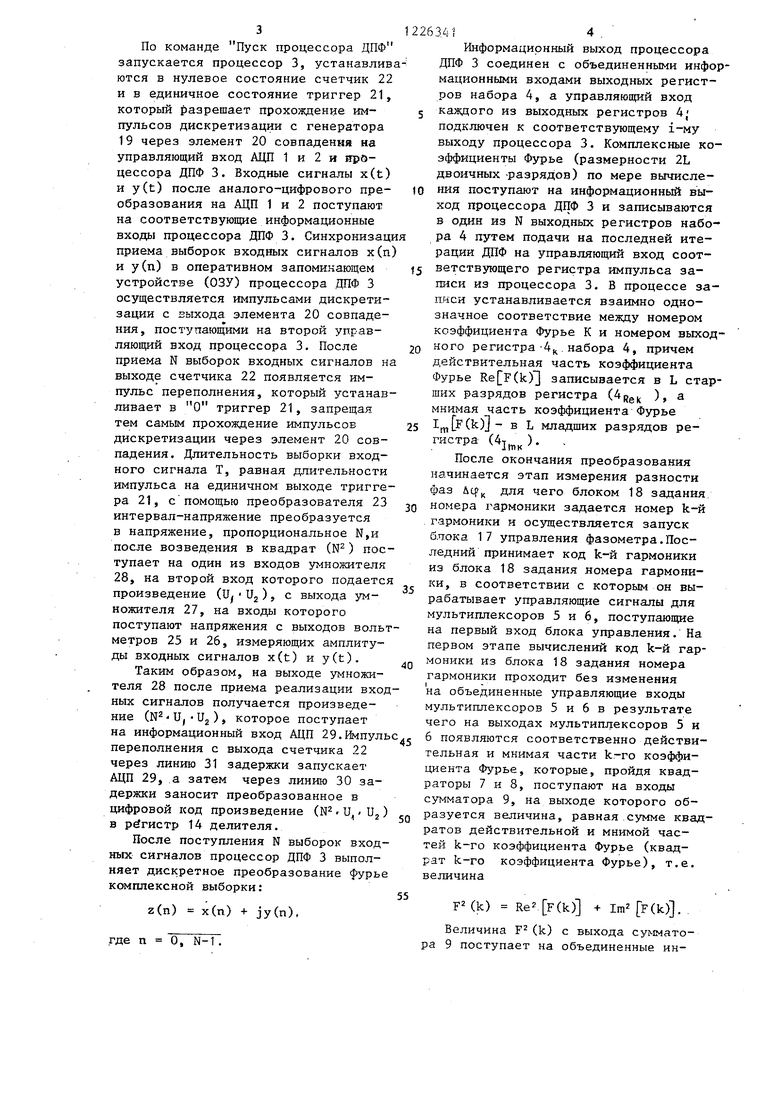

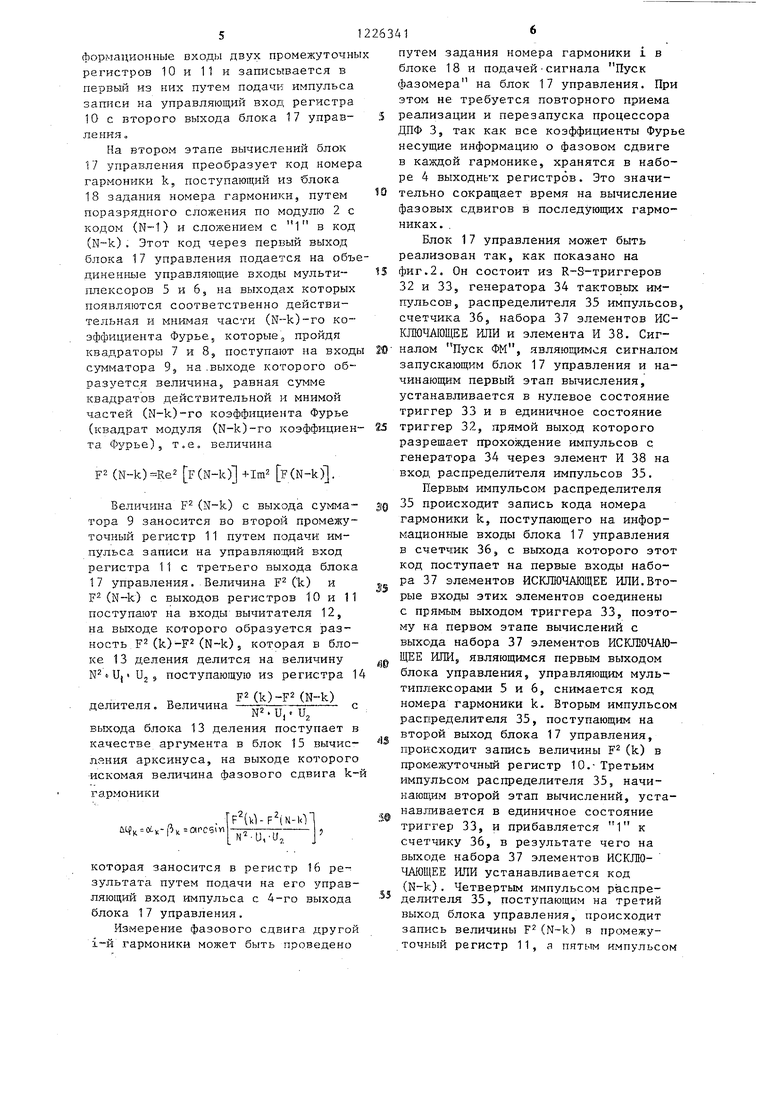

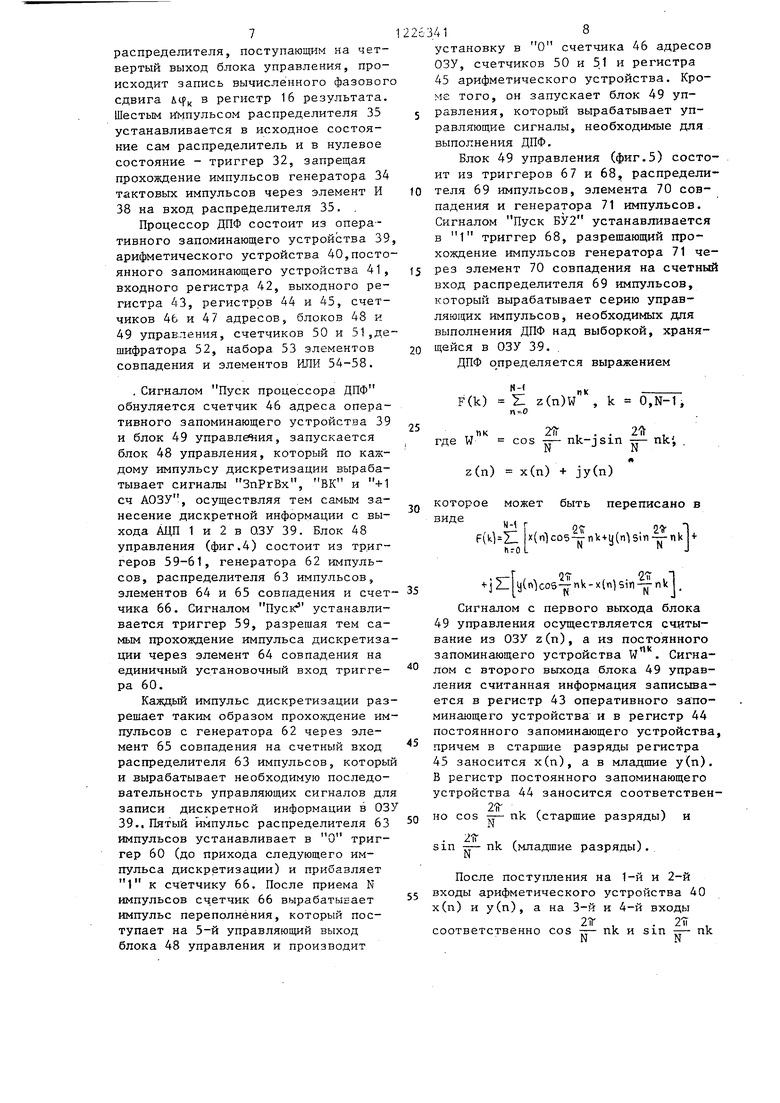

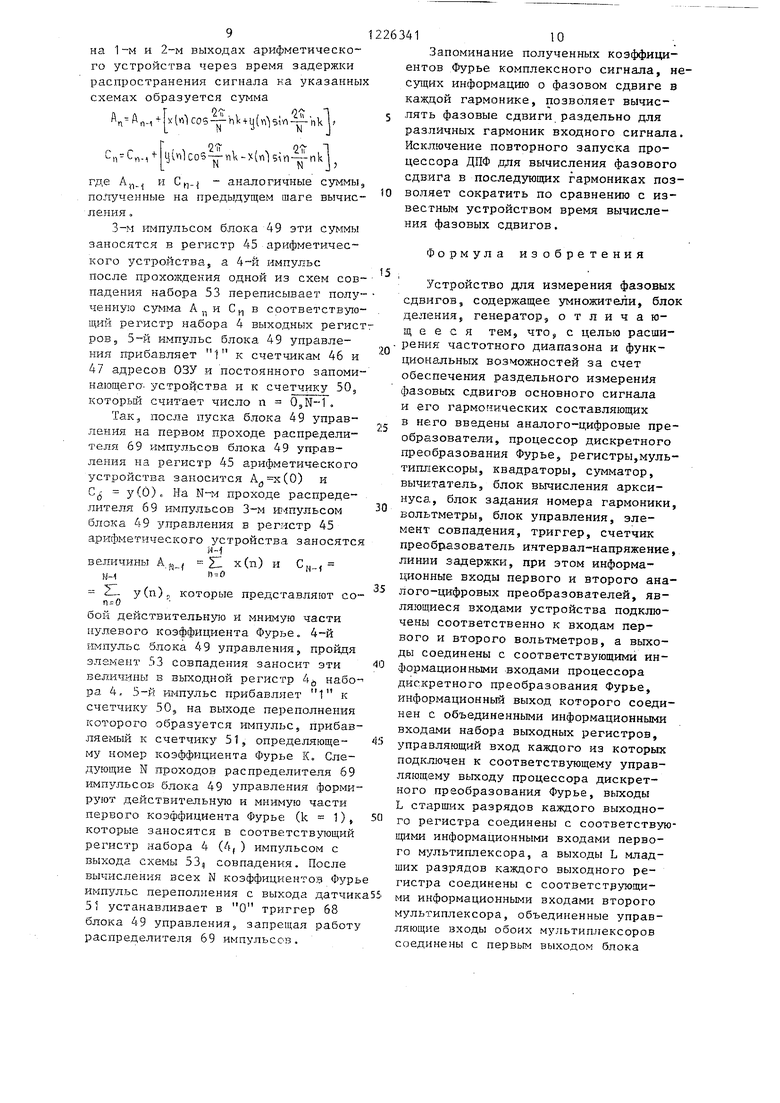

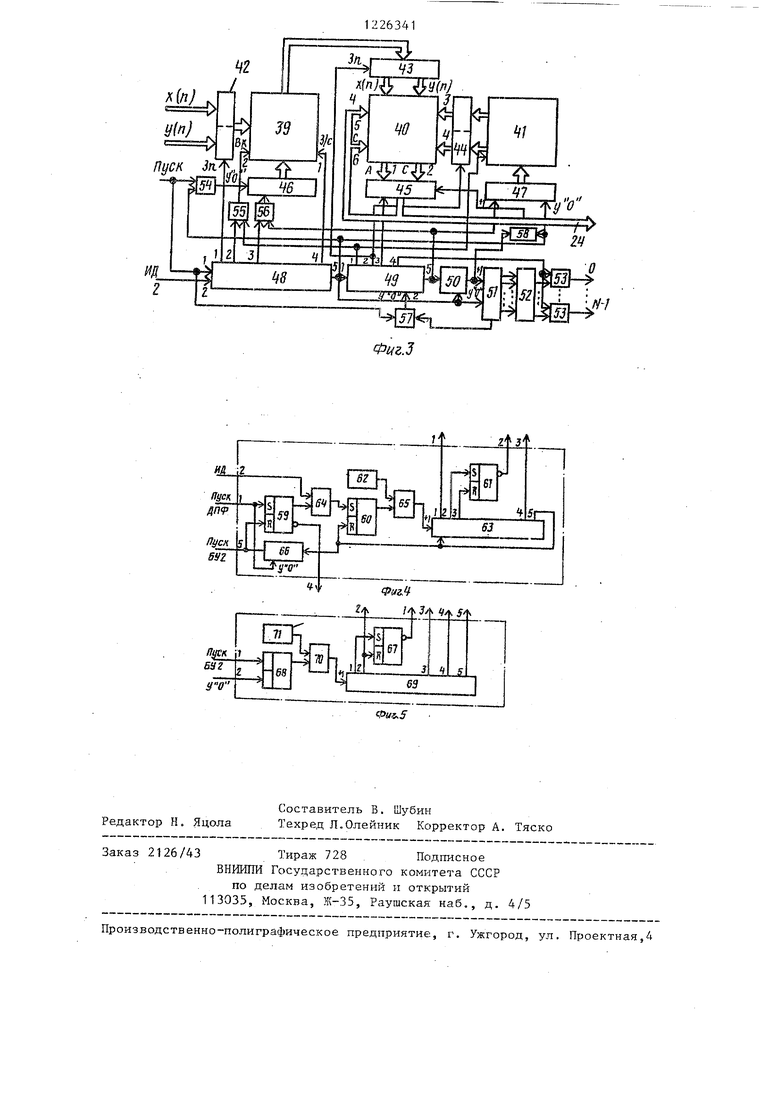

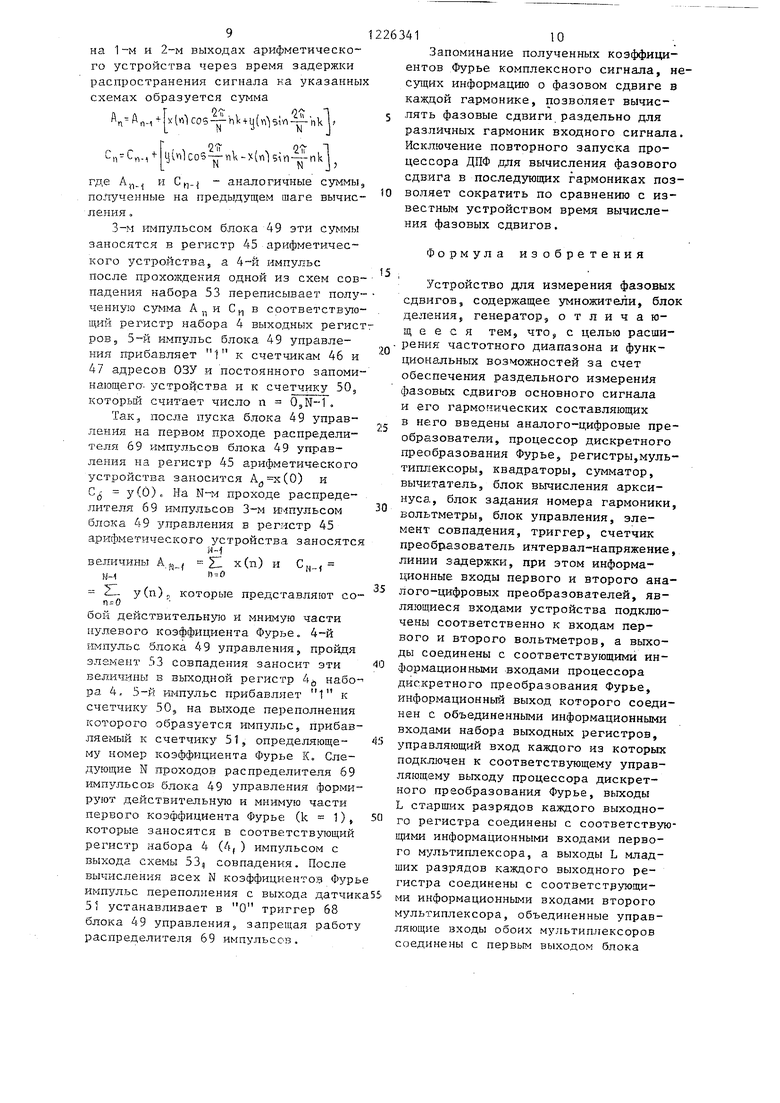

На фиг.1 изображена структурная схема устройств а для измерения фазовых сдвигов гармонических сигналов| на фиг.2 -- структурная схема блока управления всем устройством на фиг 3 - структурная схема процессора дискретного преобразования Фурье (ДПФ) э на фиг.4 -- структурная схе ма первого блока управления процессора ДПФэ на - структурная схема второго блока управления про- цессорс ДПФ.

Устройство содержит аналого- цифровые преобразователи (АЦП) 1 и процессор ДПФ 3, набор 4 выходных регистровS мультиплексоры 5 и 6, квадраторы 7 и 8. сумматор 9, про- меясуточные регистры 10 и 11 , вьпшта тель 12 блок 13 деления, регистр 14 делителя 5 блок 15 вычисления арксинуса; регистр 16 результата, блок 17 управления, блок 18 задания номера гармоники генератор 19, элемент 20 совпадения, триггер 21, счетчик 22,;преобразователь 23 интервал-напряжение, квадратор 24, вольтметры 25 и 26, умножители 27 и 28э А1Щ 29s, линии 30 и 31 задержк

При этом информационные входы первого и второго АЦП, являющиеся входами устройства,подключены соответственно к входам первого и второго вольтметров,, а выходы соедине- 1 ы с соответств тощими информацион™ входами процессора ДПФ, инфор- мадионньп выход которого соединен с объединенными информационными входами набора выход:1ых регистров, управляющий вход каждого из которых подключен к соответствующему управляющему выходу процессора ДПФ, Выходы L старших разрядов каждого выходного регистра соединены с соответст- вз-тощими информационными входами первого мультиплексора, а выхода L млад .ших,разрядов каждого выходного регистра соединены с соответствующими

15

-

25

2263412

,информационными входами второго мультиплексора: объединенные управ- ляюш,ие йходы обоих мультиплексоров соединены с первым выходом блока 5 управления5 а выход каждого мультиплексора подключен к входам соответствующего квадратора, выходы которого соединены с входами сумматора, выход которого подключен к объеди- te ненным информационным входам двух промежуточных регистров управляющие входы которых соединены, соот- ветстве.нно с вторым и третьим выходами блока управления, а выходы ре- гистров подключены к соответствующим входам вычитателяд выход которого соединен с входом делимого блока деления , вход делителя которого подключен к выходу регистра делителя, а выход через блок вычисления арксинуса - к информационному входу регистра результата, управляющий вход которого соединен с четвертым выходом блока управления, управляющий вход которого подключен к выходу блока задания номера гармоники.

Выходы каждого из вольтметров соединены с соответствующим входом первого умножителя, выход которого подключен к первому входу второго умногштеля, выход которого соединен с информационным входом третьего аналого-цифрового преобразователя, выход которого подключен к информационному входу регистра результата, управляющий вход которого через первую, линию задержки соединен с управляющим входом третьего АЦП и через вторую линию з.адержки соединен с нулевым установочным входом триггера и выходом переполнения счетчика, управляющий вход которого соединен с первьм управляющим входом процессора ДПФ и единичным установочным входом триггера, а счетный вход счетчика подключен к объединенным управляющим входам первого и второго АЦП к второму управляющему входу процессора ДПФ и выходу элемента совпадения, один из входов которого подключен к выходу генератора импульсов, а второй - к прямому выходу триггера и входу преобразователя интервал- напряжение, выход которого через третий квадратор подключен к второ- му вхо;|у второго умножителя.

30

35

40

50

SS

Устройство работает следующим образом.

По команде Пуск процессора ДПФ запускается процессор 3, устанавлива ются в нулевое состояние счетчик 22 и в единичное состояние триггер 21, который разрешает прохождение им- пульсов дискретизации с генератора 19 через элемент 20 совпадения на управляющий вход АЦП 1 и 2 и йра- цессора ДПФ 3. Входные сигналы x(t) и y(t) после аналого-цифрового пре- образования на АЦП 1 и 2 поступают на соответствующие информационные входы процессора ДПФ 3. Синхронизаци приема выборок входных сигналов х(п) и у(п) в оперативном запоминающем устройстве (ОЗУ) процессора .ДПФ 3 осуществляется импульсами дискретизации с выхода элемента 20 совпадения, поступающими на второй управляющий вход процессора 3. После приема N выборок входных сигналов на выходе счетчика 22 появляется импульс переполнения, который устанавливает в О триггер 21, запрещая тем самым прохождение импульсов дискретизации через элемент 20 совпадения. Длительность выборки входного сигнала Т, равная длительности импульса на единичном выходе триггера 21, с помощью преобразователя 23 интервал-напряжение преобразуется в напряжение, пропорциональное Ы,и после возведения в квадрат (N) поступает на один из входов умножителя 28, на второй вход которого подается произведение (U Из), с выхода умножителя 27, на входы которого поступают напряжения с выходов вольтметров 25 и 26, измеряющих амплитуды входных сигналов x(t) и y(t).

Таким образом, на выходе умножителя 28 после приема реализации входных сигналов получается произведение (N Uj Uj), которое поступает на информационный вход АЦП 29.Импуль переполнения с выхода счетчика 22 через линию 31 задержки запускает АЦП 29, а затем через линию 30 задержки заносит преобразованное в цифровой код произведение (№ и и) в регистр 14 делителя.

После поступления N выборок входных сигналов процессор ДПФ 3 выполняет дискретное преобразование Фурье комплексной выборки:

z(n) х(п) + jy(n),

где п О, N-1 .

5 10 t5 20 25

5

5

5

Информационный выход процессора ДПФ 3 соединен с объединенными информационными входами выходных регистров набора 4, а управляющий вход каящого из выходных регистров 4; подключен к соответствующему i-му выходу процессора 3. Комплексные коэффициенты Фурье (размерности 2L двоичных -разрядов) по мере вычисления поступают на информационный выход процессора ДПФ 3 и записываются в один из N выходных регистров набора 4 путем подачи на последней итерации ДПФ на управляющий вход соответствующего регистра импульса записи из процессора 3. В процессе записи устанавливается взаимно однозначное соответствие между номером коэффициента Фурье К и номером выходного регистра-4.набора 4, причем действительная часть коэффициента Фурье (k)3 записывается в L старших разрядов регистра (4pg| ), а мнимая часть коэффициента Фурье (k)j- в L младших разрядов ре- гистра (4j). ,

После окончания преобразования начинается этап измерения разности фаз icfi для чего блоком 18 задания номера гармоники задается номер k-й гармоники и осзпществляется запуск блока 17 управления фазометра.Последний принимает код k-й гармоники из блока 18 задания номера гармоники, в соответствии с которым он вырабатывает управляющие сигналы для мультиплексоров 5 и 6, поступающие на первый вход блока управления. На первом этапе вычислений код k-й гармоники из блока 18 задания номера гармоники проходит без изменения на объединенные управляющие входы мультиплексоров 5 и 6 в результате чего на выходах мультиплексоров 5 и 6 появляются соответственно действительная и мнимая части k-ro коэффициента Фурье, которые, пройдя квадраторы 7 и 8, поступают на входы сумматора 9, на выходе которого образуется величина, равная сумме квадратов действительной и мнимой частей k-ro коэффициента Фурье (квадрат k-ro коэффициента Фурье), т.е. величина

F (k) Re F(k) + Im F(k). .

Величина F(k) с выхода сумматора 9 поступает на объединенные информационные входы двух промежуточны регистров 10 и 11 и записывается в первый из них путем подачи импульса saniiCH на управляющий вход регистра 10 с второго выхода блока 17 управления о

На втором этапе вычислений блок

17управления преобразует код номера гармоники k, поступающий из блока

18задания номера гармоники, путем поразрядного сложения по модулю 2 с кодом (N-1) и сложением с 1 в код

(N-k). Этот код через первый выход блока 17 управления подается на объединенные управляющие входы мультиплексоров 5 и 6, на выходах которых появляются соответственно действительная и мнимая части (N-k)-го коэффициента Фурье, которые, пройдя квадраторы 7 и 8, поступают на входы сумматора 9, на .выходе которого образуется величина5 равная сумме квадратов действительной и мнимой частей (N-k)-го коэффициента Фурье (квадрат модуля (N-k)-ro коэффициен- 23 триггер 32, прямой выход которого

Блок 17 управления может быть реализован так, как показано на

15 фиг.2. Он состоит из R-S-триггеров 32 и 33, генератора 34 тактовьк им пульсов, распределителя 35 импульс счетчика 36, набора 37 элементов И КЛЮЧАЮЩЕЕ ИЛИ и элемента И 38. Си

JU налом Пуск ФМ, являющимся сигнал запускающим блок 17 управления и н чинающим первый этап вычисления, устанавливается в нулевое состояни триггер 33 и в единичное состояни

та Фурье)5 т.е. величина рг (N-k)Re2 F(N-k) +Im2 F(N-k).

Величина F(N-k) с выхода сумматора 9 заносится во второй промежуточный регистр 11 путем подачи импульса записи на управляющий вход регистра 11 с третьего выхода блока 17 управления. Величина Е(k) и F(N-k) с выходов регистров 10 и 11 поступшот на входы вычитателя 12, на вьпсоде которого образуется разность F (k)-F (N-k), которая в блоке 13 деления делится на величину Uj5 поступающую из регистра 14

делителя. Величина

F(k)-F(N-k) N2. и, U

выхода блока 13 деления поступает в качестве аргумента в блок 15 вычис- лания арксинуса, на выходе которого искомая величина фазового сдвига k-й

гармоники

utfj, oL);-fin arcsm

F ( , U,

которая заносится в регистр 16 результата путем подачи на его управляющий вход импульса с 4-го выхода блока 17 управления.

Измерение фазового сдвига другой 1-й гармоники может быть проведено

триггер 32, прямой выход которого

путем задания номера гармоники i в блоке 18 и подачейсигнала Пуск фазомера на блок 17 управления. При этом не требуется повторного приема

реализации и перезапуска процессора ДПФ 3, так как все коэффициенты Фурье несущие информацию о фазовом сдвиге в каждой гармонике, хранятся в наборе 4 выходнь х регистров. Это значительно сокращает время на вычисление фазовых сдвигов в последующих гармониках. ,

Блок 17 управления может быть реализован так, как показано на

фиг.2. Он состоит из R-S-триггеров 32 и 33, генератора 34 тактовьк импульсов, распределителя 35 импульсов, счетчика 36, набора 37 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ и элемента И 38. Сигналом Пуск ФМ, являющимся сигналом запускающим блок 17 управления и начинающим первый этап вычисления, устанавливается в нулевое состояние триггер 33 и в единичное состояние

S

О

разрешает прохождение импульсов с генератора 34 через элемент И 38 на вход распределителя импульсов 35.

Первым импульсом распределителя 35 происходит запись кода номера гармоники k, поступающего на инфор- гaциoнныe входы блока 17 управления в счетчик 36, с выхода которого этот код поступает на первые входы набора 37 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ.Вторые входы этих элементов соединены с прямым выходом триггера 33, поэтому на первом этапе вычислений с выхода набора 37 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, являющимся первым выходом блока управления, управляющим мультиплексорами 5 и 6, снимается код номера гармоники k. Вторым импульсом распределителя 35, поступающим на

- второй выход блока 17 управления, происходит запись величины F(k) в промеж5 точный регистр 10.-Третьим импульсом распределителя 35, начи- второй этап вычислений, уста- навпивается в единичное состояние триггер 33, и прибавляется 1 к счетчику 36, в результате чего на выходе набора 37 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ устанавливается код (N-k). Четвертым импульсом распре делителя 35, поступающим на третий выход блока управления, происходит запись величины F(N-k) в промежуточный регистр 11, а пятьтм импульсом

7

распределителя, поступающим на четвертый выход блока управления, происходит запись вычисленного фазового сдвига мрц в регистр 16 результата. Шестым импульсом распределителя 35 устанавливается в исходное состояние сам распределитель и в нулевое состояние - триггер 32, запрещая прохождение импульсов генератора 34 тактовых импульсов через элемент И 38 на вход распределителя 35. .

Процессор ДПФ состоит из оперативного запоминающего устройства 39 арифметического устройства 40,постоянного запоминающего устройства 41, входного регистра 42, выходного регистра 43, регистров 44 и 45, счетчиков 46 и 47 адресов, блоков 48 и 49 управления, счетчиков 50 и 51,дешифратора 52, набора 53 элементов совпадения и элементов ИЛИ 54-58.

. Сигналом Пуск процессора ДПФ обнуляется счетчик 46 адреса оперативного запоминающего устройства 39 и блок 49 управления, запускается блок 48 управления, который по каждому импульсу дискретизации вырабатывает сигналы ЗпРгВх, ВК и +1 сч АОЗУ, осуществляя тем самым занесение дискретной информации с выхода АЦП 1 и 2 в ОЗУ 39. Блок 48 управления (фиг.4) состоит из триггеров 59-61, генератора 62 импульсов, распределителя 63 импульсов, элементов 64 и 65 совпадения и счет- чика 66. Сигналом устанавливается триггер 59, разрешая тем самым прохождение импульса дискретизации через элемент 64 совпадения на единичный установочный вход тригге- ра 60.

Каждый импульс дискретизации разрешает таким образом прохождение импульсов с генератора 62 через элемент 65 совпадения на счетный вход распределителя 63 импульсов, который и вырабатывает необходимую последовательность управляющих сигналов для записи дискретной информации в ОЗУ 39.. Пятый импульс распределителя 63 импульсов устанавливает в О триггер 60 (до прихода следующего импульса дискретизации) и прибавляет 1 к счетчику 66. После приема N импульсов счетчик 66 вырабатывает импульс переполнения, который поступает на 5-й управляющий выход блока 48 управления и производит

418

установку в О счетчика 46 адресов ОЗУ, счетчиков 50 и 51 и регистра 45 арифметического устройства. Кроме того, он запускает блок 49 управления, который вырабатывает управляющие сигналы, необходимые для выполнения ДПФ,

Блок 49 управления (фиг,5) состоит из триггеров 67 и 68, распределителя 69 импульсов, элемента 70 совпадения и генератора 71 импульсов. Сигналом Пуск БУ2 устанавливается в 1 триггер 68, разрешающий прохождение импульсов генератора 71 через элемент 70 совпадения на счетный вход распределителя 69 импульсов, который вырабатывает серию управляющих импульсов, необходимых для выполнения ДПФ над выборкой, хранящейся в ОЗУ 3-9. .

ДПФ определяется выражением

N-(

11 z

IdПК

(n)W , k

n-o

0,N-1,

где W

ПК2 ... 2 .

cos - nk-jsin j- nk .

(n) x(n) + jy(n)

которое виде

может быть переписано в

N-1

FikbH |x(nlco5- nk + y(M5lti- n hroL J

(nlco6 nk-x(«lsin nkj,

Сигналом с первого выхода блока 49 управления осуществляется считывание из ОЗУ z(n), а из постоянного запоминающего устройства W . Сигналом с второго выхода блока 49 управления считанная информация записывается в регистр 43 оперативного запоминающего устройства и в регистр 44 постоянного запоминающего устройства, причем в старшие разряды регистра 45 заносится х(п), а в младшие у(п). В регистр постоянного запоминающего устройства 44 заносится соответственно cos rr- nk (старшие разряды) и

f

sin nk (младшие разряды).

После поступления на 1-й и 2-й входы арифметического устройства 40 х(п) и у(п), а на 3-й и 4-й входы

2 , . , соответственно cos -- nk и sin -- nk

NN

N-

y(n),,, которые представляют co

на и 2-м выходах арифметического устройства через время задержки распространения сигнала на указанных схемах образуется сумма

f)r- о 1 («lC05- bUl.j(n 5iri likj

Г о г

С,гС„., + hlvilcoS--nk-x(inn n-j;J -nkl

где А. и C.j - аналогичные суммы, по-Ггученные на предыдущем шаге вычисления о

3-м рмпульсом блока 49 эти суммы заносятся в регистр 45 арифметического устройства, а импульс после прохож,п;ения одной из схем совпадения набора 53 переписывает полученную сумма А ,, и Ср, в соответствующий регистр набора 4 выходных регист ров, 5-й импульс блока 49 управления прибавляет 1 к счетчикам 46 и 47 адресов ОЗУ и постоянного запоминающего- устройства и к счетчику ЗОд которьй считает число п OjN-l,

Так, после пуска блока 49 управления на первом проходе распределителя 69 импульсов блока 49 управления на регистр 45 арифметического устройства заносится (0) и Сд у(С))с- На N-M проходе распределителя 69 импульсов 3-м импульсом блока 49 управления в регистр 45

арифметического устройства заносятс

N-f

величины А |,)j 21 х(п) и С, ы-1

Z

П 0

бой действительную н мнимую части пулевого коэффициента Фурье. 4-й ш.1пульс блока 49 управления, пройдя элемент 53 совпадения заносит эти величины в выходной регистр 4,, набо ра 4, 5-й импульс прибавляет 1 к счетчику 50, на выходе переполнения которого образуется импульс, прибавляемый к счетчику 51, определяющему номер коэффициента Фурье К. Следующие N проходов распределителя 69 импульсов блока 49 управления формируют действительную и мнимую части первого коэффициента Фурье (k 1), которые заносятся в соответствующий регистр набора 4 (4() импульсом с выхода схемы 53 совпадения. После вычисления всех N коэффициентоз Фур импульс переполнения с датчи 51 устанавливает в О триггер 68 блока 49 управления, запрещая работ распределителя 69 импульсов.

5

о

5

5

0

0

S

(1

Запоминание полученных коэффициентов Фурье комплексного сигнала, несущих информацию о фазовом сдвиге в каясдой гармонике, позволяет вычислять фазовые сдвиги раздельно для различных гармоник входного сигнала. Исключение повторного запуска процессора ДПФ ДД1Я вычисления фазового сдвига в последующих гармониках позволяет сократить по сравнению с известным устройством время вычисления фазовых сдвигов.

Формула изобретения

Устройство для измерения фазовых сдвигов, содержащее умножители, блок деления, генератор, отличающееся тем, что, с целью расширения частотного диапазона и функциональных возможностей за счет обеспечения раздельного измерения фазовьпс сдвигов основного сигнала и его гармонических составляющих в него введены аналого-цифровые пре- обрс13ователи, процессор дискретного преобразования Фурье, регистры,муль- типхшксоры, квадраторы, сумматор, вычи:татель, блок вычисления арксинуса, блок задания номера гармоники, вольтметры, блок управления, элемент совпадения, триггер, счетчик преобразователь интервал-напряжение, линии задержки, при этом информационные входы первого и второго аналого-цифровых преобразователей, являющиеся входами устройства подключены соответственно к входам первого и второго вольтметров, а выходы соединены с соответствующими информационными входами процессора дискретного преобразования Фурье, информационный выход которого соединен с объединенными информационными входами набора выходных регистров, управляющий вход каждого из которых подк.гаочен к соответствующему управляющему выходу процессора дискретного преобразования Фурье, выходы L старших разрядов каждого выходного регистра соединены с соответствующими информационными входами первого мультиплексора, а выходы L младших разрядов каждого выходного регистра соединены с соответструющи- ми информационными входами второго мультиплексора, объединенные управляющие входы обоих мультиплексоров соединены с первьгм выходом блока

11

управления, а выход каящого мультиплексора подключен к входу соответствующего квадратора, выходы которых соединены с входами сумматора,подсоединенного своим выходом к объединенным информационным входам двух промежуточных регистров, управляющие входы которых соединены соответственно с вторыми и третьим выходами блока управления, а выходы регистров подключены к соответствзгющим входам вычитателя, выход которого соединен с входом делимого блока деления, вход делителя которого подключен к выходу регистра делитeляj а выход через блок вычисления арксинуса подключен к информационному входу регистра результата, управляющий вход которого соединен с четвертым вьЕходом блока управления, соединенного управляющим входом с выходом блока задания номера гармоники, выход каждого из вольтметров соединен с соответствующим входом первого умножителя, выход которого подключен к первойу входу второго умножителя, соединенного выходом с

34112

информационным входом третьего аналого-цифрового преобразователя,выход которого подключен к информационному входу регистра делителя, управляю- щий вход которого через первую линию задержки соединен с управляющим входом третьего аналого-цифрового преобразователя, и через вторую линию задержки соединен с нулевым установочньм входом триггера и -выходом переполнения счетчика, управляющий вход которогЪ соединен с первым управляющим входом процессора дискретного преобразования Фурье

и единичным входом триггера, а счетный вход счетчика подключен к объединенным управляющим входам первого и второго аналого-цифрового преобразователя, к второму управляющему

входу указанного процессора и выходу элемента совпадения, один из входов которого подключен к выходу генератора, а второй - к прямому выходу триггераи входупреобразователя

интервал-напряжение, выход которого черей третий квадратор подключен к второму входувторого умножителя.

Ф11г.г

Редактор Н. Яцола

Составитель В. Шубин

Техред Л.Олейник Корректор А. Тяско

Заказ 2126/43 Тираж 728 , Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие:, г, Ужгород, ул. Проектная,4

| название | год | авторы | номер документа |

|---|---|---|---|

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ДЛЯ ВЫПОЛНЕНИЯ ДИСКРЕТНОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ | 1991 |

|

RU2015550C1 |

| Устройство для вычисления ядер Винера нелинейных объектов | 1984 |

|

SU1196896A1 |

| Устройство для вычисления коэффициентов Фурье | 1985 |

|

SU1283790A1 |

| Цифровой спектроанализатор | 1982 |

|

SU1092518A1 |

| Субоптимальный нелинейный фильтр | 1990 |

|

SU1714618A1 |

| Устройство для вычисления коэффициентов Фурье | 1985 |

|

SU1290351A1 |

| Цифровой анализатор спектра | 1985 |

|

SU1322172A1 |

| Цифровой обнаружитель-измеритель частоты | 1989 |

|

SU1797127A1 |

| Устройство для вычисления коэффициентов Фурье | 1985 |

|

SU1273944A1 |

| Устройство для измерения электромагнитных параметров объемных экранов | 1983 |

|

SU1228150A1 |

Изобретение может быть использовано для помехоустойчивого измерения сдвига фаз в радиотехнических и измерительных устройствах. Устройство содержит згмножители 27 и 29, блок 13 деления и генератор 19.Введение в устройство аналого-цифровых преобразователей 1, 2 и- 29, процессора 3 дискретного преобразования Фурье, регистров 4, мультиплексоров 5 и 6, квадраторов 7 и 8, сумматора 9, вычитателя 12, блока 15 вычисления арксинуса, блока 18 задания номера гармоники, вольтметров 25 и 26, бло ка 17 управления, элемента 20 совпадения, триггера 21, счетчика 22, преобразователя 23 интервал-напряжение, линий задержки 30 и 31 и образование новых связей между элементами устройства обеспечило возможность раздельного измерения фазовых сдвигов основного сигнала и его гармонических составляющих за счет запоминания полученных коэффициентов Фурье комплексного сигнала, несущик информацию о фазовом сдвиге в каждой гармонике.. 5 шт. i (Л IFT JO Фиг.1

| Цифровой корреляционный фазометр | 1980 |

|

SU943598A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| СПОСОБ ИЗМЕРЕНИЯ РАЗНОСТИ ФАЗ ГАРМОНИЧЕСКИХСИГНАЛОВ | 0 |

|

SU174711A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1986-04-23—Публикация

1984-11-22—Подача