10

20

11257849

Изобретение относится к автоматике и вьгчислйтельной технике и может быть использовано.в устройствах цифровой обработки случайных стационарных процессов в качестве модулятора для цифровых фильтров и корреляторов.

Цель изобретения - повьппение надежности функционирования и достоверности преобразования,

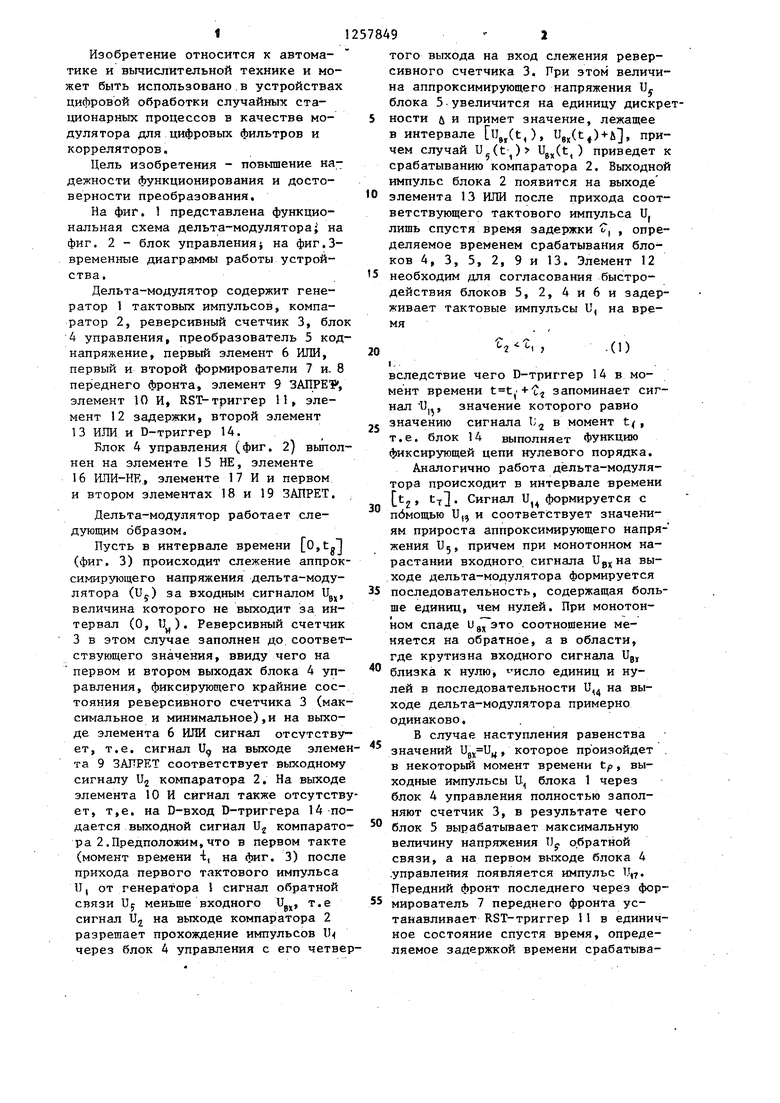

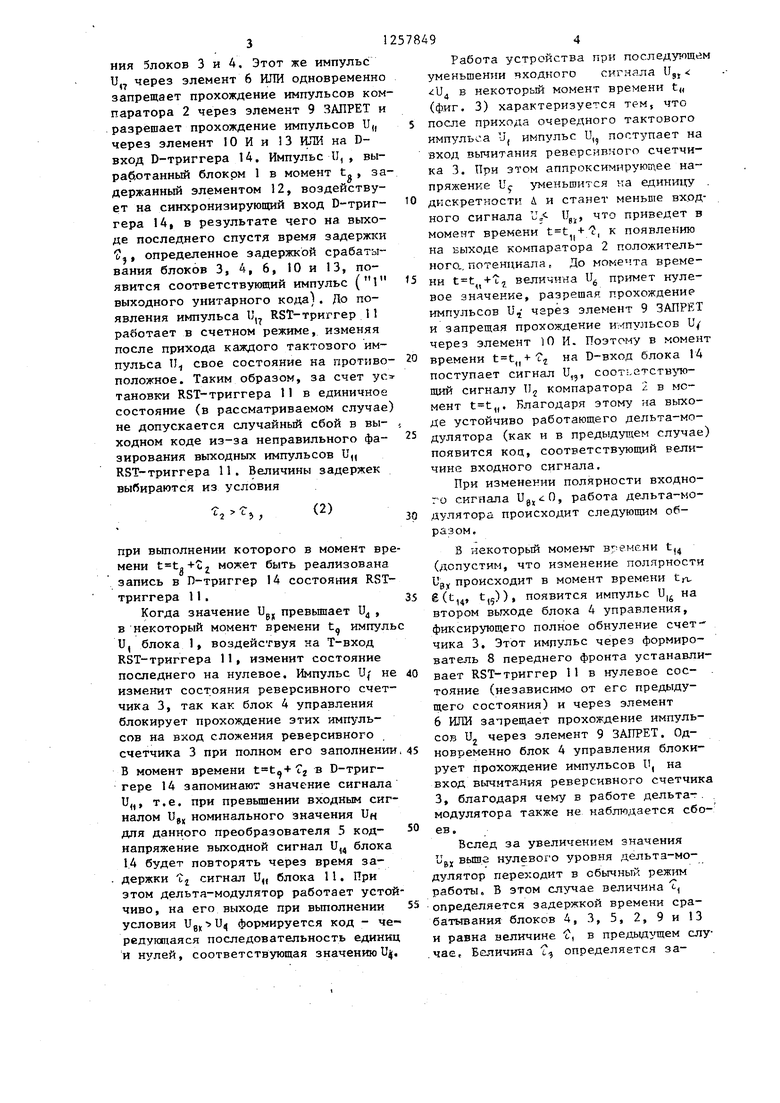

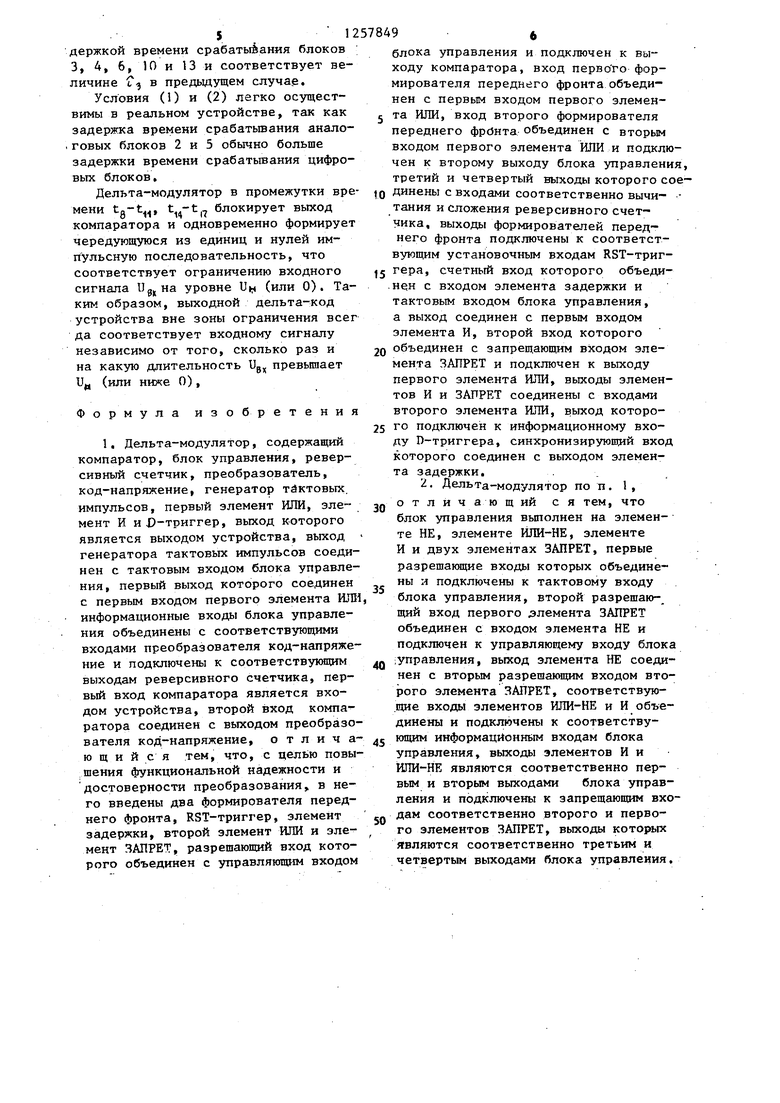

На фиг. 1 представлена функциональная схема дельта-модулятора на фиг. 2 - блок управленияi на фиг.З- временные диаграммы работы устройства.

Дельта-модулятор содержит генератор 1 тактовых импульсов, компаратор 2, реверсивный счетчик 3, блок 4 управления, преобразователь 5 код- напряжение, первый элемент 6 ИЛИ, первый и второй формирователи 7 и, 8 переднего фронта, элемент 9 ЗАПРЕ , элемент 10 И, RST-триггер 11, элемент 12 задержки, второй элемент 13 ИЛИ и D-триггер 14.

Блок 4 управления (фиг. 2) выполнен на элементе 15 НЕ, элементе 16 ИЛИ-НЕ., элементе 17 И и первом и втором элементах 18 и 19 ЗАПРЕТ.

Дельта-модулятор работает следующим образом.

Пусть в интервале времени 0,tg (фиг. 3) происходит слежение аппроксимирующего напряжения дельта-модулятора (Uy) за входным сигналом U, величина которого не выходит за интервал (О, L ). Реверсивный счетчик 3 в этом случае заполнен до соответствующего значения, ввиду чего на первом и втором выходах блока 4 управления, фиксирующего крайние состояния реверсивного счетчика 3 (максимальное и минимальное),и на выходе элемента 6 ИЛИ сигнал отсутствует, т.е. сигнал U на выходе элемента 9 3AJTPET соответствует выходному сигналу Uj компаратора 2. На выходе элемента 10 И сигнал также отсутствует, т,е. на D-вход D-триггера 14 потого выхода на вход слежения реве сивного счетчика 3, При этом вели на аппроксимирующего напряжения U блока 5 увеличится на единицу дис ности U и примет значение, лежаще в интервале Ug,(t,), Uj(t) + u, п чем случай U(t) Ug,(t, ) приведе срабатыванию компаратора 2. Выход импульс бпока 2 появится на выход элемента 13 ИЛИ после прихода со ветствующего тактового импульса U лишь спустя время задержки о, , оп деляемое временем срабатывания бл ков 4, 3, 5, 2, 9 и 13, Элемент 1 5 необходим для согласования быстро действия блоков 5, 2, 4 и 6 и зад живает тактовые импульсы U, на вр мя

30

35

40

45

г.

1 J

.(1)

вследствие чего D-триггер 14 в мо мент времени запоминает с нал U , значение которого равио 25 значению сигнала iJj в момент t , т,е. блок 14 выполняет Функцию фиксирующей цепи нулевого порядка

Аналогично работа дельта-модул тора происходит в интервале време t, t-f3« Сигнал и формируется с пбмощью и, и соответствует значен ям прироста аппроксимирующего нап жения Uj, причем при монотонном н растании входного сигнала в ходе дельта-модулятора формируетс последовательность, содержащая бо ше единиц, чем нулей. При монотон ном спаде и и, это соотношение ме 8Х

няется на обратное, а в области, где крутизна входного сигнала Uj, близка к нулю, иcлo единиц и нулей в последовательности U на вы ходе дельта-модулятора примерно одинаково,

В случае наступления равенства значений , которое произойде в некоторый момент времени tp, вы ходные импульсы и блока 1 через блок 4 управления полностью запол няют счетчик 3, в результате чего

дается выходной сигнал Uj, компарато- 50 5 вырабатывает максимальную

величину напряжения Uj, обратной

ра 2.Предположим,что в первом такте (момент времени i, на фиг. 3) после прихода первого тактового импульса и, от генератора 1 сигнал обратной связи Uy меньше входного U, т,е сигнал Uj на выходе компаратора 2 разрешает прохождение импульсов И через блок 4 управления с его четверсвязи, а на первом выходе блока 4 управления появляется импульс U,7. Передний фронт последнего через ф 55 мирователь 7 переднего фронта устанавливает RST-триггер 11 в един ное состояние спустя время, опред ляемое задержкой времени срабатыв

того выхода на вход слежения реверсивного счетчика 3, При этом величина аппроксимирующего напряжения U, блока 5 увеличится на единицу дискретности U и примет значение, лежащее в интервале Ug,(t,), Uj(t) + u, причем случай U(t) Ug,(t, ) приведет к срабатыванию компаратора 2. Выходной импульс бпока 2 появится на выходе элемента 13 ИЛИ после прихода соответствующего тактового импульса U, лишь спустя время задержки о, , определяемое временем срабатывания блоков 4, 3, 5, 2, 9 и 13, Элемент 12 необходим для согласования быстродействия блоков 5, 2, 4 и 6 и задерживает тактовые импульсы U, на время

20

г.

1 J

.(1)

вследствие чего D-триггер 14 в момент времени запоминает сигнал U , значение которого равио значению сигнала iJj в момент t , т,е. блок 14 выполняет Функцию фиксирующей цепи нулевого порядка.

Аналогично работа дельта-модулятора происходит в интервале времени t, t-f3« Сигнал и формируется с пбмощью и, и соответствует значениям прироста аппроксимирующего напряжения Uj, причем при монотонном нарастании входного сигнала выходе дельта-модулятора формируется последовательность, содержащая больше единиц, чем нулей. При монотонном спаде и и, это соотношение ме 8Х

няется на обратное, а в области, где крутизна входного сигнала Uj, близка к нулю, иcлo единиц и нулей в последовательности U на выходе дельта-модулятора примерно одинаково,

В случае наступления равенства значений , которое произойдет в некоторый момент времени tp, выходные импульсы и блока 1 через блок 4 управления полностью заполняют счетчик 3, в результате чего

5 вырабатывает максимальную

величину напряжения Uj, обратной

связи, а на первом выходе блока 4 управления появляется импульс U,7. Передний фронт последнего через фор- 55 мирователь 7 переднего фронта устанавливает RST-триггер 11 в единичное состояние спустя время, определяемое задержкой времени срабатыва3

ния Злоков 3 и 4, Этот же импульс и, через элемент 6 ИЛИ одновременно запрещает прохождение импульсов компаратора 2 через элемент 9 ЗАПРЕТ и разрешает прохождение импульсов U(, через элемент 10 И и 3 ИЛИ на D- вход D-триггера 14, Импульс U, , выработанный блоком 1 в момент t. , задержанный элементом 12, воздействует на синхронизирующий вход D-триггера 14, в результате чего на выходе последнего спустя время задержки , определенное задержкой срабатывания блоков 3, 4, 6, Юн 13, появится соответствующий импульс (1 выходного унитарного кода). До появления импульса и, RST-триггер 11 работает в счетном режиме, изменяя после прихода каждого тактового им

щий сигналу Uj компаратора 2 в момент ... Благодаря этому на выхопульса П свое состояние на противо- 20 времени ,, Т на D-вход блока 14 положное. Таким образом, за счет ус поступает сигнал U,, соотьетств то- тановки RST-триггера 11 в единичное состояние (в рассматриваемом случае) не допускается случайный сбой в вы- ,, де устойчиво работающего дельта-мо- ходном коде из-за неправильного фа- 25 дулятора (как и в предыдущем случае)

появится код, соответствующий величине входного сигнала.

При изменении полярности входного сигнала , работа дельта-мо- 30 дулятора происходит следующим образом.

зирования выходных импульсов U,, RST-триггера П. Величины задержек выбираются из условия

Ъ }

(2)

при вьтолнении которого в момент времени может быть реализована запись в П-триггер 14 состояния RST- триггера 11.

Когда значение U,, превьщ1ает U ,

В некоторый момент в : емени t, (допустим, что изменение полярности Ugj происходит в момент времени tn, 35 (t,4 15) появится импульс U| на втором выходе блока 4 управления.

в некоторый момент времени t, импульс фиксирующего полное обнуление счет- и, блока 1, воздействуя на Т-вход 3. Этот импульс через формиро- RST-триггера 11, изменит состояние ватель 8 переднего фронта устанавли- последнего на нулевое. Импульс U( не 40 вает RST-триггер 11 в нулевое сое- . изменит состояния реверсивного счет- тояние (независимо от его предыду- чика 3, так как блок 4 управления состояния) и через элемент блокирует прохождение этих импульсов на вход сложения реверсивного

счетчика 3 при полном его заполнении,45 повременно блок 4 управления блоки- В момент времени в D-триг- рует прохождение импульсов U, на гере 14 запоминают значение сигнала и„, т.е. при превышении входным сигналом UjK номинального значения UH для данного преобразователя 5 код- 50 напряжение выходной сигнал U, блока 1.4 будет повторять через время задержки i: J сигнал и„ блока 11. При этом дельта-модулятор работает устойчиво, на его выходе при вьтолнении 55 определяется задержкой времени ера- условия формируется код - че- батывания блоков 4, 3, 5, 2, 9и13 редугадаяся последовательность единиц и нулей, соответствующая значению U.

6 ИЛИ запрещает прохождение импульсов Uj через элемент 9 ЗАПРЕТ. Одвход вычитания реверсивного счетчика 3, благодаря чему в работе дельта-г. модулятора также не наблюдается сбо ев.

Вслед за увеличением значения LJ(j,( выше нулевого уровня дельта-модулятор переходит в обычный режим работы. В этом случае величина

и равна величине t, в предыдущем слу- .чае. Величина ц определяется за4

Работа устройства при последующем уменьшении входного сигнала IJjj : iU в некоторый момент времени t, (фиг. 3) характеризуется тем, что после прихода очередного тактового импульса Uj импульс U, поступает на вход вычитания реверсивного счетчика 3. При этом аппроксимнруюпт,ее напряженке Lb уменьшится на единицу . дискретности Д и станет меньше входного сигнала 11, что приведет в момент времени «- г, к появлению на выходе компаратора 2 положительного., потенциала, До времени величина U примет нулевое значение, разрешая прохождение импульсов и через элемент 9 ЗАПРЕТ и запрещая прохождение импульсов U| через элемент 10 И. Поэтому в момент

щий сигналу Uj компаратора 2 в момент ... Благодаря этому на выховремени ,, Т на D-вход блока 14 поступает сигнал U,, соотьетств то- де устойчиво работающего дельта-мо- дулятора (как и в предыдущем случае)

В некоторый момент в : емени t, (допустим, что изменение полярности Ugj происходит в момент времени tn, (t,4 15) появится импульс U| на втором выходе блока 4 управления.

фиксирующего полное обнуление счет- 3. Этот импульс через формиро- ватель 8 переднего фронта устанавли- вает RST-триггер 11 в нулевое сое- тояние (независимо от его предыду- состояния) и через элемент

фиксирующего полное обнуление счет- 3. Этот импульс через формиро- ватель 8 переднего фронта устанавли- вает RST-триггер 11 в нулевое сое- тояние (независимо от его предыду- состояния) и через элемент

повременно блок 4 управления блоки- рует прохождение импульсов U, на определяется задержкой времени ера- батывания блоков 4, 3, 5, 2, 9и13

6 ИЛИ запрещает прохождение импульсов Uj через элемент 9 ЗАПРЕТ. Одповременно блок 4 управления блоки- рует прохождение импульсов U, на определяется задержкой времени ера- батывания блоков 4, 3, 5, 2, 9и13

вход вычитания реверсивного счетчика 3, благодаря чему в работе дельта-г. модулятора также не наблюдается сбоев.

Вслед за увеличением значения LJ(j,( выше нулевого уровня дельта-модулятор переходит в обычный режим работы. В этом случае величина

повременно блок 4 управления блоки- рует прохождение импульсов U, на определяется задержкой времени ера- батывания блоков 4, 3, 5, 2, 9и13

и равна величине t, в предыдущем слу- .чае. Величина ц определяется за$ 1257849

ержкой времени срабатывания блоков ; , 4, 6,10 и 13 и соответствует веичине С предыдущем случае.

Условия (1) и (2) легко осущестимы в реальном устройстве, так как задержка времени срабатьшания анало- овых блоков 2 и 5 обычно больше задержки времени срабатьшания цифровых блоков.

Дельта-модулятор в промежутки времени tg-Ц, блокирует выход компаратора и одновременно формирует чередующуюся из единиц и нулей импульсную последовательность, что соответствует ограничению входного

сигнала ПдцНа уровне Ui (или 0). Таким образом, выходной дельта-код устройства вне зоны ограничения всег да соответствует входному сигналу независимо от того, сколько раз и на какую длительность Ug превьппает DI, (или ниже 0),

Формула изобретения

1. Дельта-модулятор, содержащий компаратор, блок управления, реверсивный счетчик, преобразователь, код-напряжение, генератор тйктовых, импульсов, первый элемент ИЛИ, элемент И иР-триггер, выход которого является выходом устройства, выход генератора тактовых импульсов соединен с тактовым входом блока управления, первый выход которого соединен с первым входом первого элемента HJHi, информационные входы блока управления объединены с соответствующими входами преобразователя код-напряжение и подключены к соответствующим выходам реверсивного счетчика, первый вход компаратора является входом устройства, второй вход компаратора соединен с выходом преобразователя код-напряжение, отличающийся тем, что, с целью повышения функциональной надежности и достоверности преобразования, в него введены два формирователя переднего фронта, RST-триггер, элемент задержки, второй элемент ИЛИ и элемент ЗАПРЕТ, разрешаюшлй вход которого объединен с управляющим входом

х м н 5 т п в ч т

0 д т ву

5 ге .н т а эл

20 о м п то в

25 г д к т

;у .щ ю л

30

35

40

45

50

блока управления и подключен к выходу компаратора, вход перво го формирователя переднего фронта объединен с первым входом первого элемен- 5 та ИЛИ, вход второго формирователя переднего фронта объединен с вторым входом первого элемента ИЛИ и подключен к второму выходу блока управления, третий и четвертый выходы которого сое0 динены с входами соответственно вычи- тания и сложения реверсивного счетчика, выходы формирователей переднего фронта подключены к соответствующим установочным входам RST-триг5 гера, счетный вход которого объеди- .нен с входом элемента задержки и тактовым входом блока управления, а выход соединен с первым входом элемента И, второй вход которого

0 объединен с запрещающим входом элемента ЗАПРЕТ и подключен к выходу первого элемента ИЛИ, выходы элементов И и ЗАПРЕТ соединены с входами второго элемента ИЛИ, выход которо5 го подключен к информационному входу D-триггера, синхронизирующий вход которого соединен с выходом элемента задержки. .

2. Дельта-модулятор по п. 1, о т л и ч а ю щ ий с я тем, что блок управления выполнен на элементе НЕ, элементе ШШ-НЕ, элементе И и двух элементах ЗАПРЕТ, первые разрешающие входы которых объедине ны и подключены к тактовому входу блока управления, второй разрешаю- щий вход первого элемента ЗАПРЕТ объединен с входом элемента НЕ и подключен к управляющему входу блока ;управления, выход элемента НЕ соединен с вторым разрешающим входом второго элемента ЗАПРЕТ, соответствую- .щие входы элементов ИЛИ-НЕ и И объединены и подключены к соответствующим информационным входам блока управления, выходы элементов И и ИПИ-НЕ являются соответственно первым и вторым выходами блока управления и подключены к запрещающим входам соответственно второго и первого элементов ЗАПРЕТ, выходы которых являются соответственно третьим и четвертым выходами блока управления.

0

5

5

0

fpue.Z

111101011010

Редактор М.Петрова

Составитель О.Ревинский

Техред И.ВересКорректор М.Максимишинец

Заказ 5041/58Тираж 816 . Подписное

ВНИИПИ Государственного комитета CLOF

по делам изобретений и открытий ПЗП35, Москва, К-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

00 10101110

фиё.З

| название | год | авторы | номер документа |

|---|---|---|---|

| Дельта-модулятор | 1986 |

|

SU1388992A1 |

| Дельта-модулятор | 1988 |

|

SU1510090A2 |

| Дельта-модулятор | 1987 |

|

SU1448411A1 |

| Дельта-модулятор | 1987 |

|

SU1508350A2 |

| Дельта-модулятор | 1986 |

|

SU1345349A2 |

| Дельта-модулятор | 1989 |

|

SU1649666A1 |

| Дельта-модулятор | 1990 |

|

SU1718383A1 |

| Дельта-модулятор | 1990 |

|

SU1709531A2 |

| Цифровой фильтр с дельта-модуляцией | 1985 |

|

SU1347188A1 |

| Цифровой фильтр с линейной дельта-модуляцией | 1988 |

|

SU1589383A1 |

Изобретение относится к автоматике и вычислительной технике. Его применение в устройствах цифровой обработки случайных стационарных процессов позволяет повысить надежность функционирования устройства и достоверность преобразования информации. Дельта-модулятор содержит генератор тактовых импульсов, компаратор, блок управления, реверсивный счетчик, преобразователь код-напряжение, D-триг- гер, первый элемент ИЛИ, элемент И и элемент задержки. Благодаря введению RST-триггера, двух формирователей переднего фронта, элемента ЗАПРЕТ и второго элемента ИЛИ дельта- модулятор при воздействии на него сигнала, выходящего за пределы динамического диапазона, формирует сигнал, соответствующий этим преде- лам, т.е. осуществляеэт цифровое ограничение кратковременных выбросов входного сигнала 1 з.п. ф-лы, 3 ил.

| Устройство для передачи сигналов с дельта-модуляцией и мгновенным компандированием | 1977 |

|

SU641648A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Дельта-кодер | 1981 |

|

SU953725A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1986-09-15—Публикация

1985-03-25—Подача