iV/V-1. .F

f Чл -ч Т i -cjf if)

: и -Ч.

| название | год | авторы | номер документа |

|---|---|---|---|

| Динамический триггер А.С.Гребнева | 1982 |

|

SU1058074A1 |

| Формирователь одиночных импульсов | 1983 |

|

SU1160548A1 |

| ТРИГГЕРНОЕ УСТРОЙСТВО | 2002 |

|

RU2237354C2 |

| ТРИГГЕРНОЕ УСТРОЙСТВО | 2002 |

|

RU2224357C2 |

| Аналоговое запоминающее устройство | 1979 |

|

SU822295A1 |

| ЗАДАЮЩИЙ ГЕНЕРАТОР ПРЕОБРАЗОВАТЕЛЯ НАПРЯЖЕНИЯ | 2022 |

|

RU2784620C1 |

| Формирователь дискретных сигналов | 1979 |

|

SU809523A1 |

| ИСТОЧНИК ПИТАНИЯ ДЛЯ ЭЛЕКТРОЛЮМИНЕСЦЕНТНОЙ ПАНЕЛИ | 2001 |

|

RU2210120C1 |

| Одновибратор | 1983 |

|

SU1129716A1 |

| ТАЙМЕР С КОНТРОЛЕМ | 1990 |

|

RU2037872C1 |

ФОРМИРОВАТЕЛЬ ЛИСКР ГНЖ СИГНАЛОВ, содержащий D-rpHrrGj;- :-4i формационным входом подкл;о--е к ;; к шине входных сигналов, первый кокденсаторг первый и второй диоды, ГТЕОвый и второй резивторЫ; первый резистор подключен к катоду первого диода, а второй резистор - к аноду второго диода катод которого соединен с одной обкладкой первого короденсатора, отличающийся тем, ЧТО; с целью повышения надежности, в него введены второй конденсатор, третий и четвертый диоды,причем анод третьего диода подключен к аноду второго диода и соединен с тактовым входом В-триггера, катод четвертого диода подключен к катоду первого дио3; анод которого соединен с катоом второго диода, катод третьего иода соединен с анодом четвертого иода и через второй конденсатор с улевым выходом В-триггера, единичьлй выход которого подключен к второй обкладке первого конденсатора, два других вывода первого и второрезисторов подключены к источнику тания

.....

е

CTDФи8.1

f11

Изобретение относится к импульсной технике и может использоваться в устройствах обработки лискрет ой информавди при наличии помех на фронтах импульсов, и.апример в устройствах

ввода информаили устранения влияния дребезга контактов на электронные .

Известно устройство ;тля формирования импульсов, содержап ее два триггера, инвертор, элемент задержки и элемент СП.

Недостатком данного устройства является ТО; чтс точность воспроизведения временного положения фронтов . sxoAisoro сигнала сохраняется только в случае возникновения помех на заднем фропте имлульсов.

Наиболее б1гизкнм по технической сущности и достигаемому результату к предлагаемому является формирователь .дискретных сигналов, содержагляй В-триггер, двухтзходовый элемент И-ИЕ н Брс-:мязадающий контур, вьтолнен}1ый на ко1 денсаторе,, резисторах и диодах, причем ьчина входных сигналов подключеJ I- JO ц о ио- входу Г -тригт юа

I 1 леяым выходами

к о т ор ( Г о и кл i04 н вр е мя з а да ющи и к о нт ур с гсон/1енсатороМэ обкладки которого соединены соответствонио с Д1Амя вхо. злеманта И-НЕ, ргиход которого

сор/лпне с тактовым УХОДОМ Dгригге-ра f .:

ie;i, язвестното формирова-теля янт;яется низкая надежность, поско:1ьку i aiipHseчио ма входах логическог-о -элемента превышает капряжепие питангЯ и наличие дребезга на фронте ныхо;,г1ого сигнала

цс-ль изобретения повьгаетае надеж; :; и формирователя ,

Пос авлекиа;: цель достигается тем. что в формироватвль дискретных сигнатриггер 5 информационным входом подключенный к шине вкодньпс сигналов, первый конденсатор, первьгй и второй диоды и первьш и второй резисторы, первый резистор подключен к катоду первого диода, а второй резистор - к аноду второго диодаj катод которого соедд-знен с одной обкладкой первого конденсатора, введены второй конденсатор, третий и четвертый диоды, причем анод третьего диода подтспючен к аноду второго диода и соединен с тактовым входом Dтриггера, катод четвертого диода под02

ключе} к катоду первого диода, анод которого соединен с катодом второго диода, катод третьего диода соединен с анодом четвертого диода и чере;; второй кон ченсатор с нулевым выходом В-триггера, единичный вьгход которого подключен к второй обкладке первого конденсатора, а два других вывода первого и второго резисторов подключены к источнику питания.

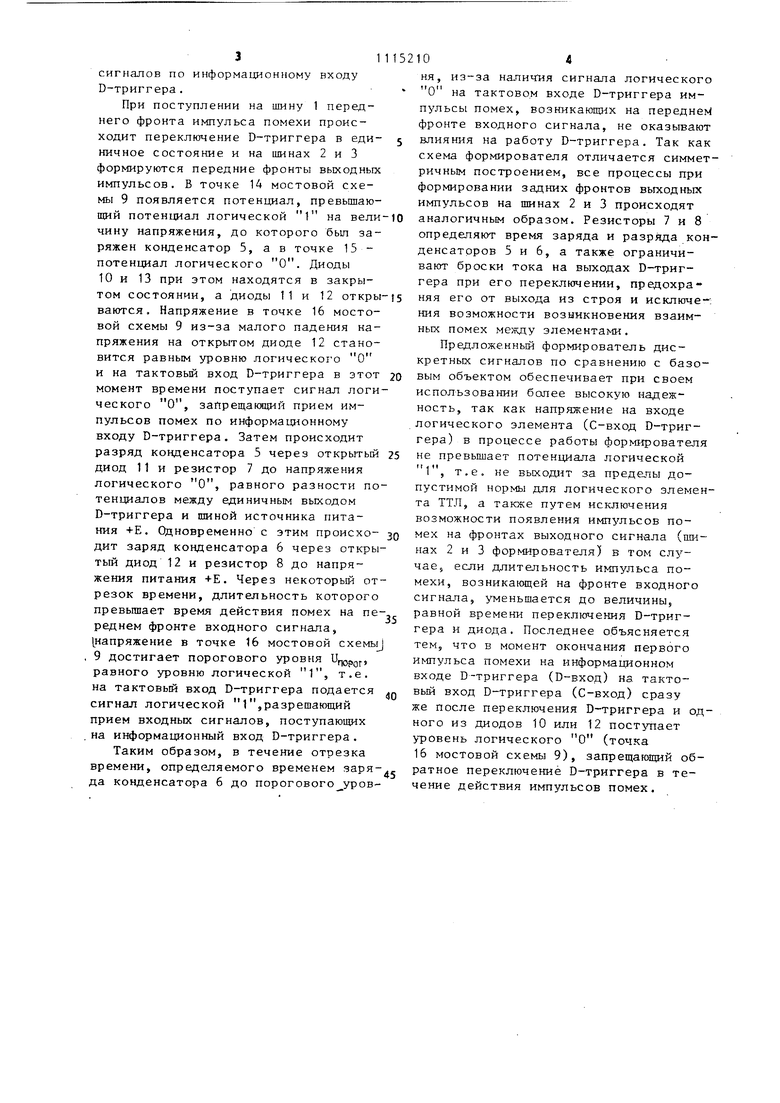

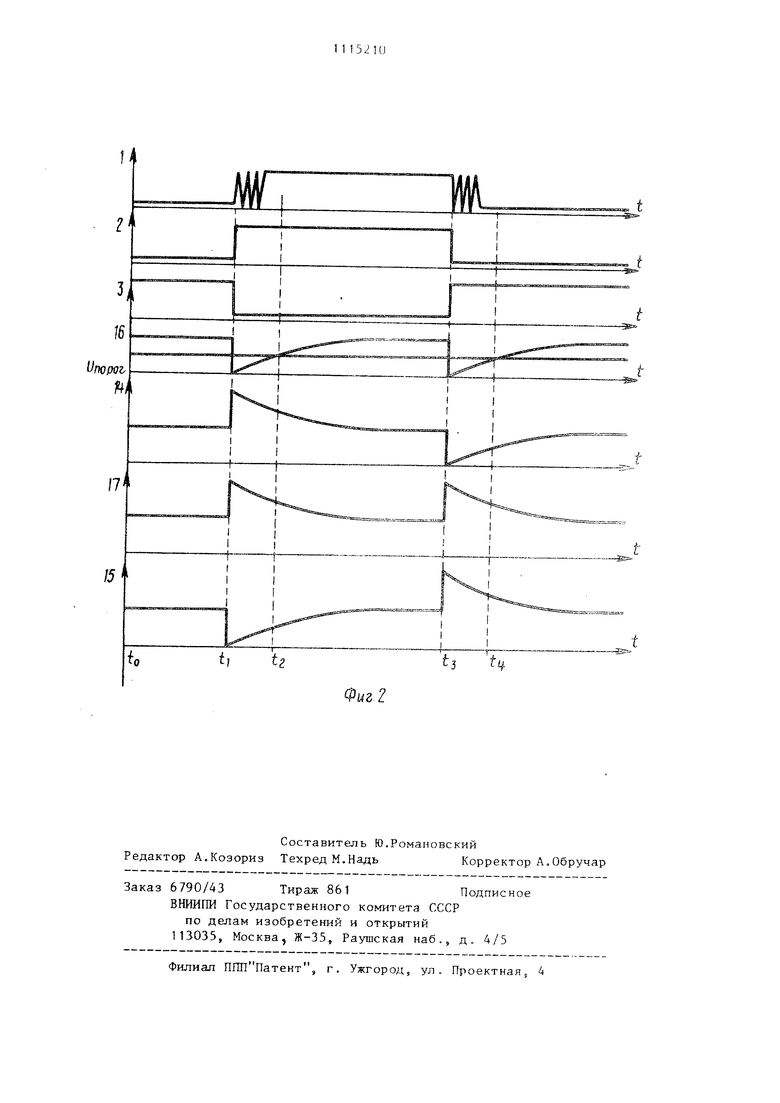

На фиг. 1 представлена принципиальная схема формирователя дискретных сигналов; на фиг. 2 - эпюры напряжений .

Формирователь содержит шину 1 входньк сигналов, шины 2 и 3 выходных: сигналов, D-триггер 4, первьй 5 и ; торой 6 конденсаторы, первый 7 и второй 8 резисторы, мостовую схему 9 из второго 10, первого 11, третьего 12 и четвертого 13 диодов и точки 14-17 мостовой схемы 9.

Информац онный вход D-триггера 4 подключен к шине 1 входных сигналов. Выходные шины 2 и 3 соединены соответственно с единичньгм и нулевым выходами D-триггера, Един.ичный выход D-триггера через конденсатор 5 подключен к аноду диода 11 и к катоду диода Ю, а нулевой выход В-триггерг через второй конденсатор 6 - к катоду диода 12 и к аноду диоца 13. Ратод диода 1 1 соединен с катодом диода 13 и через резистор 7 с источ;гиком питания. Анод диода 10 соединен с ан9дом диода 12 с тактовым входом D-триггера и через резистор 8 с источником питания.

Формирователь дискретных сигналов работает следующим образом.

В исходном состоянии на шине 1 присутствует уровень логического О. D-триггер 4 установлен в нулевое состояние, т.е. на шину 2 поступает уровень логического О, а на шину 3 - уровень логической 1. Конденсатор 5 заряжен через резистор 8 и диод Ш до напряжения источника питания . Конденсатор 6 находится под напряжением близким к нулевому, так как на одну обкладку конденсатора 6 поступает уровень логической 1 с нулевого выхода D-триггера, а на другую его обкладку через резистор 8 и диод 12 - напряжение питания -Е. На тактовый вход D-триггера через резистор 8 подается потенциал логической

, разрешающий прием входных 31 сигналов по информационному входу D-триггера. При поступлении на шину 1 переднего фронта импульса помехи происходит переключение D-триггера в едияичное состояние и на шинах 2 и 3 формируются передние фронты выходных импульсов, В точке 14 мостовой схемы 9 появляется потенциал, превышающий потенциал логической 1 на вели чину напряжения, до которого был заряжен конденсатор 5, а в точке 15 потенциал логического О. Диоды 10 и 13 при этом находятся в закрытом состоянии, а диоды 11 и 12 откры ваются. Напряжение в точке 16 мостовой схемы 9 из-за малого падения напряжения на открытом диоде 12 становится равным уровню логического О и на тактовый вход D-триггера в этот момент времени поступает сигнал логи ческого О, запрещающий прием импульсов помех по информационному входу D-триггера. Затем происходит разряд конденсатора 5 через открытьй диод 11 и резистор 7 до напряжения логического О, равного разности по тенциалов между единичным выходом D-триггера и шиной источника питания +Е. Одновременно с этим происходит заряд конденсатора 6 через откры тый диод 12 и резистор 8 до напряжения питания +Е. Через некоторый от резок времени, длительность которого превышает время действия помех на пе реднем фронте входного сигнала, |напряжение в точке 16 мостовой cxeMb , 9 достигает порогового уровня Uriopor равного уровню логической 1, т.е. на тактовый вход D-триггера подается сигнал логической 1,разрешающий прием входных сигналов, поступающих .на информационный вход D-триггера. Таким образом, в течение отрезка времени, определяемого временем заря да конденсатора 6 до порогового уров 104 ня, из-за наличия сигнала логического О на тактовом входе D-триггера импульсы помех, возникающих на переднем фронте входного сигнала, не оказывают влияния на работу D-триггера. Так как схема формирователя отличается симметричным построением, все процессы при формировании задних фронтов выходных импульсов на шинах 2 и 3 происходят аналогичным образом. Резисторы 7 и 8 определяют время заряда и разряда конденсаторов 5 и 6, а также ограничивают броски тока на выходах D-триггера при его переключении, предохраняя его от выхода из строя и исключе-: ния возможности возникновения взаимных помех между элементами. Предложенный формирователь дискретных сигналов по сравнению с базовым объектом обеспечивает при своем использовании более высокую надежность, так как напряжение на входе логического элемента (С-вход D-триггера) в процессе работы формьгрователя не превышает потенциала логической 1, т.е. не выходит за пределы допустимой нормы для логического элемента ТТЛ, а также путем исключения возможности появления импульсов помех на фронтах выходного сигнала (пшнах 2 и 3 формирователя) в том случае, если длительность импульса помехи, возникающей на фронте входного сигнала, уменьшается до величины, равной времени переключения D-триггера и диода. Последнее объясняется тем, что в момент окончания первого импульса помехи на информационном входе D-триггера (D-вход) на тактовый вход D-триггера (С-вход) сразу же после переключения D-триггера и одного из диодов 10 или 12 уровень логического О (точка 16 мостовой схемы 9), запрещающий обратное переключение D-триггера в течение действия импульсов помех.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| 8СЕСОЮЗМАЯ i | 0 |

|

SU373864A1 |

| Способ утилизации отработанного щелока из бучильных котлов отбельных фабрик | 1923 |

|

SU197A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Способ изготовления электрических сопротивлений посредством осаждения слоя проводника на поверхности изолятора | 1921 |

|

SU19A1 |

Авторы

Даты

1984-09-23—Публикация

1982-07-05—Подача