сивного счетчика, информационные входы которого соединены с соответствующими выходами задатчика начального кода,R -вход соединен с общей шиной устройства, прямые выходы соединены с соответствующими входами дешифратора, выход младшего разряда дешифратора соединен с первым входом пятого элемента И, группа старших выходов с соответствующими входами первого элемента ИЛИ, выход которого соединен с первым входом второго элемента ИЛИ и с вторым входом пятого элемента И, соединенного выходом с вторым входом второго элемента ИЛИ,выход которого соединен с первым входом шестого элемен та И,соединенного вторым входом с прямым выходом четвертого Т) -триггера и с первы входом третьего элемента ИЛИ,выходом ХЬвходом первого D-триггера, С -вход которого соединен с выходом элемента ИСКПЮЧАКЩЕЕ ИЛИ и с входом второго формирователя импульсов, выход которого соединен с второй выходной клеммой устройства и с первым входом. 11 84 |Вьгход второго элемента И соединен с R-ВХОДОМ второго 33-триггера, второй вход - с D -входом второго)-триггера и с первым входом первого элемента И, второй вход которого соединен с С-входом третьего)-триггера, с пер(вьы входом четвертого элемента ИЛИ и с вторым входом третьего элемента ИЛИ, вь1ход четвертого элемента ИЛИ соединен С Первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого соединен с выходом третьего элемента ИЛИ, второй вход четвертого элемента ИЛИ соединен сD -входом третьего -триггера прямой выход которого соединен с четвертым входом третьего элемента И, а инверсный выход соединен cD -входом третьегоD-триггера, с четвертым четвертого элемента И и с управляющим входом ключа, первый вьшод которого соединен через второй конденсатор с первой выходной клеммой устройства, второй вьгоод - с вторьм вьшодом первого конденсатора и , входом усилителя.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля сопротивления изоляции | 1980 |

|

SU935832A1 |

| Устройство для защиты трехфазной сети от обрыва фазы | 1984 |

|

SU1279013A1 |

| Преобразователь перемещения в код | 1989 |

|

SU1646055A1 |

| Устройство для автоматизированного контроля параметров реле | 1985 |

|

SU1265704A1 |

| ГЕНЕРАТОР ТЕСТОВЫХ ПОСЛЕДОВАТЕЛЬНОСТЕЙ | 1990 |

|

RU2034399C1 |

| ЗАДАЮЩИЙ ГЕНЕРАТОР ПРЕОБРАЗОВАТЕЛЯ НАПРЯЖЕНИЯ | 2022 |

|

RU2784620C1 |

| Устройство для контроля контактирования интегральных схем | 1987 |

|

SU1483411A1 |

| Устройство для разбраковки диодов по времени восстановления обратного сопротивления | 1983 |

|

SU1140064A1 |

| Устройство для контроля цифровых блоков | 1988 |

|

SU1619208A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА ИНФОРМАЦИИ ПО ДВУХПРОВОДНОЙ ЛИНИИ СВЯЗИ | 1991 |

|

RU2023310C1 |

УСТРОЙСТВО ДЛЯ КОНТРОЛЯ СОПРОТИВЛЕНИЯ ИЗОЛЯЦИИ, содержащее источник испытательного напряжения, соединенный первым выводом с общей шиной устройства, вторым выводом с первой клеммой для подключения объекта контроля, с первым вьшодом первого конденсатора, первым выводом первого резистора, соединенного вторык вьшодом через второй резистор с общей шиной устройства, непосредственно с. первым входом нуль-органа, второй вход которого соединен через третий резистор с общей шиной устройства, через первый диод с выходом усилителя, первый вход которого соединен через четвертый резистор с второй клеммой для подключения объекта контроля, а непосредственно с вторым вьшодом первого конденсатора и через последовательно соединенные второй диод и пятый резистор - с первым вьшодом третьего диода, соединенного выводом через источник опорного напряжения с общей шиной устройства, первая выходная клемма которого соединена с прямым выходом первого D-триггера R-вход которого соединен с входной клеммой устройства, выход srti ; i; : . Us iiij- n - .. : %:Чс1|1«)ТШй задатчика времени запуска соединен а первьм входом первого элемента И, соединенного вторым входом с выходом первого формирователя импульсов,выходом - с С-входом второго Г-триггера, третий)Триггер, генератор импульсов, отличающееся тем, что с целью повьш1ения точности контроля, S устройство введены второй конденсатор, ключ, второй, третий четвертый, пятый и шестой элементы И, задатчик начального кода, реверсивный счетчик, дешифратор, первый, второй третий и четвертый элементы ИЛИ, элемент ИСКЛЮЧАЮЩЕЕ КШ, второй формиро ватель импульсов, четвертый ,-триггер, причем выход второго формирователя W импульсов соединен с первым входом второго элемента И, первыйвыход га-, нератора импульсов соединен с анодом третьего диода, с входом первого формирователя импульсов, с первым входом третьего элемента И, с первы«( входом четвертого элемента И, второй вход которого соединен с выхосо а дом нуль-органа, с вторым входом третьего элемента И и I) -входом четвертого .D.-триггера, R -вход которого 00 4 соединен с R-входом третьего D-тригг гера, старт-стоповым входом генератора импульсов, прямым выходом второго ф-триггера,V-входом реверсивного счетчика, С-вход четвертого D-триггера соединен с вычитаюпщм входом счет чика и выходом четвертого элемента И, третий вход которого соединен с вторым выходом генератора импульсов и с третьим входом третьего элемента И, четвертый вход которого соединен с прямым выходом третьегоD-триггера, выход - с суммирующим входом ревер-

Изобретение относится к контрольно-измерительной технике и может быть использовано для контроля сниже« ния сопротивления изоляции относительно допустимой нормы. .

Известно устройство для контроля сопротивления изоляции, содержащее усилитель, нуль-орган и источник испытательного напряжения

Недостатком известного устройства является низкая достоверность контроля, обусловленная недостаточной помехозащищенностью

Наиболее близким техническим решением к предлагаемому является устройство для контроля сопротивления изоляции, содержащее источник испытательного напряжения, соединенный первым выводом с общей шиной устройства, вторым выводом с первой клеммой для подключения объекта контроля, с первым выводом первого конденсатора, первым вьтодом первого резистора, соединенного вторым выводом через второй резистор с общей шиной устройства, неп9средственно с первым входом

нуль-органа, второй вход которого соединен через третий резистор с общей щиной устройства, через первый диод с выходом усилителя, первый вход которого соединен через четвертый резистор с второй клеммой для подключения объекта контроля, а непосредственно с вторым выводом первого конденсатора и через последовательно соединенные второй диод и пятый резистор с первым выводом третьего диода, соединенного вторым вьтодом через источник опорного напряжения с общей шиной устройства, первая выходная клемма которого соединена с прямым выходом первого D-триггера,Р-вход которого соединен с входной клеммой устройства, выход задатчика времени запуска соединен с первым входом первого элемента И, соединенного вторым входом с выходом первого формирователя импульсов, выходом- с С-входом второго D-триггера, третий) -три:- гер, генератор импульсов 2,

Недостатком известного устройства является низкая точность контроля. обусловленная тем, что на результат контроля влияет разброс величины сум марной паразитной емкости контролиру емых цепей, линий связи и коммутатора. Указанный недостаток не позволяет контролировать с заданной погрешностью крупногабаритные изделия с разви той разнодлинной кабельной сетью, а также объекты, удаленные на различны расстояния и подключаемые.через различные коммутаторы к устройству конт роля. Цель изобретения - повьшгение точности устройства. Поставленная цель достигается тем, что в устройство для контроля -. сопротивления изоляции, содержащее источник испытательного напряжения, соединенный первьм .вьшодом с общей шиной устройства, вторым выводом с первой клеммой для подключения объек та контроля, с первым выводом первого конденсатора, первым выводом первого резистора, соединенного вторым вьшодом через второй резистор с обще шиной устройства, непосредственно с первым вхЬдом нуль-органа, второй вход которого соединен через третий резистор с общей шиной устройства, через первый диод с выходом усилител первый вход которого соединен через четвертый резистор с второй клеммой для подключения объекта контроля, а непосредственно с вторым выводом первого конденсатора и через последовательно соединенные второй диод и пятый резистор - с первым вьшодом третьего диода, соединенного вторым выводом через источник опорного напряжения с общей шиной устройства первая выходная клемма которого соединена с прямым выходом первого D-триггера, Р-вход :. которого соедииен с входной клеммой устройства, вь 45 РЗ ход задатчика времени запуска соединен с первым входом первого элемента И, соединенного вторым входом с выходом первого формирователя импульсов, выходом с С-входом второго Р-триггера, третий)-триггер, генератор импульсов, введены второй конденсатор, ключ, второй, третий, четвертый, пятый и шестой элементы И, задатчик начального кода, реверсивный счетчик, дешифратор, первый, второй, третий и четвертый элементы ИЛИ, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, второй формирователь импульсов, четвертый

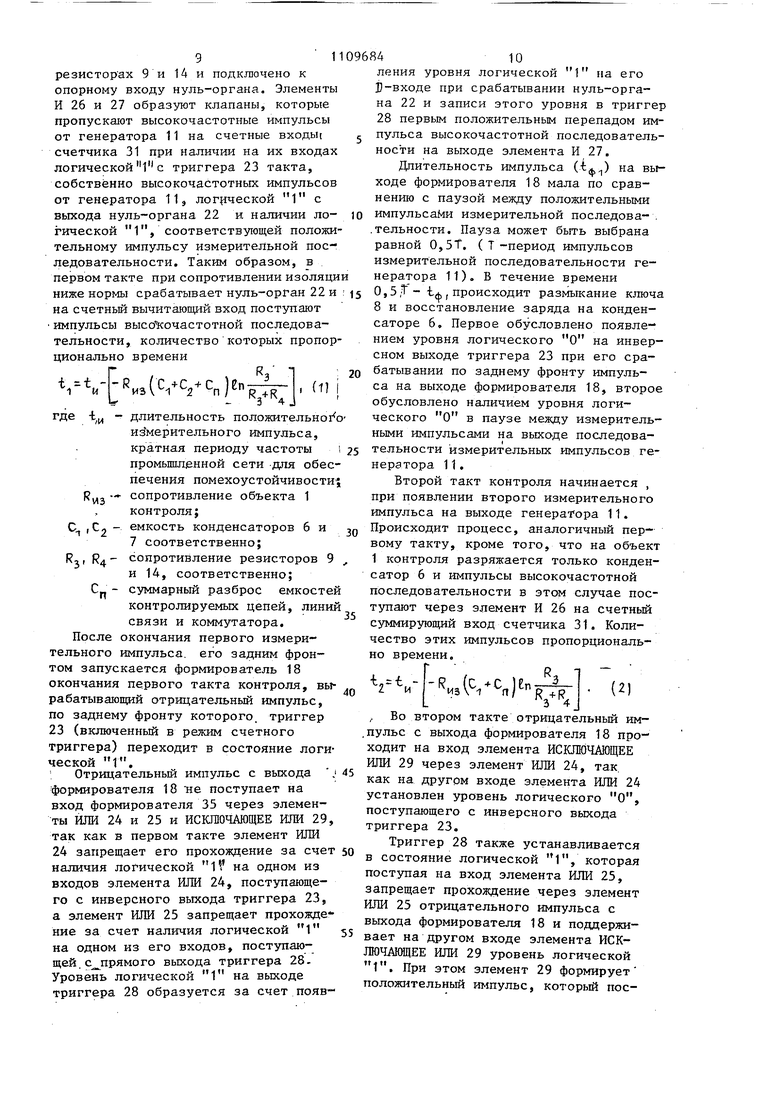

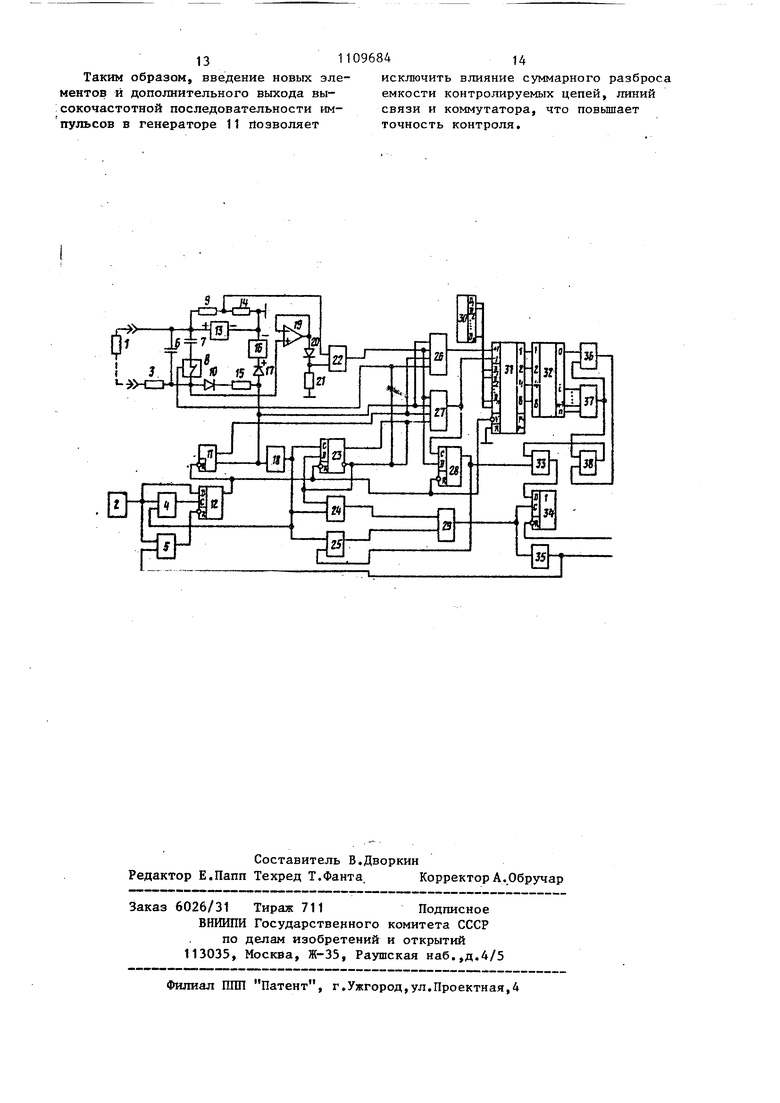

соответствующими входами первого элемента ИЛИ, выход которого соединен с первым входом второго элемента ИЛИ и с вторым входом пятого элемента И, 40 соединенного выходом с вторым входом второго элемента ИЛИ, выход которого соединен с первым входом шестого элемента И, соединенното вторым входом с прямым выходом четвертого.D-тригге- 1 -триггер, причем выход второго формирователя импульсов соединен с первым входом второго элемента И, первый выход генератора импульсов соединен с анодом третьего диода, с входом первого формирователя импульсов, с первым входом третьего элемента И, с первым входом четвертого элемента И, второйВХОД которого соединен с выходом нуль-органа, с вторым входом третьего элемента И и Р-входом чет- вертого)-триггера, R-вход которого соединен сР-входом третьегоD-триггера, старт-стоповым входом генератора импульсов, прямым выходом второго D-триггера, У -входом реверсивного счетчика, С-входом четвертого В-триггера соединен с вычитающим входом реверсивного счетчика и выходом четвертого элемента И, третий вход которого соединен с вторым выходом генератора импульсов и с третьим входом третьего элемента И, четвертый вход которого соединен с прямым выходом третьего I -триггера, выход с суммирующим входом реверсивного . : счетчика, информационные входы которого соединены с соответствующими выходами задатчика начального кода, R-вход соединен с общей шиной устройства, прямые выходы соединены с соответствующими входами дешифратора, выход младшего разряда дешифратора соединен с первым входом пятого элемента И, группа старших выходов - с и с первым входом третьего элемента ИЛИ, выходом - с р -входом первого D-триггера, С-вход которого соединен с выходом элемента ИСКЛЮЧАКЩЕЕ ИЛИ и с входом второго формирователя импульсов, выход которого соединен с второй выходной клеммой устройства и с первым входом, выход второго элемента И соединен с -входом второго Ф-триггера, второй вход - ciD-BXoдом второго В-триггера и с первым входом первого элемента И, второй вход которого соединен с С-входом третьего)-триггера, с первым входом четвертого элемента ИЛИ и с вторым входом третьего элемента ИЛИ, выход четвертого элемента ИЖ соединен с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого соединен с выходом третьего элемента ИЛИ, вто рой вход четвертого элемента ИЛИ соединен сD-входом третьего,)-триггера, прямой выход которого соединен с четвертым входом третьего элемента И, а инверсный выход соединен с 1)-входрм третьего 3)-триггера, с четвертым входом четвертого элемента И и с управляющим входом ключа, первьм вывод которого соединен через второй конденсатор с первой вьпсодной клеммой устройства, второй вывод со вторым выводом первого конденсато ра и входом усилителя, На чертеже приведена принципиальная схема устройства. Устройство для контроля сопротивления изоляции объекта 1 контроля со держит задатчик 2 времени запуска, {четвертый резистор 3, первый элемент И 4, второй элемент И 5, первый конденсатор 6, втордй конденсатор 7, ключ 8, первый .резистор 9, второй диод 10, генератор 11 импульсов, второй 1) -триггер 12, источник 13 ис пытательного напряжения, второй резистор 14, пятый резистор 15, источник 16 опорного напряжения, третий диод 17, первый формирователь 18 импульсов, усилитель 19, первый диод 20, третий резистор 21, нуль-орган 2 третий Г-триггер 23, четвертый элемент ШШ 24, третий элемент РШИ 25, третий элемент И 26, четвертый элемент И 27, четвертый)-триггер 28, элемент ИСКЛЮЧАЮЩЕЕ ШЩ 29, задатчик 30 начального кода, реверсивный счет чик 31, дешифратор 32, шестой элемен И 33, первый Р-триггер 34, второй формирователь 35 импульсов, пятый элемент И 36, первый элемент ИЛИ 37, второй элемент ИЛИ 38. Первым выводом источник 13 испытательного напряжения соединен с общей шиной устройства, вторым выводом с первой клеммой для подключения объекта 1 контроля, с первым выводом первого конденсатора 6,первым выводом первого резистора 9, соединенного вторым выводом через второй резистор 14 с общей шиной устройства, непосредственно с первым входом нульоргана 22, второй вход которого соединен через третий резистор 21 с общей шиной устройства, первый диод 20 с выходом усилителя 19, первый вход которого соединен через четвертый резистор 3 с второй клеммой для подключения объекта 1 контроля, а непосредственно с вторЕ)1М выводом первого конденсатора 6 и через последовательно соединенные второй диод 10 и пятый резистор 15 - с первым выводом третьего диода 17, соединенного вторым выводом через источник опорного напряжения с общей шиной устройства, первая выходная клемма которого соединена с прямым выходом первого D -триггера 34, R-вход которого соединен с входной клеммой устройства, выход задатчика 2 времени запуска соединен с первым входом первого элемента И 4, соединенного вторым входом с выходом первого формирователя 18 импульсов, выходом - с С-входом второгоD-триггера 12, первый выход второго формирователя 35 импульсов соединен с первьм входом второго элемента И 5, первый выход генератора 11 импульсов соединен с анодом третьего диода 17, с входом первого формирователя 18 импульсов, с первым входом третьего элемента Е 26, с первым входом четвертого Элемента И 27,. второй вход которого соединен с выходом нуль-органа 22, с вторым входом третьего элемента И 26 и В-входом четвертого Г-триггера 28, R-вход которого соединен с R -входом третьегоD-триггера 23, стартстоповым входом генератора 11 импульсов, прямым выходом второго D-тригЕера 12,V-входом реверсивного счетчика,С -вход четвертого D-триггера 28 соединен с вычитающим входом реверсивного счетчика 31 и выходом четвертого элемента И 27, третий вход которого соединен с вторым выходом генератора 11 импульсов и с третьим входом элемента И 26, четвертый вход которого соединен с прямым выходом третьего )-триггера 23, выход - с суммирзпощим входом ре версивного счетчика 31, информационные входы которого соединены с соответствующими выходами задатчика 30 начального кода, R-вход соединен с общей шиной устройства, прямые вы ходы соединены с соответствующими входами дешифратора 32, выход младшего разряда дешифратора 32 соединен с первым входом пятого элемента И 36 группа старших выходов--с соответст вующими входами первого элемента ИЛИ 37, выход которого соединен с первым входом второго элемента ИЛИ 38 и с вторым входом пятого элемента И 36, соединенного выходом с вторым входом второго элемента ИЛИ 38, выход которого соединен с первым входом шестого элемента И 33, соединенного вторым входом с прямым выходом четвертогоD-триггера и с первым входом третьего элемента ИЛИ 25, выг ходом - с Б-входом первого D-триггера 34,С -вход которого соединен с выходом элемента ИСКЛЮЧАЮЩЕЕ ИЖ 29 к с входом второго формирователя импульсов 35, выход которого соединен с второй выходной клеммой устрой ства и с первым входом, выход второго элемента И 5 соединен с Р-входом второго 1 -триггера 12, второй вход с D-входом второго Б-триггера 12 и с первым входом первого элемента И 4, второй вход которого соединен с С-входом третьегоD-триггера 23, с первым входом четвертого элемента ИЛИ 24 и с вторым входом третьего элемента 25 ИЛИ, выход четвертого элемента ИЛИ 24 соединен с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 29, второй вход которого соединен с выхо дом третьего элемента ИЛИ 25, второй вход четвертого элемента ИЛИ 24 соединен с D-входом третьего)-триггера 23, прямой выход которого соединен с четвертым входом третьего элемента И 26, а инверсный выход соединен с1 -входом третьего)-триггера 23, с четвертым входом четвертого элемента И 27 и с управляющим входом ключа 8, первый вьшод которого соединен через второй конденсатор 7 с первой выходной клеммой устройства, второй вьгоод - с вторым выводом первого конденсатора 6 и входом усителя 19. Устройство работает следующим образом. Задатчик 2 вырабатывает импульс запуска, длительность которого определяется программой и условиями работы: при низком уровне помех производится цикл однократного контроля и импульс снимается после появления им пульса окончания контроля на выходе формирователя 35 и считывания резуль тата контроля с прямого выхода триггера 34. При высоком уровне помех пр производится многократный контроль для усреднения результата и импульс запуска снимается после прохождения требуемого количества циклов контроля. Выход формирователя 18 находится в состоянии логической 1 при отсутствии отрицательного перепада на его входе, что разрешает прохождение импульсов . запуска через элемент И 4 на тактовый вход триггера 12, Выход формирователя 35 находится в состоянии логической 1 при отсутствии положительного перепада на его входе, поэтому элемент И 5 разрешает прохождение уровня логической 1 во время действия импульса запуска на R-вход триггера 12, разрешающего его работу, йбота устройства начинается с появлением на выходе задатчика 2 по- ложительного импульса запуска, который поступает на)-вход триггера 12, на один из входов элемента И 5 и через элемент И 4 на С-вход триггера 12, устанавливая его в состояние логической 1. ; Уровень логической 1 на прямом выходе триггера 12 вызьшает переход реверсивного счетчика 31 по ходу в режим хранения начального кода от задатчика 30 и режим счета, по суммирую щему и вычитающему входам, одновременно этот 5фовень разрешает работу триггеров 23 и 28 и запускает в непрерывный режим работы генератор 11. Цикл контроля начинается с появлением положительного импульса измерительной последовательности на первом выходе генератора 11, на первом выходе которого синхронно появляется последовательность высокочастотных импульсов. Импульс измерительной последовательности от генератора 11 запирает диод 10 и предварительно заряженные от источника 13 конденсаторы 6 и 7 начинают разряжаться на контролируемое сопротивление изоляции () объекта 1 контроля. Ключ 8 в первом такте (первом периоде Т частоты последовательности измерительных им пульсов) замкнут за счет наличия на его управляющем входе логической 1 с инверсного выхода триггера 23. При этом потенциал входа усилителя 19 по абсолютной величине растет относительно общей точки, напряжение с выхода усилителя 19 подается на сигнальный вход нуль-органа 22. Напряжение на сигнальном входе нуль-органа 22 сравнивается с опорным, которое снимается с резистивного делителя на 1 резисторах 9 и 14 и подключено к опорному входу нуль-органа. Элементы И 26 и 27 образуют клапаны, которые пропускают высокочастотные импульсы от генератора 11 на счетные входы счетчика 31 при наличии на их входах логической триггера 23 такта, собственно высокочастотных импульсов от генератора 11, логической 1 с выхода нуль-органа 22 и наличии логической 1, соответствующей положи тельному импульсу измерительной последовательности. Таким образом, в первом такте при сопротивлении изоляци ниже нормы срабатывает нуль-орган 22 и на счетньй вычитающий вход поступают импульсы высокочастотной последовательности, количество которых пропор ционально времени R. 1 f HslVc cJen t t(Я где -t, длительность положительног из°мерительного импульса, кратная периоду частоты промьшшенной сети -для обес печения помехоустойчивости сопротивление объекта 1 контроля; емкость конденсаторов 6 и 1 7 соответственно; сопротивление резисторов 9 р 3 и 14, соответственно; суммарньЕй разброс емкосте контролируемых цепей, лини связи и коммутатора. После окончания первого измерительного импульса, его задним фронтом запускается формирователь 18 окончания первого такта контроля, вь рабатывающий отрицательный импульс, по заднему фронту которого, триггер 23 (включенный в режим счетного триггера) переходит в состояние логи ческой 1. Отрицательный импульс с выхода формирователя 18 не поступает на вход формирователя 35 через элементы ИЛИ 24 и 25 и ИСКЛЮЧАЮЩЕЕ ШШ 29, так как в первом такте элемент ИЛИ 24 запрещает его прохождение за счет наличия логической 1 на одном из входов элемента РШИ 24, поступающего с инверсного выхода триггера 23, а элемент ИЖ 25 запрещает прохождение за счет наличия логической на одном из его входов, поступающей, с прямо го выхода триггера 28. Уровень логической 1 на выходе триггера 28 образуется за счет появ410уровня логической 1 на его J)-входе при срабатывании нуль-органа 22 и записи этого уровня в триггер 28 первым положительным перепадом импульса высокочастотной последовательности на выходе элемента И 27. Дпительность импульса (Ьф-,) на выходе формирователя 18 мала по сравнению с паузой между положительными импульсами измерительной последова- . .тельности. Пауза может быть выбрана равной 0,5Т. (Т -период импульсов измерительной последовательности генератора 11). В течение времени 0,5 Т - t(|,, происходит размыкание ключа и восстановление заряда на конденсаторе 6. Первое обусловлено появлением уровня логического О на инверсном выходе триггера 23 при его срабатывании по заднему фронту импульса на выходе формирователя 18, второе обусловлено наличием уровня логического О в паузе между измерительными импульсами на выходе последовательности измерительных импульсов генератора 11. Второй такт контроля начинается , при появлении второго измерительного импульса на выходе генератора 11. Происходит процесс, аналогичный первому такту, кроме того, что на объект 1 контроля разряжается только конденсатор 6 и импульсы высокочастотной последовательности в этом случае поступают через элемент И 26 на счетный суммирующий вход счетчика 31. Количество этих импульсов пропорционально времени. ,t.4-R. , (с +С 1 in - MsVS f Во втором такте отрицательньй импульс с выхода формирователя 18 проходит на вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 29 через элемент ИЛИ 24, так. как на другом входе элемента ИЛИ 24 установлен уровень логического О, поступающего с инверсного выхода триггера 23. Триггер 28 также устанавливается в состояние логической 1, которая поступая на вход элемента ИЛИ 25, запрещает прохождение через элемент ЛИ 25 отрицательного импульса с ыхода формирователя 18 и поддержиает на другом входе элемента ИСКЮЧАЩЕЕ ИЛИ 29 уровень логической 1. При этом элемент 29 формирует оложительный импульс, который поступает на С-вход триггера 34, записывающего по переднему фронту этого импульса.результат контроля (логический О - норма, логическая 1 ненорма), поступающий с выхода эле мента HItti 38. Результат контроля фор мируется следующим образом. За два такта контроля в счетчике 31 устанавливается число, пропорциональное времени |-f-to t-2- f o-RM}C2 , (3) где to С- - время, эквивалентное началь ному коду в счетчике 31; заданная норма сопротивления изоляции, не зависящая от разброса суммарной пара- зитной емкости . Двоичное число, пропорциональное величине (3), дешифрируется дешифратором 32, Если сопротивление изоляции объек та 1 контроля точно равно норме или его значение находится в доверительном интервале, соответствующем требуемой погрешности, то на выходе элемента ИЛИ 38 - логический О, та как на выходах дешифратора 32,, соответствующих числам, равным верхней границе доверительного интервала или более, присутствует уровень логичес- кого О, которьш запрещает изменени состояния выхода элемента И 36, поддерживая логический О на обоих входах и выходе элемента ИЛИ 38. Есл

сопротивление изоляции объекта 1 контроля меньше нижней границы доверительного интервала, то на выходах дешифратора 32,соответствующих верхней границе доверительного интервала и более,присутствует уровень логической 1,который через элемент ИЛИ 37 устанавливается на входе и выходе элемента ИЛИ 38, Состояние логической 1 по вьгходу триггера 28 обеспечивает передачу на D-ВХОД триггера 34 информации с выхода элемента ИЛИ 38 через элемент И 33. Если сопротивление изоляции больше нормы на столько, что в первом такте нуль-орган 22 не срабатывает, то устройство сокращает цикл контроля, ограничиваясь первым тактом и обеспечивает защиту от выдачи ложной информации о результате контроля следующим образом.

Если в течение первого такта нульорган 22 не сработал, то не срабаты вает триггер 28, и логический О на

при наличии импульса запуска от задатчика, в противном случае повторный запуск не происходит.

Для нормальной работы устройства необходимо, чтобы длительность импульса на выходе формирователя 18 превьш1ала длительность импульса на выходе формирователя 35.

Параметры измерительной цепи и реS .зистивного делителя на резисторах 9 и 14 выбирают так, чтобы

t-Rn .

йС

-из

иэ

tTrtOtX

глох

R.

|Сп

+ ЙС

()

0

1

max

,,,ди, ЛС -максимально допустимые погрешности контроля сопротивления изоляции значений емкостей С

конденсаторов 6 и 7 соответствени Cj но;

ntncix максимально ожидаемый сумматорный разброс емкостей контролируемых цепей, линий связи и коммутатора. прямом выходе триггера 28 поступает на вход элемента И 33, запрещая прохо)тсдение информации с выхода элемента ИЛИ 38 через элемент Pi 33 и под- держивая уровень логического О на выходе элемента И 33 и 1 -входе триггера 34, Логический О с выхода триггера 28 поступает также на вход/ элемента ИЛИ 25, разрешая- прохождение отрицательного импульса с выхода формирователя 18 через элемент ИЛИ 25 При этом на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЖ 29 формируется положительный импульс, который, поступая на С-вход триггера 34, обеспечивает запись логического О (норма) в триггер 34, одновременно этот импульс запускает формирователь 35, с выходакоторого отрицательный импульс поступает на второй выход устройства, сигнализируя об окончании контроля, и через элемент И 5 на R -вход триггера 12. Появление отрицательного импульса на R-входе триггера 12 устанавливает его в состояние логического О, При этом логический О на прямом выходе триггера 12 поступает на R-вход генератора 11, останавливая его работу, поступает на V-вход счетчика 31, разрешая ввод начального кода от задатчика 30, поступает на R-входы триггеров 23 и 28, подтверждая нулевое . состояние этих триггеров. Отрицательньй импульс с выхода формирователя 18 своим задним фрон том повторно запускает устройство

13110968414

Таким образом, введение новых эле- исключить влияние суммарного разброса ментов и дополнительного выхода вы- емкости контролируемых цепей, линий :сокочастотной последовательности им- связи и коммутатора, что повьшает пульсов в генераторе 11 Позволяет точность контроля.

&1

26

| Устройство для контроля сопротивления изоляции | 1971 |

|

SU486276A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Велотренажер | 1981 |

|

SU995832A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1984-08-23—Публикация

1983-04-29—Подача