ратбры, счетчик импульсов, реверсивный счетчик, декодер и пороговый блок, первыйн второй выходы счетчика импул ьсов соединены соответственно с первым и вторым входами первого и второго коммутаторов, выход первого коммутатора и первый выход второго коммутатора подключены соответственно к входам первого и второго дешифраторов, выходы первого дешифратора через последовательно соединенные первые сумматор и интегратор соединены соответственно с входом второго сумматора, выход которого подключен к первому входу декодера, выходы второго дешифратора чррез последовательно соединенные третий сумматор и второй интегратор подключены соответственно к входам четвертого сумматора, выход которого соединен с вторым входом декодера, выходы первого и второго фазовых детекторов подключены соответственно к первому и второму входам переключателя, первый и второй выходы которого соединены соответственно с первыми входами первого и второго регистров сдвига, выходы которых соединены соответственно с входами первого и второго коммутаторов, третий выход счетчика импульсов подключен к третьему входу первого коммутатора второй выход второго коммутатора соединен с вторыми входами первого и второго регистров сдвига, выход первого формирователя импульсов подключен к первому входу второго формирователя импульсов, выход которого соединен с третьим входом переключателя и первым входом реверсивного счетчика, выход которого подключен к входу порогового блока, выходы декодера, четвертого сумматора и порогового блока являются соответственно первым, вторым и третьим выходами демодулятора, первым, вторым, третьим, четвертым, пятым, шестым и седьмым входами которого являются соответственно вход счетчика импульсов, объединенные входы первого и второго фазовых детекторов, вход первого формирователя импульсов, второй и третий входы второго формирователя импульсов, второй вход реверсивного счетчика и четвертый вход переключателя.

| название | год | авторы | номер документа |

|---|---|---|---|

| Демодулятор частотно-манипулированных сигналов | 1984 |

|

SU1223393A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ РАДИОТЕЛЕМЕТРИЧЕСКИХ СИГНАЛОВ | 1994 |

|

RU2126139C1 |

| ПРЕОБРАЗОВАТЕЛЬ ИНЕРЦИАЛЬНОЙ ИНФОРМАЦИИ | 2006 |

|

RU2325620C2 |

| ПРИЕМОПЕРЕДАТЧИК ВОЛОКОННО-ОПТИЧЕСКОЙ ЛИНИИ СВЯЗИ | 1989 |

|

RU2221342C2 |

| Устройство для управления преобразователем постоянного напряжения в постоянное | 1983 |

|

SU1144174A1 |

| Устройство для демодуляции частотно-манипулированных сигналов | 1982 |

|

SU1059694A1 |

| ПЕРЕНОСНОЕ АВТОМАТИЗИРОВАННОЕ РАБОЧЕЕ МЕСТО | 2006 |

|

RU2316812C1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА ДИСКРЕТНОЙ ИНФОРМАЦИИ | 1990 |

|

RU2022470C1 |

| Устройство для разделения направлений передачи в дуплексных системах связи | 1989 |

|

SU1672575A2 |

| МНОГОКАНАЛЬНАЯ АППАРАТУРА ПЕРЕДАЧИ ДАННЫХ | 2009 |

|

RU2406121C2 |

УСТРОЙСТВО ДЛЯ ПРЕОБРАЗО ВАНИЯ СИГНАЛОВ, содержапдее первый модулятор, выход которого соединен с первым входом первого переключателя, выход которого через первый фильтр соединен с первым входом сумматора, выход которого подключен к входу первого согласующего трансформатора, выход которого является выходом устройства, переключатель скорости, выход которого соединен с первыми входами второго модулятора и демодулятора, переключатель режимов, выход которого подключен к второму входу первого переключателя, геиер:1тор импульсов, второй, третий и четвертый фильтры, второй согласующий трансформатор, первый, второй и третий усилители, отличающееся тем, что, с целью расширения области применения устройства, в него введен второй переключатель, выходы которого соединены соответственно с вторым и третьим входами демодулятора, к четвертому и пятому входу которого подключен выход переключателя режимов, первый, второй, третий и четвертый выходы генератора импульсов соединены соответственно с шестым и седьмым входами демодулятора, первым и вторыми входами первого и второго модуляторов, выход второго модулятора соединен с третьим входом первого переключателя и входом второго фильтра, выход которого подключен к второму входу суммара, выход переключателя режй)Аов соединен с третьим входом второго модулятора и первым входом второго переключателя, выход второго согласуюпюго трансформатора соединен с входом первого усилителя, выход которого подключен к входам третьего и четвертого фильтров, выходы которых соответственно через второй и третий усилители подключены к второму и третьему входам второго переключателя, второй и четвертый входы соответственно первого и второго модуляторов являются первым входом устройства, вторым и третьим входами которого являются соответственно пятый вход второго модулятора и вход второго согласующего трансформатора, выход первого согласующего трансформатора и выходы демодулятора являются соответственно первым, вторым, третьим и четвертым выходами устройства. 2.Устройство но п. I, отличающееся тем, что второй модулятор содержит первый и i второй делители имнульсов, формирователь импульсов, элемент 2И-ИЛИ и кодопреоб(Л разователь, выход первого делителя импульсов подключен к входу второго делителя импульсов, выходы которого через соответст- вующие формирователи импульсов соединены с соответствуюншми первыми входами элемента 2И-ИЛИ, выход которого соединен с первым входом первого делителя импульсов, выходы кодопреобразователя подклю-чены соответственно к вторым входам элею мента 2И-ИЛИ, первый, второй, третий и оо четвертый входы кодопреобразователя являОС ются соответственно первым, третьим, чета вертым и пятым входами второго модулятора вход первого делителя импульсов и выход второго делителя импульсов являются соответственно вторым входом и выходом второго модулятора. 3.Устройство по пп. I и 2, отличающееся тем, что демодулятор содержит первый и второй фазовые детекторы, первый и второй формирователи импульсов, переключатель, первый и второй регистры сдвига, первый и второй коммутаторы, первый и второй дешифраторы, первый, второй, третий и четвертый сумматоры, первый и второй интег

1

Изобретение относится к технике электросвязи и может быть использовано в системах передачи данных.

Известно устройство для обработки телеизмерительной информации, содержащее блок считывания, линейный блок, буферный регистр, дешифраторы, шифраторы, блоки памяти, блок управления, блоки согласования, генератор, формирователи, регистраторы, индикаторы, элементы И и ИЛИ-НЕ 1.

Однако устройство не обеспечивает обработку сигналов различного вида.

Наиболее бли5ким к предлагаемому является устройство для преобразования сигналов, содерл ащее первый модулятор, выход которого соединен с первым входом первого переключателя, выход которого через первый фильтр соединен с первым входом сумматора, выход которого подключен к входу первого согласующего трансформатора, выход которого является выходом устройства, переключатель скорости, выход которого соединен с первыми входами второго Модулятора и демодулятора, переключатель режимов, выход которого подключен к второму входу первого переключателя, генератор импульсов, второй, третий и четвертый фильт ры, второй согласующий трансформатор, первый, второй и третий усилители, а также дополнительные усилители, фильтры и ключи (21..

Однако структура модулятора и демодуляторов не позволяет использовать узлы как при обработке ФМ-, так и ЧМ-сигналов. Целью изобретения является расширение 5 области применения устройства.

Поставленная цель достигается тем, что в устройство для преобразования сигналов, содержащее первый модулятор, выход которого соединен с первым входом первого пере ключателя, выход которого через Первый фильтр соединен с первым входом сумматора, выход которого подключен к входу первого согласующего трансформатора, выход которого является выходом устройства, переключатель скорости, выход которого

5 соединен с первыми входами второго модулятора и демодулятора, переключатель режимов, выход которого подключен к второму входу первого переключателя, генератор импульсов, второй, третий и четвертый фильтры, второй согласующий трансформатор,

первый, второй и третий усилители, введен

второй переключатель, выходы которого

соединены соответственно с вторым и третьим входами демодулятора, к четвертому

и пятому входу которого подключен выход

переключателя режимов, первый, второй, третий и четвертый выходы генератора импульсов соединены соответственно с шестым и седьмым входами демодулятора, первым и вторым входами первого и второго модуляторов, выход второго модулятора соединен с третьим входом первого переключателя и входом второго фильтра, выход которого подключен к второму входу сумматора, выход переключателя режимов соединен с третьим входом второго модулятора и первым входом второго переключателя, выход второго согласующего трансформатора соединен с входом первого усилителя, выход которого подключен к входам третьего и четвертого фильтров, выходы которых соответственно через второй и третий усилители подключены к второму и третьему входам второго переключателя, второй и четвертый входы соответственно первого и второго модуляторов являются первым входом устройства, вторым и третьим входами которого являются соответственно пятый вход второго модулятора и вход второго согласующего трансформатора, выход первого согласующего трансформатора и выходы демодулятора являются соответственно первым, вторым, третьим и четвертым выходами устройства.

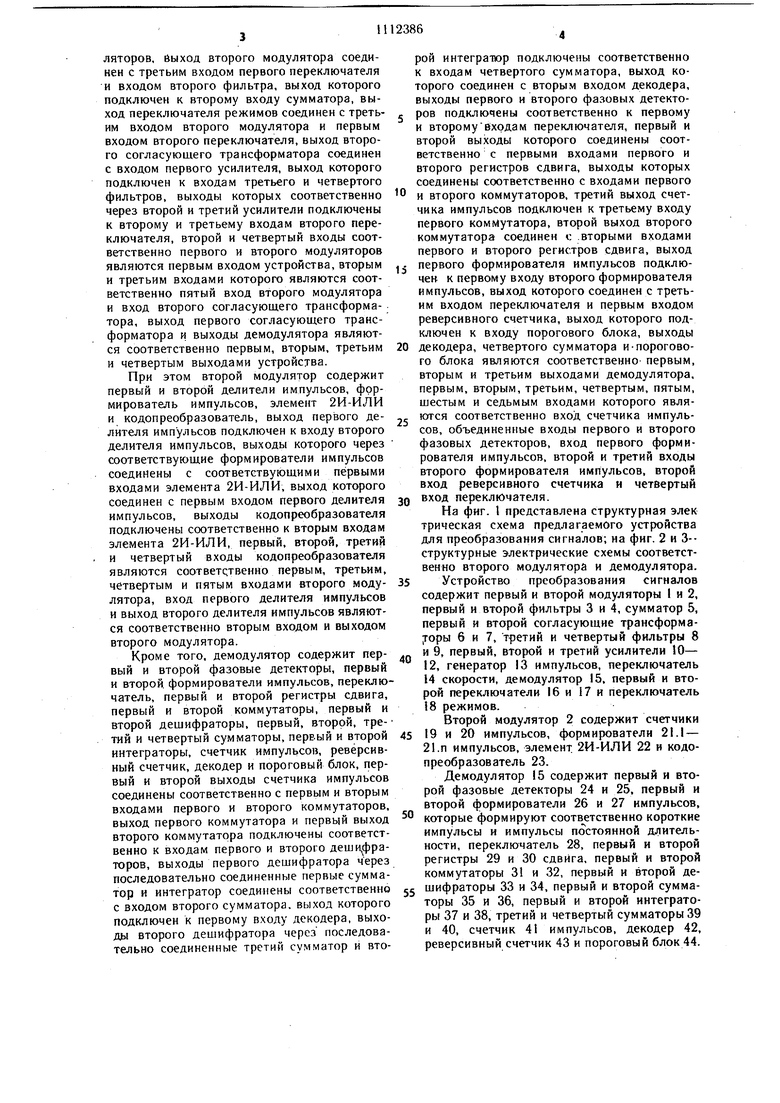

При этом второй модулятор содержит первый и второй делители импульсов, формирователь импульсов, элемент 2И-ИЛИ и кодопреобразователь, выход первого делителя импульсов подключен к входу второго делителя импульсов, выходы которого через соответствующие формирователи импульсов соединены с соответствующими первыми входами элемента 2И-ИЛИ, выход которого соединен с первым входом первого делителя импульсов, выходы кодопреобразователя подключены соответственно к вторым входам элемента 2И-ИЛИ, первый, второй, третий и четвертый входы кодопреобразователя являются соответственно первым, третьим, четвертым и пятым входами второго модулятора, вход первого делителя импульсов и выход второго делителя импульсов являются соответственно вторым входом и выходом второго модулятора.

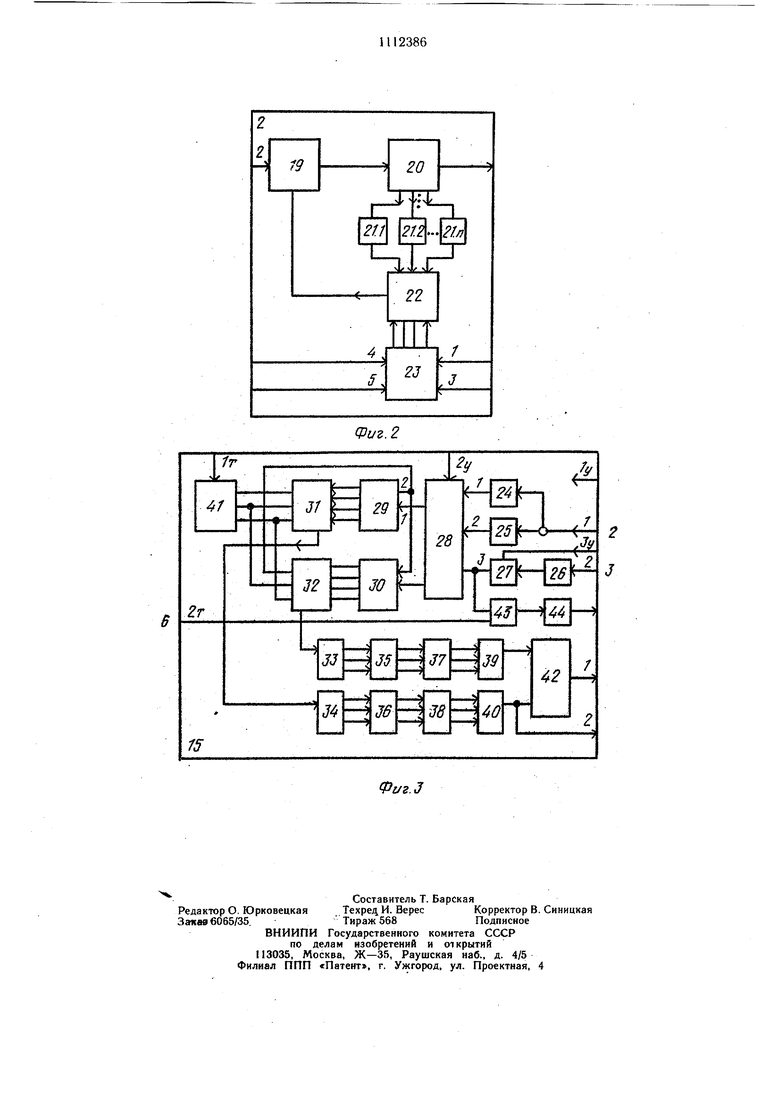

Кроме того, демодулятор содержит первый и второй фазовые детекторы, первый и второй, формирователи импульсов, переключатель, первый и второй регистры сдвига, первый и второй коммутаторы, первый и второй дешифраторы, первый, второй, третий и четвертый сумматоры, перн.ый и второй интеграторы, счетчик импульсов, реверсивный счетчик, декодер и пороговый блок, первый и второй выходы счетчика импульсов соединены соответственно с первым н вторым входами первого и второго коммутаторов, выход первого коммутатора и первый выход второго коммутатора подключены соответственно к входам первого и второго деши фраторов, выходы первого дешифратора через последовательно соединенные первые сумматор и интегратор соединены соответственно с входом второго сумматора. в):ход которого подключен к первому входу декодера, выходы второго дешифратора через последовательно соединенные третий сумматор и второй интегратор подключены соответственно к входам четвертого сумматора, выход которого соединен с вторым входом декодера, выходы первого н второго фазовых детекторов подключены соответственно к первому и второму Входам переключателя, первый и второй выходы которого соединены соответственно с первыми входами первого и второго регистров сдвига, выходы которых соединены соответственно с входами первого и второго коммутаторов, третий выход счетчика импульсов подключен к третьему входу первого коммутатора, второй выход второго коммутатора соединен с .вторыми входами первого и второго регистров сдвига, выход

первого формирователя импульсов подключен к первому входу второго формирователя импульсов, выход которого соединен с третьим входом переключателя и первым входом реверсивного счетчика, выход которого подключен к входу порогового блока, выходы

декодера, четвертого сумматора и-порогового блока являются соответственно первым, вторым и третьим выходами демодулятора, первым, вторым, третьим, четвертым, пятым, шестым и седьмым входами которого являются соответственно вход счетчика импульсов, объединенные входы первого и второго фазовых детекторов, вход первого формирователя импульсов, второй и третий входы второго формирователя импульсов, второй вход реверсивного счетчика и четвертый

вход переключателя.

На фиг. I представлена структурная элек трическая схема предлагаемого устройства для преобразования сигналов; на фиг. 2 и 3-структурные электрические схемы соответственно второго модулятора и демодулятора.

Устройство преобразования сигналов содержит первый и второй модуляторы 1 и 2, первый и второй фильтры 3 и 4, сумматор 5, первый и второй согласующие трансформа7оры 6 и 7, третий и четвертый фильтры 8 и 9, первый, второй и третий усилители 10- 12, генератор 13 импульсов, переключатель 14 скорости, демодулятор 15, первый и второй переключатели 16 и 17 и переключатель 18 режимов.

Второй модулятор 2 содержит счетчики

19 и 20 импульсов, формирователи 21.1 - 21.П импульсов, элемент. 2И-ИЛИ 22 и кодопреобразователь 23.

Демодулятор 15 содержит первый и второй фазовые детекторы 24 и 25, первый и второй формирователи 26 и 27 импульсов,

которые формируют соответственно короткие импульсы и импульсы постоянной длительности, переключатель 28, первый и второй регистры 29 и 30 сдвига, первый и второй коммутаторы 31 и 32, первый и второй дешифраторы 33 и 34, первый и второй сумматоры 35 и 36, первый и второй интеграторы 37 и 38, третий и четвертый сумматоры 39 и 40, счетчик 41 импульсов, декодер 42, реверсивный счетчик 43 и пороговый блок 44.

Устройство рабЬтает следующим образом,

Передаваемые данные прямого канала поступающие от первого источника информации на второй вход первого и четвертый вход второго модуляторов, преобразуются в соответствии-сустановленным переключателем 8 режимов работы в ФМ- или ЧМсигналы тональной частоты. На пятый вход второго модулятора 2 поступают данные обратного канала от второго источника информации.

В режиме «ФМ фазомодулированные сигналы с выхода первого модулятора I через первый переключатель 16, управляемый переключателем 18 режимов, поступают на первый фильтр 3, ограничивающий спектр передаваемого сигнала. С выхода первого фильтра 3 сигнал через сумматор 5 и первыйсогласующий трансформатор 6 поступает на первый выход устройства.

Одновременно передаваемые данные обратного канала, поступающие от второго источника информации на пятый вход второго модулятора 2, преобразуются в. режиме «ФМ в ЧМ-сигнал обратного канала, который через второй фильтр 4 поступает на второй вход сумматора 5, служащего для смешивания сигналов прямого и обр.атного каналов.

В режиме «ЧМ частотно-модулированный сигнал прямого канала через второй вход первого переключателя 16, первый вход которого закрыт сигналом с переключателя 18 режимов, поступает на вход первого фильтра 3.

Второй модулятор 2 -работает следующим образом.

Частотно-модулированный сигнал формируется делением опорной импульсной последовательности, поступающей от генератора 13, делителем частоты в виде счетчика 20 с переменным коэффициентом деления. Изменение коэффициента деления делителя частоты производится путем добавления определенного числа импульсов на его входе под воздействием информационных сигналов. Импульсы добавления формируются управляемым делителем 20 частоты. Получение необходимого числа импульсов добавления производится . суммированием единичных импульсов определенных разрядов делителя 20 частоты.

Формирователи 21 импульсов, подключенные к выходам соответствующих разрядовделится 20, формируют по каждому переходу сигнала делителя в единичное состояние импульс длительностью, равной периоду опорной частоты. С выходов формирователей 21 импульсы поступают на элемент 2ИИЛИ 22, управляемый кодопреобразовате лем 23. Кодопреобразователь преобразует пс ступающие на его входы сигналы и разре щает их прохождение через элемент 2И.ИЛИ 22 с выходов формирователей 21. .

При этом через элемент 2И-ИЛИ 22 проходят импульсы от тех формирователей 21, сумма импульсов с выхода которых за цикл деления делителя равна необходимому числу импульсов, подлежащих добавлению.

Импульсы добавления с выхода элемента 2И-ИЛИ 22 поступают на делитель в виде счетчика 19, чем достигается необходимый коэффициент деления делителя.

Такое построение модулятора 2 харак0 теризуется гибкостью и универсальностью и позволяет на одной структуре получить различные модуляторы с различной скоростью работы.

В режиме «ФМ принимаемый сигнал через третий вход устройства, второй согласующий трансформатор 7 и усилитель 12 поступает на входы фильтров 8 и 9, осуществляющих разделение спектров сигналов прямого и обратного каналов. С выходов фильтров 8 и 9 сигналы прямого и обратного

0 каналов соответственно через усилители 10 и 11 и второй переключатель 17 поступают на информационные входы демодулятора 15. В режиме «ЧМ ртррой вход второго переключателя 17 закрыт и принимаемый сигнал прямого канала с третьего входа устройства через второй согласующий трансформатор 7,усилитель 12, фильтр 8, усилитель 10 и второй выход второго переключателя 17 поступает на информационный вход демодулятора 15.

д Демодулятор 15 работает следующим образом.

В режиме «ФМ предельно ограниченный фазомодулированный сигнал прямого канала через второй вход демодулятора поступает на входы фазовых детекторов 24 и 25,

в которых производится суммирование по модулю два этого сигнала с когерентными сигналами (не показаны). Выходные сигналы фазовых детекторов через переключатель 28, первый и второй входы которого открыты, а третий -закрыт, поступают на

первые входы регистров 29 и 30 сдвига соответственно. С помощью импульсов, поступаю щих с третьего выхода счетчика 41 импульсов, в ячейки регистров 29 и 30 записывается информация с выходов фазовых детекторов

г 24 и 25. В промежутках между записью информации с отводов регистров 29 и 30 сдвига с помощью первого 31 и второго 32 коммутаторов считывается информация, по мере считывания которой в зависимости от состояния счетчика 41 и от значения

0 сигнала на выходе коммутаторов 31 и 32 (логические «О или «I) на выходах дешиф,раторов 33 и 34 появляются двоичные числа, соответствующие выборкам сигнала ;типа приподнятый косинус, которые суммируются сумматорами 35 и 36. Числа, накопленные в накапливающих сумматорах, поступают на интеграторь 37 и 38, которые вычисляют скользящее среднее нескольких огибающих сигналов на выходах фазовых детекторов 24 и 25, возникающих соответственно на выходах сумматоров 35 и 36 вследствие того, что количество отводов регистров 29 и 30 сдвига выбирается меньшим количества его ячеек, поскольку для увеличения точности при демодуляции ЧМ- или ФМ-сигналов необходима высокая тактовая частота на вторых входах регистров 29 и 30 сдвига. При равенстве количества отводов регистров 29 и 30 сдвига количеству их ячеек сумматоры 35 и 36 за период тактовой частоты должны успеть вычислить сумму чисел, поступающих с дешифраторов. При этом быстродействие накапливающих сумматоров должно быть высоким. Для снижения требований по быстродействию к накапливающим сумматорам количество отводов выбирается меньщим количестве ячеек, но после вычисления сумм производится вычисление скользящего среднего этих сумм. С помощью сумматоров 39 и 40 из последовательности чисел, поступающих с выходов интеграторов 37 и 38, вычитается постоянное число (порог) и определяются тем ;амым моменты манипуляции. Выход знакового разряда сумматора 39 является информационным выходом синфазного канала, а выход знакового разряда сумматора 40 - информационным выходом квадратурного канала. Сигналы с выходов синфазного и квадратурного каналов поступают на декодер42, в котором информация обоих каналов регенерируется и преобразуется в последовательность информационных импульсов, поступающих на первый выход устройства. При приеме ЧМ-сигнала обратного канала предельно ограниченный сигнал обратного канала через третий вход демодулятора поступает на вход формирователя 26 коротi6 ких импульсов, где осуществляется преобразование входного сигнала в последовательность коротких импульсов, моменты появления которых совпадают с моментами пересечения входным сигналом нулевой оси. С выхода формирователя 26 импульсы поступают на первый вход формирователя 27 импульсов постоянной длительности, формирующего импульсы, длительность которых меньще длительности полупериода верхней частоты манипулированного сигнала. Эти импульсы поступают на первый вход реверсивного счетчика 43, на второй вход которого поступают импульсы с генератора 13. В реверсивном счетчике 43 производится выделение огибающей ЧМ-сигнала обратного канала, и с помощью порогового блока 44 выделяются моменты манипуляции. Выход порогового устройства является третьим выходом обратного канала. В режиме «ЧМ третий вход переключателя 28 открыт и предельно ограниченный ЧМ-сигнал прямого канала через второй информационный вход демодулятора 15, формирователи 26 и 27 и переключатель 28 поступает на первые входы регистров 29 и 30 сдвига. Дальнейщая обработка ЧМсигнала происходит аналогично обработке ФМ-сигнала. Знаковый выход одного из сумматоров 39 и 40 является вторым информационным выходом устройства. Таким образом, предлагаемое устройство преобразования сигналов может работать в режиме с «ЧМ со скоростью 600- 1200 бит/с, что расширяет его функциональные возможности. Использование предлагаемого устройства в системах передачи данных различного назначения позволит расширить сферу его применения, поскольку отпадает необходимость в отдельной разработке УПС с ЧМ на скорость работы 600-1200 бит/с.

Фиг.2

2

J

(Pf/2.j

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для обработки телеизмерительной информации | 1977 |

|

SU670958A2 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| УСТАНОВКА ДЛЯ НЕФТЯНОГО ОТОПЛЕНИЯ ФОРСУНКАМИ | 1925 |

|

SU2830A1 |

Авторы

Даты

1984-09-07—Публикация

1983-01-10—Подача