второй вывод первого резистора подключен к первому выводу потенциометра и первому выходу источника допусков напряжений, второй вывод второго резистора соединен с вторым выходом источника допусковых напряжений и вторым выводом потенциометра третий вывод которого подключен к выходу второго источника напряжения .

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для измерения погрешности аналого-цифрового преобразователя | 1982 |

|

SU1115219A1 |

| Устройство для измерения погрешнос-Ти цифРОАНАлОгОВОгО пРЕОбРАзОВАТЕля | 1979 |

|

SU817999A1 |

| Устройство для измерения погрешности цифро-аналогового преобразователя | 1980 |

|

SU902245A1 |

| Устройство для измерения времени установления цифроаналогового преобразователя | 1986 |

|

SU1432776A1 |

| Устройство для контроля и настройки параметров | 1989 |

|

SU1647521A1 |

| Устройство для измерения времени установления выходного сигнала цифроаналогового преобразователя | 1990 |

|

SU1716601A2 |

| Вероятностный преобразователь аналог-код | 1984 |

|

SU1229950A1 |

| Программируемое устройство допускового контроля | 1989 |

|

SU1620950A1 |

| Устройство для контроля многовыходных цифровых узлов | 1984 |

|

SU1176333A1 |

| Устройство для измерения погрешности аналого-цифрового преобразователя | 1980 |

|

SU884125A1 |

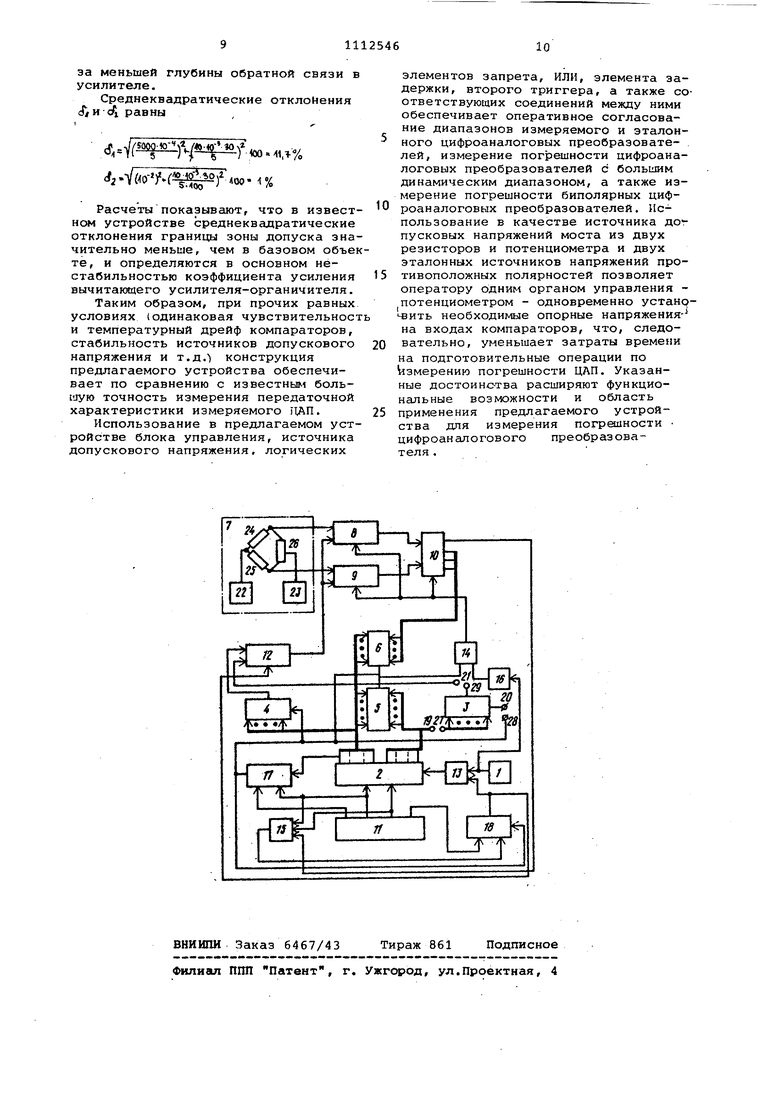

1. УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ПОГРЕШНОСТИ ЦИФРОАНАЛОГОВЫХ ПРЕОБРАЗОВАТЕЛЕЙ , содержащее генератор импульсов , выход которого соединен с входом элемента задержки, блок сравнения кодов, первые входы которого соединены с первыми входами эталонного циЛроаналогового преобразователя и с первыми выходами 2п-разрядного счетчика, вторые выходы которого подключены к первой выходной шине и вторым входам блока сравнениякодов, выход которого соединен с первым входом элемента И, блок вычитания , первый вход которого подключен к выходу эталонного цифроаналогового преобразователя, два компаратора, первый вход первого из которых соединен с выходом блока вычитания, управляющие входы обоих компараторов подключены к выходу элемента И и управляклцему входу блока логической обработки, первый и второй входы которого подключены к выходам первого и второго компараторов соответственно, а первые выходы - к первым входам блока индикации, второй вход которого соединен с выходом первого триггера, и второй триггер, отличающееся тем, что, с целью повышения точности измерения и расширения функциональных возможностей, в него введены источник допускового напряжения, первый выход которого соединен с вторы 1 входом первого компаратора, второй выход - с первым входом второго компаратора, элемент ИЛИ, элемент запрета и блок управления, первый выход которого соединен с первыми входами первого триггера и 2празрядного счетчика, второй выход с вторым входом первого триггера, тре тий вход которого подключен к выходу старшего разряда 2п-разрядного счетчика, выход первого триггера - с второй выходной шиной, вторым входом эталонного цифроаналогового преобразователя и первым входом второго триггера, выход которого соединен g с управляющим входом блока вычитания и первым входом элемента запрета, (Л второй вход которого подключен к вы ходу генератора импульсов, выход с элемента запрета - с вторым входом 2п-разрядного счетчика, первые выхо-. ды которого соединены с вторыми входами блока индикации, третий вход- с третьим выходом блока управления и . первыгл входом элемента ИЛИ, второй вход которого подключен к первому выходу блока управления, третий вход к второму выходу блока логической обработки, а выход элемента ИЛИ - к второму входу второго триггера, третий вход которого соединен с четвертым выходом блока управления, при этом второй вход второго компаратора подключен к выходу блока вычитания, второй вход которого соединен с входной шиной, причем выход элемента задержки подключен к второму входу элемента И. 2. У :тройство по п. 1, отличающееся тем, что источник допускового напряжения выполнен на двух источниках напряжений противоположных полярностей, потенциометре и двухрезисторах, первые выводы которых соединены между собой и с выходом первого источника напряжения.

Изобретение относится к вычислительной и импульснойтехнике и может быть использовано для измерения погрешности цифроаналоговых преобразователей .

Известно устройство для измерения погрешности цифроаналоговых преобразователей, содержащее генератор импульсов, эталонный цифроаналоговый преобразователь, счетчик, блок сравнения кодов, индикатор, блок усиления вычитания, аналоговое запоминающее устройство Cll.

Недостатком данного устройства является ограниченная точность измерения погрешности цифроаналогового преобразователя (ЦАП),

Известно также устройство для измерения погрешности ЦАП, содержащее генератор импульсов, выход которого соединен с входом элемента задержки. блок сравнения кодов, первые входы которого соединены с первыми входами эталонного цифроаналогового преобразователя и с первыми выходами 2п-разрядного счетчика, вторые выходы которого подключены к первой выходной шине и вторым входам блока сравнения кодов, выход которого соединен с пepвы 1 входом элемента И, блок вычитания, первый вход которого подключен к выходу эталонного цифроаналогового преобразователя, два компаратора, первый вход первого из которых соединен с выходом блока вычитания, управляющие входы обоих компараторов подключены к выходу элемента И и управляющему входу блока логической обработки, первый и второй входы которого подключены к выходам первого и второго компараторов соответственно, а первые выходы - к первьлм входам блока индикации, второй вход которого соединен с выходом первого триггера, второй триггер и шину Сброс, выход которой соединен с первым входом первого триггера и пер-; BhiM входом 2п-разрядного счетчика

Недостатками известного устройства являются ограниченная точность измерения, обусловленная недостаточной чувствительностью компараторов (единицы МВ) и не позволяющая измерять погрешности высокоразрядных , и ограниченные функциональные

возможности, так как известное устройство не измеряет погрешности ЦАП

с диапазоном, превышающим допустимые

значения синфазных и дифференциальных 5 напряжений компараторов. Кроме того, затраты времени оператора на предварительные операции по согласованию диапазона измеряемого цифроаналогового преобразователя с диапазоном эта10 лонного цифроаналогового преобразователя большие.

Цель изобретения - повышение точности измерения и расширение функциональных возможностей.

5 Поставленная цель достигается тем, что в устройство для измерения погрешности цифроаналоговых преобразователей, содержащее генератор импульсов, выход которого соединен

0 с входом элемента задержки, блок

сравнения кодов, первые входы которого соединены с первыми входами эталонного цифроаналогового преобразователя и с первыми выходами 2п-разряд5 ного счетчика, вторые выходы которого подключены к. первой выходной umне и вторым входам блока сравнения кодов, выход которого соединен с первым входом элемента И, блок вьтчита„ ния, первый вход которого подключен к выходу эталонного цифроаналогового преобразователя, два компаратора, первый вход первого из которых соединен с выходом блока вычитания, управляющие входы обоих компараторов под ключены к выходу элемента И и управляющему входу блока логической обработки, первый и второй входы которого подключены к выходам первого и второго компараторов соответственно,

0 а первые выходы - к первым входам блока индикации, второй вход которого соединен с выходом первого триггера, и второй триггер, введены источник допускового напряжения, пер5 вый выход которого соединен с вторым входом первого компаратора, второй выход - с первым входом второго компаратора, элемент ИЛИ, элемент запрета и блок управления, первый вып ход которого соединен с первыми входами первого триггера и 2п-разрядного счетчика, второй выход - с вторым входом первого триггера, третий вход которого подключен к выходу старшего разряда 2n-разрядного счетчика, выход первого триггера - с второй BIJходной шиной, вторым входом эталонного цифроаналогового преобразоватеfiH и. первым входом второго триггера, Ьыход которого соединен с управляющим входом блока вычитания и первым Входом элемента запрета, второй вход которого подключен к выходу генератора импульсов, выход элемента запрета - с вторым входом 2п-разрядного счетчика, первые выходы которого соединены с вторыми входами блока индикации, третий вход - с третьим выходом блока управления и первым входом элемента НЛН, второй вход которого подключен к первому выходу бл ка управления, третий вход - к второму выходу блока логической обработ ки, а выход элемента ИЛИ - к второму входу второго триггера, третий вход которого соединен с четвертым выходом блока управления, при этом второй вход второго компаратора подключен к выходу блока вычитания, вто рой вход которого соединен с входной шиной, причем выход элемента задержки подключен к второму входу элемента И. Кроме того, источник допускового напряжения выполнен на двух источниках напряжений противоположных поляр ностей , потенцио 1етре и двух резис горах, первые выводы которых соединены между собой и с выходом первого источника напряжения, второй вывод первого резистора подключен к перво му выводу потенциометра и первому вы ходу источника допусков напряжений, второй вывод второго резистора соед нен с вторым выходом источника допусковых напряжений и вторым выводом потенциометра, третий вывод которог подключен к выходу второго источник напряжения. На чертеже приведена структурная схема устройства для измерения погрешности цифроаналогового преобраз вателя. Устройство содержит генератор 1 импульсов, 2п-разрядный счетчик 2, измеряемый цифроаналоговый преобразователь 3, эталонный цифроаналоговый преобразователь 4, блок 5 сравнения кодов, блок 6 индикации, исто ник 7 допусковых напряжений противо положных полярностей, компараторы 8 и 9, блок 10 логической обработки, блок 11 управления, вычитающий усилитель-ограничитель 12 с программир емыг/ коэффициентом усиления, логические элементы 13 запрета, И 14 и ИЛИ 15. элемент 16 задержки у тригге ры 17 и 18, первую выходную шину 19 входного кода вторую выходную шину 20 и входную тину 21 выходного сигнала для подключения изменяегюго |ЦАП 3, эталонные источники 22 и 23 напряжений противоположных полярностей, резисторы 24 и 2S и потенциометр 26. Шины 27-29 представляют собой входные и выходную шины измерительного цифроаналогового преобразорателя. Генератор 1 импульсов подключен через элемент 13 запрета к второму входу (синхронизации) 2п-разрядного счетчика 2 и через элемент 16 задерж- ки - к первому входу элемента И 14. Вторые выходы (младшие разряды) 2п разрядного счетчика 2 соединены через шину 19 с входами измеряемого цифроаналогового преобразователя 3 и с вторыми входами блока 5 сравнения кодов. Первые выходы (старшие разряды ) 2п-разрядного счетчика 2 соединены с входами эталонного цифроаналогового преобразователя 4, с первыми входами блока 5 сравнения кодов и с вторыми входами блока 6 индикации. Выходы эталонного 3 и измеряемого 4 через шину 21) цифроаналоговых преобразователей соединены с первым и вторым входами вы 1итаю1чего блока (, усилителя-органичителя 12, выход которого подключен к первому входу компаратора 8 и второму входу компаратора 9. Источник 7 допусковых напряжений противоположных полярностей выполнен в виде моста из резисторов 24 и 25 и потенциометра 26, одна диагональ моста подключена к второму входу компаратора 8 и к первому входу компаратора 9, другая соединена с выходами эталонных источников 22 и 23 напряжений противоположных полярностей. Выходы компараторов В и 9 через блок 10 логической обработки соединены с первыми входами блока 6 индикации и с вторым входом элемента ИЛИ 15. Входы управления (стробирования) компараторов 8 и 9 и блока 10 логической обработки соединены с выходом элемента 14 И, второй вход которого подключен к выходу блока 5.. сравнения кодов. Первый выход блока 11 управления соединен с первыми входами (установки в О) 2п -разрядного счетчика 2 и первого триггера 17 и с вторым входом элемента 15 или; второй выход блока 11 управления - с входом установки в 1 первого триггера 17; третий выход блока 11 управления - непосредственно с входом установки 1 2п-разрядного счетчика 2 и с вторым входом элемента 15 ИЛИ, выход которого соединен с вторым входом (установки в 1) второго триггера 18. Четвертый выход блока 11 управления соединен с третьим входом установки в О второго триггера 18,выход которого подключен к входу управления коэффициентом усиления вычитающего усилитe IЯгOpгaничитeля 12 и к первому входу элемента 13 запрета. Старший разряд 2п-разрядного счетчика 2 сое динен с третьим входом (синхронизации ) первого триггера 17, выход которого подключен к управляющим входам разряда знак.а измеряемого 3 (че рез шину 20) и эталонного 4 цифроаналоговых преобразователей, к третьему входу блока б индикации и к первому входу (синхронизации ) второ го триггера 18. Устройство работает следующим об разом. С помошью шин 19 и 27, 20 и 28, 21 и 29 измеряемый цифроаналоговый преобразователь 3 подключают к устройству, в исходном состоянии, после про;хождения импульса из первого выхода блока 11 управления, устанавливаются в нулевое состояние 2п-разрядный счетчик 2 и первый триггер 17, а второй триггер 18 - в состояние 1 На управляющем входе элемента 13 за прета действует сигнал 1, и импул сы с генератора 1 импульсов не проходят на вход синхронизации 2п-разрядного счетчика 2. С прямого выхода второго триггера 18 сигнал 1 поступает на вход управления вычитающего блока (усилителя-органичите ля) 12, что вызывает увеличение его коэффициента усиления. На входах блока 5 сравнения кодов действуют н левые коды и на его выходе устанавливается уровень 1, обеспечивающий прохождение через элемент И 14 импульсов с выхода элемента 16 заде жки на входы стробирования компараторов 8 и 9 и блока 10 логической обработки. Выходное напряжение эталонного цифроаналогового преобразователя 4 равно нулю, а выходное напряжение измеряемого цифроаналогового преобразователя 3 может или равняться нулю, или отличаться от нулевого уровня. При отклонении выходного напряжения измеряемого цифроаналогового преобразователя 3 от нуля (в блоке индикации б высвечен индикатор Выше или Ниже) операт устанавливает нулевое напряжение подстроечными элементами измеряемого цифроаналогового преобразователя 3, используя показания блока 6 индикации (ПО появлению сигнала Годен). Увеличенный коэффициент усиления вычитающего усилителя-ограничителя 12 обеспечивает высокую точность установки нулевого напряжения на выходе измеряемого цифроанало гового преобразователя 3 (до долей младшего разряда). После подстройки нуля измеряемого цифроаналогового преобразователя 3 из третьего выхода блока 11 управления передается сигнал, устанавлива ющий 2п-разрядный счетчик 2 в соетояние 1. Второй триггер 18 остается в состоянии 1, и коэффициент усиления вычитающего усилителя-ограничителя 12 сохраняется увеличенным. Первый триггер 17 остается в нулевом состоянии, что соответствует, например, положительному значению знакового разряда цифрового кода 2п-разрядного счетчика 2. Оператор корректирует усиление измеряемого ЦАП 3. По показаниям блока б индикации ( по появлению сигнала Годен) устанавливается максимальное выходное напряжение измеряемого цифроаналогового преобразователя 3, равное выходному напряжению эталонного цифроаналогового преобразователя 4. Увеличенный коэффициент усиления вычитающего усилителя-ограничителя 12 обеспечивает . согласование выходных напряжений измеряемого 3 и эталонного 4 цифроаналоговых преобразователей с точностью до долей младшего разряда. При измерении погрешности биполяр ого цифроаналогового преобразоватейя с второго выхода блока iT. управления подается сигнал на вход установки в 1 первого триггера 17. Состояния 2п-разрядного счетчика 2 и второго триггера 18 сохраняются прежними (1). в единичном состоянии первого триггера 17 разряд знака соответствует отрицательному цифровому КОЛУ 2п-разрядного счетчика 2, и цифроаналоговые преобразователи 3 и 4 вырабатывают напряжения отрицательной полярности. Подстроечными элементами корректируется усиление измеряемого цифроаналогового преобразователя 3 с выходн лм напряжением эталонного цифроаналогового преобразователя 4 (аналогично по сигналу Годен в блоке индикации). После проведения подстройки нуля и коэффициента передачи измеряемого цифроаналогового преобразователя 3 с блока 11 управления последовательно передаются импульсные сигналы с первого и четвертого выходов. По сигналу Сброс 2п-разрядный счетчик 2и первый триггер 17 устанавливаются в нулевое состояние, и по сигналу Пуск второй триггер 18 устанавливается также в нулевое состояние. На управляющем входе элемента 13 запрета появляется уровень О, уменьшается коэффициент усиления вычитающего блока 12, от генератора 1 импульсов через элемент 13 запрета импульсы проходят на вход синхронизации 2п-разрядного счетчика 2. Счетчик 2 подсчитывает импульсы от генератора 1 импульсов и на выходах младших и старших разрядов изменяются цифровые коды. При изменении цифровых кодов на выходах измеряемого 3и эталонного 4 цифроаналоговых преобразователей появляются линейноизменяющиеся во времени напряжения ступенчатой Форгла. При этом протяжен ность каждой ступени эталонного цифроаналогового преобразователя 4 в два раза больше, чем у -измеряемого цифроаналогового преобразователя 3, что позволяет использовать в качестве эталонного менее быстродействующий, но более точный цифроаналоговый преобразователь. При равенстве кодов младших и старишх разрядов 2п-разрядного счетчика 2 блок 5 срав нения кодов вырабатывает сигнал, раз решающий сравнение разности выходных напряжений эталонного 4 и измеряемого 3 цифроаналоговых преобразователей с зоной допуска формируемой источником 7 допусковых напряжений противоположных полярностей. Если усиленная разность выходных напряжений цифроаналоговых преобразователей 4 и 3 на выходит за ,предел д установленного допуска (определенная часть младшего разряда, большая, чем при проведении подстройки нуля и коэффициента передачи измеряемого цифро аналогового преобразователя 3, то измерение автоматически продолжаетс (на блоке 6 индикации вспыхивает ин дикатор Годен) . При выходе разнос ти выходных напряжений цифроаналого вых преобразователей 4 и 3 за преде лы допуска в блоке б индикации заго рается индикатор Выше или Ниже зоны допуска, и импульс Не годен блока 10 логической обработки через элемент 15 ИЛИ проходит на вход установки в 1 триггера 18. При этом триггер 18 переключается в сос тояние 1, элемент 13 запрета не пропускает импульсы от генератора 1 импульсов на вход синхронизации 2п-разрядного счетчика 2. В блоке б индикации высвечивается код 2п разрядного счетчика 2, при котором происходит останов счета, и информация о знаке кода, поступающая от первого триггера 17. Если останов 2п-разрядного счетчика 2 не происходит при состояниях первого тригге ра 17 О и 1, то при переключени его из 1 в О триггер 18 перебрасывается в состояние 1 и запре щает прохождение импульсов синхронизации на вход 2п-разрядного счетчика 2. В блоке 6 индикации высвечи вается результирующая информация Годен. Точность известного и предлагаемого УСТРОЙСТВ зависит от многих факторов. в частности от стабильности коэффициентов передачи вычитающего и суммирующего усилителей, температурного дрейфа пороговых уро ней компараторов, напряжения смещения, входных токов, чувствительности компараторов и т.д. Оценка точности сравниваемых объктов проводится по среднеквадратич-1 ому отклонению границы, например, ерхней зоны допуска. В известном устройстве нестабиль - а Ki ость коэффициента передачи --- , де К 1 усилителя, суммирующего ыходное напряжение Uj эталонного ифроаналогового преобразователя с апряжением Uq источника допусковоо напряжения вызывает сдвиг верхей границы зоны допуска. .Ug + Uq)uK, Поскольку Utj сохраняется постояным, а Ug изменяется при увеличении ода, сдвиг верхней границы достигат максимума в конце диапазона пифоаналогового преобразователя U(-uft,yx ( , - Приближение учитывает то, что-UQ оставляет часть младшего разряда 1АП. Относительное температурное изенение порога срабатывания компаратора ) УПОР поР где п. мкВ/°С - температурный коэффициент порога срабатывания компаратора ) и пор - поооговый уровень составляющий часть (1/4 или 1/В) младшего значащего разряда. Среднеквадратичное отклонение «У, верхней границы зоны допуска в базовом объекте составляет с l (( Уа-гк.f UnopUnop В данном объекте температурный дрейф компаратора пересчитывается через коэффициент усиления Kj. вычитающего усилителя-ограничителя и среднеквадратическое отклонение определяется йУпоР 1 URSP К Произведен расчет dj , d , полагая, что 500 мВ, 4.КД/К, 10- , t 10 мкВ/°С, AT 30, Unop 5 мВ (что составляет пpи 1epнo 1/4 часть младшего значащего разряда 8-разрядного ЦАП), К 100, а 10 , т.е. в Кг 100 раз больше, чем у суммирук 1его усилителя с К i 1, изг

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для измерения погрешности цифро-аналогового преобразователя | 1974 |

|

SU600719A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для измерения погрешности цифро-аналогового преобразователя | 1980 |

|

SU902245A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1984-09-07—Публикация

1982-11-10—Подача