первым выходом блока управления , а выход - с вторым входом второго ариф метического блока, причем-второй вход блока логической обработки соединен с четвертым выходом блока управления, третьи входы которого соединены с входами цифроаналогового преобразователя,

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для измерения погрешности аналого-цифрового преобразователя | 1980 |

|

SU884125A1 |

| Аналого-цифровой преобразователь с коррекцией динамической погрешности | 1987 |

|

SU1607076A1 |

| Устройство для измерения погрешности цифро-аналоговых преобразователей | 1982 |

|

SU1112546A1 |

| Устройство аналого-цифрового преобразования | 1987 |

|

SU1559405A2 |

| Параллельно-последовательный п-разрядный аналого-цифровой преобразователь с автоматической коррекцией функции преобразования | 1988 |

|

SU1732471A1 |

| Устройство для сопряжения ЦВМ с аналоговыми объектами | 1986 |

|

SU1425698A2 |

| СПОСОБ И УСТРОЙСТВО КОРРЕКЦИИ ПОГРЕШНОСТЕЙ АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ | 2007 |

|

RU2352060C1 |

| Аналого-цифровой преобразователь | 1980 |

|

SU1117835A1 |

| Функциональный аналого-цифровой преобразователь | 1985 |

|

SU1260979A1 |

| Устройство для регистрации информации | 1989 |

|

SU1698895A1 |

УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ПОГРЕШНОСТИ АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАТЕЛЯ, содержащее генератор тактовых импульсов, выход которого соединен с первым входом блока управления , второй вход которого соединен с шиной Пуск, первый выход с первыми входами (n+m)-разрядного счетчика, регистра, блока регистрации, второй выход - с первой выходной шиной устройства, вторая шина которого соединена с выходом (п+т)-разрядного цифроаналогового преобразователя, а входная шина с первым входом первого арифметического блока, второй вход которого соединен с выходами разрядов, кроме старшего разряда, (п+т)-разрядного счетчика и входами (n+m)разрядного цифроаналогового преобразователя, а выход - с вторым входом регистра, выход которого соединен с первым входом второго арифметического блока, выход которого соединен с первым входом блока логической обработки, выход которого соединен с вторым входом блока регистрации, отличающееся тем, что, с целью расширения функциональ ых возможностей путем обеспечения измерения динамической погрешности, в него введены блок памяти, блок определения кодового перехода, элементИ, блок элементов И, элемент ИЛИ, элемент запрета, элемент равнозначности, два триггера, первый вход первого из которых соединен с первым выходом блока управления, второй вход - с третьим выходом блока управления, а выход - с вторым входом (п+га)-разрядного счетчика и пер§ вым входом элемента И, второй вход которого соединен с выходом второго (Л триггера и инверсным входом элемента запрета, а выход - с первым входом элемента ИДИ, второй вход которого соединен с выходом элемента запрета, а выход - с вторым входом первого арифметического блока, входом старшего разряда (п+т)-разрядного цифроаналогового преобразователя и перО1 вым входом элемента равнозначности, второй вход которого соединен с выхоКд дом старшего разряда (n+m)-разрядного счетчика, первым входом второго триг & гера и прямь1м входом элемента запрета, а выход - с первыми входами блока элементов И, вторые входы которого соединень с входной шиной устройства, а выход - с первым входом блока определе 1ия кодового перехода, второй вход которого соединен с вторым входом второго триггера и с первым выходом блока управления, а выход - с третьим входом регистра, при этом первым вход блока памяти соединен с выходом регистра, второй вход - с

Изобретение относится к вычислительной технике, предназначено для автоматического измерения погрешности аналого-цифрового преобразователя напряжения (тока) в код и обеспечивает получение информации о динамических погрешностях с представлением результатов измерения в цифровой форме.

Известно устройство для контроля качества работы п -разрядного АЦП, содержащее (п+т)-разрядные счетчики и эталонный цифроаналоговый преобразователь, ключи, входы управления которых подключеггы к шине Конец преобразования, .п -разрядный ЦАП, вычитаю1ций усилитель, входы которого подкдпочены к выходам (п+га)- и И -разрядных цифроаналоговы преобразователей, и регистрирующее

устройство осциллоскоп tn. I

Недостатком данного устройства является низкая точность оценки качества АЦП.

Наиболее близким по технической сущности является устройство для измерения погрешности аналого-цифрового преобразователя, содержащее генератор тактовых импульсов, выход которого соединен с первым входом блока управления, второй вход кото- рого соединен с щиной Пуск, первый выход - с первыми входами (.n+m)разрядного счетчика, регистра, блока регистрации, второй выход - с первой выходной шиной устройства, вторая выходная шина которого соединена с выходом (n+m)-разрядного цифроаналогового преобразователя, а входная шина - с первым входом первого арифметического блока, второй вход которого соединен с -выходами разрядов, кроме старшего разряд, (n+m)-разрядного счетчика и входами (n+m)-разрядного цифроаналогового преобразователя, а выход - с вторым входом регистра, выход которого соединен с первым входом второго арифметического блока, выход которого соединен с первым входом блока логической обработки, выход которого соединен с вторым входом блока регистрации C2j.

Недостатком известного устройства является ограниченная область его применения.

Цель изобретения - расширение функфункциональных возможностей путем Ъбеспечения измерения динамической погрешности и ее составляющих.

Поставленная цель достигается тем, что в устройство для измерения погрешности аналого-цифрового преобразователя, содержащее генератор тактовых импульсов, выход которого соединен с первым входом блока управления, второй вход которого соединен с шиной Пуск, первый выход - с первыми входами (п+т)-разрядного счетчика, регистра, блока регистрации, второй выход - с первой выходной шиной устройства, вторая выходная шина которого соединена с выходом (n+m)-разрядного цифроаналогового преобразователя, а входная

шина - с первым входом первого арифметического блока, второй вход которого соединен с выходами разрядов, кроме старшего разряда (п+га)-разрядного счетчика и входами (n+m)-разрядного цифроанапогового преобразователя , а выход - с вторым входом регистра, выход которого соединен с первым входом второго арифметического блока, выход которого соединен с первым входом блока логической обработки, выход которого соединен с вторым входом блока регистрации, введены блок памяти, блок определения кодового перехода, элемент И, блок элементов И, элемент ИЛИ, элем нт запрета, элемент равнозначности, два триггера,первый вход первого из которых сое;щнен с первым выходом блока упраапения, второй вход с третьим выходом блока управления, а выход - с вторым входом (n+m)-разрядного счетчика и первым входом элемента И, второй вход которого соединен с выходом второго триггера и инверсным входом элемента запрета, а выход - с первым входом элемента ИЛИ, второй вход которого соединен с выходом элемента запрета, а выход - с вторым зходом первого арифметического блока, входом старшего разряда (п+т)-разрядного цифроаналогового преобразователя и первым входом элемента равнозначности, второй, вход которого соединен с выходом старшег9 разряда (п+т)-разрядного счетчика, первым входом второго триггера и входом элемента запрета, а выход - с первыми входами блока элементов И, вторые входы которого соединены с входной шиной устройства, а выход - с первым входом блока определения кодового перехода, второй вход которого соединен с вторым входом второго триггера и с первым выходом блока управления, а выход - с третьим входом регистра, при этом nepnbrii вход блока памяти соединен с выходом регистра, второй вход - с первым выходом блока управления, а выход - с вторым входом второго арифметического блока, причем второй вход блока логической обработки соединен с четвертым выходом блока управления , третьи входы которого соединены с входами цифроаналогового преобразователя.

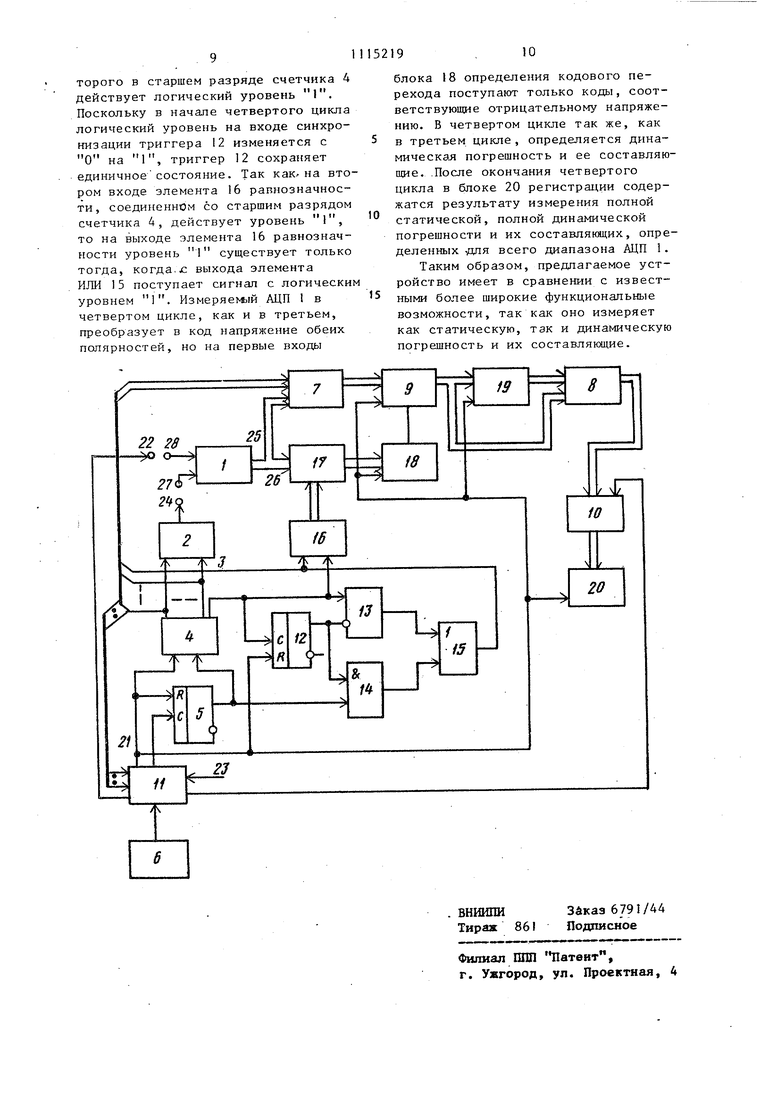

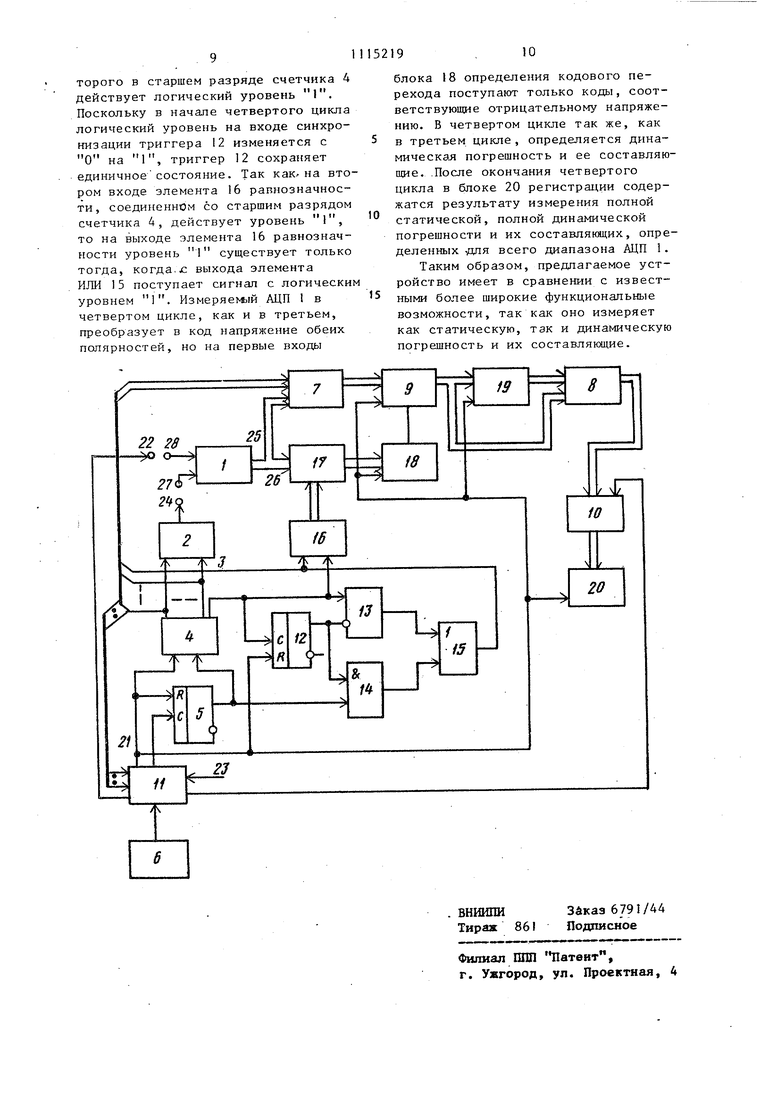

На чертеже приведена структурная схема предлагаемого устройства.

Устройство содержит ц-разрядный измеряемзш аналого-цифровой преобразователь (АЦП1 1, эталонный (n+m)разрядный цифроаналоговый преобразователь (ЦАП) 2, шину знакового разряда 3, (п-ьт)-разрядный счетчик 4, первый триггер 5, тактовый генератор 6, арифметические блоки 7 и 8, регистр 9, блоки логической обработки 10 и управления 11, второй триггер 12, логический элемент 13 запрета, элементы И 14, ИЛИ 15, элемент 16 равнозначности, блок 17 элементов И, блоки определения кодового перехода 18, памяти 19, регистрации 20, шину 21 сброса, первую

выходную шину 22, шину 23 пуска,вторую выходную шину 24, входную шинуГ5, шины 26-28 измеряемого анало1о-циф рового преобразователя. Входы эталонного ЦАП 2 соеди}1е}п.1

с выходами счетчика 4, объединенными с вторыми входами первого арифметического блока 7, а шина 3 знакового разряда соединена через элемент

ИЛИ 15 с выходами элемента И 14 и элемента 13 запрета. Старший разряд счетчика 4 соединен с первым входом триггера 12, с прямым входом элемента 13 запрета и с одним входом элемснта 16 равнозначности, инверсньнЧ вход элемента 13 запрета и второй вхол; элемента И 14 подключены к прямому выходу триггера 12, а первый вход элемента И 14 и второй вход счстчи-

ка 4 - к выходу триггера 5, второй вход которого соединен с третьим выходом блока 11 управления и с выходом генератора 6. Выходы АЦП 1 подключенъ к выходной шине 25. Первые входы блока элементов 17 объединены и соединены с выходом элемента 16 равнозначности, первый вход которого подключен к шине 3 знакового разряда. Выходы первого арифметического блока 7 соединены через

регистр 9 с первыми входами блока 19 памяти и с первыми входами второго арифметического блока 8, вторые входы которого подюпочены к в 1ходам блока 19 памяти, а рыходы второго арифметического блока 8 соединоры через блок 10 логической обработки с блоком 20 регистрации. Третий

вход регистра 9 подключен к вы.ходу блока 18 определения кодового перехода, входы которого соединены с выходами п элементов блока 17 элементов И.

Выходные шины блока 11 управления подключены к соответствующим шинам 21 сброса, к первой выходной шине 22 синхронизации блоков устройства. Блок 1I управления запускается по шине 23 пуска. Выходы счетчика 4 соединены с третьими входами блока 11 управления, а второй вход блока 10 логической обработки соединен через блок 11 управления с выходомm-го разряда счетчика 4. Перед началом измерения погрешностей шины 26-28 аналого-цифрового преобразователя 1 соединяются соответственно с шинами 25, 24 и 22 устройства. Устройство работает следующим образом. По сигналу Сброс по шине 21 сброса на выходах счетчика 4 устанавливается нулевой код, выходное напряжение эталонного ЦАП 2 устана ливается равным йулю, триггеры 5 и 12,регистр 9, блок 19 памяти, блок 20 регистрации, блок 18 определения кодового перехода обнуляются и на выходе элемента ИЛИ 15 и ши не 3 знакового разряда устанавливаются уровни логического О, на обоих входах- элемента 16 равнозначности логические уровни равны О, .с его выхода на первые входы блока элементов И 17 поступает уровень логической 1. По сигналу Пуск на шине 23 тактовые импульсы с ге.нератора 6 поступают через блок 1 управления на второй вход триггера 5 и на шину 22, Триггер 5 выраб тывает импульсную последовательность со скважностью, равной двум, частота которой определяет частоту смены кода в счетчике 4. ЦАП 2 вырабатывает испытательно напряжение для АЦП 1 в соответствии с кодом счетчика 4 и логическим уровнем на шине 3 знакового разряда. АЦП 1 преобразует выходное напряжение ЦАП 2 в код, причем частота преобразования равна частоте генератора 6, при этом при преобразовании АЦП 1 нулевого выходно напряжения ЦАП 2 в регистре .9 сохраняется нулевой код, если смещегше передаточной характеристики АЦП 1 не превьш1ает эквивалента млад шего разряда АЦП 1. Нулевой код с выхода регистра 9 записывается с тактовой частотой в блок 19 памяти до тех пор, пока на выходе АЦП.1 н появится код, отличным от нулевого 1 Измерение погрешности АЦП 1 выпо няется за четыре цикла. В первом и втором измеряется статическая погрешность при поступлении с выхода ЦАП 2 на вход АЦП 1 линейно нарастаюш;его и линейно убывающего напря жений ступенчатой . В первом цикле на выходе -элемента ИЛИ 15 и на выходе старшего разряда счетчика 4 существуют логические уровни, равные О, ввиду чего на выхо де элемента 16 равнозначность действует уровень логической 1. Во втором цикле на выходе элемента ИЛИ 15 и на выходе старшего разряда счетчика 4 действуют логические уровни 1 и на выходе элемента 16 равнозначности сохраняется уровень логической 1. Сигнал с уровнем логической 1 с выхода элемента 16 равнозначности разрешает прохождение кода АЦП 1 через и элементов блока 17 элементов И на первые входы блока 18 определения кодового перехода, который вырабатывает сигнал записи выходного кода первого арифметического блока 7 в регистр 9 -только при изменении кода на выходах АЦП 1. В первом цикле при монотонном изменении кода счетчика 4 входное напряжение АЦП 1 изменяется с дискретностью, „ г.т составляющей 2 часть эквивалента мпадшего разряда АЦП 1. При достижении напряжением уровня кодового перехода изменяется выходной код АЦП 1. При передаточной характеристике АЦП 1, близкой к идеальной, изменение кода АЦП 1 (кодовый переход происходит через каждые 2 п тактов (частота смены кода) счетчика 4 в два раза меньше частоты генератора 6. Первый арифметический блок 7 вырабатывает разность кодов АЦП 1 и. счетчика 4. При этом разность кодов изменяется как за счет изменения кода счетчика, так и за счет изменения кода АЦП 1. Изменение кода разнос ти, происходящее при отсутствии кодового перехода в АЦП 1, не записывается в регистр 9, поскольку блок 1Ь определения кодового перехода не вырабатывает в этом случае сигнала записи кода разности в регистр 9. Разность кодов АЦП 1 и счетчика 4, полученная при наличии кодового перехода, записывается в блок 19 памяти с тактовой частотой до появления кодового перехода. Так как блок 19 памяти имеет последовательную выборку, -то только на первых входах второго арифметического блока 8, соединенных с выходами регистра 9, существуют коды, не равные нулевым. Коды, записанные в блок 19 памяти, представляют полную статическую погрешность АЦП 1 при нарастакяцем входном сигнале в первом цикле. Полная статическая погрешность, а также ее составляющие, список которых определяется функциональным составом блока 10 логической обработки, регистрируются а блоке 20. Работа блока 10 логической обработки регистрируется в блоке 20 и,синх ронизируется блоком 11 управления, при этом сигнал, прошедший с выхода Р7-ГО. разряда счетчика 4 через блок управления на блок Ю логической обработки, позволяет измерить стати ческую погрешность для всех точек передаточной характеристики измеряв мого АЦП 1.(п + т-ч1 После прохождения 2 -го импульса на вход счетчика 4 в старш разряде последнего устанавливается уровень логической 1. При этом триггер 12 сохраняет исходное состо ние, на инверсном входе элемента 13 запрета сохраняется нулевой логический уровень, а на его прямом вхо де действует уровень логической 1 что приводит к изменению уровня с О на 1 на выходе элемента ИЛИ 1 На обоих входах и следовательно на выходе элемента 16 равнозначности действуют логические уровни I. С этого времени начинается второй цик в течение которого эталонный ЦАП 2 вырабатывает линейно убывающее напряжение ступенчатой формы. При воз никновении кодовых переходов в . АЦП I разность кодов АЦП 1 и счетчи ка 4 проходит в регистр 9 и записывается в блок 19 памяти как полная статическая погрешность АЦП 1, преобразующего отрицательное напряжени В блоке 20 регистрации фиксируются дополнительно и составляющие статической погрешности. После поступления с триггера 5 -го импульса в старшем разряде счетчика 4 устанавливается уровень логического О. Поскольку на первом входе синхронизации триггера 12 логический уровень изменяется с 1 на О, то триггер 12 переходит в единичное состояние и на инверсном входе элемента 13 запрета, а также на .второй входе элемента И 14 устанавливается логический уровень 1. Ввиду этого на выходе элемента 13 запрета появляется логический уровень О, а так как первый вход элемента И 14 соединен с выходом триггера 5, то на вых де элемента ИЛИ 15 и следовательно на шине 3 знакового разряда и на первом входе элемента 16 равнозначности действует последовательность из 6 и 1. Последовательность из О и I существует в течение третьего и четвертого циклов, пока триггер 12 не возвратится в нулевое состояние при повторном переходе логического уровня с 1 на О в старшем разряде счетчика 4 после завершения четвертого цикла. Эталонный ЦАП 2 вырабаты вает в третьем и четвёртом циклах линейно изменяющееся во времени знакопеременное напряжение, которое преобразуется в код измеряемым АЦП 1. В третьем цикле в старшем разряде счетчика 4 действует логический уровень О и поэтому на выходе элемента 16 равнозначность логический уровень 1 существует в те интервалы времени, когда на шине 3 знакового разряда действует уровень О и ЦАП 2 вырабатывает положительное напряжение. Ввиду этого с выхода МШ 1 , преобразующего напряжение обеих полярностей,, на первые входы блока 18 определеш1я кодового перехода проходят только коды, соответствуюир е положительной полярности входного напряжения АЦП 1. При н-аличии кодового перехода аналогично как в первом и втором циклах, разность кода АЦП 1 и кода счетчика 4 записывается в регистр 9, блок 19 памяти поступает на первые входы второго арифметического блока 8. С началом цикла 3 на вторые входы второго арифметического блока начинают поступать с выходов блока 19 памяти коды, представляющие полную статическую погрешность АЦП 1, измеренную в первом цикле. Во втором арифметическом блоке 8 из полной погрешности АЦП 1, измеренной в третьем цикле ,- вычитается полная статическая погрешность, измеренная в первом цикле. Код разности на выходе второго арифметического блока 8 представляет динамическую погрешность измеряемого АЦП 1. Полная динамическая погрешность и ее составляющие, вычисленные в блоке 10 логической обработки, фиксируются в блоке 20 егистрах ии. После прохождения серии из 2 импульсов с выхода триггера 5 начинается четвертый цикл, в течение которого в старшем разряде счетчика 4 действует логический уровень 1. Поскольку в начале четвертого цикла логический уровень на входе синхронизации триггера 12 изменяется с О на 1, триггер 12 сохраняет единичное состояние. Так втором входе элемента 16 равнозначности, соединенном со старшим разрядом счетчика 4, действует уровень 1, то на выходе элемента 16 равнозначности уровень 1 существует только тогда, когда,JC выхода элемента ИЛИ 15 постулает сигнал с логическим уровнем 1. Измеряе 4|1Й АЦП 1 в четвертом цикле, как и в третьем, преобразует в код напряжение обеих полярностей, но на первые входы

блока 18 определения кодового перехода поступают только коды, соответствующие отрицательному напряжению. В четвертом цикле так же, как в третьем цикле , определяется динамическал погрешность и ее составляющие. .После окончания четвертого цикла в блоке 20 регистрации содержатся результату измерения полной статической, полной динамической погрешности и их составлякндих, определенных -для всего диапазона АЦП 1. Таким образом, предлагаемое устройство имеет в сравнении с известными более широкие функциональные возможности, так как оно измеряет как статическую, так и динамическую погрешность и их составляющие.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Экспресс-информация, сер | |||

| Приборы и элементы автоматической и вычислительной техники, реф | |||

| Автоматический огнетушитель | 0 |

|

SU92A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для измерения погрешности аналого-цифрового преобразователя | 1980 |

|

SU884125A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1984-09-23—Публикация

1982-01-20—Подача