(S) УСТРОЙСТВО для ИЗМЕРЕНИЯ ПОГРЕШНОСТИ

ЦИФРОАНАЛОГОВОГО ПРЕОБРАЗОВАТЕЛЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для измерения погрешности цифро-аналоговых преобразователей | 1982 |

|

SU1112546A1 |

| Устройство для контроля напряжений | 1990 |

|

SU1725190A1 |

| Устройство для измерения погрешнос-Ти цифРОАНАлОгОВОгО пРЕОбРАзОВАТЕля | 1979 |

|

SU817999A1 |

| Синтезатор частот | 1977 |

|

SU819976A1 |

| Устройство для измерения погрешности линейности цифро-аналогового преобразователя | 1980 |

|

SU884123A1 |

| Устройство измерения длительности импульсных сигналов | 1986 |

|

SU1476405A1 |

| УСТРОЙСТВО КОНТРОЛЯ ВОСПРИИМЧИВОСТИ РАДИОПРИЕМНИКА К ПОМЕХАМ | 1991 |

|

RU2032272C1 |

| Измеритель нелинейности цифро-аналоговых преобразователей | 1983 |

|

SU1112547A1 |

| Устройство для контроля цифроаналоговых преобразователей | 1980 |

|

SU919075A1 |

| Устройство для определения временного положения абсолютного максимума в реализации сигнала | 1985 |

|

SU1297003A1 |

I

Изобретение относится к вычислите льной и импульсной технике и может быть использовано для измерения погрешности цифрраналогового преобразователя.

Известно устройство для измерения погрешности цифроаналогового преобразователя (ЦАП), содержащее измеряемый ЦАП и эталонный ЦАП, генератор импульсов, счетчики, блок сравнения кодов, эле1«1ент вычитания и усиления, аналоговое запоминащее устройство (АЗУ) и индикатор 1.

Недостаток известного устройства- сложность реализации эталонного ЦАП и АЗУ, к точности и быстродействию которых предъявляются более высокие требования, чем к измеряемому ЦАП.

Известно также устройство для измерения погрешности цифроаналогового преобразователя, содержащее генератор импульсов, измеряемый и эталонный цифроаналоговые преобразователи,, счетчик , блок сравнения кодов, блок

суммирования, блок вычитания, блок логической обработки, два компаратора и индикатор, причем выходы младших и старших разрядов счетчика соединены соответственно с входами измеряемого и эталонного цифроаналоговых преобразователей, а также с первыми и вторыми входами блока сравнения кодов, выход эталонного цифроаналогового преобразователя подклю10чен к первым входам блоков суммирования и вычитания, выходы которых соединены с первыми входами компараторов, вторые входы компараторов подключены к выходу измеряемого цифро аналогового преобразователя, выходы компараторов соединены через блок логической обработки с первым входами индикатора 2 .

Однако данное устройство требует

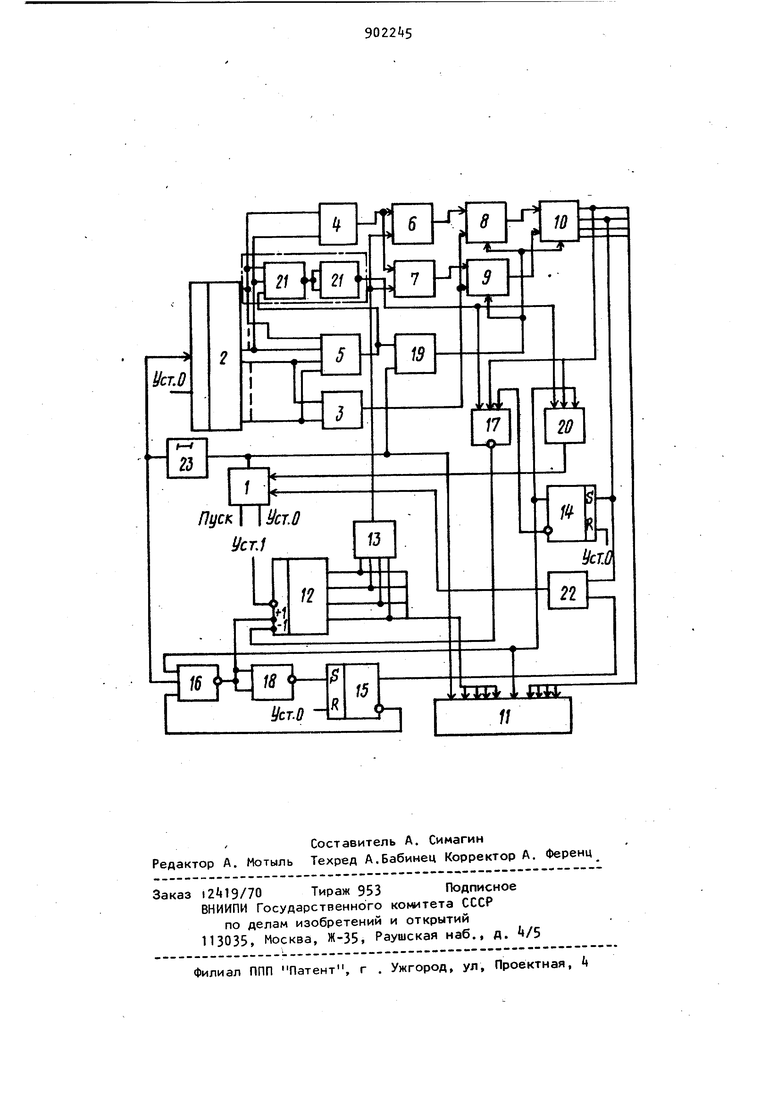

20 относительно больших затрат времени на проведение серии измерений в связи с тем, что оператор проводит вручную установку напряжения источника допускового напряжения и частоты ге нератора импульсов. Цель изобретения - уменьшение вр мени измерения погрешности ЦАП. Указанная цель достигается тем, что в устройство, содержащее генера тор импульсов, измеряемый и эталонный цифроаналоговый преобразователи счетчик, блок сравнения кодов, блок суммирования, блок вычитания, блок логической обработки, два компарато ра и индикатор, причем выходы младоаих и старших разрядов счетчика сое динены соответственно с входами измеряемого и эталонного цифроаналоговых преобразователей, а также с-первыми и вторыми входами блока сравнения кодов, выход эталонного цифроаналогового преобразователя подключен к первым входам блоков суммирования и вычитания, выходы которых соединены с первыми входами компараторов, вторые входы компараторов под ключены к выходу измеряемого цифроаналогового преобразователя, выходы компараторов соединены через блок логической обработки с первыми входами индикатора, введены элемент задержки, два триггера, реверсивный счетчик, дополнительный цифроанапоговый преобразователь, четыре эле мента И, два элемента И-НЕ, элемент НЕ, причем выход генератора Импульсов подключен к второму входу индикатора и к первому входу первого эле мента И и через элемент задержки к входу синхронизации счетчика и первому входу первого элемента И-НЕ, второй вход первого элемента И соединен с выходом .блока сравнения кодов и первым входом второго элемента И, выход первого элемента И подключен к третьим входам компараторов :и блока логической обработки, первы выход которого соединен с первыми входами Bfoporo элемента И-НЕ и тре его элемента И, второй выход блока логической обработки подключен к прямому входу первого триггера и первому входу четвертого элемента И старшие разряды счетчика соединены с вторыми входами второго элемента И, выход которого подключен к вторы входам третьего элемента И и второго элемента И-НЕ, третий вход которого соединен с инверсным выходом первог триггера, выход второго элемента Иподключен к пер0ому входу реверсивного счетчика, прямой выход первого триггера соединен с третьим еходом третьего элемента И, третьим входом индикатора и вторым входом первого элемента И-НЕ, выход которого подключен ко второму входу реверсивного счетчика и через элемент НЕ к прямому входу второго триггера, инверсный выход которого соединен с третьим входом первого элемента И-НЕ, прямой выход второго триггера подключен к второму входу четвертого элемента И, выход которого соединен с первым входом генератора, второй вход которого подключен к выходу третьего элемента И, выходы реверсивного счетчи к.a соединены с входами дополнительного цифроаналогового преобразователя и четвертыми входами индикатора, выход дополнительного цифроаналогового преобразователя подключен к вторым, входам блоков суммирования и вычитания . На чертеже приведена функциональная схема устройства измерения погрешности ЦАП. Устройство содержит генератор 1 импульсов, счетчик 2, измеряемый ЦАП 3, эталонный ЦАП k, блок 5 сравнения кодов, блоки суммирования 6 и вычитания 7, два компаратора 8 и 9, блок 10 логической обработки, индикатор 11, реверсивный счетчик 12, дополнительный ЦАП 13, два триггера и 15, два элемента И-НЕ 16 и 17, элемент НЕ 18, четыре элемента И 19 - 22 и элемент 23 задержки. Генератор 1 импульсов соединен через элемент 23 задержки с входом синхронизации счетчика 2 и первым входом первого элемента И-НЕ 16 и непосредственно с первым входом первой схемы И 19 и с вторым входом индикатора 11. Выходы младших и старших разрядов счетчика 2 соединены соответственно с входами измеряемого ЦАП, 3 и эталонного ЦАП 4, первыми и вторыми входами блока 5 сравнения кодов. Первый вход второго элемента И 21 подключен к выходу блока 5 сравнения кодов, а вторые входы элемента И 21 к выходам старших разрядов счетчика 2. Выходы эталонного ЦАП Ц соединены с первыми входами блоков суммирования 6 и вычитания 7, выходы которых подключены соответственно к первым входам компараторов 8 и 9 . Выход измеряемого ЦАП 3 подключен к вторым входам компараторов 8 и 9, выходы ко торых подключены к входам блока 10 логической обработки. Выход блока 5 сравнения кодов соединен с вторым входом первой схемы И 19, выход которой подключен к третьим входам компараторов 8,9 и блока 10 логической обработки. Btopыe входы блоков суммирования 6 и вычитания 7 подключены к выходу дополнительного ЦАП 13, входы которого соединены с выходами реверсивного счетчика 12. Первый вход реверсивного счетчика 12 подключен к выходу второго элемента И-НЕ 17, а второй вход к выходу первого элемента И-НЕ 16. Первые и вторык входы второго элемента И-НЕ 17 и третьего элемента И 20 попарно объ единены и подключены соответственно к первому выходу блока 10 логической обработки и к выходу второго элеменЧа И 21. Третий вход второго элемен та И-НЕ 17 соединен с инверсным выходом первого триггера 1. Третий вход третьего элемента И 20 и второй вход первого элемента И-НЕ 16 соединены с прямым выходом первого триггера 1А. Выход первого элемента И-НЕ 1б подключен к второму входу реверсивного счетчика 12 и через элемент НЕ 18 к прямому входу второго триггера 15 инверсный выход которого соединен с третьим входом первого элемента И-НЕ 16. Первый вход четвёртого элемента И 22 и прямой вход первого триггера 1 подключены к второму выходу блока 10логической обработки. Второй вход четвертого элемента И 22 соединен с прямым выходом второго триггера 15. Выход четвертого элемента И 22 подключен к первому входу генератора 1 импульсов, второй вход которого соединен с выходом третьего элемента И 20. Первый, второй, третий и четвертый входы индикатора под ключены соответственно к выходам бло ка 10 логической обработки, генератора 1 импульсов, прямому выходу пер вого триггера 1 и выходам реверсивного счетчика 12. Устройство работает следующим образом. При поступлении сигналов УстановкаО и Установка 1 происходит обну

ление счетчика 2, установка первого 14 и второго 15 триггеров в нулевое состояние, установка триггеров реуровня.

Если выходное напряжение измеряемого ЦАП 3 находится в пределах зоны 456 версивного счетчика 12 в единичное состояние, а для генератора. 1 импульсов устанавливается режим работы с минимальной частотой следования импульсов. При этом на выходах измеряемого ЦАП 3 и эталонного ЦАГ1 k устанавливаются напряжения, соответствующие нулевым кодам, а на выходе дополнительного ЦАП 13 устанавливается максимальное напряжение и блоки суммирования 6 и вычитания 7 формируют около нулевого уровня верхнюю и нижнюю границы зоны допуска. На всех . трех входах третьего элемента И 20 действуют сигналы О и, следовательно, на одном входе управления генератора 1 импульсов действует сигнал О, что обеспечивает работу генератора 1 импульсов с минимальной частотой. На первом и втором входах четвертого элемента И 22 действуют сигналы О и, следовательно, на другом входе управления генератора 1 импульсов существует сигнал О, что создает условия для прохождения импульсов с выхода генератора 1 импульсов в устройство измерения после по- . ступления на него сигнала Пуск. На первом и втором входах второго элемента И-НЕ 17 приложены сигналы Ю, а на третьем выходе 1. Поэтому к первому входу реверсивного счетчика 12 приложен сигнал 1. На первом и втором входах первого элемента И-НЕ 16 действуют сигналы О, а на третьем входе , Следовательно, и на втором входе реверсивного счетчика 12 дейс1вует сигнал 1. При поступлении сигнала Пуск импульсы с генератора 1 импульсов ачинают поступать на первый вход первой схемы И 19, элемент задержки 3 и на второй вход индикатора 11. Величина задержки элемента 23 задержки устанавли.вается на основании бреени обработки сигналов в первой хеме И 19, компараторах 8 и 9, блоке 10 логической обработки. Поэтому о момента поступления импульса с ыхода элемента 23 задержки на вход инхронизации счетчика 2 компараторы и 9 сравнивают выходное напряжение змеряемого ЦАП 3, соответствующее улевому входному коду, с зоной доуска, расположенной около нулевого допуска, то на втором выходе блока 10 логической обработки сохраняется сигнал О и триггеры I и 15 остаются в нулевом состоянии. Состояние выхода четвертой схемы И 22 не изме няется и, следовательно, на входе управления генератора 1 импульсов сохраняется сигнал О, разрешающий прохождение импульсов с выхода генератора 1 импульсов. При поступлении импульсов с выхода элемента 23 задержки на вход синхронизации счетчика 2 происходит изменение выходного кода счетчика 2 и, следовательно, напряжений на выхо дах измеряемого 3 и эталонного ЦАП При каждом равенстве кодов на первых и вторых входах блока 5 сравнения кодов выходное напряжение измеряемого ЦАП 3 сравнивается с верхним и нижним уровнями зоны допуска, котора смещается в соответствии с изменением напряжения на выходе эталонного ЦАП k. Блок 10 логической обработки вырабатывает сигнал, соответствующий результату сравнения. Изменение напряжения на выходе эталонного ЦАП k происходит с частотой в 2 раз меньшей (где п - число разрядов измеряемого ЦАП), чем частота изменения, напряжения на выходе измеряемого ЦАП 3. Работа эталонного ЦАП k с меньшей частотой обеспечивает завершение переходных процессов в эталонном ЦАП k к моменту сравнения, в связи с чем напряжение с выхода измеряемого ЦАП 3 сравнивается с установившимися значениями уровней зоны допуска. При нахождении, выходного напряжения измеряемого ЦАП 3 в зоне допуска процедура измерения для данной зоны допуска продолжается до поступления на вход синхронизации счетчика 2{.2 - 1) импульса. При поступлении (2 - 1) импульса на входах измеряемого ЦАП 3, эталонного ЦАП i, а так же на первых и вторых входах блока 5 сравнения устанавливаются единичные .коды (во всех разрядах 1). Есл напряжение на выходе измеряемого ЦАП 3 не вышло за пределы зоны допуска, то на первом выходе блока 10 логической обработки действует сигнал 1. На всех трех входах второго элемента И-Н 17 имеет сигналы 1, следовательно, на первом входе реверсивного счетчика 12 появляется сигнал О, счетчик работает в режиме вычитания и его выходной код уменьшается на единицу. При этом выходное напряжение дополнительного ЦАП 13 уменьшается, что вызывает сужение зоны допуска, формируемой блоками суммирования 6 и вычитания 7. С поступлением 2° импульса происходит переполнение счетчика 2, на входах измеряемого ЦАП 3 и эталонного ЦАП вновь появляются нулевые коды. Далее процедура измерения повторяется для новой зоны допуска. Описанным способом измерение проводится до тех пор, когда при чекоторой величине зоны допуска не появится c гнал 1 (не годен) на втором выходе блока 10 логической обработки. В этом случае первый триггер 14 переходит в единичное состояние, на его прямом выходе устанавливается сигнал 1, а на инверсном О. В связи с этим на выходе второго элемента И-НЕ.17 в дальнейшем действует сигнал 1 независимо от значений сигналов на его первом и втором входах. Работа реверсивного счетчика 12 в режиме вычитания прекращается. С поступлением с выхода элемента 23 задержки импульса на первый вход первого элемента И-НЕ 16 на втором входе реверсивного счетчика 12 появляется сигнал О и его выходной код увеличивается на единицу. Зона допуска увеличится до предыдущего значения, при котором измеряемый ЦАП 3 имеет для всех кодовых комбинаций выходное напряжение в пределах зоны допуска. На прямом входе триггера 15 появляется сигнал 1 и I . триггер переходит в единичное состояние. После перехода второго триггера 15 в единичное состояние на третьем входе первого элемента И-НЕ 16 действует сигнал О и в дальнейшем состояние выхода этого элемента сохраняется неизменным. На втором входе реверсивного счетчика 12 постоянно действует сигнал 1, выходной код реверсивного счетчика 12 и величина зоны допуска сохраняются неизменными при продолжении измерений ЦАП З.Код с выхода реверсивного счетчика 12 фиксируется в индикаторе 11, а так как измерение проводится на низкой частоте генератора 1 импульсов, то зафиксированный код определяет с погрешностью дискретности дополнительного ЦАП 13 статическую точность из меряемого ЦАП 3. После перехода второго триггера 15 в единичное состояние на втором входе четвертого элемента И 22 действует сигнал 1. Далее измерения повторяются для предыдущего значения зоны допуска до заполнения счетчика 2. При запол нении счетчика 2 на входах измеряемого ЦАП 3, эталонного ЦАП , на пер вых и вторых входах блока 5 сравнени кодов действуют единичные коды, на выходе второго элемента И 21 действует сигнал 1 и блок 10 логической обработки формирует на первом выходе сигнал 1 (годен). Поэтому на всех трех входах третьего элемента И 20 1. С выхода трет действуют сигналы сигнал 1 воздейего э/1емента И 20 ствует на вход управлениягенератора 1 импульсов и частота импульсов гене ратора увеличивается на определенную величину. Процедура измерений повторяется вновь для всех кодовых комбинаций при постоянной зоне допуска и при увеличивающейся от одного цикла . измерения к другому частоте генератора 1 импульсов до тех пор, когда при некоторой частоте при какой-то кодовой комбинации выходное напряжение измеряемого ЦАП 3 не выйдет за пределы зоны допуска. В этом случае на втором выходе блока 10 логической обработки вновь появляется сигнал 1. Состояние выхода четвертого элемента И 22 изменяется и на другом входе управления генератора 1 импуль сов появляется сигнал 1, запрещающий прохождение импульсов с выхода генератора 1 импульсов в устройство измерения. Индикатор 11 фиксирует период сле дования импульсов генератора 1 импульсов и, следовательно, по его показаниям с учетом дискретности изменения частоты генератора 1 импульсов и величины задержки элемента задержки 23 для величины допуска, заданной дополнительным ЦАП 13, можно опреде; 1ть для измеряемого ЦАП время установления . Таким образом, введение в устройство для измерения погрешности ЦАП новых узлов триггеров, реверсивного счетчика, дополнительного ЦАП, логических элементов И, И-НЕ, НЕ, а такж соответствующих связей между ними и блоками известного устройства обеспечивает автоматическое измерение статической погрешности измеряемого ЦАП с точностью, определяемой величиной младшего разряда дополнительного ЦАП, после измерения статической погрешности осуществляет автоматический переход к циклу измерения динамического параметра ЦАП времени установления и автоматически измеряет время установления с точностью, определяемой дискретностью изменения периода следования импульсов генератора для величины допуска, автоматически установленной при измерении статической погрешности. Предлагаемое устройство значительно сокращает затраты времени оператора на проведение измерений, что позволяет широко использовать устройство как при разработке, и исследованиях новых конструкций ЦАП, так и при контроле качества готовой продукции на промышленных предприятиях, изготавливающих цифроаналоговые преобразователи. Особенно эффективно применение предлагаемого устройства при проведении серии повторяющихся испытаний, например при климатических испытаниях. Формула изобретения Устройство для измерения погр шности цифроамалогового преобразователя, содержащее генератор импульсов, измеряемый и эталонный цифроаналоговые преобразователи, счетчик, блок сравнения кодов, блок суммирования,, блок вычитания, блок логической обработки, два компаратора и индикатор, причем выходы младших и старших разрядов счетчика соединены соответственно с входами измеряемого и эталонного цифроаналоговых преобразователей, а также с первыми и вторыми входами блока сравнения кодов, выход эталонного цифроаналогд Ъого преобразователя подключен к первым, входам блоков суммирования и вычитания, выходы которых соединены с первыми входами компараторов, вторые входы компараторов подключены к выходу измеряемого цифроаналогового преобразователя, выходы компараторов соединены через блок логической обработки с первыми входами индикатора, отличающееся тем, что, с целью уменьшения времени измерения погрешности цифроаналогового преобразователя, в него введены элемент задержки, два триггера, реверсивный счетчик, дополнительный цифроаналоговый преобразователь, четыре элемента И, два элемента И-НЕ, элемент НЕ, причем выход генератора импульсов подключен к второму входу индикатора и к первому входу первого элемента И и через элемент задержки к входу синхронизации счетчика и первому входу первого элемента И-НЕ, второй вход 15

первого элемента И соединен с выходом блока сравнения кодов и первым входом второго элемента И, выход первого элемента И подключен к третьим входам компараторов и блока логической обработки, первый выход которого соединен с первыми входами второго элемента И-НЕ и третьего элемента И, второй выход блока логической обработки подключен к прямому входу первого триггера и первому входу четвертого элемента И, старшие разряды счетчика соединены с вторыми входами второго элемента И, выход которого подключен к вторым входам третьего элемента И и второго элемента И-НЕ, третий вход которого соединен с инверсным выходом

первого триггера, выход второго элемента И-НЕ подключен к первому входу реверсивного счетчика, прямой выход первого триггера соединен с третьим входом третьего элемента И, третьим входом индикатора и вторым входом . первого элемента И-НЕ, выход которого подключен ко второму входу реверсивного счетчика и через элемент НЕ к прямому входу второго триггера, инверсный выход которого соединен с третьим входом первого элемента И-НЕ, прямой выход второго триггера подключен к второму входу четвертого элепервым входом генератора, второй вход которого подключен к выходу третьего элемента И, выходы реверсивного счетчика соединены с входами дополнительного цифроаналогового преобразователя и четвертыми входами индикато-ра, выход дополнительного цифроаналоrf-oBoro преобразователя подключен к вторым входам блоков суммирования и вычитания.

Источники информации, принятые во внимание при экспертизе

Авторы

Даты

1982-01-30—Публикация

1980-06-24—Подача