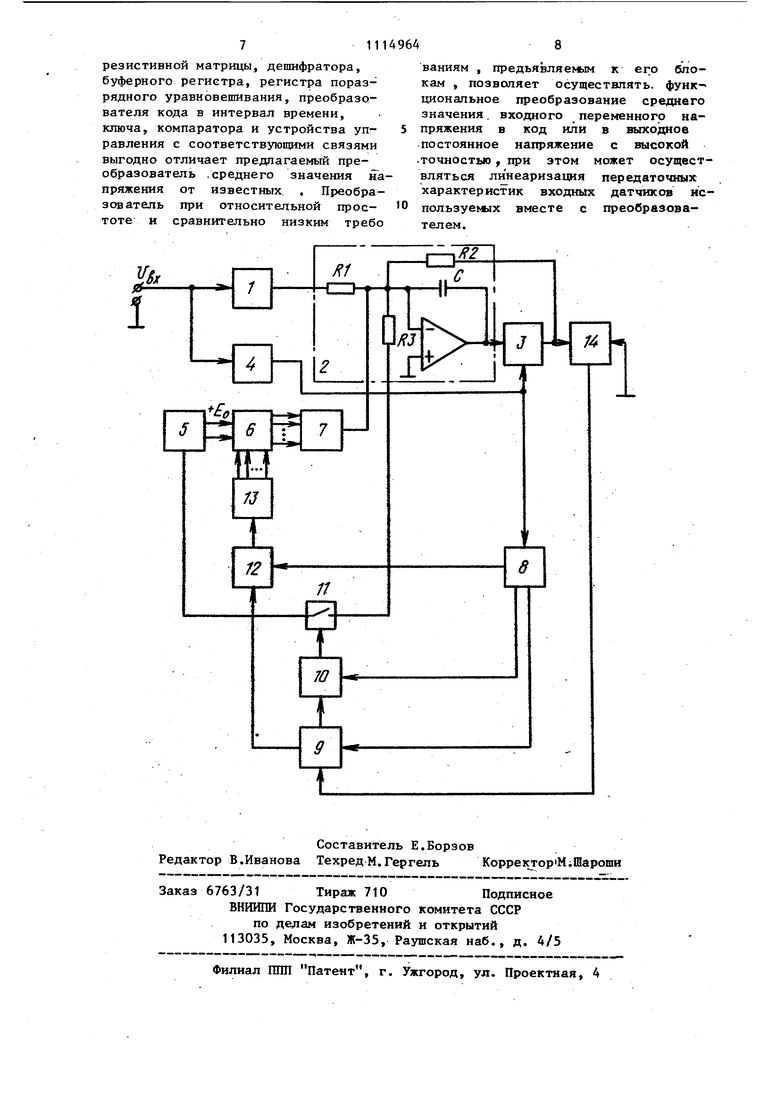

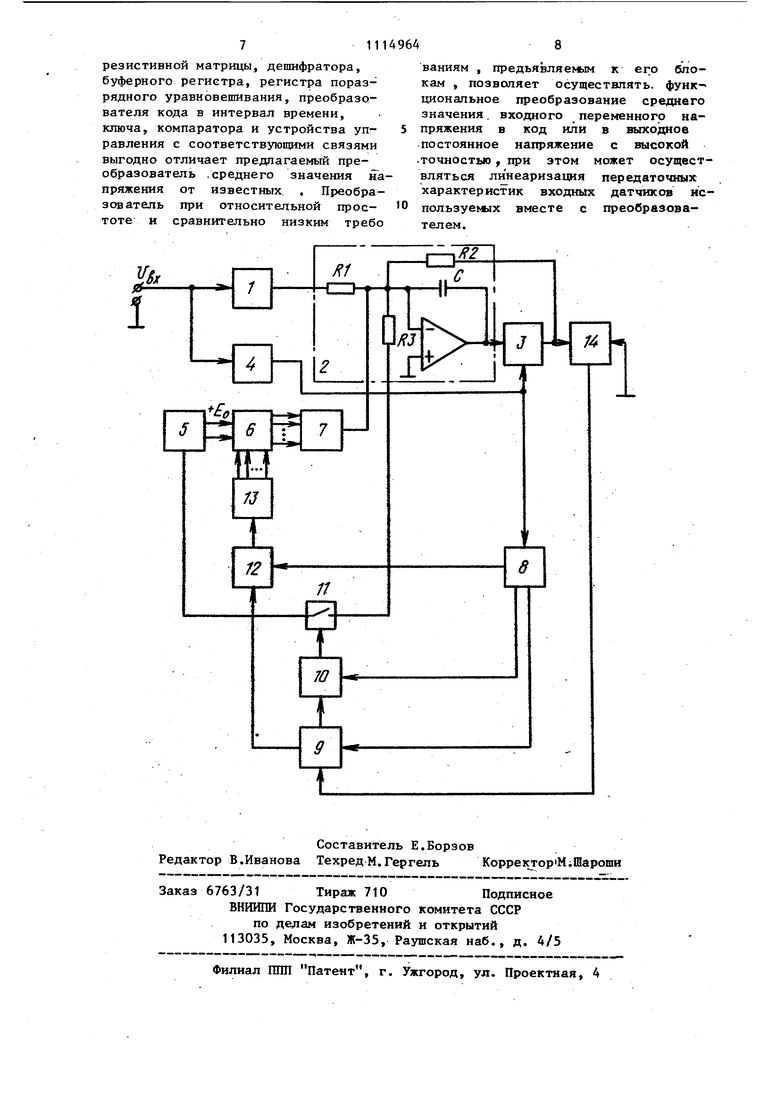

Изобретение.относится к измери тельной технике и может быть использовано в измерительных и управляющих системах для преобразования переменного сигнала в постоянное напряжение или цифровой-код. Известны преобразователи перемен ного сигналу в цифровой код, содержащие формирователь противофазного входного сигнала, два сумматора, два элемента сравнения, генератор пилообразного напряжения, триггер, управляющее устройство, элемент совпадений, генератор теплойых импульсов, ключ и цифровой счетчик ij К недостаткам подобных устройств относятся невозможность получения выходного сигнала в аналоговой форме, а также низкая точность, вызван ная различным дрейфом пороговых уро ней элементов сравнения. Наиболее близким к изобретению по технической сущности является преобразователь среднего значения напряжения, содержащий включенные последовательно линейный детектор, интегратор и элемент выборки-хранения, выход которого подключен к второму входу интегратора, а также формирователь, включенный между вхо дом линейного детектора и управляющим входом элемента выборки-хранения 2 , Недостатком известного преобразо вателя является низкая точность пре образования, вызванная нелинейность функции преобразования при работе с цифровьми регистрирующими устройствами . Целью изобретения является повышение точности преобразования при работе с цифровыми регистрирующими устройствами путем введения корректирующего кусочно-ступенчатого напр жения. Поставленная цель достигается те что в преобразователь среднего знач ния напряжения, содержащий включенные последовательно линейный детект интегратор и элемент выборки-хранения, выход которого подключен к вто рому входу интегратора, а также фор мирователь, включенный между входом линейного детектора и управляющим входом элемента выборки-хранения, дополнительно введены соединенные последовательно буферный регистр, дешифратор, коммутатор и резисторная матрица, выход которой подключен к третьему входу интегратора, соединенные последовательно регистр поразрядного уравновешивания и преобразователь кода во временой интервал, выход которого подключен к управляющему входу ключа, источник эталонных напряжений, компаратор и блок управления, вход котор.ого подключен к выходу формирователя, а выходы соответственно - к управляющим входам регистра поразрядного уравновепивания, преобразователя кода во временной интервал и буферного регистра, причем первый выход источника эталонных напряжений соединен через ключ с четвертым входом интегратора, а два вторых его выхода - с вторыми входами коммутатора, вторые выходы регистра поразрядного уравновешивания соединены с входами буферного регистра, а вход регистра поразрядного уравно вещивания соединен с выходом компаратора, входы которого соединены соответственно с выходом элемента выборки-хранение и общей шиной. На чертеже представлена блоксхема преобразователя среднего значения напряжения. Преобразователь содержит соединенные последовательно линейный, детектор 1, интегратор 2 и элемент 3 выборки-хранения, выход которого соединен с вторым входом интеграToipa 2, формирователь 4, включенный между входом линейного детектора 1, соединенным с входной шиной устройства и зтравляющим входом элемента 3 выборки-хранения, источник 5 эталонных напряжений, первые два входа которого соединены с первьвчи входами коммутатора 6, выходы которого через резисторную матрицу 7 соединены с третьим входом интегратора 2, блок 8 управления, вход которого соединен с выходом формирователя 4, а два первьк выхода соединены соответственно с управляющими входами соединенных последовательно регистра 9 поразрядного уравновешивания и преобразователя 10 кода во временной интервал, выход которого подключен к управляющему входу ключа 11, включенного между третьим выходом источника 5 и четвертым входом интегратора 2, соединенные последовательно буферный регистр 12 и дешифратор 13, выходыкоторого соединены с вторыми входами коммутатора 6, входом буферного регистра 12, входы которого соединены с выходами регистра 9 поразряд кого уравновешивания, вход которого соединен с выходом компаратора 14, входы которого соединены соответственно с выходом элемента 3 и общей шиной. Блок 8 управления может быть вьшолнен следующим образом. Между ег входом и вторым выходом включен умножитель 15 частоты, .между его .входом и первым выходом включен делитель 16 частоты, между выходом делителя 16 частоты и третьим выходом - соединенные последовательно делитель 17 частоты и элемент 18 задержки. Коэффициент умножения в умножителе 15 определяется требуемой точностью преобразователя и при погрешности 0,1% равен 1000, в качестве этого умножителя можно использовать генератор синхронизируемый импульсами формирователя 4. Коэффициент деления блока 16-6 равен количеству циклов сходимости преобра зователя. Коэффициент деления блока 17 зависит от точности преобразователя и разрядности регистра 9 поразрядного уравновепшвания. При погрешности 0,1% он равен 10. Преобразователь среднего значения напряжения работает в два этапа каждый из которых состоит из нескольких циклов,, за время Kotopbix преобразование заканчивается. В каждом цикле первого этапа осуществляется одновременное интегрирование интегратором 2 в течение периода Т входного переменного напряжения выходных напряжеНИИ линейного детектора 1 и элемента 3 выборки-хранения, и в течение времени Т; компенсации напряжения источника 5 эталонных напряжений. Кроме того, в каждом цикле по сигналу формирователя 4, синхронизированному с входным переменным сигналом, например с переходом его через ноль, осуществляется выборка выходного напряжения интегратора 2 и запоминание этого значения в течение периода Т. Предположим, «iTo перед началом преобразования напряжение на выходе элемента 3 выборки хранения равно Цц. На вход интегратора 2 поступает выпрямленное линейньвм детектором 1, представляющим собой двухпалупериодный выпрямитель, напряжение. После окончания первого цикла работы преобразователя напряжение j на выходе элемента 3 выборки-хранения определяется выражением ..a,Ut-|,,-.,, ЙК.ф-р1гЧ 14-Ш где К - коэффициент передачи элемента 3 выборки-хранения; R - времязадающее .сопротивление ийтегратора 2 по первому входу; 2 времязадающее сопротивление интегратора 2 по второму входу; времязадающее сопротивление интегратора 2 по четвертому входу; С - емкость конденсатора интегратора 2; Е - напряжение источника 5 эталонного напряжения. Аналогично, после окончания п-го цикла преобразования первого этапа напряжение на выходе элемента 3 выборки-хранения определяется выражением«.К.и,ьУ..„|,. и fbJliiLl Ч RiC 1 (2) Выражение (2) состоит из двух частей: геометрической прогрессии, сходящейся при условии J1 N 1, и убывающего при этом же условии члена. В установившемся режиме ( И- t ) если выполняется неравенство КпТ напряжение на выходе элемента 3 выборки-хранения определяется вьфажениемV,.co |f, JKH),T,, о(4) с помощью регистра 9 осуществляется поразрядное уравновешивание напряжения на выходе элемента 3 выборкихранения. Сначала записывается 1 в старший разряд регистра 9 с помощью блока 8 управления. С помощью J преобразователя 10 этот код преобраз1 ется в интервал времени и управляет ключом 11, подключая к четвертому входу интегратора 2 напряжение Ер. Если произошла перексмпен сация (изменился знак напряжения на вькоде элемента выборки-хранения и соответственно на вькоде компаратора 14), то 1 записывается в следующий разряд регистра 9, а 1 в старшем разряде регистра 9 стирается. Затем снова определяется знак напряжения на выходе компаратора 14, Этот процесс продолжается до тех пор, пока напряжение на выходе элемента 3 выборки.-хранения не станет равным нулю (или точнее, пока оно не попадет в область нечувствительности компаратора 14). Из выражения (4) имеем Т 4 i eA«ut, т где Uj, YJ lUg(t)dt - среднее знач 0 ние входного напряжения Ugj(t). Соответствующий интервалу времени компенсации Ту код U с выхода регистра 9 поразрядного уравновешивания по сигналу блока 8 управления (сигнал конца первого этапа преобра зования) переписывается в буферный регистр 12, где хранится в течение всего второго этапа преобразования. 1 Каждый цикл второго этапа преобразования отличается от первого тем что по коду, записанному в буферном регистре 12с помощью дешифратора 13 и коммутатора 6, к входу интегра тора 2 подключается напряжение Е (положительной или отрицательной полярности) через один из резисторо RI, резисторной матрицы 7 и интегрируется в течение всего времени цикла Т. I В результате преобразования на втором этапе код в регистре 10 поразрядного уравновешивания будет пропорционален интервалу времени Тд N - Tjjg- период квантирующего импул са. Как следует из уравнения преобAразования выходной код NX имеет две составляющие Первая из них - g-j-- определяется средним значением входного переменного напряжения, а вторая формируется вновь введенными в преобразователь среднего значения напряжения блоками. Составляющая ip -F-F-- Л boVj-6 определяется средним значением входного переменного напряжения (определяемого на первом этапе и которому соответствует подключение резистора R; и источника Е|). Весь диапазон изменения среднего значения входного переменного напряжения разбивается на поддиапазон, в каждом из которых посредством буферного регистра 12, дешифратора 13 и коммутатора 6 между. входом интегратора 2 и выходами источника эталонного напряжения включается соответствуюс ий этому поддиапазону резистор R резистивной матрицы 7. В результате в каждом поддиапазоне к основной составляющей выходного кода-g , прибавляется (или вычитается -° в зависимости от полярности EJ) добавка. Совокупность всех добавок во всем диапазоне изменения Ujp представляет собой кусочно-ступенчатую функцию, которой можно аппроксимировать различные линейные зависимости. Благодаря этому в результирующую зависимость выходного кода от среднего значения входного переменного напряжения может быть введена требуемая нелинейность для линеаризации характеристики преобразователя или для осуществления функционального преобразования в код. Преобразователь среднего значения напряжения также можно использовать как функциональный калибратор среднего значения напряжения, если на втором этапе преобразования отключить ключ 1 Г от входного интегратора 2 и в качестве вькодной величины использовать напряжение на выходе элемента 3 выборки-храненияRI R Это напряжение можно Использовать для управления различного рода регуляторами, используемыми в системах автоматического управления. Введение в устройство источника эталонного напряжения, коммутатора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Функциональный преобразователь | 1982 |

|

SU1016799A1 |

| Функциональный преобразователь | 1983 |

|

SU1109765A1 |

| Функциональный преобразователь | 1979 |

|

SU894856A1 |

| Функциональный преобразователь | 1983 |

|

SU1107138A1 |

| Способ контроля положения объекта относительно опорного луча и устройство для его осуществления | 1987 |

|

SU1674368A1 |

| Измерительный преобразователь | 1986 |

|

SU1374149A1 |

| Преобразователь угла поворота вала в код | 1985 |

|

SU1347186A1 |

| Функциональный преобразователь | 1989 |

|

SU1674173A1 |

| Многоканальный преобразователь угла поворота вала в код | 1980 |

|

SU947895A1 |

| Устройство для ввода информации | 1983 |

|

SU1145336A1 |

ПРЕОБРАЗОВАТЕЛЬ СРЕДНЕГО ЗНАЧЕНИЯ НАПРЯЖЕНИЯ, содержащий включенные последовательно линейный детектор, интегратор и элемент выборки-хранения, выход которого подключен к второму входу интегратора, a также формирователь, включенный между входом линейного детектора и управляющим входом элемента выборки хранения, отличающийся тем, что, с целью повышения точности преобразования, в него дополнительно введены соединенные последовательно буферньй регистр, дещифратор, коммутатор и резисторная матрица, выход которой подключен к третьему входу интегратора, соединенные последовательно регистр поразрядного уравновешивания и преобразователь кода во временный интервал, выход которого подключен к управляющему входу ключа, источник эталонных напряжений, компаратор и блок управления, вход которого подключен к выходу формирователя, a выходы соответственно к управляюпщм входам регистра поразрядного уравновешивания, преобразователя кода во временный интер(Л вал и буферного регистра, причем первый выход источника эталонных напряжений соединен через ключ с четвертым входом интегратора, a два вторых его выхода - с вторыми входами коммутатора, вторые выходы регистра поразрядного уравновешивания соединены с входами буферного регистра, a вход регистра пораз4 рядного уравновешивания соединен СО с выходом KcwnapaTopa, входы кото0д рого соединены соответственно с выktiib ходом элемента выборки-хранения и общей шиной.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Мартяшин А.И | |||

| и др | |||

| Преобразователи электрических параметров для систем контроля и измерения | |||

| М.,Энергия 976, с.159,рис.3 - 23.2 | |||

| Волгин Л.И | |||

| Измерительные преобразователи переменного напряжения в постоянное | |||

| М., Советское радио, 1977, с | |||

| Огнетушитель | 0 |

|

SU91A1 |

Авторы

Даты

1984-09-23—Публикация

1982-02-05—Подача