Изобретение относится к автоматике и вычислительной технике и может быть использовано в вычислительных комплексах для решения задач управления.

Известны аналогичные преобразователи угла поворота вала в код, содержащие синусно-косинусные датчики,подключенные через входной коммутатор и развязывающие усилители с коммутато,ром октантов, регистр октантов, распределительный блок с регистром управления, блок сравнения, преобразователь код-капряжение, блок признака отсчета и блок автоматической синхронизации .l.

Наиболее близким к предлагаемому является многоканальный преобразователь угла поворота вала в код, содержащий синусно-косинусные датчики, соединенные q входным коммутатором, коммутатор квадрантов, вход которого соединен с первым выходом распределительного блока, второй выход которого соединен с первым входом декодирующего преобразователя, выход которого соединен с одним из входов бло- ка сравнения, выход блока сравнения соединен с вторым входом декодирующего преобразователя, причем входной коммутатор соединен с коммутатором

квадрантов, первый выход которого соединен с входом распределительного блока и второй и третий выходы через соответствующие развязывающие усили5тели соединены с третьим входом декодирующего преобразователя, другой вход блока сравнения соединен с нулевой шиной.

Однако Нсшичие развязывающих уси10лителей на входе и согласующих масштабных усилителей на выходе коммутатора квадрантов, где производится определение фаз напряжений обмоток СКТ-датчика и коммутация зтих на15пряжений на входе масштабных усилителей , приводит к появлению дополнительных погрешностей и снижение точности преобразования.

Цель изобретения - повышение точ20ности преобразователя.

Поставленная цель достигается тем, что в многоканальный преобразователь угла поворота вала в код, содержащий синусно-косинусные датчики угла, соединенные с входным

коммутатором, распределительный блок, первый выход которого соединен с управляющим входом входного коммутатора, второй выход соединен с первым

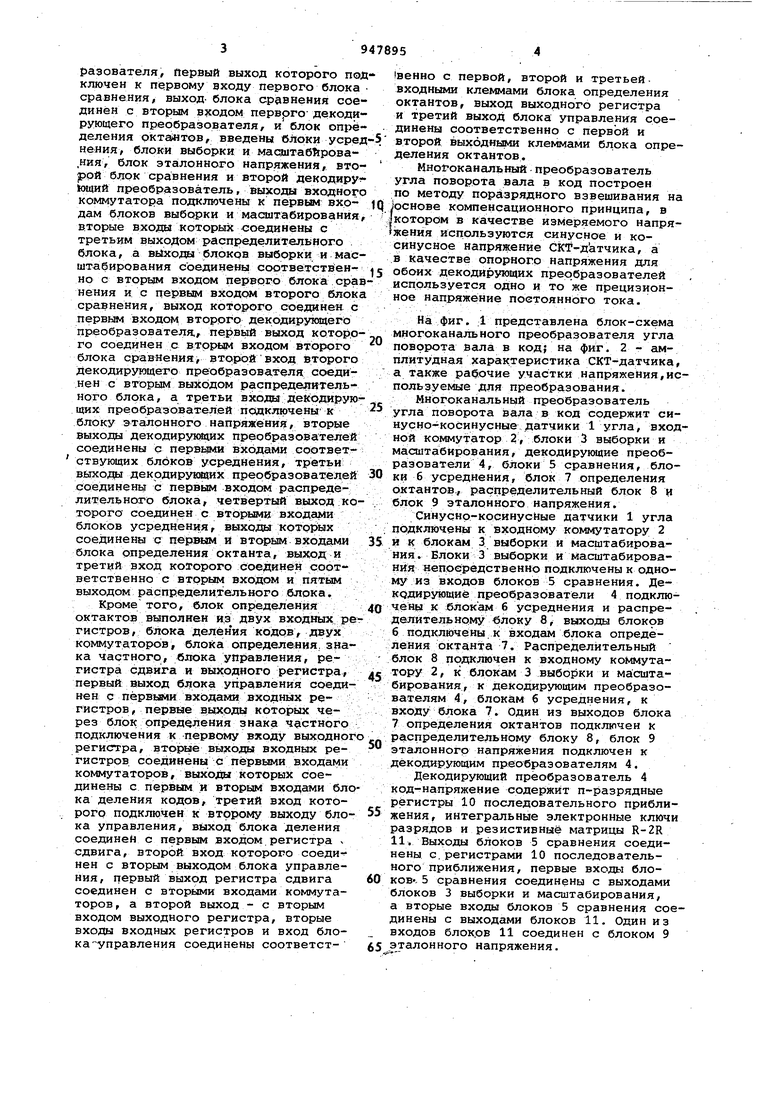

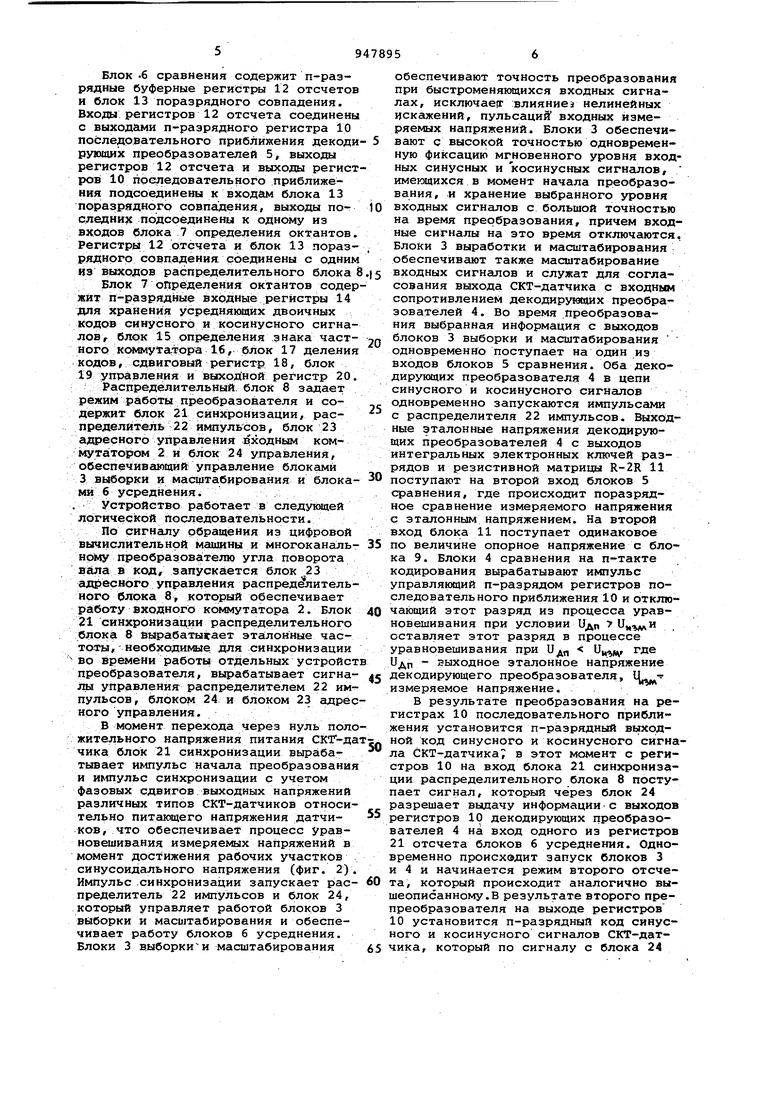

30 входом первого декодирующего-преобразователя. Первый выход которого по ключей к первому входу первого блока сравнения, выход- блока сравнения сое динён с вторым входом перврго- декоди рующего преобразователя, и блок опре деления OKTaiHTOB, введены блоки усре нения, блоки выборки и масаитаб11рова,ния, блок эталонного напряжения, вто рой блок сравнения и второй декодиру Киций преобразователь, выходы входног коммутатора подключены к первым входам блоков выборки и масяитабирования вторые входы которых соединены с третьим выходом распределительного . блока, а выходы блоков выбрркц и мас штабирования соединены соответственно с вторым входом перврго блока сра нения и с первым входом второго сравнения, выход которого соединен с первьвл входом второго декодирующего преобразователя,, первый выход которо го соединен с втррь1М входом второго блока сравнения, второй вход второго Декодирующего прообразова,теля соединен с вторым выходом распределительного блока, а третьи входы декодирую щих преобразователей подключены; к блоку эталонного напряжения g,j,ppyg выходы декодирукадих преобразователей соединены с первыми вх6да 1И соответствующих блоков усреднения, третьи: выходы декодирукивих преобразователей соединены с первым входом распределительного блока, четвертый выход/ко торого соединен с вторыми входами блоков усредчения, выхода которых соединены с первым и вторым вхоДё1МИ блока определения октанта, выход и третий вход которого соединен соответственно с вторым входом и пятым выходом распределительного блока. Кроме того, блок определения октактов выполнен из двух входных pa гистров, блока делёния кодов, двух коммутаторов, блока определения, знака частного, блока управления, регистра сдвига и выходного регистра, первый В1ЫХОД блока управления соединен с пёрв1 «и входами входных регистров, первые выходы которых через блок определения знака частного подключения к -первому входу вьаходног регистра, вторые выходы входных регистров, соединены с первыми нxoдa 4и коммутаторов, выходы которых соединены с первым и вторым входами бло ка деления кодов, третий вход которого подключен к второму выходу блока управления, выход блока деления соединен с первым входом.регистра v сдвига, второй вход которого соединен с вторым выходом блока управления, первый выход регистра сдвига соединен с вторыми входами коммутаторов , а второй выход - с вторым входом выходного регистра, вторые входы входных регистров и вход блока управления соединены соответст1венно с первой, второй и третьей входными клеммами блока определения октантов, выход выходного регистра и третий выход блока управления соединены соответственно с первой и второй быходньлш клеммами блока определения октантов. Многоканальный преобразователь угла поворота вала в код построен по методу поразрядного взвешивания на снове компенсационного принципа, в отором в ка честве измеряемого напряжения используются синусное и косинусное напряжение СКГ-д атчика, а в качестве опорного напряжения для обоих декодирующих преобразователей используется од;но и то же прецизионное напряженнее постоянного тока. На фиг. .1 представлена блок-схема многоканального преобразователя угла поворота вала в код; на фиг. 2 - амплитудная характеристика СКТ-датчика, а также рабочие участки напряжения,используемые для преобразования. многоканальный преобразователь угла поворота вала в код содержит синусно-косинусные датчики 1 угла, входной коммутатор 2, блоки 3 выборки и масштабирования, декодирующие преобразователи 4, блоки 5 сравнения, блоки б усреднения, блок 7 определения октантов., распределительный блок 8 и блок 9 эталонного напряжения. СинУСНо-косинусНые датчики 1 угла подключены к входному коммутатору 2 и к блокам 3 выборки и масштабирования. Блоки 3 выборки и масштабирования непосредственно подключены к одному из входов блоков 5 сравнения. Декодирующие преобразователи 4 подключены к .блокам 6 усреднения и распределительному влоку 8, выходы блоков 6подключены к входам блока определения октанта 7. Распределительный блок 8 подключен к входному коммутатору 2, к блокам 3 выборки и масштабирования, к декодирующим преобразователям 4, блокам 6 усреднения, к входу блока 7. Один из выходов блока 7определения октантов подключен к распределительному блоку 8, блок 9 эталонного напряжения подключен к декодирующим преобразователям 4. Декодирующий преобразователь 4 код-напряжение содержит п-разрядные регистры 10 последовательного приближения, интегральные электронные ключи разрядов и резистивныё матрицы R-2R 11, Выходы блоков 5 сравнения соединены с. регистрами 10 последовательного приближения, первые входы блоков-, 5 сравнения соединены с выходами блоков 3 выборки и масштабирования, а вторые входы блоков 5 сравнения соединены с выходами блоков 11. Один из входов блоков 11 соединен с блоком 9 эталонного напряжения.

Блок -б сравнения содержит п-раэрядные буферные регистры 12 отсчетов и блок 13 поразрядного совпадения. Входы, регистров 12 отсчета соединены с выходами п-раэрядного регистра 10 последовательного приближения декоди руюших преобразователей 5, выходы регистров 12 отсчета н выходы регистров 10 последовательного приближения подсоединены к входам блока 13 поразрядного совпадения выходы последних подсоединены к одному из входов блока 7 определения октантов. Регистры 12 отсчета и блок 13 поразрядного совпадения соединены с одним из выходов распределительного блока 8

Блок 7 определения октантов содержит п-разрядные входные регистры 14 для хранения усредня мдих двоичных кодов синусного и косинусного сигналов / блок 15 определения .знака частного KC iMyta,Topa 16, блок 17 деления кодов, сдвиговый регистр 18, блок 19 управления и выходной регистр 20.

Распределительный, блок 8 задает режим работы преобразователя и со держит блок 21 синхронизации, распределйтель 22 импульсов, блок 23 адресного управления входным коммутатором 2 и блок 24 управления, обеспечивающий управление блоками 3 выборки и масштабирования и блоками 6 усреднения.

. Ус Тр1Ойство работает в следукнцей логической последовательности.

По сигналу обращения из цифровой вычислительной машины и многоканальНОМУ преобразователю угла поворота вгша в код, запускается блок .23 адресного управления распред лительного блока 8, который обеспечивает работу входного ко виутатора 2. Блок 21 синхронизации распределительного блока 8 вырабатывает эталонные частоты, Необходимые для синхронизации во времени работы отдельных устройст преобразователя, вырабатывает сигнаjffii управления распределителем 22 импульсов, 6ЛОКО1М 24 и блоком 23 адресного управления.

В момент перехода через нуль положительного напряжения питания СКТ-дачика блок 21 синхронизации вырабатывает импульс начала преобразования и импульс синхронизации с учетом фазовых сдвигов.выходных напряжений различных типов СКТ-датчиков относительно питакяцего напряжения датчиков, что обеспечивает процесс уравновешивания измеряемых напряжений в момент достижения рабочих участков синусоидального напряжения (фиг. 2). Импульс .синхронизации запускает распределйтель 22 импульсов и блок 24, который управляет работой блоков 3 выборки и масштабирования и обеспечивает работу блоков 6 усреднения. Блоки 3 выборки и масштабирования

обеспечивают точность преобразования при быстроменяющихся входных сигналах, исключае{г влиянием нелинейных искажений, пульсаций входных измеряемых напряжений. Блоки 3 обеспечивают с высокой точностью одновременную фиксацию мгновенного уровня входных синусных и косинусных СИГНёШОВ,

имеквдихся в момент начала преобразования, и хранение выбранного уровня входных сигналов с большой точностью на время преобразования, причем входные сигналы на это время отключаются Блоки 3 выработки и масштабирования обеспечивают также масштабирование входных сигналов и служат для согласования выхода СКТ-датчика с входным сопротивлением декодируюцих преобразователей 4. Во время преобразования выбранная информация с выходов блоков 3 выборки и масштабирования одновременно поступает на рдин из входов блоков 5 сравнения. Оба декодирующих преобразователя 4 в цепи синусного и косинусного сигналов одновременно запускаются импульсами с распределителя 22 импульсов. Выходные эталонные напряжения декодирующих преобразо вателей 4 с выходов интегральных электронных ключей разрядов и резистивной матрицы R-2R 11 поступают на второй вход блоков 5 сравнения, где происходит поразрядное сравнение измеряемого напряжения с эталонным напряжением. На второй вход блока 11 поступает одинаковое по величине опорное напряжение с блока 9. Блоки 4 сравнения на п-такте кодирования вырабатывают импульс управлянвдий п-разрядс 1 регистров последовательного приближения 10 и отключающий этот разряд из процесса уравновешивания при условии Цдп иц. оставляет этот разряд в процессе уравновешивания при Цд иц, где дп эыходное эталонное напряжение декодирующего преобразователя, Цл измеряемое напряжение.

В результате преобразования на регистрах 10 последовательного приближения установится п-разрядный выходной код синусного и косинусного сигнала СКТ-датчика7 в этот момент с регистров 10 на вход блока 21 синхронизации распределительного блока 8 поступает сигнал, который через блок 24 разрешает выдачу информации с выходов регистров 10 декодирующих преобразователей 4 на вход одного из регистров 21 отсчета блоков 6 усреднения. Одновременно происходит запуск блоков 3 и 4 и начинается режим второго отсчета, который происходит аналогично вышеописанному. В результате второго препреобразователя на выходе регистров 10 установится п-разрядный код синусного и косинусного сигналов СКТ-датчика, который по сигналу с блока 24

распределительного блока перепишется во второй регистр 12 блдка 6, после чего начинается работа преобразователя в третьем режиме отсчета. -После окончания третьего преобразователя блок 24 распределительного блока 8 вырабатывает сигнал, разрешаюсдай одновременное поразрядное поступление п-разрядных выходных кодов синусного и косинусного сигналов с выходов регистров 12 отсчетб и регистра 10 последовательного приближения на входы блока 13 поразрядного совпадения блока б усреднения, в результате производится усреднение двух наиболее близких по величине кодов отсчета и на выходах блока,13 формируется усредненный п-разрядный выходной код и sin ci и и- cos «яб СКТ-датчиков.

Многоотсчетный режим работы предлагаемого преобразователя исключает случайные погрешности преобразования, тем самым повырлается точность и достоверность преобразования. Многоотсчетный режим работы обеспечивается высоким быстродействием работы блоков 3, 5 и 8 СФиг. 2). После окончания процесса сравнения и усреднения результатов преобразований .(отсчетов) блок 21 синхронизации распределительного блока 8 запускает блок 19 управления блока 7 деления кодов. Блок 19 обеспечивает управление работой всех устройств ,блока 7.

Перед началом преобразования деление кодов) выходные коды U sino и Ucos о с выходов блока 13 поступают на входные регистры 14, где они преобразуются в коды положительных чисел и запоминаются на время работы блока 7. Истинные значения знаковых разрядов Usin об и Ucosoi поступают на входы блока 15 определения знака частного, которое определяет значени квадранта угла поворота вала (знак /и sin и знак / -sinef+ U-cos at/), после чего входы входных регистров 14 блокируются, запрещая поступление информации с выходов блоков 13. Таки образом, операция деления кодов проиводится со значимой частью выходного кода синусного и косинусного сигнала т.е. с абсолютными значениями.

Первым тактом работы блока 7 определения октантов производится сравнение по абсолютной величине кодов Usin oL и U-COS.C6, т.е. происходит определение октанта угла поворота вала (участок в . Причем сигнал сравнения кодов по абсолютной величине далее используется для передачи на входы блока 17 делимого (меньшего по .абсолютной величине числа) в прямом коде и делителя Iбольшего по абсолютной величине числа) в инверсном коде. Сигнал сравнения колов управляет KONwyxaторами 16 таким образом, что вход регистра 14 делимого отключается от первого входа блока 17 после окончания в.торого такта работы блока 7 - суммирования на блоке 17 делимого (в прямом коде) с делителем (в инверсном коде) и записи результата суммирования в сдвиговый регистр 18. Вместо делимого на первый вход блока 17 поступает код с выхода сдвигового регистра 18.

Затем производится запись инверсного значения старшего разряда регистра 18 в выходной регистр 20 и осуществляется сдвиг кода разряда влево в регистре 18. В зависимости от знака старшего разряда регистра 18 (до сдвига) код с регистра 14 делителя поступает на второй вход блока 17 через коммутатор 16 в прямом коде (если 1 в старшем разряде регистра 18) или в инверсном коде (если О в старшем разряде регистра 18).

Далее операции суммирования в блоке 17 деления кодов, регистра 18 и регистра 14 делителя, записи результата суммирования в сдвиговый регистр 18, записи старшего разряда регистра 18 в выходной регистр 20, сдвиг кода влево в регистре 18 повторяется до тех пор, пока процесс деления кодов U-sin об и U-cos/aC. друг на друга не закончится. В результате на выходе регистра 20 формируется выходной линейный , код отношения двух напряжений U-sinoi и U -coscL с учетом знака (коррекцию знака частного осуществляют блок 15). Угол поворота вала равен е arctg N (знак частного - положителен) ai. 90 arctg N (знак частного отрицателен), где N - код выходного регистра 20.

Данное построение преобразователя позволяет исключить ряд аналоговых (линейных) интегральных схем (масштабные усилители, аналоговые ключи коммутатора квадрантов и т.п.), аппаратурно упростить схему данного преобразователя (в том смысле, что предлагаемый подход позволяет для реализации преобразователя применить интегральные цифро-аналоговые и аналого-цифровые преобразователи, а это в свою очередь, существенно уменьшит габариты и увеличит надежность устройства) и тем самым повысить точность его работы, поскольку основные операции по определению кода угла поворота, (определение квадранта, октантов и выходного кода отношений двух напряжений) производится цифровьЛми методами. В предлагаемом многоканальном преобразователе по сравнению с известным; применение блоков выборки и масштабирования, блоков усреднения, а также блока определения октантов позволяет повысить точ 1ость преобразования за счет.исключения ряда аналоговых элементов схемы (источники дополнительных- погрешностей преобразования) , за счет увеличения числа разря дов п-разрядного преобразования при процессе поразрядного взвешивания угла поворота вала в пределах октанта (-IS), в известном преобразователе три первых разряда п-разрядного кода определяют октант, п-3 разряда идут на определение угла в пределах октанта, В предлагаемом преобразователе два первых разряда (знак и опре деление делимого и делителя) идут на определение октанта, а п-2 разряда идут на определение угла поворота в пределах октанта. Точность преобра зования повышается и за счет исключе ния случайных погрешностей преобразо вания путем применения блока усредне ния, а также за счет освобождения центрального вычислителя от ряда дополнительных и вспомогательных опе раций, В известном преобразователе угол поворота вала в пределах сктанта определяют как о6 arctg Kf-f- или 0 90 - arctgKK-K, где К - код -преобразователя поразрядного взвешивания, т,е, передавая код К в центральный вычислитель комплекса, после ний вычисляет сначала величину 1-К, затем величины Kj-f-K и только после этого переходит к вычислению кода угла, что приводит не только к увели чению затрат времени центрального вычислителя, но и к появлению дополнительной погрешности. В известном устройстве также отсутствуют элемент многоотсчетности и усреднения резуль татов преобразования (отсчетов),что в свою очередь приводит к дополнительным случайным погрешностя преоб разования. Формула изобретения Многоканальный.преобразователь угла поворота вала в код, содержащий синусно-косинусныё датчики угла, сое диненные с входным коммутатором, рас пределительный блок, первый выход , которого соединен с управляющим входом входного коммутатора, второй выход соединен с первым входом первого декодирующего преобразователя, первый выход которого подключен к первому входу первого блока сравнения, выход блока сравнения соединен с вто рым входом первого декодирующего пре образователя, и блок определения октантов, отличающийся тем что, с целью повышения .точности прео разователя, в него введены блоки усреднения, блоки выборки и масштаби рования, блок эталонного напряжения, второй блок сравнения и второй декод рующий преобразователь, выходы входного коммутатора подключены к первым входам блоков выборки и масштабирования, вторые входы которых соед нены с третьим выходом распределительного блока, а выходы блоков выборки и масштабирования соединены соответственно с вторым входом первого блока сравнения, и с первым входом второго блока сравнения, выход которого соединен с первым входом второго декодирующего преобразователя, первый выход которого соединен с вторым входомвторого блока сравнения, второй вход второго декодирующего преобразователя соединен с вторым выходом распределительного блока, а третьи входы декодирующих преобразователей подключены к блоку эталонного напряжения, вторые выходы декодирующих преобразователей соединены с первыми входами соответствующих блоков усреднения, третьи выходы декодирующих преобразователей соединены с первым входом распределительного блока, четвертый выход которого соединен с вторыми входами блоков усреднения,вь1ходы которых соединены с первым и вторым входами блока определения октантов, выход и третий вход которого соединены соответственно с вторым входом и пятым выходом распределительного блока, 2. Преобразователь ijo п,1, о т л ичающийся тем, что блок определения октантов выполнен из двух входных регистров, блока деления кодов, двух коммутаторов, блока определения знака частного, блока управления, регистра сдвига и выходного регистра, первый выход блока управления соединен с первыми входами входных регистров, первые выходы которых через блок определения знака частного подключены к первому входу выходного регистра, вторые выходы входных регистров соединены с первыми входами коммутаторов, выходы которых соединены с первым и вторым входами блока деления кодов, третий вход которого подключен к второму выходу блока управления, выход блока деления соединен с первым входом регистра сдвига, второй вход которого соединен с вторым выходом блока управления, первый выход регистра сдвига соединен с вторыми входами коммутаторов,а второй выход - с вторым входом выходного регистра, вторые входы выходных регистров и вход блока управления соединены соответственно с первой, второй и третьей входными клеммами блока определения октантов, выход выходного регистра и третий выход блока управления соединены соответственно с первой и второй выходными клеммами блока определения октантов,. Источники информации, принятые во внимание при экспертизе 1,Авторское свидетельство СССР № 328493, кл, G 08 С 9/04, 1970, 2,Авторское свидетельство СССР №742956,кл, G 08 С9/04,1977 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальный преобразователь угла поворота вала в код | 1977 |

|

SU732956A1 |

| Многоканальный преобразователь угла поворота вала в код | 1983 |

|

SU1144190A1 |

| Многоканальный преобразователь угла поворота вала в код | 1979 |

|

SU873260A2 |

| МНОГОКАНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ УГОЛ - КОД | 1972 |

|

SU355640A1 |

| Преобразователь угла поворота вала в код | 1985 |

|

SU1261118A2 |

| Преобразователь угла поворота вала в код | 1984 |

|

SU1231610A1 |

| Многоканальный преобразователь угла поворота вала в код | 1987 |

|

SU1462478A2 |

| ВСЕСОЮЗНАЯ 1 | 1972 |

|

SU328497A1 |

| Многоканальный преобразователь угла поворота вала в код | 1975 |

|

SU523434A1 |

| БЫСТРОДЕЙСТВУЮЩИЙ МНОГОФУНКЦИОНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ УГЛА В КОД ДЛЯ УСТРОЙСТВ ЭЛЕКТРОМЕХАНОТРОНИКИ | 1994 |

|

RU2094945C1 |

Авторы

Даты

1982-07-30—Публикация

1980-12-19—Подача