ный вход которого соединен с вьгходом второго коммутатора, вход управления которого подключен ко второму выходу блока управления, адресный вход к цифровому выходу аналого-цифрового преобразователя, выходы сумматора соединены с информационными входами блока элементов И и с информационными входами буферного накопителя, выход блока элементов И соединен со входом параллельного ввода регистра данных, взбоды чтения и записи буферного накопителя подключены соответственно к третьему и четвертому выходам блока управления, пятьй выход которого подсоединен к входу последовательного ввода регистра сдвига, выход которого соединен с входом ввода уставки аналого-цифрового преобразователя, а шестой и седьмой выходы блока управления подключены к управляющим входам сумматора, причем седьмой выход подсоединен к управлякнцему входу блока элементов И, восьмой выход блока управления подключен к управляющему входу первого коммутатора, другие выходы регистра команд соединены с входами деишфратора команд, выходы регистра данных подключены к информационным входам второго коммутатора. 2, Устройство по п. 1, отличающееся тем, что блок управления содержит третий триггер, первый и второй элементы задержки, с первого по шестой элементы И, неинвертирующий выход третьего триггера является первым и вторым выходами блока и соединен с первыми входами первого, второго и третьего элементов И, выходы которых являются пятым, четвертым и шестым выходами блока, инвертирующий выход третьего триггера является Bocbfaw выходом блока и подсоединен к первым входам 11 6 . четвертого и пятого элементов. И, выходы которых являются третьим и седьмым выходами блока, вход установки в 1 третьего триггера подсоединен к выходушестого элемента И, входы которого являются первым и третьим входами блока, вход установки в О третьего триггера является вторым входом блока, вход первого элемента задержки является четвертым входом блока , выход подключен ко второму входу первого элемента И, вторые входы второго и пятого элементов И соединены с выходом второго элемента задержки, который является вторым выходом блока, вход второго элемента задержки соединен со вторыми входами третьего и четвертого элементов И и является пятым входом блока. 3. Устройство, по п. 1, отличающееся тем, что аналогоцифровой преобразователь содержит компараторы, мультиплексор, регистр последовательных приближений и цифроаналоговый преобразователь, выход которого является аналоговым выходом аналого-цифрового преобразователя и подключен к первым входам компараторов, вторые входы которых являются информационными входами аналогоцифрового преобразователя, один информационный вход мультиплексора, ад)есный вход мультиплексора, тактовый вход и выход регистра последовательных приближений являются входами ввода уставки, адресным синхровходом и цифровым выходом аналогоцифрового преобразователя соответственно, выходы компараторов соединены с другими информационными входами мультиплексора, выход которого подключен к информационному входу регистра последовательных приближений, выход которого соединен с входом цифро-аналогового преобразователя.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сбора и предварительной обработки информации | 1981 |

|

SU1012230A1 |

| Устройство для ввода-вывода информации при обработке физических величин | 1981 |

|

SU966683A1 |

| Многоканальная система измерения и регистрации | 1988 |

|

SU1707546A1 |

| Устройство для ввода аналоговых сигналов | 1990 |

|

SU1742810A1 |

| Многоканальное устройство для регистрации аналоговых и цифровых сигналов | 1988 |

|

SU1564649A1 |

| Устройство для определения ядер нелинейных объектов | 1981 |

|

SU1008747A1 |

| УСТРОЙСТВО ДЛЯ СБОРА И ОБРАБОТКИ ДАННЫХ | 2002 |

|

RU2218597C2 |

| Многоканальная система для анализа формы и регистрации аналоговых процессов | 1983 |

|

SU1149242A1 |

| МНОГОКАНАЛЬНАЯ СИСТЕМА ДЛЯ РЕГИСТРАЦИИ ФИЗИЧЕСКИХ ВЕЛИЧИН | 1991 |

|

RU2037190C1 |

| ТЕЛЕВИЗИОННАЯ СИСТЕМА ВЫСОКОГО РАЗРЕШЕНИЯ | 1996 |

|

RU2127961C1 |

Ь УСТРОЙСТВО ДЛЯ ВВОДА ИНФОРМАЦИИ, .содержащее первый коммутатор, дешифратор команд, счетчик адреса, блок управления, буферный накопитель и аналоговый коммутатор, информационные входы которого являютс,я информационными входами устройства, адресный вход буферного накопителя соединен с выходом счетчика адреса , отличающееся тем. что, с целью упрощения устройства, оно содержит второй коммутатор, сумматор, блок, аналоговой памяти, дешифратор адреса, счетчик, генератор тактовых импульсов, первый и второй триггеры, блок элементов И, регистры сдвига5команд и данных,входы параллельного ввода регистра сдвига и регистра данных являются входом-выходом данных устройстваэ а входы регистра команд - входом-выходом управления устройства, одни выходы регистра команд подключены к входам дешифратора команд и к адресному входу анапого-цифрового преобразователя, а через дешифратор адреса - к первому входу блока управленияj первый выход дешифратора команд подключен к управляющим входам регистров сдвига и данных, второй выход - ко второму входу блока управления, третий выход - к третьему входу блока управления, к счетному входу счетчика адреса, к входам установки в 1 первого и второго триггеров, четвертьй выход - ко входу сброса счетчика адреса и к входу установки в О второго триггера, неинвертирующий выход которого подключен к управляющему входу блока аналоговой памяти, выходы которого соединены с информа(Л ционными входами аналого-цифрового преобразователя, входы - с выходами аналогового коммутатора, к входам управления которого подключен аналоговый выход аналого-цифрового преоб разователя, а к стробирующему вз{одупервый выход блока управления, второй выход которого подключен к вхо4: ДУ установки в О первого триггера, сл неинвертируииций выход которого сосо со единен с входом генератора импуль- , сов, выход которого подсоединен к О) четвертому входу блока управления, к синхровходу аналого-цифрового преобразователя и к счетному входу счетчика, выход которого соединен с пятым входом блока управления, цифровой выход аналого-цифрового преобразователя и выход буферного накопителя подсоединены соответственно к адресному и информационному входам первого коммутатора, выход которого подключен к первому информационному входу сумматора, второй информацион

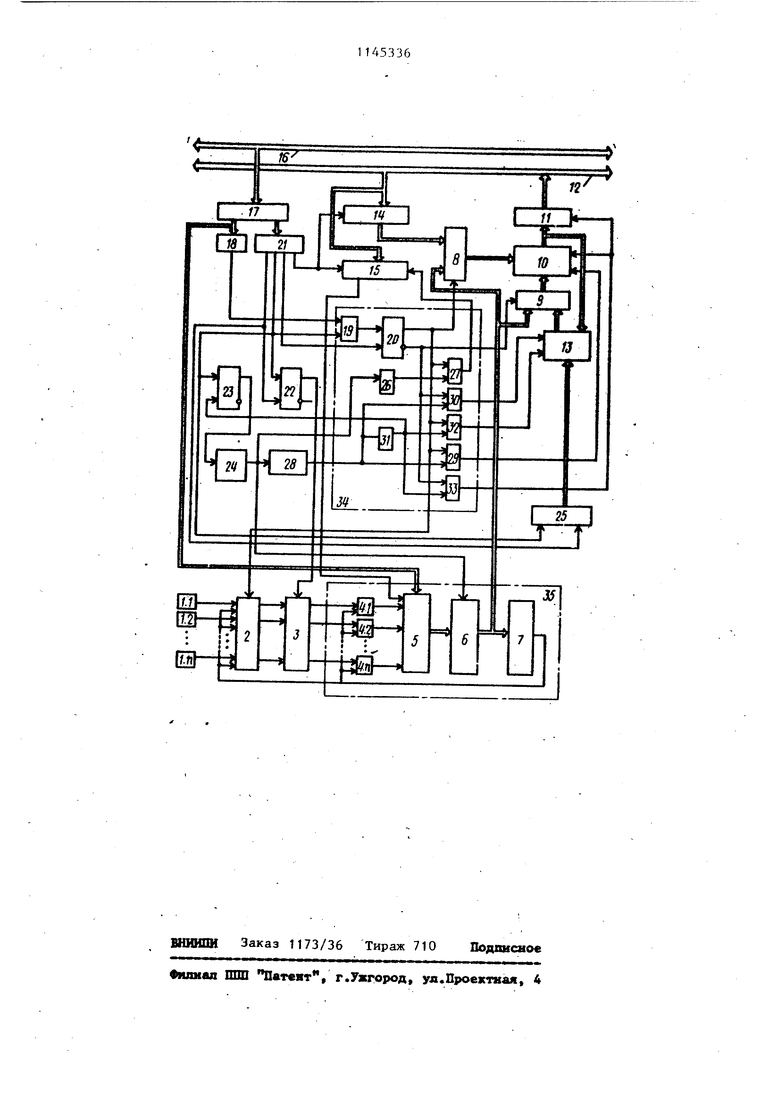

Изобретение относится к автоматик и вычислительной технике и может быть использовано в качестве прецизионной системы сбора и измерения быстроменяющейся аналоговой информации, а также в тренажерных системах и комплексах, обеспечивакяцих управление и слежение за динамическими объектами. Известно устройство для ввода информации, содержащее входной усилитель, аналого-цифровой преобразова тель, две схемы сравнения, четыре регистра, два счетчика, два блока памяти, блок отображения, блок управления, генератор тактовых импульсов, сукшатор, блок вычитания, блок масштабирования и формирователь tl Недостатком устройства является его сложность. Наиболее близким к изобретению по технической сущности является устройство для ввода информации, содержащее блок управления, последо вательно соединенные датчики, коммутатор датчиков, аналого-цифровой преобразователь, блок записи воспроизведения, а также последовательно соединенные блок хранения коэффициентов апроксимации тарированных характеристик датчиков,, арифметический блок, блок регистрации, блок дешифрации номера участка обработки, коммутатор опроса узла хранения номеров каналов, счетчик текущего номер канала, буферный накопитель, коммутатор опроса буферного накопителя, элемент сравнения L21, Недостаток устройства - сложность. Целью изобретения является упро-г щение устройства. Поставленная цель достигается тем, что устройство для ввода информации, содержащее первый коммутатор дешифратор команд, счетчик адреса, блок управления, буферный накопите 1ь и аналоговый коммутатор, информацион ные входы которого являгются информационными входами устройства, адресный вход буферного накопителя соединен с выходом счетчика адреса, содержит второй коммутагор, сумматор, блок аналоговой памяти, дешифратор адреса, счетчик, генератор тактовых импульсов, первьй и второй триггеры блок элементов И, регистры сдвига, команд и данных, входы параллель- . него ввода регистра сдвига и регистра данных являются входом-выходом данных устройства, а входы регистра команд - входом-выходом управления устройства, ОДНИ вьпсоды регистра команд подключены к входам дешифратора команд и к адресному входу аналого-цифрового прербразователя, а чере дешифратор адреса - к первому входу блока управления, первый выход дешифратора команд подключен к управляющим входам регистров сдвига и данных, второй выход - к второму входу блока управления, третий выход к третьему входу блока управления, к счетному входу счетчика адреса к входам-, установки в 1 первого и второго триггеров, четвертый вы- ход - ко входу сброса счетчика адреса и к входу установки в О второго триггера, неинвертирующий выход которого подключен к управляющему входу блока аналоговой памяти, выходы которого соединены с информационными входами аналого-цифрового / преобразователя, входы - с вькодами аналогового коммутатора, к входам управления которого подключен аналоговый выход аналого-цифрового преобразователя, а к стробирующему входу - первый выход блока управления, второй выход которого подключен к входу установки в О первого триггера, неинвертирующий выход которого соединен с входом генератора импульсов, выход которого подсоединен к четвертому входу блока управления, к синхровходу аналого-цифрового преобразователя и к счетному входу счетчика, выход которого соединен с пятым входом блока управления, цифровой,вькод аналого-цифрового преобразователя и выход буферного накопителя подсоединены соответственно к адресному и информационному входам первого коммутатора, выход которого подключен к первому информационному входу сумматора, второй информационный вход которого соединен с выходом второго коммутатора, вход управления которого подключен ко второму выходу блока управления, адресный вход - к цифровому выходу аналого-цифрового преобразователя, выходы сумматора соединены с информационньв и входами блока элементов И и с информационными входами буферного накопителя, выход блока элементов И соединен с входом параллельного ввода регистра данных, входы чтения и записи буферного накопителя подключены соответственно к третьему и четвертому выходам блока управления, пятый выход которого подсоединен к входу последовательного ввода регистра сдвига, вьЬсод которого соединен с входом ввода уставки аналого-цифрового преобразователя,, а шестой и седьмой выходы блока управления подключены к управляющим входам сумматора, причем седьмой выход подсоединен к управляющему входу блока элементов И, восьмой выход бло ка управления подключен к управляюще му входу первого коммутатора, другие выходы регистра команд соединены с входами дешифратора команд, выходы регистра данных подключены к информационным входам второго коммутатора Причем блок управления содержит третий триггер, первый и второй элементы заде)жки, с первого по шестой элементы И, неинвертирующий выход третьего триггера является первым и вторым выходами блока и соединен с первыми входами первого, второго и третьего элементов И, выходы которых являются пятым, четвертым и шестым выходами блока, инвертирующий выход третьего триггера является восьмым выходом блока и подсоединен к тepвым входам четвертого и пятого элементов И, выходы которых являются третьим и седьмым выходами блока, ход установки в 1 третьего триггера подсоединен к выходу шестого элемента И, входы которого являются первым и входами блока вход установки в О третьего триггера является вторым входом блока, вход первого элемента задержки яв- / ляется четвертым входом блока, выход подключен к второму входу первого элеме нта И, вторые входы второго и пятого элементов И соединены с выходом второго элемента задержки, который является вторым- выходом блока, вход второго элемента задержки соединен со вторыми входами третьего и четвертого элементов И и является пятым входом блока. Кроме того, аналого-цифровой преобразователь содержит компаратор мультиплексор, регистр последовательных приближений и цифроаналоговый преобразов-атель, выход которого является аналоговым выходом аналого -цифрового преобразователя и подключен к первым входам компараторов, вторые входы которых являются инфор мационными входами аналого-цифровог преобразователя, один информационный вход мультиплексора, адресный вход мультиплексора, тактовый вход и выход регистра последовательных приближений являются входами ввода уставки, адресным синхровходом и цифровым выходом аналого-цифрового преобразователя соответственно, выходы компараторов соединены с другими информационными входами мультиплексора, выход.которого подключен к информационному входу регистра последовательных приближений, вькодкоторого соединен с входом цифроаналогового преобразователя. На чертеже представлена схема устройства. Схема содержит датчики 1 аналоговых сигналов, аналоговый коммутатор 2, блок 3 аналоговой памяти, компараторы 4, мультиплексор 5, регистр 6 последовательных приближений, Цифроаналоговый преобразователь 7, второй 8 и первый 9 ко1 1утаторы, сумматор 10, блок 11 элементов И, вход-выход 12 данных устройства, буферный накопитель 13, регистр 14 данных, регистр 15 сдвига, вход-выход 16 управления, регистр 17 команд, дешифратор 18 команд, шестой элемент И 19, третий триггер 20, дешифратор 21 команд, второй 22 и первый 23 триггеры, генератор 24 тактовых импульсов, счетчик 25 адреса, первьй элемент задержки 26,. первый элемент И 27, счетчик 28, третий и четвертый элемента И 29, 30, второй элемент задержки 31, второй элемент И 32, пятый элемент И 33 блок 34 управления, аналого-цифровой преобразователь 35. Устройство работает следующим об- , разом. Для введения точного процесса измерения с учетом аддитивных погрешностей цикл обработки входной аналоговой информации осуществляется в два приема, которые обеспечиваются следующими основными режимами: тестовым и собственно измерением. Тестовый режим предназначен для определения индивидуальных погрешностей каждого канала измерения и разделяется на два подрежиму. Первый подрежим обеспечивает занесение кода эталонного значения в ЦАП и начинается с приема по входу-выходу 16 на регистр 17, в результате формируется сигнал Прием кода на регистры 14 и 15, на которые поступает эталонный код данных. Следующая команда, принимаемая на регистр 17, расшифровьшается дешифраторами 21 и устанавливает триггеры 23 и 22 в единичное состояние а по совпадению сигналов на элементе И 19 триггер 20 также уста навливается в единичное состояние. Код адреса направления, снимаемый с регистра 17, коммутирует на мультиплексоре 5 выход регистра 15, хра нящего код эталонного значения, на вход Данные регистра 6. Переход триггера 23 в единичное состояние обеспечивает запуск генератора 24, импульсы с выхода которого через элемент 26 задержки поступают в открытый элемент И 27 и осуществляют сдвиг содержимого регистра 15. Таким образом код эталонного значения поразрядно через мультиплексор 5 по ступает на регистр 6 последовательных приближений, где разворачивается и преобразуется ЦАП 7 в эталонный уровень напряжения, которое подается на входы аналогового коммутатора 2 и компараторов 4. Вьшол- нение команды завершается по переполнению счетчика 28. Первый подрежим заканчивается подачей команды на регистр 17, обнуляющий счетчик 2 адреса и триггер 22. Второй тестовы подрежим обеспечивает вычисление индивидуальных погрешностей для каж дого канала и начинается с приходом команды и адреса на регистр 17, устанавливая триггеры 22, 23 в единич ное состояние и увеличивает содержи мое счетчика 25, обеспечивающего адресацию соответствукяцей ячейки памяти в накопителе 13, Триггер 22 управляет режимом , выборки-хранения блока 3 аналоговой памяти и обеспечивает фиксацию эталонного напряжения, поступающего с ЦДЛ 7 через коммутатор 2, Таким образом, напряжение ЦАП 7, соответствуквцее эквивалентному коду, фиксируется по всем датчикам. По очередному запуску генератора 24 начинается цикл преобразования (с помощью АЦП 35) напряжения первого канала. Цифровой эквивалент этого напряжения устанавливается на выходе регистра 6, за время, необходимое для пересчета счетчика 28, а ПО сигналу переполнения счетчика вы полняется операция вычисления погрешности в сумматоре 10 с данными, поступающими из регистров 6 и 14 через коммутаторы 9 и 8. Результат операции через некоторое время, обеспечиваемое элементом задержки 3 записывается в накопитель 13 (по импульсу с элемента И 32) в ячейку. ; адресуемую счетчиком 25. Таким образом, в первой ячейке накопителя записывается код рассогласования меж-, ду эталонным кодом, хранящимся в регистре 14, и кодом, полученным в результате преобразования на АЦП. Этот код характеризует аддитивную погрешность индивидуального канала преобразователя (погрешность квантования, дрейф блока аналоговой памяти, погрешность компаратора и т.д.) за время, необходимое для измерения первого канала. Эта операция повторяется для всех остальных каналов и соответственно в ячейках накопителя 13 фиксирются значения поправочных коэффициентов, отражающих качество электронных узлов устройства. В измерительном режиме, следукмцим за тестовым, с подачей команды, дешифрируемой в блоке 21, триггер 20 переводится в нулевое состояние, что означает изменение режима работы. Далее повторяется последовательность действий, необходимая для запуска АЦП на преобразование напряжения выбранного канала. Состояние триггера 20 в этом режиме обеспечивает чтение поправочного коэффициента на первой ячейке накопителя 13 после измерения первого канала и суммирования этих величин на сумматоре 10, результат с которого передается через блок элементов И 11 на вход-выход 12, Таким образом, устройство o6jecneчивает прецизионное измерение многоканальной информации с автоматической коррекцией аддитивной погрешности каждого канала преобразователя. Устройство обладает возможиостями, позволяющими в любой момент времени фиксировать состояние всех датчиков, т.е. получать срез во времени многоканальной информации,,и осуществлять оперативный контроль работы каналов преобразователей на точность измерения. Для достижения аналогичного эфекта в устройстве-прототипе неободимо использовать параллельно раотающие аналого-цифровые преобраователи и дополнительную аппаратуру. равним эффективность двух вариантов ерез приведенные затраты на оборуование, необходимое для обеспечения динаковых функциональных возможносей и заданной точности.

Затраты по базовому и предлагаемому вариантам могут быть оценены следующими величинами:

+ с + с

Сс, С„

ком

2С, «- СйЧС|«4« + с

ССАИ

PC + + С

де С стоимость одноканального /аналого-цифрового преобразователя;

С - стоимость сумматора;

Сд - стоимость буферного накопителя ;

Cj - стоимость блока управления;

koM стоимость коммутатора;

Сс - стоимость счетчика;

-С - cтoи focть генератора;

С - стоимость регистра сдвига;

Cpnh стоимость регистра последовательных приближений;

С - стоимость компаратора;

С„ - стоимость мультиплексора Сц - стоимость цифроаналогового преобразователя.

Если учесть, что С

С, С, Cf,t,,, С 5

Ком5

«н

УН

CjjoMu исключить одинаковые час ти, то можно получить следуннщую оценку затрат на организацию вычислений по базовому и предлагаемому вариантам

(N-1)(Cn ч- CJ,

ком + Ср + 2С(.

CCM + 2С (N-1) Сд + CM .

PC

Для сравнения приведенных выражений необходимо их привести к стоимости эквивалентного функционального элемента, например к стоимости триггера. Если разрядность данных - К, а N .- число каналов, то С ,„ К-С, Се СYKj, Ср Сц С, м (N+I)CT, С,„„ КС, с рс КСт, с,. С„ + К-Сч., Ср„„ КСт, Сг А,

и, ц тогда С к (N-1)(A + К А + К А + А)

2A(N-1)(K+1), Г. „ К А + К-А + 21og.jK 4- 2А + К А +

(N-1)A + (N+1)A ЗМ + 2А «

2AN + 2Alog.,K.

Эффективность предлагаемого варианта может быть оценена относительны коэффициентом

С ) -(K+D

ЗКА + 2А + 2AN- + 2А logjK (N-t)(K+1)

IK + 1 -f N +

что, например, при количестве кана,лов N 16 и разрядности преобразования К 12 дает значение коэффициента йС 5 и означает, что эффективность предлагаемого выше базового и растет с увеличением N по закону, определяемому вьфажением для Д.С.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для регистрации информации | 1980 |

|

SU953644A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для обработки измеритель-НОй иНфОРМАции | 1978 |

|

SU807311A1 |

Авторы

Даты

1985-03-15—Публикация

1983-12-14—Подача