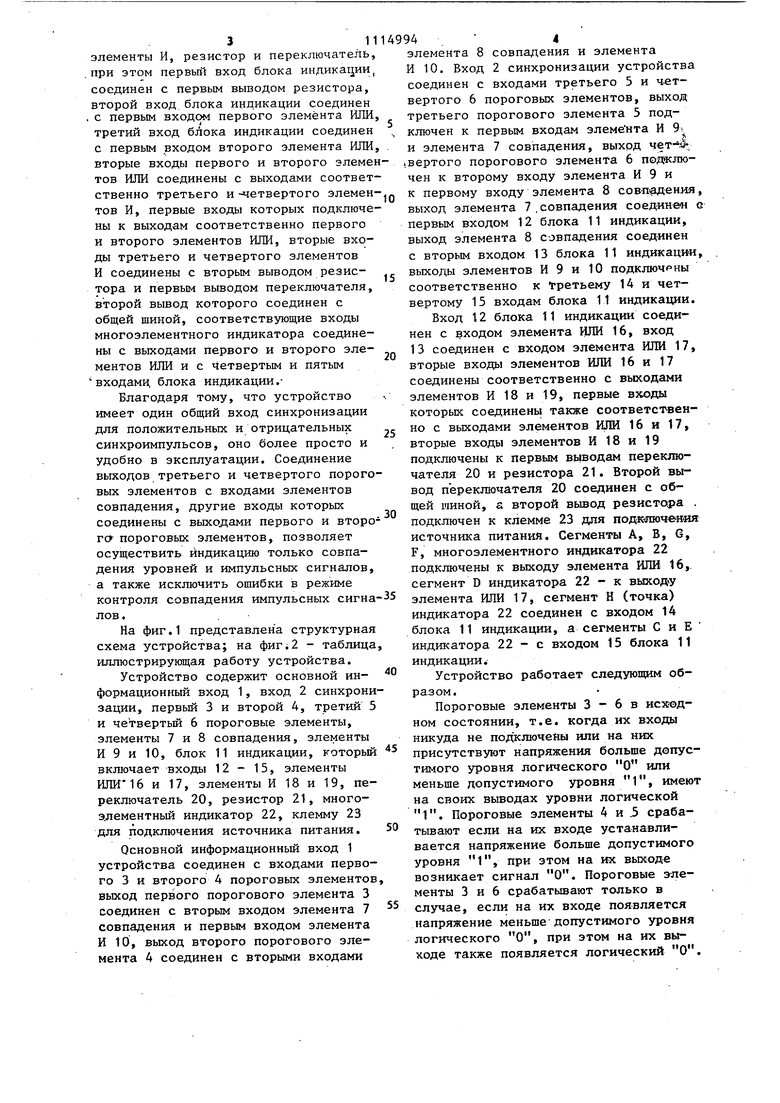

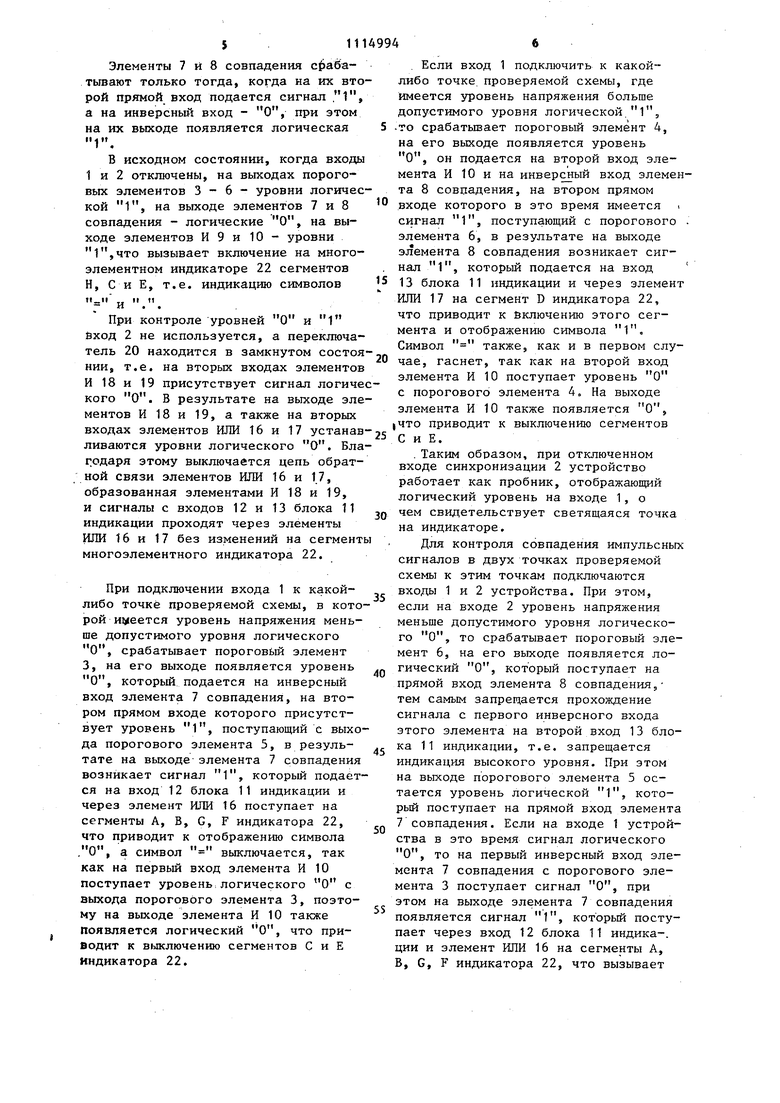

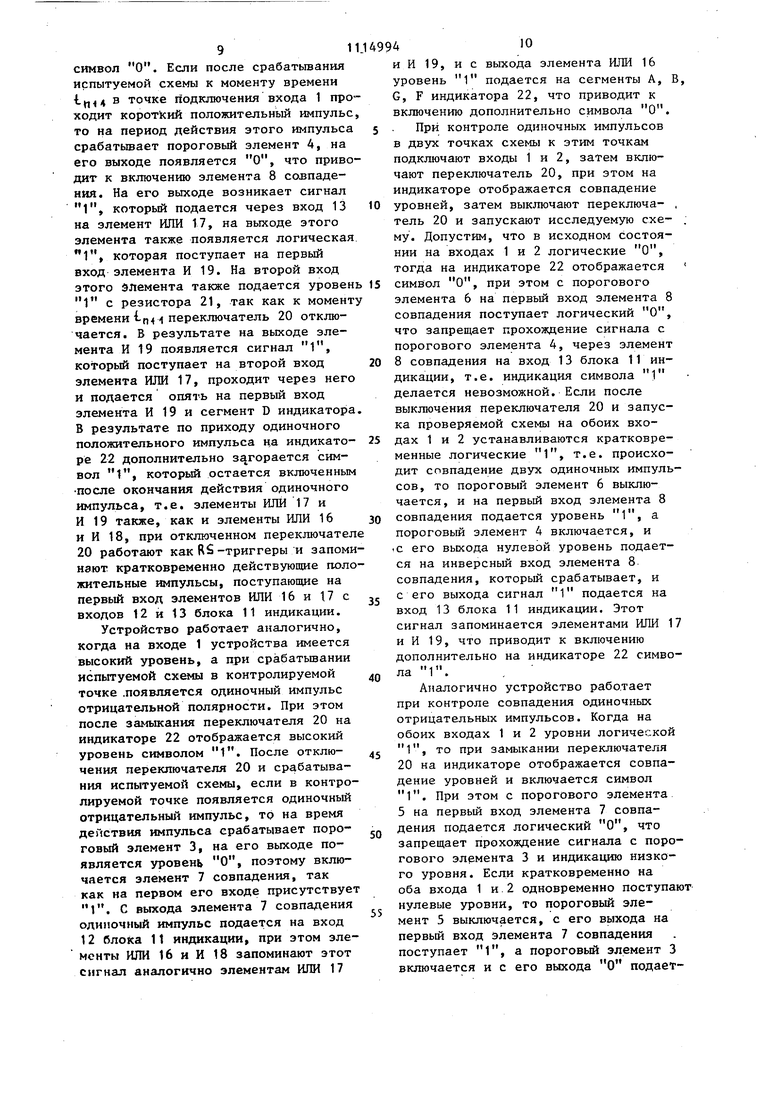

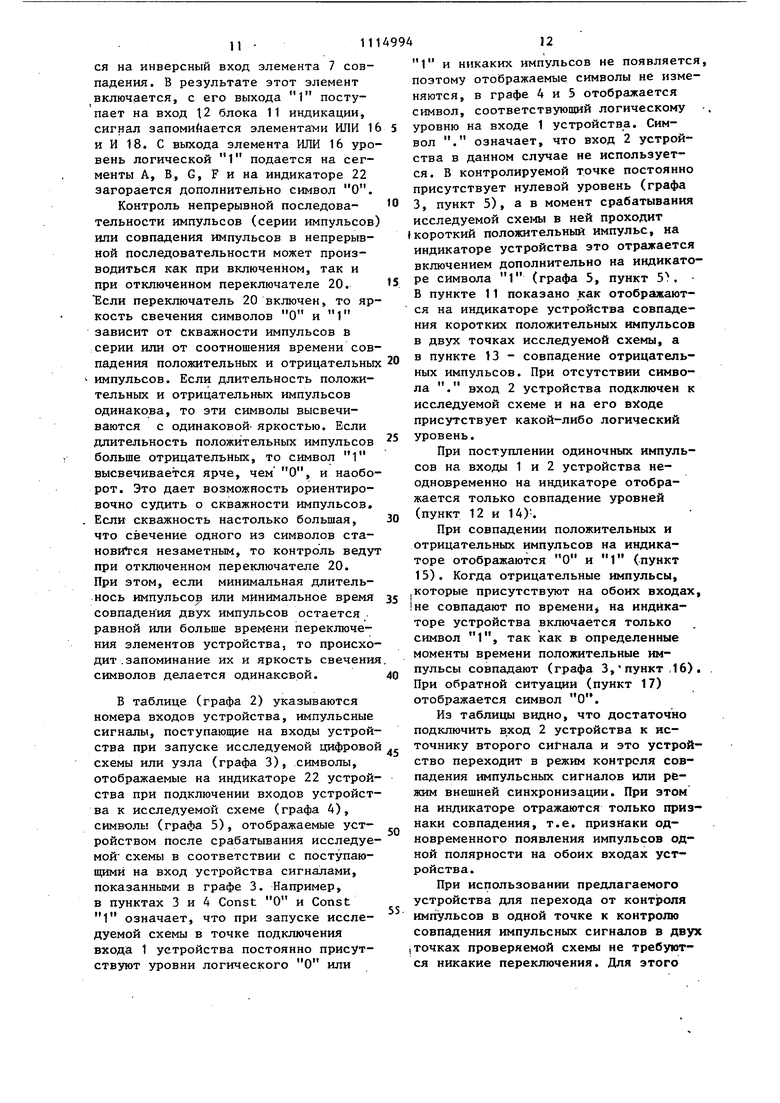

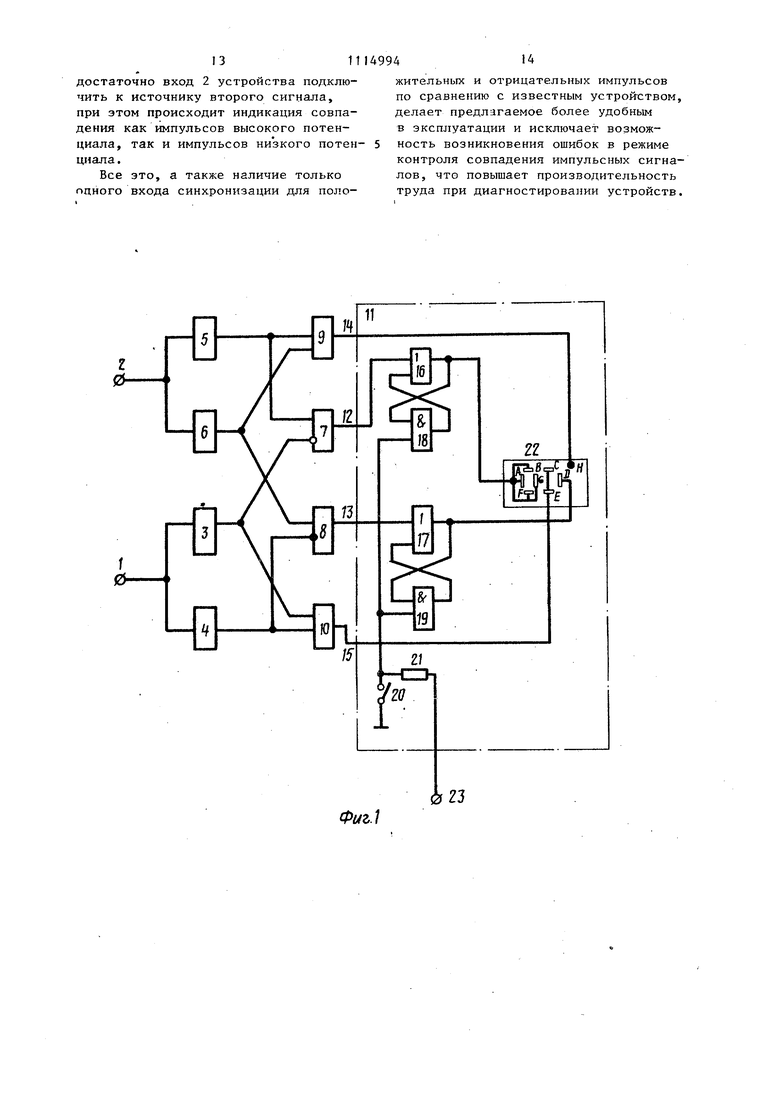

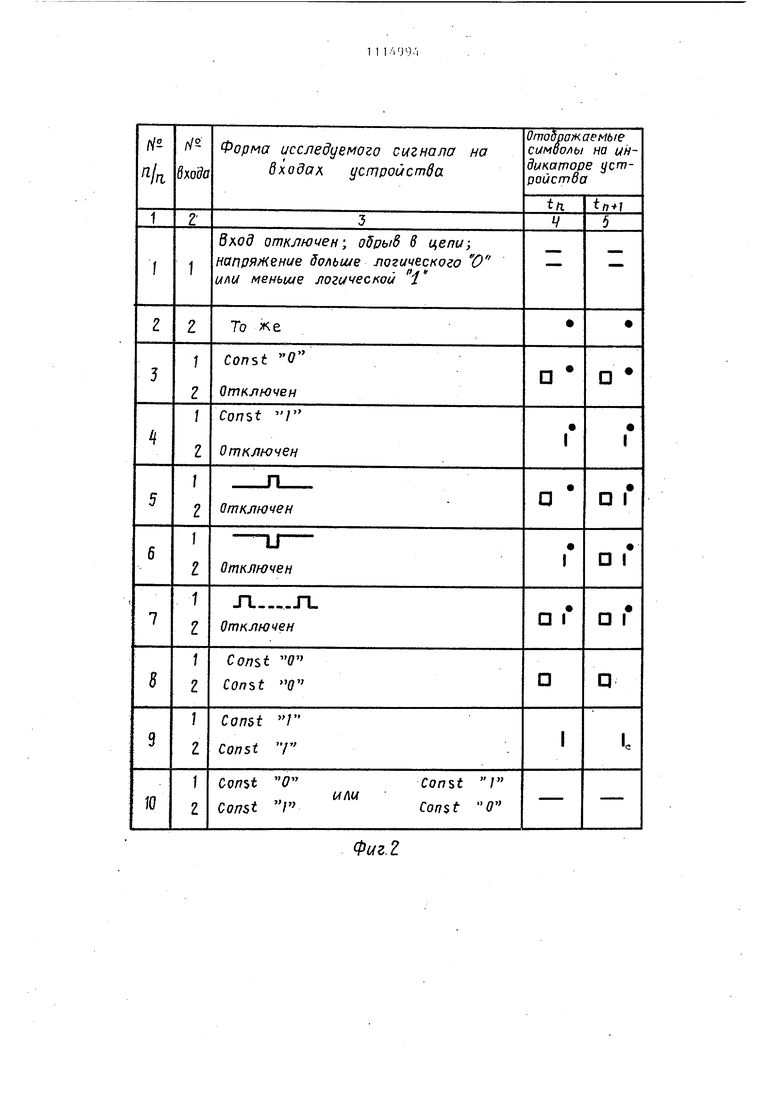

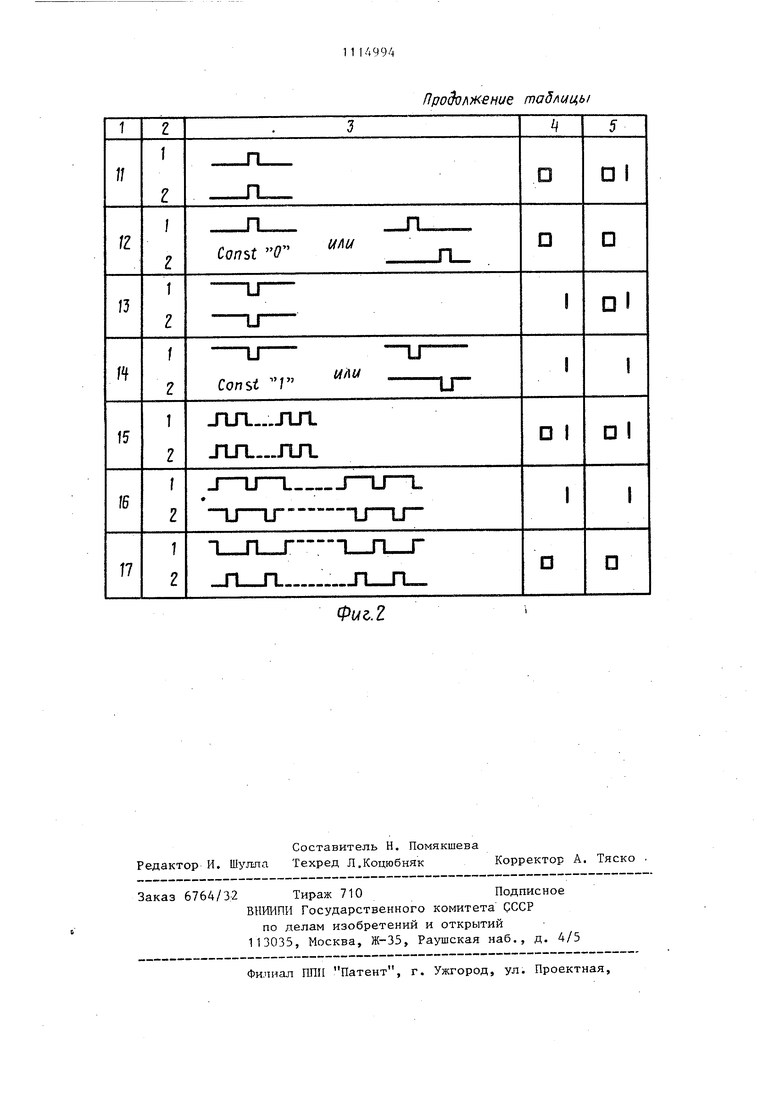

1111 Изобретение относится к импульсно технике и может быть использовано при наладке, контроле -и диагностике цифровых устройств. Известен логический зонд для проверки цепей цифровых узлов, содержащий входной повторитель, пороговые устройства, дешифратор и многоэлементный индикатор, элементы И, элеj BHT ИЛИ, ждущий мультивибратор, фор мирователь коротких импульсов, генератор вытекающего тока нагрузки и RS-триггеры, причем вход входного повторителя соединен с входом логического зонда, выход входного повторителя соединен с входами пороговыхустройств, инверсный выход первого порогового устройства соединен с пер вым входом первого элемента И, второ вход которого соединен с инверсным выходом второго порогового устройства, прямой каждого из пороговы устройств соединен с соответствующим входом дешифратора и элемента ИЛИ, выход которого через ждущий мультивибратор соединен с входом дешифрато рА и непосредственно с R -входами триггеров Cl. Недостатком данного устройства является то, что оно не позволяет контролировать в двух точках схемы совпадение импульсных сигналов. Наиболее близким к изобретению является пробник для проверки цепей цифровых устройств, содержащий пороговые элементы, усилители, блок индикации, два диода, транзистор, синхронизатор, выход которого соединен с первыми входами элементов совпадения, вторые входы которых соединены с выходами пороговых элементов через соответствующие усилители, и блок индикации L2J. Недостатком известного пробника является наличие двух входов синхронизации - отдельно для полояштельных и отрицательных синхроимпульсов. Это приводит к необходимости поочередно переклю.чать их при контроле импульсных сигналов в разньк точках логи-. ческих схем, что снижает оперативность. Кроме того, при подключении к двум точкам схемы с низкими уровнями входа синхронизации для положительных синхроимпульсов и информационног входа пробника прекращается индикаци этого уровня. Аналогично индикация не происходит при подключении информационного входа и входа синхронизации для отрицательных синхроимпульсов к двум точкам схемы с высоким уровнем. Если вход отрицательных синхроимпульсов оказывается подключенным к точке с низким уровнем или вход положительных синхроимпульсов к точке с высоким уровнем, то пробник отображает импульсный сигнал на информационном входе точно также, как и при отключенном входе синхрониза- , ции, все это приводит к возникновению. ошибок при проверке цифровых узлов в режиме контроля совпадения импульсных сигналов. Целью изобретения является повышение удобства эксплуатации и повышение достоверности при контроле совпадения импульсных сигналов. Поставленная цель достигается тем, что в устройство для контроля и настройки цифровых узлов, содержащее клемму для подключения источника питания, первый и второй пороговые элементы, информационный вход устройства, первый и второй элементы совпадения, блок индикации, первый вход которого соединен с клеммой для подключения источника питания, и вход синхронизации устройства,введены третий и четвертый пороговые элементы и два элемента И,при этом входы третьего и четвертого пороговых элементов соединены с входом синхронизации устройства, входы первого и второго пороговых элементов соединены с информационным входом устройства, выходы первого и второго пороговых элементов соединены с первыми входами первого и второго элементов совпадения, выход третьего порогового элемента соединен с первым входом первого элемента И и вторым входом первого элемента совпадения, выход четвертого порогового элемента соединен с вторым входом первого элемента И и вторым входом второго элемента совпадения, вьгходы первого и второго элементов совпадения соединены соответственно с вторым и третьим входами блока индикации, входы второго элемента И соединены с выходами первого и второго пороговых элементов, а выходы первого и второго элементов И подключены соответственно к четвертому и пятому входам блока индикации. Кроме того, блок индикации содер жит мйогоэлементный индикатор, два элемента ИЛИ, третий и четвертый элементы И, резистор и переключатель .при этом первый вход блока индика1 иИ соединен с первым выводом резистора, второй вход блока индикации соединен , с первым входом первого элемента ШТИ третий вход блока индикации соединен с первым входом второго элемента ИЛИ вторые входы первого и второго элеме тов ИЛИ соединены с выходами соответ ственно третьего и -четвертого элемен тов И, первые входы которых подключе ны к выходам соответственно первого и второго элементов ИЛИ, вторые входы третьего и четвертого элементов И соединены с вторым выводом резистора и первым выводом переключателя, второй вывод которого соединен с общей шиной, соответствующие входы многоэлементного индикатора соединены с выходами первого и второго элементов ИЛИ и с четвертым и пятым входами, блока индикации,Благодаря тому, что устройство имеет один общий вход синхронизации для положительных и отрицательных синхроимпульсов, оно более просто и удобно в эксплуатации. Соединение выходов третьего и четвертого порого вых элементов с входами элементов совпадения, другие входы которых соединены с выходами первого и второ гсг пороговых элементов, позволяет осуществить индикацию только совпадения уровней и импульсных сигналов, а также исключить ошибки в режиме контроля совпадения импульсных сигна лов. На фиг. 1 представлена структурная схема устройства; на фиг.2 - таблица иллюстрирующая работу устройства. Устройство содержит основной информационный вход 1, вход 2 синхрони зации, первый 3 и второй 4, третий 5 и четвертьш 6 пороговые элементы, элементы 7 и 8 совпадения, элементы И 9 и 10, блок 11 индикации, которьш вкл очает входы 12 - 15, элементы и 17, элементы И 18 и 19, переключатель 20, резистор 21, многоэлементный индикатор 22, клемму 23 для подключения источника питания. Основной информационный вход 1 устройства соединен с входами первого 3 и второго 4 пороговых элементов выход первого порогового элемента 3 соединен с вторым входом элемента 7 совпадения и первым входом элемента И 10, выход второго порогового элемента 4 соединен с вторыми входами элемента 8 совпадения и элемента И 10. Вход 2 синхронизации устройства соединен с входами третьего 5 и ч-етвертого 6 пороговых элементов, выход третьего порогового элемента 5 подключен к первым входам элемента И 9t и элемента 7 совпадения, выхрд вертого порогового элемента 6 подключен к второму входу элемента И 9 и к первому входу элемента 8 сов-П1адения, выход элемента 7.совпадения соединен G первым входом 12 блока 11 индикации, выход элемента 8 совпадения соединен с вторым входом 13 блока 11 индикации, выходы элементов И 9 и 10 подключены соответственно к третьему 14 и четвертому 15 входам блока 11 индикации. Вход 12 блока 11 индикации соединен с входом элемента ИЛИ 16, вход 13 соединен с входом элемента ИЛИ 17, вторые входы элементов ИЛИ 16 и 17 соединены соответственно с выходами элементов И 18 и 19, первые входы которых соединены также соответственно с выходами элементов ИЛИ 16 и 17, вторые входы элементов И 18 и 19 подключены к первым выводам переключателя 20 и резистора 21. Второй вывод переключателя 20 соединен с общей шиной, а второй вывод резистора . подключен к клемме 23 для иод-к-люче ия источника питания. Сегменты А, В, G, F, многоэлементного индикатора 22 подключены к выходу элемента ИЛИ 16,, сегмент D индикатора 22 - к выход«у элемента ИЛИ 17, сегмент Н (точка) индикатора 22 соединен с входом 14 блока 11 индикации, а сегменты С и Е индикатора 22 - с входом 15 блока 11 индикации. Устройство работает следующим образом. Пороговые элементы 3 - 6 в исходном состоянии, т.е. когда их входы никуда не подключены или на них присутствуют напряжения больше допустимого уровня логического О или меньше допустимого уровня 1, имеют на своих выводах уровни логической 1. Пороговые элементы 4 и .5 срабатывают если на их входе устанавливается напряжение больше допустимого уровня 1, при этом на их выходе возникает сигнал О. Пороговые элементы 3 и 6 срабатывают только в случае, если на их входе появляется напряжение меньше допустимого уровня логического О, при этом на их выходе также появляется логический О. j11 Элементы 7 и 8 совпадения срабатывают только тогда, когда на их вто рой прямой вход подается сигнал 1 а на инверсный вход - О , при этом на их выходе появляется логическая la Ч В исходном состоянии, когда входы 1 и 2 отключены, на выходах пороговых элементов 3 - 6 - уровни логичес кой 1, на выходе элементов 7 и 8 совпадения - логические О, на выходе элементов И 9 и 10 - уровни 1,что вызывает включение на многоэлементном индикаторе 22 сегментов Н, Си Е, т.е. индикацию символов и .. При контроле уровней О и 1 йход 2 не используется, а переключа тель 20 находится в замкнутом состо нии, т.е. на вторых входах элементо И 18 и 19 присутствует сигнал логич кого О. В результате на выходе эл ментов И 18 и 19, а также на вторых входах элементов ИЛИ 16 и 17 устана ливаются уровни логического О. Бл годаря этому выключается цепь обратной связи элементов ИЛИ 16 и 1.7, образованная элементами И 18 и 19, и сигналы с входов 12 и 13 блока 11 индикации проходят через элементы ИЛИ 16 и 17 без изменений на сегмент многоэлементного индикатора 22. При подключении входа 1 к какойлибо точке проверяемой схемы, в кото рой имеется уровень напряжения меньше допустимого уровня логического О, срабатывает пороговый элемент 3, на его выходе появляется уровень О, который подается на инверсный вход элемента 7 совпадения, на втором прямом входе которого присутствует уровень 1, поступающий с выхо да порогового элемента 5, в результате на выходе элемента 7 совпадения возникает сигнал 1, который подает ся на вход 12 блока 11 индикации и через элемент ИЛИ 16 поступает на сегменты А, В, G, F индикатора 22, что приводит к отображению символа .О, а символ выключается, так как на первый вход элемента И 10 поступает уровень:логического О с выхода порогового элемента 3, поэтому на выходе элемента И 10 также Появляется логический О, что приводит к выключению сегментов С и Е Индикатора 22. . Если вход 1 подключить к какойлибо точке, проверяемой схемы, где имеется уровень напряжения больше допустимого уровня логической. то срабатывает пороговый элемент 4, на его выходе появляется уровень О, он подается на второй вход элемента И 10 и на инверсный вход элемента 8 совпадения, на втором прямом входе которого в это время имеется сигнал 1, поступающий с порогового . элемента 6, в результате на выходе элемента 8 совпадения возникает сигнал 1, который подается на вход 13 блока 11 индикации и через элемент ИЛИ 17 на сегмент D индикатора 22, что приводит к Включению этого сегмента и отображению символа 1, Символ также, как и в первом случае, гаснет, так как на второй вход элемента И 10 поступает уровень О с порогового элемента 4. На выходе элемента И 10 также появляется О, ЧТО приводит к выключению сегментов . Таким образом, при отключенном входе синхронизации 2 устройство работает как пробник, отображаю1ций логический уровень на входе 1, о чем свидетельствует светящаяся точка на индикаторе. Для контроля совпадения импульсных сигналов в двух точках проверяемой схемы к этим точкам подключаются входы 1 и 2 устройства. При этом, если на входе 2 уровень напряжения меньше допустимого уровня логического О, то срабатывает пороговый элемент 6, на его выходе появляется логический О, который поступает на прямой вход элемента 8 совпадения, тем самым запрещается прохождение сигнала с первого инверсного входа этого элемента на второй вход 13 блока 11 индикации, т.е. запрещается индикация высокого уровня. При этом на выходе порогового элемента 5 остается уровень логической 1, который поступает на прямой вход элемента 7 совпадения. Если на входе 1 устройства в это время сигнал логического О, то на первый инверсный вход элемента 7 совпадения с порогового элемента 3 поступает сигнал О, при этом на выходе элемента 7 совпадения появляется сигнал 1, которьй поступает через вход 12 блока 11 индика-. ции и элемент ИЛИ 16 на сегменты А, В, G, F индикатора 22, что вызывает 711 включение знака О. Если на входе 1 устройства в это время уровень логической 1, то срабатывает пороговый элемент 4 и на его выходе появляется сигнал О, а/на выходе порогового элемента 3 остается уровень 1, который поступает на инверсный вход элемента 7.. совпадения, и на его выхо де, так же как и на выходе элемента 8 совпадения, логический О. Также логические О на выходах элементов И 9 и 10, так как на втором входе элемента И 9 присутствует уровень О, поступающий с выхода порогового элемента 6, а на одном из входов эле мента И 10 также уровень О, поступающий с порогового элемента 4, в зависимости от того, какой уровень О или 1 на входе 1. При этом на индикаторе 22 устройства все элемент ;отключены. Так происходит индикация совпадения низких уровней. При подключении входа 2 устройства к какой-либо точке проверяемой схемы, где имеется напряжение больше допустимого уровня логической 1, на второй прямой вход элемента 7 совпадения с порогового элемента 5 подается логический О, что запрещает прохождение сигналов с порогового элемента 3, т.е. индикацию низ-) кого уровня. На первом входе элемента 8 совпадения остается сигнал 1, поступающий с порогового элемента 6 Если на входе 1 устройства в это вре мя уровень логической 1, то на инверсный вход элемента 8 совпадения поступает логический О с выхода по рогового элемента 4, поэтому элемент 8 совпадения срабатьшает, на его выходе появляется сигнал 1, который подается на вход 13 блока индикации 11 и через элемент ИЛИ 17 проходит на сегмент D индикатора 22, что вызы вает включение символа 1. Если на входе 1 устройства О, когда на входе 2 уровень 1, то на второй вход элемента 7 совпадения с порогового элемента 5 поступает О, а на инверсный вход элемента 8 совпадения с выхода порогового элемента 4 подае ся уровень 1, поэтому на выходах .элементов 7 и 8 совпадения логически О, которые Подаются на входы 12 и 13 блока 11 индикации, также на первые входы элементов И 9 и 10 с пороговых элементов 3 и 5 поступают нуле вые уровни, поэтому,на их выходах, а следовательно, и на входах 15 и 8 14 блока 11 индикации сигналы О. При этом все элементы на индикаторе 22 отключены. Таким образом, при подключении входа 2 устройства к какой-либо точке схемы осуществляется индикация только совпадения сигналов, при этом знак . на индикаторе выключен, так как на один из входов элемента И 9 поступает сигнал логического О с порогового элемента 5 или 6. Для контроля прохождения в испытуемой схеме одиночных импульсов, серий коротких импульсов и совпадения их (т.е. одновременного прохс ; дения в двух разных цепях исследуемой схемы) используется запоминание кратковременных процессов в блоке индикации. Для этого в случае контроля прохождения одиночных импульсов и серий импульсов подключается к проверяемой схеме только вход 1, для контроля совпадения одиночных импульсов и совпадения серий импульсов в двух точках исследуемой схемы подключаются к этим точкам входы 1 и 2. В обоих случаях после подключения входов включается испытуемая схема и замыкается переключатель 20 устройства, при этом на индикаторе устройства осуществляется индикация имеющихся уровней на входах 1 и 2, как описано выше. Обозначим этот момент времени i. Затем переключатель 20 выключается, при этом на индикаторе устройства продолжают высвечиваться те же символы, однако на вторые входы элементов И 18 и 19 с резистора 21 поступает уровень логической 1, тем самым включается цепь обратной связи элементов ИЛИ 16 и 17 и они становятся подготовленными для запоминания информации с входов 12 и 13 блока 11 индикации. После этого испытуемая цифровая схема или узел запускается на выполнение своей работы или на ее вход подается от внешнего источника. Обозначим момент времени после срабатывания контролируемой схемы tf,. Предположим, что если при контроле прохождения одиночного импульса в момент времени i ( на входе 1 устройства низкий уровень, то с порогового элемента 3 нулевой уровень подается на инверсный вход элемента 7 совпадения, в результате на индикаторе 22 устройства отображается 9 символ О Если после срабатьгоания испытуемой схемы к моменту времени в точке подключения входа 1 про ходит короткий положительный импульс то на период действия этого импульса срабатывает пороговый элемент 4, на его выходе появляется О, что приво дит к включению элемента 8 совпадения. На его выходе возникает сигнал 1, который подается через вход 13 на элемент ИЛИ 17, на выходе этого элемента также появляется логическая 1, которая поступает на первый вход элемента И 19. На второй вход этого элемента также подается уровен 1 с резистора 21, так как к момент времени переключатель 20 отключается. В результате на выходе элемента И 19 появляется сигнал 1, который поступает на второй вход элемента ИЛИ 17, проходит через него и подается опять на первый вход элемента И 19 и сегмент D индикатора В результате по приходу одиночного положительного импульса на индикаторе 22 дополнительно загорается символ 1, который остается включенным после окончания действия одиночного импульса, т.е. элементы ИЛИ 17 и И 19 также, как и элементы ИЛИ 16 и И 18, при отключенном переключател 20 работают как RS-триггеры и запоми нают кратковременно действующие поло жительные импульсы, поступающие на первый вход элементов ИЛИ 16 и 17 с входов 12 и 13 блока 11 индикации. Устройство работает аналогично, когда на входе 1 устройства имеется высокий уровень, а при срабатьшании испытуемой схемы в контролируемой точке .появляется одиночный импульс отрицательной полярности. При этом после замыкания переключателя 20 на индикаторе 22 отображается высокий уровень символом 1. После отключения переключателя 20 и срабатывания испытуемой схемы, если в контролируемой точке появляется одиночный отрицательный импульс, то на время действия импульса срабатывает пороговый элемент 3, на его выходе появляется уровень О, поэтому включается элемент 7 совпадения, так как на первом его входе присутствует Г. С выхода элемента 7 совпадения одиночный импульс подается на вход 12 блока 11 индикации, при этом элементы ИЛИ 16 и И 18 запоминают этот сигнал аналогично элементам ИЛИ 17 А10 и И 19, и с выхода элемента ИЛИ 16 уровень 1 подается на сегменты А, В, G, F индикатора 22, что приводит к включению дополнительно символа О. . При контроле одиночных импульсов в двух точках схемы к этим точкам подключают входы 1 и 2, затем включают переключатель 20, при этом на индикаторе отображается совпадение уровней, затем выключают переключа- , тель 20 и запускают исследуемую схему. Допустим, что в исходном состоянии на входах 1 и 2 логические О, тогда на индикаторе 22 отображается симв1ол О, при этом с порогового элемента 6 на первый вход элемента 8 совпадения поступает логический О, что запрещает прохождение сигнала с порогового элемента 4, через элемент 8 совпадения на вход 13 блока 11 индикации, т.е. индикация символа 1 делается невозможной. Если после выключения переключателя 20 и запуска проверяемой схемы на обоих входах 1 и 2 устанавливаются кратковременные логические 1, т.е. происходит совпадение двух одиночных импульсов, то пороговый элемент 6 выключается, и на первый вход элемента 8 совпадения подается уровень 1, а пороговый элемент 4 включается, и с его выхода нулевой уровень подается на инверсный вход элемента 8 совпадения, который срабатывает, и с его выхода сигнал 1 подается на вход 13 блока 11 индикации. Этот сигнал запоминается элементами ИЛИ 17 и И 19, что приводит к включению дополнительно на индикаторе 22 символа 1. Аналогично устройство работает при контроле совпадения одиночных отрицательных импульсов. Когда на обоих входах 1 и 2 уровни логической 1, то при замыкании переключателя 20 на индикаторе отображается совпадение уровней и включается символ 1. При этом с порогового элемента 5 на первый вход элемента 7 совпадения подается логический О, что запрещает прохождение сигнала с порогового элемента 3 и индикацию низкого уровня. Если кратковременно на оба входа 1 и.2 одновременно поступают нулевые уровни, то пороговый элемент 5 выключается, с его выхода на первый вход :элемента 7 совпадения поступает 1, а пороговый элемент 3 включается и с его выхода О подается на инверсный вход элемента 7 совпадения. В результате этот элемент включается, с его выхода 1 поступает на вход 12 блока 11 индикации, сигнал запоминается элементами ИЛИ 1 и И 18. С выхода элемента ИЛИ 16 уро вень логической 1 подается на сегменты А, В, G, F и на индикаторе 22 загорается дополнительно символ О. Контроль непрерывной последовательности импульсов (серии импульсов или совпадения импульсов в непрерывной последовательности может производиться как при включенном, так и при отключенном переключателе 20. Если переключатель 20 включен, то яр кость свечения символов О и 1 зависит от скважности импульсов в серии или от соотношения времени сов падения положительных и отрицательны импульсов. Если длительность положительных и отрицательных импульсов одинакова, то эти символы высвечиваются с одинаковой- яркостью. Если длительность положительных импульсов больше отрицательных, то символ 1 высвечивается ярче, чем О, и наобо рот. Это дает возможность ориентировочно судить о скважности импульсов. Если скважность настолько большая, что свечение одного из символов становится незаметным, то контроль веду при отключенном переключателе 20. При этом, если минимальная длительнось импульсов или минимальное время совпадения двух импульсов остается . равной или больше времени переключения элементов устройства, то происхо дит .запоминание их и яркость свечени символов делается одинаковой. В таблице (графа 2) указываются номера входов устройства, импульсные сигналы, поступающие на входы устрой ства при запуске исследуемой цифрово схемы или узла (графа 3), символы, отображаемые на индикаторе 22 устрой ства при подключении входов устройст ва к исследуемой схеме (графа 4), символы (графа 5), отображаемые устройством после срабатывания исследуе мой схемы в соответствии с поступающими на вход устройства сигналами, показанными в графе 3. Например, в пунктах 3 и 4 Const О и Const 1 означает, что при запуске исследуемой схемы в точке подключения входа 1 устройства постоянно присутствуют уровни логического О или 1 и никаких импульсов не появляется, поэтому отображаемые символы не изменяются, в графе 4 и 5 отображается символ, соответствующий логическому . уровню на входе 1 устройства. Символ . означает, что вход 2 устройства в данном случае не используется. В контролируемой точке постоянно присутствует нулевой уровень (графа 3, пункт 5), а в момент срабатывания исследуемой схемы в ней проходит короткий положительный импульс, на индикаторе устройства это отражается включением дополнительно на индикаторе символа 1 (графа 5, пункт 5). В пункте 11 показано как отображаются на индикаторе устройства совпадения коротких положительных импульсов в двух точках исследуемой схемы, а в пункте 13 - совпадение отрицательных импульсов. При отсутствии символа . вход 2 устройства подключен к исследуемой схеме и на его входе присутствует какой-либо логический уровень. При поступлении одиночных импульсов на входы 1 и 2 устройства неодновременно на индикаторе отображается только совпадение уровней (пункт 12 и 14). При совпадении положительных и отрицательных импульсов на индикаторе отображаются О и 1 (пункт 15). Когда отрицательные импульсы, которые присутствуют на обоих входах, не совпадают по времениj на индикаторе устройства включается только символ 1, так как в определенные моменты времени положительные импульсы совпадают (графа 3,пункт ,16), При обратной ситуации (пункт 17) отображается символ О. Из таблицы видно, что достаточно подключить вход 2 устройства к источнику второго сигнала и это устройство переходит в режим контроля совпадения импульсных сигналов или режим внешней синхронизации. При этом на индикаторе отражаются только признаки совпадения, т.е. признаки одновременного появления импульсов одной полярности на обоих входах устройства. При использовании предлагаемого устройства для перехода от импульсов в одной точке к контролю совпадения импульсных сигналов в двух точках проверяемой схемы не требуются никакие переключения. Для этого 1311 достаточно вход 2 устройства подключить к источнику второго сигнала, при этом происходит индикация совпадения как импульсов высокого потенциала, так и импульсов низкого потен циала. Все это, а также наличие только одного входа синхронизации для поло414жительных и отрицательных импульсов по сравнению с известным устройством, делает предлагаемое более удобным в эксплуатации и исключает возможность возникновения ошибок в режиме контроля совпадения импульсных сигналов, что повышает производительность труда при диагностировании устройств.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля цифровых узлов | 1988 |

|

SU1636811A1 |

| Устройство для контроля цифровых узлов | 1985 |

|

SU1352419A1 |

| Устройство для контроля и настройки цифровых узлов | 1987 |

|

SU1471159A1 |

| Логический зонд | 1986 |

|

SU1383237A1 |

| Устройство для контроля цифровых сигналов | 1981 |

|

SU1032428A1 |

| Устройство для измерения параметров дыхания | 1990 |

|

SU1803037A1 |

| Устройство для контроля цифровых блоков | 1987 |

|

SU1503031A1 |

| Логический пробник | 1986 |

|

SU1352421A1 |

| Устройство для контроля и диагностики цифровых устройств | 1988 |

|

SU1583886A2 |

| Логический пробник | 1987 |

|

SU1525636A1 |

1. УСТРОЙСТВО ДЛЯ КОНТРОЛЯ И НАСТРОЙКИ ЦИФРОВЫХ УЗЛОВ, содержащее клемму для подключения источника питания, первый и второй пороговые элементы, информационный вход устройства, первый и второй элементы совпадения, блок индикации, первый вход которого соединен с клеммой для подключения источника питания, и вход синхронизации устройства, отличающееся тем, что, с целью повьп1ения удобства эксплуатации и повышения достоверности при контроле совпадения импульсных сигналов, в него введены третий и четвертый пороговые элементы и два элемента И, при этом входы третьего и четвертого пороговых элементов соединены с входом синхронизации устройства, входы первого и второго пороговых элементов соединены с информационным входом устройства, выходы первого и второго пороговых элементов соединены с первыми входами первого и второго элементов совпадения, ныход трет1.его порогового элемента соединен с первым входом первого элемента И и вторым входом перпо)-о элемента совпадения, выход четвертого порогового элемента соединен с вторым входом первого элемента И и вторым входом второго элемента совпадения, выходы первого и второго элементов совпадения соединены соответственно с вторым и третьим входами блока индикации, входы второго элемента И соединены с выходами первого и второго пороговых элементов, и выходы первого и второго элементов И подключены соответственно к четвертому И пятому входам блока ин- . дикации. / 2. Устройство по п. I, о т л ичающееся тем, что блок инди- , кации содержит многоэлементный индикатор, два элемента ИЛИ, третий и чет(Л вертьш элементы И, резистор и переключатель, при этом первый вход блока индикации соединен с первым выводом резистора, второй вход блока индикации соединен с первым входом первого элемента ИЛИ, третий вход блока индикации соединен с первым входом второго элемента ИЛИ, вторые входы первого и второго элементов ДЛИ сое1 динены с выходами соответственно со третьего и четвертого элементов И, 00 первые входы которых подключены к 1 выходам соответственно первого и второго элементов ИЛИ, вторые входы третьего и четвертого элементов И соединены с вторым выводом резистора и первым выводом переключателя, второй вывод которого соединен с общей шиной, соответствующие входы многоэлементного индикатора соединены с выходами первого и второго элементов ИЛИ и с четвертым и пятым входами блока индикации.

Фиг.1

&гз

.2

Прод жение тадл1 14ы

DI

/ 2

/2

или

C(7r7St

D

D

Л

13

Dl

f

w/iw

Const f

г

ЛЛ-ЛЛ.

t5 JLTL-ял.

15

г

-TJ-LT

17

-Л-П.

Фме.2

-и

Dl

D i

П

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Логический зонд | 1977 |

|

SU729533A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Патент США № 3742351, кл | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1984-09-23—Публикация

1983-01-07—Подача