вогр и второго элементов И прдклю- отрицательной шиной устройства, а ,чены к.выходу первого элемента НЕ, выход третьего элемента И-НЕ непоси-входы первого, второго и третьего редственно и через шестой элемент НЕ И-триггеров и второй вход первого подключен к третьим входам первого

переключателя режимов соединены с элемента И-ИЛИ-НЕ.

1032А28

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля функционирования логических блоков | 1986 |

|

SU1327107A1 |

| Устройство для контроля цифровых сигналов | 1983 |

|

SU1246056A2 |

| Многоканальное устройство тестового контроля логических узлов | 1988 |

|

SU1564623A1 |

| Логический пробник | 1987 |

|

SU1525636A1 |

| Логический пробник | 1986 |

|

SU1352421A1 |

| Устройство для тестового контроля логических узлов | 1991 |

|

SU1837297A1 |

| Устройство для измерения произведения двух напряжений | 1983 |

|

SU1195265A1 |

| Устройство измерения угла опережения впрыска топлива дизеля | 1984 |

|

SU1229413A1 |

| Устройство для испытаний датчиков давления | 1983 |

|

SU1129624A1 |

| Устройство для формирования гистограммы случайных чисел | 1988 |

|

SU1702391A1 |

1

Изобретение относится к автоматике и может быть использовано для оперативного визуального контроля за состоянием логических элементов в цифровой аппаратуре.5

Известно устройство для проверки логических блоков, содержащее инвертор, первый и второй элементьГ И-НЕ, интегратор, пороговый блок, Г1ервый и второй формирователи сигналов 10 первый и второй триггеры, фильтр, генератор импульсов, а также третий и четвертый триггеры, первый и второй индикаторы .

Недостатком устройства является 15 ограниченная полнота контроля, так как не фиксируются перепады, не отображаются фронты импульсов и полярности, нет счёта импульсов, неудобное отображение выходной информации 20 с помощью светодиодов.

Наиболее близким техническим решением к предлагаемому является логический пробник, содержащий взаимосвязанные формирователь сигна- 25 ла Сброс, переключатель режимов, элементы И и блок фиксации обрыва, а также включенные последовательно счетчик, дешифратор и блок индикации, инвертор,соединенный выходом с обнуля- зо ющим входом счетчика, а входом f с шиной питания t ,

Недостатком этого устройства является невозможность фиксации перепадов контролируемых напряжений и знаков х фронтов..

Цель изобретения - расширение обасти применения устройства путем расширения диапазона характеристик онтролируемых цифровых сигналов,

Поставленная цель достигается ем, что в устройство для контроля ифровых сигналов, содержащее формирователь сигнала Сброс, блок фикации обрыва, первый и второй элемены И, первый переключатель режимов 5

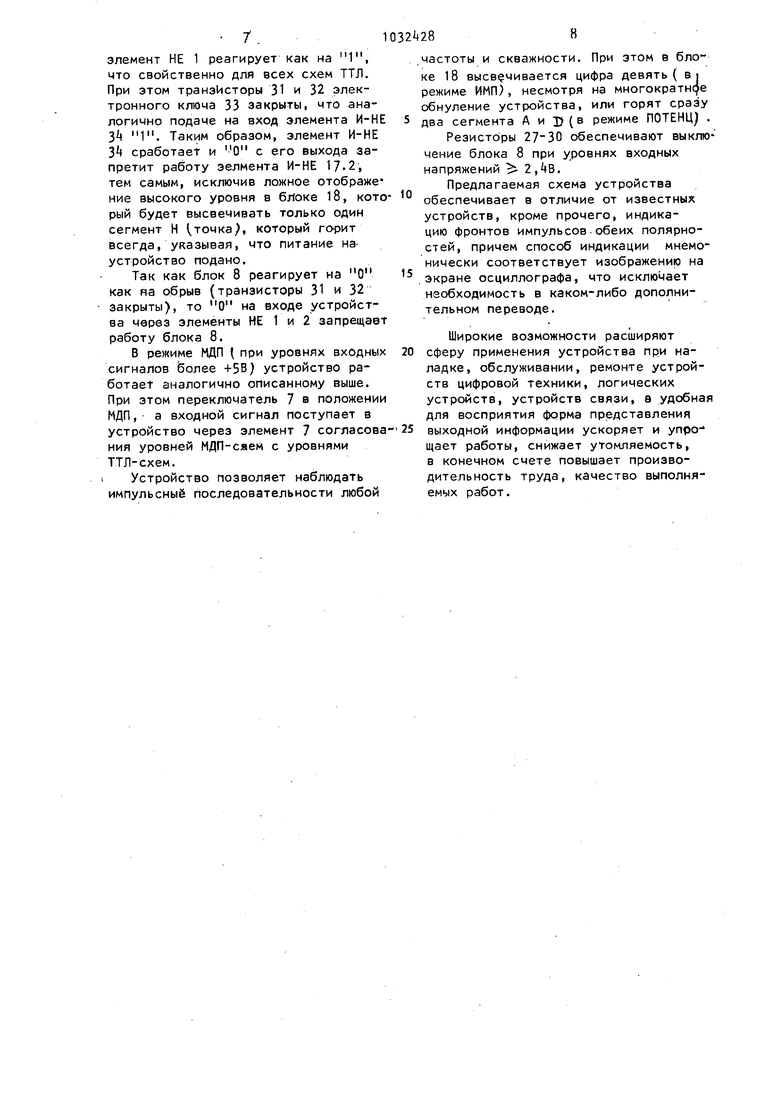

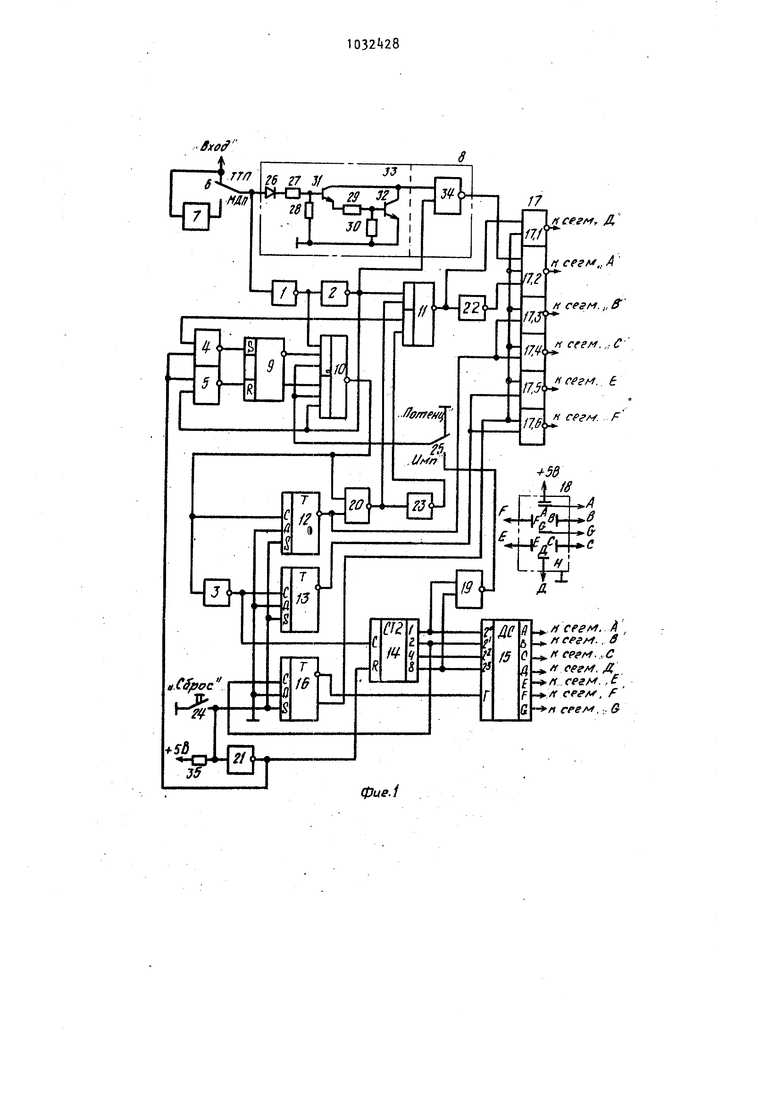

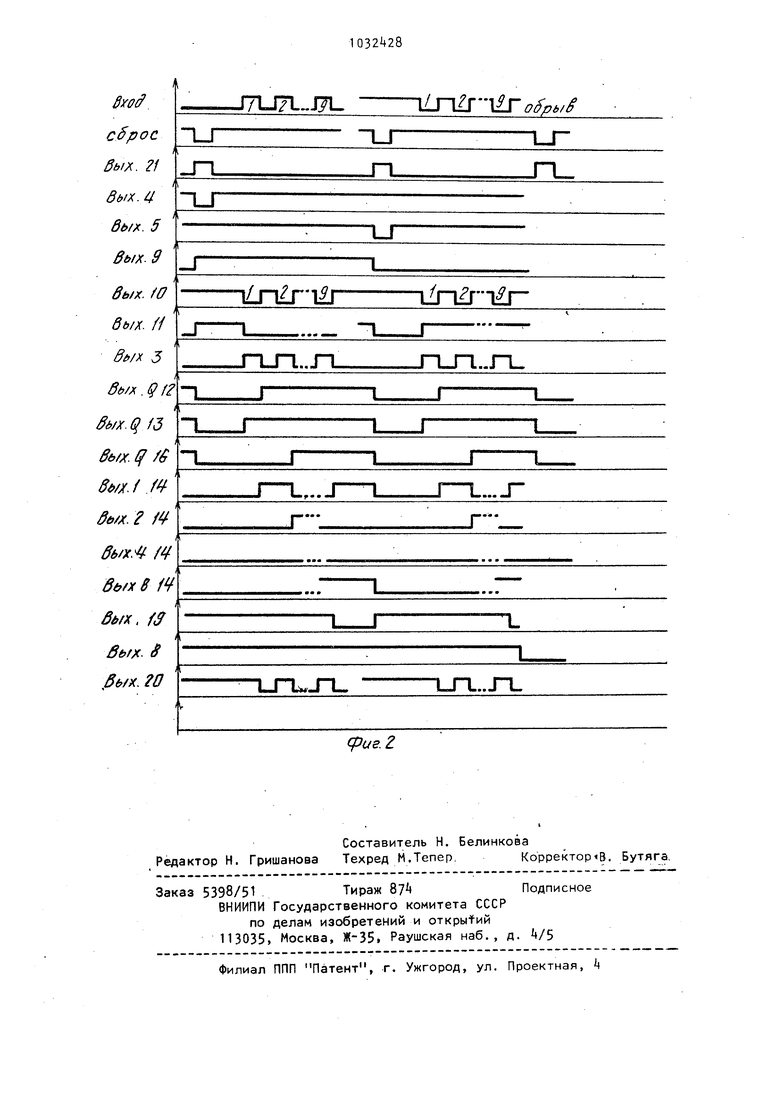

и последовательно соединенные счетчик, дешифратор и блок индикации, причем вход сброса счетчика через первый элемент НЕ подключен к поло- . жительной шине питания, введены восемь элементов И-НЕ, пять элементов НЕ, два элемента И-ИЛИ-НЕ, три1 -триггера, RS-триггер, элемент согласования уровней и второй переключатель режимов, один вход которого непосредственно, а другой вход через элемент согласования уровней соединены с входом устройства, выход первого элемента И-ИЛИ-НЕ соединен с первым ВХОДОМпервого элемента И-НЕ и через второй элемент НЕ - с первым вхо.дом второго, элемента И-НЕ, вторым входом подключенного к выходу блока фиксации обрыва, первый вход которого сое- динен с выходом второго переключателя режимов и через третий элемент НЕ с входом четвертого элемента НЕ и с первыми входами первого элемента И и первого и второго элементов И-ИЛИНЕ, а второй вход - с выходом четвертого элемента НЕ, с вторыми входами первого и второго элементов И-ИЛИНЕ и с первым входом второго элемента И, подключенного выходом к R-входу К -триггера, 5-вход которого соединен с выходом первого элемента И, а примой и инверсный выходы - с третьим и четвертым входами соответственно второго элемента-И-ИЛИ-НЕ, подсоедиенного выходом к первому вхс5ду Т15етьео элемента И-НЕ и к С-входу первого) риггера и через пятый элемент НЕ С-.входам второго) -триггера и счетчика, выход одного из разрядов которого подключен к С-входу третьего y-триггера, соединенного S-входом с S-входами первого и второго 1 -три1- геров, с положительной шиной питания и через формирователь сигнала Сброс с отрицательной- шиной питания, выхоы младшего и старшего разрядов счетчика через четвертый элемент подключены к первому входу первого переключателя режимов, соединенного выходом с пятыми входами второго эле мента И-ИЛИ-НЕ, инверсный выход первого) -триггера связан с вторым входом третьего и с первыми входами пят го и шестого элементов И-НЕ, а инверсный выход второго 1)-триггера с первыми входами седьмого и восьмог элементов И-НЕ, прямой выход третьего D-триггера подключен к вторым входам первого, второго, пятого, шестого, седьмого и восьмого элементов И-НЕ, соединенных выходами с соответствюущими входами блока индикации, вторые входы первого и второго элементов И подключены к выходу первого элемента НЕ, а1)-входы первого, второго и третвего 3)-тригге ров и второй вход первого переключателя режимов соединены с отрицательной шиной устройства, а выход третьего элемента И-НЕ непосредствен но и через шестой элемент НЕ подключен к третьим входам первого элемента И-ИЛИ-НЕ. На фиг. 1 представлена схема , устройства; на фиг. 2 - временная диаграмма работы устройства. Устройство ( фиг. Л) содержит третий 1, четвертый 2 и пятый 3 элементы НЕ, первый и второй 5 элементы И, второй переключатель 6 режимов, элемент 7 согласования уровней, блок 8 фиксации обрава, К -триггер 9. вто рой 10 и первый, 11 элемнты И-ИЛИ-НЕ, первый 12 и второй 13 -триггеры, счетчик 1, дешифратор 15 третий Ъ-дриггер 16, группу элементов И-НЕ 17. состоящуТсГиз первого 17. второго 17.2, пятого 17.3. шестого 17. седьмого 17.5 и восьмого 17.6 элемен тов И-НЕ, блок 18 индикации, состоящий из семи сегментов А. В, С,1 , Е, G, четвертый 19 и третий 20 элементы И-НЕ, первый 21, второй 22 и шестой 23 элементы НЕ, формирователь 2 сигналов Сброс первый переклю« чатель 25 режимов, блок 8 состоит из диода 26, резисторов и транзис торов 31 и 32, образующих электронный ключ 33, и из элементатИ-НЕ З в состав устройства также входит резистор 35 (токоограничивающие резисторы блока 18 не показаны). Устройство работает следующим образом. И-Н e Рассмотрим работу устройства в режимах ТТЛ (при уровнях входных сигналов не более +5В и ИМП С счетный, При этом переключатели 6 и 25 находятся в положении ТТЛ и ИМП соответственно. Перед началом контроля устройство обнуляется от формирователя 2k. При этом наS-входы триггеров 12. . . 13 и 16 кратковременно поступает низкий уровень напряжения, устанавливая их в единичное состояние, которому соответствует низкий логический уровень О на инверсных выходах. На выходе элемента НЕ 21 при обнулении появляется соответственно высокий лоигческий уровень 1 , который обнуляет счетчик Ш и устанавливает триггер Э через элементы И-НЕ 4 и 5 а состояние, сответствующее начальному уровню входного сигнала. Если начальное значение входного сигнала О, то триггер 9 при обнулении устанавливается через элемент И -НЕ k по§-входу в единичное состояние, при котором 1 с его прямого входа разрешает работу элемента И-ИЛИ-НЕ 10по нижнему плечу. Если начальное значение входного сигнала 1, то триггер 9 при обнулении устанавливается через элемент И-НЕ 5 по h-входу в нулевое состояние, при котором 1 с его инверсного выхода разрешает работу элемента И-ИЛИ-НЕ 10 по верхнему плечу. Элемент И-ИЛИ-НЕ 11в исходном состоянии открыт для прохождения входного сигнала черз элементы НЕ 1 и 2 по верхнему плечу, так как 1 с инверсного выхода триггера 12, поступая через элемент И-НЕ 20 и элемент НЕ 23, запрещает его работу по нижнему плечу. Таким обраэом, при начальном значении входного сигнала 1 на выходе эАемента И-ИЛИ-НЕ 11 будет 1, которая через элемент И-НЕ 17-1 (представляющий собой схему с от крытымколлектором на выходе), зажигает сегмент D блока 18, что соответствует изобра-. жению низкого логического уровня входного сигнала. При начальном значении входного сигнала 1 на выходе элемента И-ИЛИ-НЕ 11 будет 1, которая через элемент НЕ 22 и элемент И-НЕ 17.2 зажигает сегмент А блока 18, что соответствуетизображению высокого лоигческого уровня входного сигнала. Работа дешифратора 15 запрещена 1, поступающей с инверсного выхода триггера 1б на Г-вход. С прямого выхода триггера 16 1 разрешает работу группы элементов, И-НЕ 17. При изменении уровня входного сигнала, т.е. по переднему фронту первого): входного импульса, на выходах элементов И-ИЛИ-НЕ 10 и 11 урйвни сигналов изменяются на противоположные. |,енейия сигнала на выходе элемента 11 приводит к зажиганию сегм1ента блока 18, противоположного предыдуще му (сегменты А и1) изображают противоположные уровни входного сигнала 1 и О соответственно . На выходе элемента И-ИЛИ-НЕ 10 сигнал изменится на .О, который через элемент НЕ 3 устанавливает триггер 13 по С-8ХОДУ в нулевое состояние, при котором 1 с его инверсного выхода через элементы 17.5 и зажигает сегменты Е и V блока 1Ь, что соответствует изображению переднего фронта первого входного импульса. Таким образом, при появлении пере ;Пада уровня из О в 1 или из 1 в О на блоке индикации 18 горит сегмент А или соответственно и сег менты Е и F . При следующем изменении входного сигнала, т.е. по заднему фронту первого входного импульса, навыходе .элемента И-ИЛИ-НЕ 10 снова будет 1, которая устанавливает по С-входу триггер 12 в нулевое состояние, при котором 1 с его инверсного выхода через элементы 17.3 и 17. зажи гает сегменты В и С блока 18, что соответствует изображению заднего фронта входного импульса. Одновременно 1 с инверсного выхода триггера 12 изменяет уровни сигналов на выходах элемента И-НЕ и элемента НЕ 23 на противополож ные, раз решая работу элемента И-ЙЛИ-НЕ 11 по нижнему плечу и запрещая по верхнему. Этим сохраняется значение сигнала на выходе элемента И-ИЛИ-НЕ 11. Таким образом, после окончания первого импульса на входе устройства на блоке 18 горят сегменты В,-.С Е, F и А или Т) в зависимости от полярности импульса,, что соответствует изображению поступившего импульса. Одновременно по заднему фронту первого входного импульса, т.е. по изменению сигнала на выходе элемента И -ИЛИ-НЕ 10 из О в 1 в счетчике Н по С-входу записывается 1. При следующем изменении уровня входного сигнала, т.е. по переднему фронту второго входного импульса на выходе зелмента И-ИЛИ-НЕ 10 снова появляется О, который изменяет уровни сигналов на выходах элементов 20 и 23 на противоположные, разрешая работу элемента И-ИЛИ-НЕ 11 снова по верхнему плечу и запрещая по нижнему. В результате значения сигнала на выходе элемента И-ИЛИ-НЕ 11 сохраня1ртс:я1, а состояние блока 18 не изменится. По окончании второго входного импульса, т.е. по его заднему фронту на выходе элемента И-ИЛИ-НЕ 10 снова будет 1, которая через элемент НЕ 3 записывает в счетчик Ц по С-входу число два, при котором 1 с его второго выхода устанавливает по С-входу триггер 16 в нулевое состояние,Логическая 1 с его инверсного выхода разрешает работу дешифратора 15| а О с его прямого выхода запрещает работу группы элементов И-НЕ 17. Таким образом, после двух импульсов на входе устройства блок 18 высвечивает цифру два от дешифратора 15. При поступлении следующих импульсов на вход устройства счетчик 14 работает в счетном режиме по С-входу, а его состояние индицируется через дешифратор 15 на блоке 18. По девятому импульсу сработает элемент И-НЕ 19 на выходе которого О запрещает работу элемента И-ИЛИ-НЕ 10, т.е. дальнейший счет входных импульсов прекращается. Для последующей работы устройство обнуляется от кнопки СБРОС. Потенциальный режим устройства {переключатель 25 в положении ПОТЕНЦ.) является частным случаем режима ИМП. При этом работа элемента И-ИЛИ-НЕ 10 запрещена низким потенци- ; алом от переключателя 25- В .этом режи- i Мб элемент И-ИЛИ- НЕ 11 работает толь- ; ко по верхнему плечу, так как триггер ; 12 в.единичном состоянии, а блок 18 высвечивает текущее значение входного сигнала, т.е. при О горит сегмент, а при 1 - сегмент А. Обнуление устройства в этом-режиме не требуется.При обрыве на входе устройства (или состояний высокого 7. элемент HE 1 реагирует как на 1, что свойственно для всех схем ТТЛ. При этом транзисторы 31 и 32 электронного ключа 33 закрыты, что аналогично подаче на вход элемента И-Н ЗА 1. Таким образом, элемент И-НЕ 3 сработает и О с его выхода запретит работу эелмента И-НЕ 17.2, тем самым, исключив ложное отображе ние высокого уровня в блоке 18, кот рый будет высвечивать только один сегмент Н точка, который горит всегда, указывая, что питание наустройство подано. Так как блок 8 реагирует на О как на обрыв (транзисторы 31 и 32 закрыты), то О на входе устройства через элементы НЕ 1 и 2 запрещае работу блока 8. В режиме МДП при уровнях входны сигналов Ьолее +5В) устройство работает аналогично описанному выше. При этом переключатель 7 в положени МДП, а входной сигнал поступает в устройство через элемент 7 согласов ния уровней МДП-сяем с уровнями ТТЛ-схем. 1 Устройство позволяет наблюдать импульсные последовательности любой 28 частоты и скважности. При этом в блоке 18 высвечивается цифра девять ( BI режиме ИМП, несмотря на многократное обнуление устройства, или горят сразу два сегмента А и D(B режиме ПОТЕНЦ) . Резистбры 27-30 обеспечивают выклю чение блока 8 при уровнях входных напряжений 2,. Предлагаемая схема устройства обеспечивает в отличие от известных устройств, кроме прочего, индикацию фронтов импульсов-обеих полярностей, причем способ индикации мнемонически соответствует изображению на экране осциллографа, что исключает необходимость в каком-либо дополнительном переводе. Широкие возможности расширяют сферу применения устройства при наладке, обслуживании, ремонте устройств цифровой техники, логических устройств, устройств связи, а удобная для восприятия форма представления выходной информации ускоряет и упро щает работы, снижает утомляемость, в конечном счете повышает производительность труда, качество выполняемых работ.

8

17

Y jcffH, д.

ti сег/.,

, н cesM.,,ff 17,3

.нcegf. , . H ееем... б

.A . ,C

.ft сегм. Д M сегм. .,

./f CPf, f

л cpe .;.&

це.1

cpae.Z

Авторы

Даты

1983-07-30—Публикация

1981-09-08—Подача