Изобретение относится к измерительной технике и может быть использовано при регулировке устройств цифровой а зтоматики и вычислительной техники.

Цель изобретения - повышение достоверности контроля путем обеспечения возможности контроля сигнала во время всего контрольного такта.

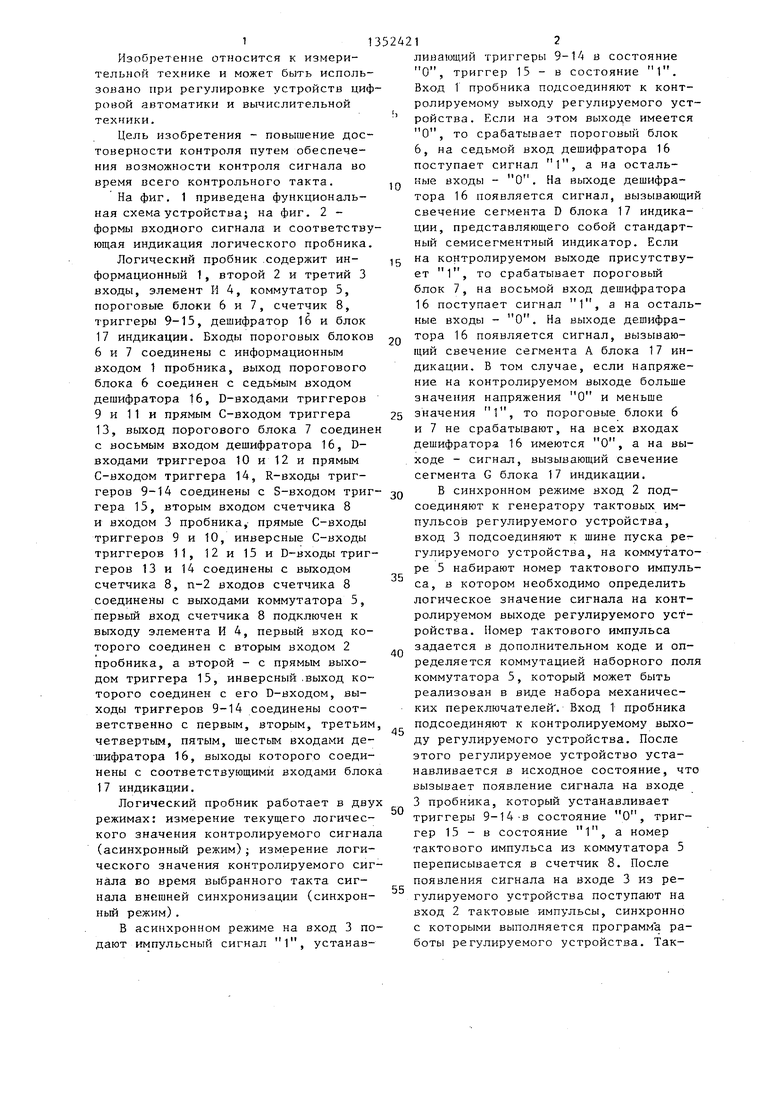

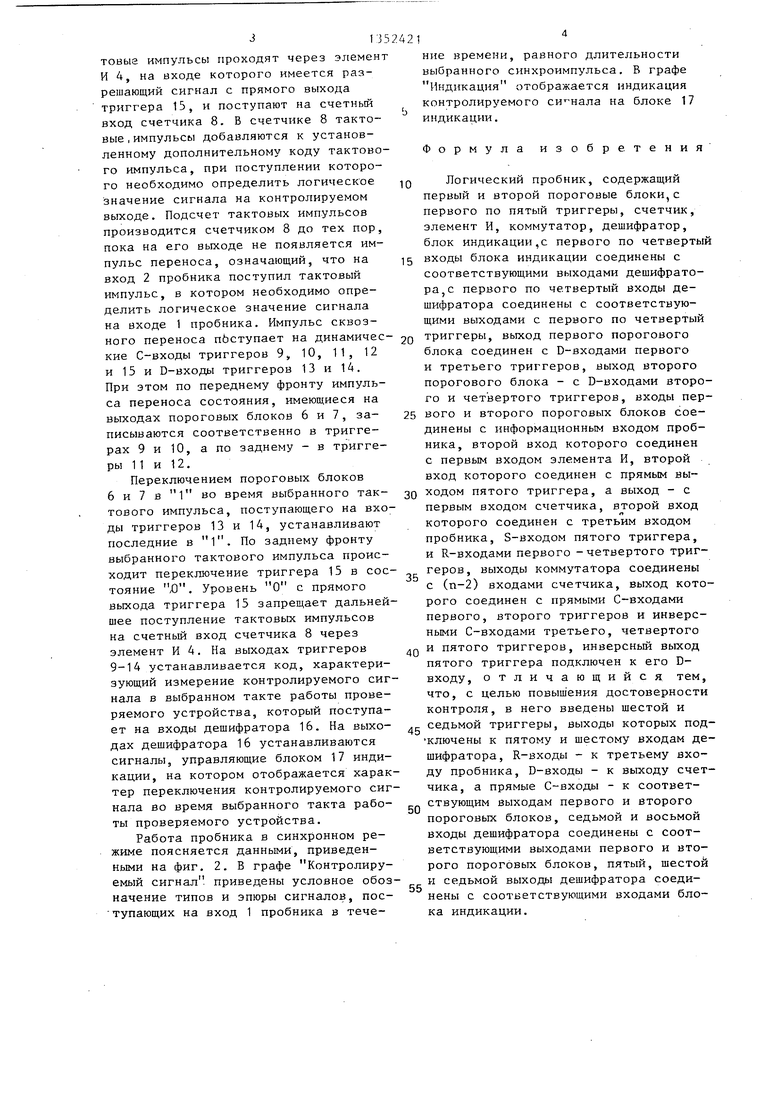

На фиг. 1 приведена функциональная схема устройства; на фиг. 2 - формы входного сигнала и соответствующая индикация логического пробника.

Логический пробник содержит информационный 1, второй 2 и третий 3 входы, элемент И 4, коммутатор 5, пороговые блоки 6 и 7, счетчик 8, триггеры 9-15, дешифратор 16 и блок 17 индикации. Входы пороговых блоков 6 и 7 соединены с информационным входом 1 пробника, выход порогового блока 6 соединен с седьмым входом дешифратора 16, D-входами триггеров 9 и 11 и прямым С-входом триггера 13, выход порогового блока 7 соедине с восьмым входом дешифратора 16, D- входами триггероа 10 и 12 и прямым С-входом триггера 14, R-входы триггеров 9-14 соединены с S-входом триггера 15, вторым входом счетчика 8 и входом 3 пробника,- прямые С-входы триггеров 9 и 10, инверсные С-входы триггеров 11, 12 и 15 и D-входы триггеров 13 и 14 соединены с выходом счетчика 8, п-2 входов счетчика 8 соединены с выходами коммутатора 5, первый вход счетчика 8 подключен к выходу элемента И 4, первый вход которого соединен с вторым входом 2 пробника, а второй - с прямым выходом триггера 15, инверсный .выход которого соединен с его D-входом, выходы триггеров 9-14 соединены соответственно с первым, вторым, третьим четвертым, пятым, шестым входами де- шифратора 16, выходы которого соединены с соответствующими входами блок 17 индикации.

Логический пробник работает в дву режимах: измерение текущего логического значения контролируемого сигнал (асинхронный режим); измерение логического значения контролируемого сигнала во время выбранного такта сигнала внешней синхронизации (синхронный режим).

В асинхронном режиме на вход 3 подают импульсный сигнал 1, устанавливающий триггеры 9-14 в состояние

0

5

0

О

1

, триггер 13 - в состояние Вход 1 пробника подсоединяют к контролируемому выходу регулируемого устройства. Если на этом выходе имеется О, то срабатывает пороговый блок 6, на седьмой вход дешифратора 16 поступает сигнал l, а на остальные входы - О. На выходе дешифратора 16 появляется сигнал, вызывающий свечение сегмента D блока 17 индикации, представляющего собой стандартный семисегментный индикатор. Если на контролируемом выходе присутствует 1, то срабатывает пороговый блок 7, на восьмой вход дешифратора 16 поступает сигнал 1, а на остальные входы - О. На выходе дешифратора 16 появляется сигнал, вызывающий свечение сегмента А блока 17 индикации. В том случае, если напряжение на контролируемом выходе больше значения напряжения О и меньше

25 значения

то пороговые блоки 6

0

5

0

5

0

5

и 7 не срабатывают, на всех входах дешифратора 16 имеются О, а на выходе - сигнал, вызывающий свечение сегмента G блока 17 индикации.

В синхронном режиме вход 2 подсоединяют к генератору тактовых импульсов регулируемого устройства, вход 3 подсоединяют к шине пуска ре гулируемого устройства, на коммутаторе 5 набирают номер тактового импульса, в котором необходимо определить логическое значение сигнала на контролируемом выходе регулируемого устройства. Номер тактового импульса задается в дополнительном коде и определяется коммутацией наборного поля коммутатора 5, который может быть реализован в виде набора механических переключателей . Вход Т пробника подсоединяют к контролируемому выходу регулируемого устройства. После этого регулируемое устройство устанавливается в исходное состояние, что вызывает появление сигнала на входе 3 пробника, который устанавливает триггеры 9-14-в состояние О, триггер 15 - в состояние 1, а номер тактового импульса из коммутатора 5 переписывается в счетчик 8. После появления сигнала на входе 3 из регулируемого устройства поступают на вход 2 тактовые импульсы, синхронно с которыми выполняется программа работы регулируемого устройства. Тактовые импульсы проходят через элемен И 4, на входе которого имеется разрешающий сигнал с прямого выхода триггера 15, и поступают на счетный вход счетчика 8. В счетчике 8 тактовые ,импульсы добавляются к установленному дополнительному коду тактового импульса, при поступлении которого необходимо определить логическое значение сигнала на контролируемом выходе. Подсчет тактовых импульсов производится счетчиком 8 до тех пор, пока на его выходе не появляется импульс переноса, означающий, что на вход 2 пробника поступил тактовый импульс, в котором необходимо определить логическое значение сигнала на входе 1 пробника. Импульс сквозного переноса пбступает на динамические С-входы триггеров 9, 10, 11, 12 и 15 и D-входы триггеров 13 и 14. При этом по переднему фронту импульса переноса состояния, имеющиеся на выходах пороговых блоков 6 и 7, записываются соответственно в триггерах 9 и 10, а по заднему - в триггеры 1 1 и 1 2 .

Переключением пороговых блоков 6 и 7 в 1 во время выбранного тактового импульса, поступающего на входы триггеров 13 и 14, устанавливают последние в 1. По заднему фронту выбранного тактового импульса происходит переключение триггера 15 в состояние Я. Уровень О с прямого выхода триггера 15 запрещает дальнейшее поступление тактовых импульсов на счетньм вход счетчика 8 через элемент И 4. На выходах триггеров 9-14 устанавливается код, характеризующий измерение контролируемого сигнала в выбранном такте работы проверяемого устройства, который поступает на входы дешифратора 16. На выходах дешифратора 16 устанавливаются сигналы, управляющие блоком 17 индикации, на котором отображается характер переключения контролируемого сигнала во время выбранного такта работы проверяемого устройства.

Работа пробника в синхронном режиме поясняется данными, приведенными на фиг. 2. В графе Контролируемый сигнал приведены условное обозначение типов и эпюры сигналов, пос- тупающих на вход 1 пробника в течение времени, равного длительности выбранного синхроимпульса. В графе Индикация отображается индикация контролируемого си -нала на блоке 17 индикации.

Формула изобретения

Q Логический пробник, содержащий первый и второй пороговые блоки,с первого по пятый триггеры, счетчик, элемент И, коммутатор, дешифратор, блок индикации,с первого по четвертый

5 входы блока индикации соединены с соответствующими выходами дешифратора, с первого по четвертый входы дешифратора соединены с соответствующими выходами с первого по четвертый

Q триггеры, выход первого порогового блока соединен с D-входами первого и третьего триггеров, выход второго порогового блока - с D-входами второго и четвертого триггеров, входы пер5 вого и второго пороговых блоков соединены с информационным входом пробника, второй вход которого соединен с первым входом элемента И, второй вход которого соединен с прямым вы0 ходом пятого триггера, а выход - с первым входом счетчика, второй вход которого соединен с третьим входом пробника, S-входом пятого триггера, и R-входами первого -четвертого триггеров, выходы коммутатора соединены с (т1-2) входами счетчика, выход которого соединен с прямыми С-входами первого, второго триггеров и инверсными С-входами третьего, четвертого

Q и пятого триггеров, инверсный выход пятого триггера подключен к его D- входу, отличающийся тем, что, с целью повышения достоверности контроля, в него введены шестой и

g седьмой триггеры, выходы которых под- ключены к пятому и шестому входам дешифратора, R-входы - к третьему входу пробника, D-входы - к выходу счетчика, а прямые С-входы - к соответствующим выходам первого и второго пороговых блоков, седьмой и восьмой входы дешифратора соединены с соответствующими выходами первого и второго пороговых блоков, пятый, шестой и седьмой выходы дешифратора соединены с соответствующими входами блока индикации.

5

0

5

Редактор Л.Пчолинская

Составитель В.Юхлин

Техред Л. Сердюкова Корректор А.Обручар

Заказ 5563/45

Тираж 730Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб,, д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная, 4

фиг.г

| название | год | авторы | номер документа |

|---|---|---|---|

| Логический пробник | 1984 |

|

SU1242863A1 |

| Логический пробник | 1981 |

|

SU970281A1 |

| Логический пробник | 1987 |

|

SU1525636A1 |

| Логический пробник | 1985 |

|

SU1275335A1 |

| Устройство для контроля и диагностики цифровых блоков | 1983 |

|

SU1167610A1 |

| ЛОГИЧЕСКИЙ ПРОБНИК | 1991 |

|

RU2041473C1 |

| Устройство для контроля цифровых блоков | 1987 |

|

SU1503031A1 |

| Логический пробник | 1986 |

|

SU1352420A1 |

| Устройство для контроля цифровых блоков | 1985 |

|

SU1262504A1 |

| Устройство для контроля логических блоков | 1984 |

|

SU1196692A1 |

Изобретение может быть использовано при регулировке устройств цифровой автоматики и вычислительной техники. Цель изобретения - повышение достоверности контроля. Пробник содержит элемент И 4, коммутатор 5, пороговые блоки 6 и 7, счетчик 8, триггеры 9-13, дешифратор 16 и блок 17 индикации. Введение триггеров 14 и 15 обеспечивает возможность контроля сигналов во время всего контрольного такта, 2 ил. (Л с со ел ГчЭ 4 to

| Логический пробник | 1984 |

|

SU1242863A1 |

Авторы

Даты

1987-11-15—Публикация

1986-04-16—Подача