Изобретение относится к автоматике и импульсной технике и используется для формирования исполнительной команды через определенный интервал времени, называемый уставкой, задаваемой последовательным цифpовым кодом перед запуском таймера. Код заданной уставки может быть проконтролирован, результат контроля выводится на выходную шину.

Цель изобретения уменьшение числа шин управления таймером.

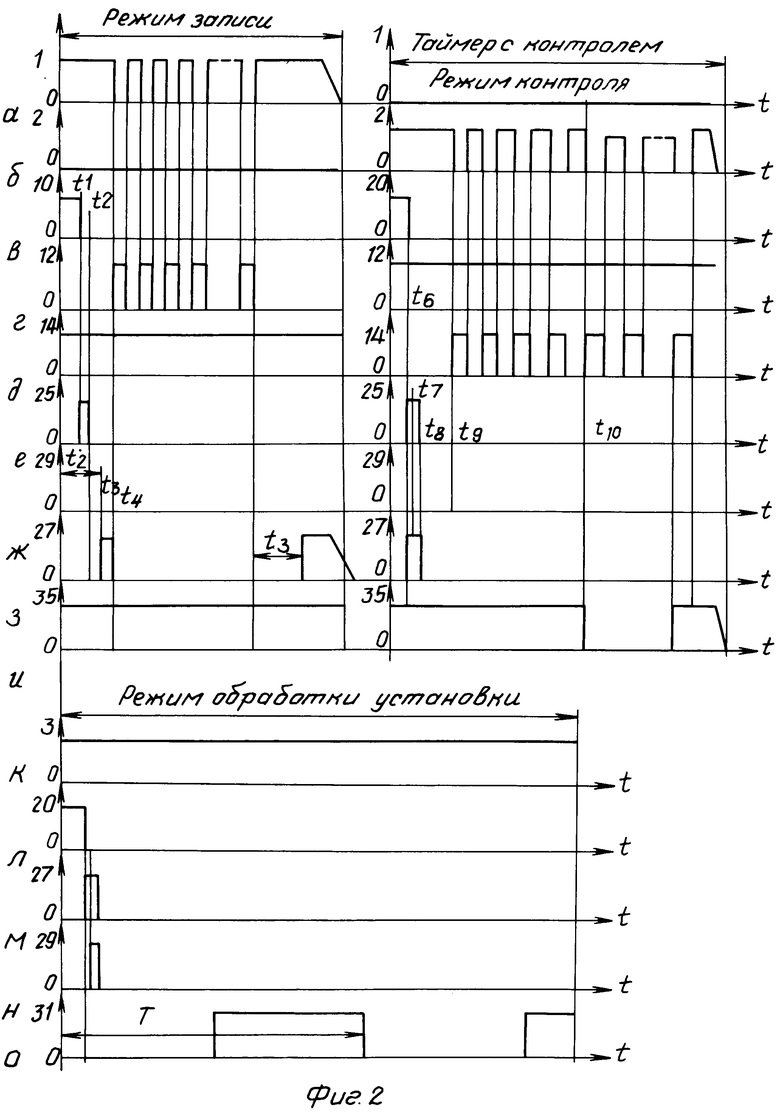

На фиг.1 представлена электрическая схема таймера с контролем; на фиг.2 представлены временные диаграммы его работы. Таймер с контролем содержит первую 1, вторую 2 и третью 3 шины управления. Шина 1 соединена с катодом диода 4 и с анодами диодов 5, 6. Шина 2 соединена с катодом диода 7 и с анодами диодов 8, 9. Шина 3 соединена с анодом диода 10. Анод диода 4 соединен с анодом диода 7 и с общей шиной 11 таймера. Катод диода 5 соединен непосредственно с входом формирователя 12 импульсов и через резистор 13 с общей шиной 11. Катод диода 8 соединен непосредственно с входом формирователя 14 импульсов, выходом формирователя 15 импульсов и через резистор 16 с общей шиной 11. Катоды диодов 6, 9, 10 соединены между собой непосредственно и через резистор 17 с входом вторичного источника 18 питания. Вход вторичного источника питания через конденсатор 19 соединен с общей шиной 11. Выход вторичного источника 18 питания соединен с входом схемы 20 начальной установки и с входами питания формирователей 12, 14, 15 импульсов. Выход формирователя 12 импульсов соединен с входом формирователя 21 импульсов, с первым входом элемента И 22 и с вторым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 23. Выход формирователя 14 импульсов соединен с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 23. Выход схемы 20 начальной установки соединен с входом формирователя 25 импульсов и с входом обнуления счетчика 26 и в коде Грея. Выход формирователя 21 импульсов соединен с вторым входом элемента И 24, выход которого соединен с первым входом элемента ИЛИ 27. Выход формирователя 25 импульсов соединен с вторым входом элемента И 22 и с тактовым входом триггера 28. Выход элемента И 22 соединен с вторым входом элемента ИЛИ 27 непосредственно и через элемент 29 задержки с входом разрешения считывания блока 30 памяти. Выход элемента ИЛИ 27 соединен с входом разрешения записи блока 30 памяти. Выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 23 соединен с входом обнуления делителя 31 частоты и с первым входом элемента ИЛИ 32. Второй вход элемента ИЛИ 32 соединен с выходом делителя 31 частоты, а выход элемента ИЛИ 32 соединен со счетным входом счетчика 26. Информационный вход делителя 31 частоты соединен с выходом задающего генератора 33. Информационный вход триггера 28 соединен с выходом блока 34 свертки по модулю два, входы которого подключены к соответствующим разрядным выходам счетчика 26. Выход триггера 28 соединен со стробирующим входом дешифратора 35. Входы дешифратора 35 соединены с выходами старших разрядов 36 счетчика 26 и с информационными входами блока 30 памяти, выход дешифратора 35 соединен с входом формирователя 15 импульсов и является выходом таймера. Входы установки в единицу старших разрядов 36 счетчика 26 соединены с соответствующими выходами блока 30 памяти. Старшие разряды 36 и младшие разряды 37 соединены последовательно и образуют единичный счетчик 26 в коде Грея, счетный вход младших разрядов 37 является счетным входом счетчика 26. Выход вторичного источника 18 питания подключен к плюсовым выводам питания формирователей 21, 25 импульсов, элементов И 22, 24, элементов ИЛИ 27, 32, элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 23, элемента 29 задержки, задающего генератора 33, делителя 31 частоты, триггера 28, блока 34 свертки, счетчика 26, блока 30 памяти, дешифратора 35 (указанные связи не показаны).

Формирователь 12 импульсов содержит стабилитрон 38, резисторы 39-42, конденсатор 43, p-n-p-транзистор 44. Катод стабилитрона 38 подключен к входу формирователя, анод через последовательно соединенные резисторы 39 и 40 соединен с базой транзистора 44. Точка соединения резисторов 39 и 40 через конденсатор 43 соединена с общей шиной 11 таймера. Эмиттер транзистора 44 непосредственно, а база транзистора 44 через резистор 41 подключены к общей шине 11 таймера. Коллектор транзистора 44 подключен к выходу формирователя 12 непосредственно и через резистор 42 к входу питания формирователя 12.

Формирователь 14 импульсов содержит стабилитрон 45, резисторы 46-49, конденсатор 50, n-p-n-транзистор 51. Катод стабилитрона 45 подключен к входу формирователя 14, анод через последовательно соединенные резисторы 46 и 47 соединен с базой транзистора 51. Точка соединения резисторов 46 и 47 через конденсатор 50 соединена с общей шиной 11 таймера. Эмиттер транзистора 51 непосредственно, а база транзистора 51 через резистор 48 подключены к общей шине 11 таймера. Коллектор транзистора 51 подключен к выходу формирователя 14 непосредственно и через резистор 49 к выходу питания формирователя 14.

Формирователь 15 импульсов содержит n-p-n-транзистора 52, p-n-p-транзистор 53, резисторы 54-58. Вход формирователя 15 через резистор 58 соединен с базой транзистора 53. Эмиттер транзистора 53 непосредственно, а база через резистор 57 соединены с входом питания формирователя 15. Эмиттер транзистора 52 непосредственно, а коллектор транзистора 53 через резистор 56 соединены с общей шиной 11 таймера. Коллектор транзистора 53 через резистор 55 соединен с базой транзистора 52. Коллектор транзистора 52 через резистор 54 соединен с выходом формирователя 15.

В качестве вторичного источника 18 питания может быть использован параметрический или компенсационный стабилизатор напряжения постоянного тока, обеспечивающий требуемые для выбранной элементной базы параметры выходного напряжения: ток нагрузки, стабильность, величину пульсаций. В примере конкретного выполнения с учетом выполнения схем и блоков таймера на базе микросхем серии 564 был использован простейший параметрический стабилизатор напряжения (Вересов Г.Н. Смуряков Ю.Л. Стабилизированные источники питания радиоаппаратуры. М. Энергия, 1978, с.53, рис.2,8 б).

Схема 20 начальной установки выполнена в соответствии с описанной в авт. св. СССР N 819964, кл. Н 03 К 21/32, опублик. 1981. Могут быть использованы другие схемы начальной установки с использованием как элементов интегральных микросхем, так и дискретных полевых и биполярных транзисторов, обеспечивающие формирование импульса при появлении напряжения питания на их входе, длительность импульса должна обеспечивать начальную установку всех триггерных устройств таймера.

Логические элементы, схемы и блоки таймера выполнены на микросхемах 564 серии. В составе формирователей 12, 14, 15, вторичного источника 18 в качестве n-p-n-транзисторов использованы матрицы 1НТ251, в качестве p-n-p-транзистора матрица 2ТС622А. В качестве диодов 4-10 использованы диоды 2Д510 А. В качестве стабилитронов 38, 45 использованы стабилитроны 2С211Ц. Опорный стабилитрон в составе вторичного источника 18 стабилитpон 2С175Ц. В качестве элементов памяти блока 30 использованы трансформаторы на базе сердечников из сплава 77 НМЦ (типоразмер М2,5-3/2,5-45), обмотка записи имеет 70 витков, обмотка считывания 210 витков. В качестве других пассивных элементов таймера использованы резисторы типа С2-33, конденсаторы типа К210-17.

Таймер с контролем работает следующим образом.

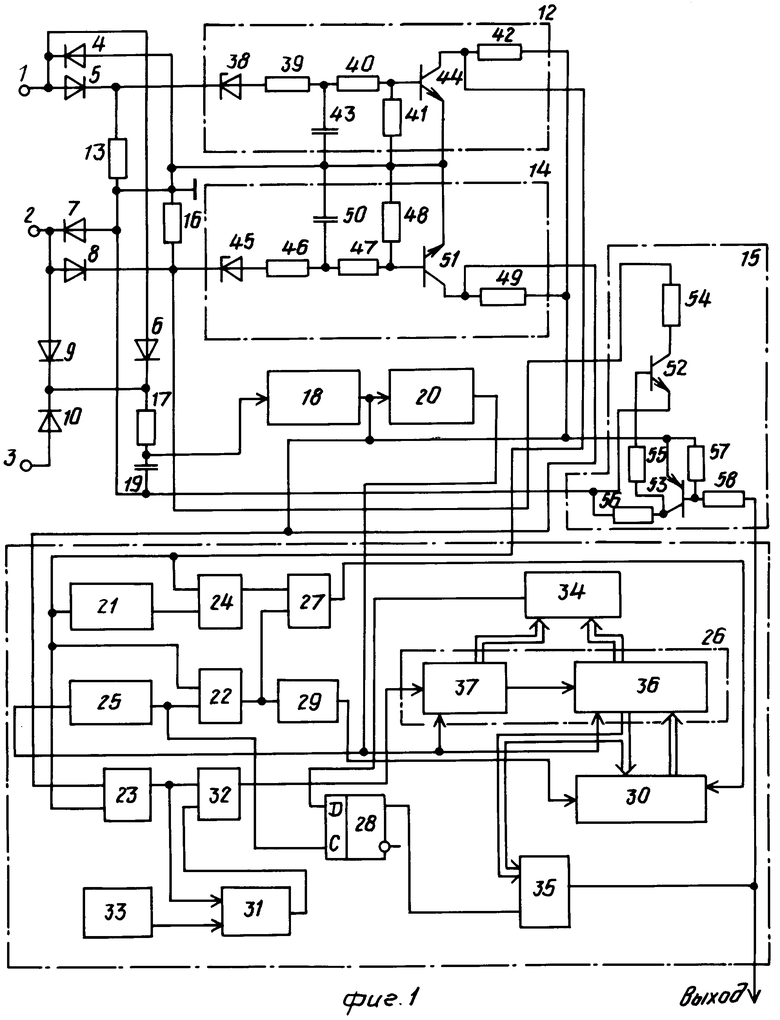

В режиме записи кода установки сигналы управления подаются по шине 1 относительно шины 2 (фиг.2 а, б). На шине 3 сигналы отсутствуют. Под действием указанных сигналов протекает ток через диоды 5, 7, резистор 13, при этом на резисторе 13 относительно общей шины 11 таймера выделяются импульсы напряжения, имеющие ту же фазу, что и сигналы на шине 1. После селекции и нормирования элементами формирователя 12 (стабилитрон 38, конденсатор 43, транзистор 44, резисторы 39-42) инвертиpованные сигналы управления поступают на входы формирователя 21, элемента И 22, элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 23 (фиг.2 г).

Питание формирователя 12 и двух элементов схем и блоков таймера осуществляется с выхода источника 18, запитываемого в этом режиме через диоды 6, 7 и элементы 17, 19 фильтра. Инерционность фильтра выбрана такой, чтобы во время перерывов питания на шине 1 (перерыв является кодовым импульсом) на входе источника 18 напряжение питания не выходило за допустимую нижнюю границу.

Импульс начальной установки, формируемый на выходе схемы 20 (фиг.2 в), обеспечивает приведение в исходное состояние триггерных структур счетчика 26. Импульс, формируемый по заднему фронту импульса начальной установки на выходе формирователя 25 (фиг.2 е), осуществляет запись в триггер 28 состояние выхода блока 34 свертки, при этом, если нечетное число разрядов счетчика 26 не установилось в исходное состояние, триггер 28 переключается в состояние логической "1". Если все разряды счетчика 26 установились в исходное состояние, триггер 28 устанавливается в состояние логического "0". Импульс с выхода формирователя 25 через элемент И 22, не проходит, так как на втором входе элемента И 22 в рассматриваемом интервале времени (t1-t2) присутствует сигнал логического "0" с выхода формирователя 12, отсутствует сигнал разрешения считывания на выходе элемента 29 задержки (фиг.2 ж).

Формируемый на выходе формирователя 21 сигнал записи с задержкой t3 поступает на вход элемента И 24, поскольку элемент И 24 по второму входу открыт (на выходе формирователя 14 потенциал логической "1"), сигнал записи через элемент ИЛИ 27 поступает на вход разрешения записи блока 30 памяти (фиг.2, интервал времени t3-t4). В результате в блок 30 памяти записывается нулевое состояние старших разрядов 36 счетчика 26.

Необходимо отметить, что обмен информацией между старшими разрядами 36 счетчика 26 и блоком 30 памяти осуществляется следующим образом. Триггерные устройства старших разрядов 36 счетчика 26 выполнены с возможностью включения в цепь их обратной связи интегрирующих RC-цепей, инерционность триггерных устройств с включенными в цепь обратной связи интегрирующими элементами больше, чем время перемагничивания магнитных элементов блока 30 памяти. В режиме записи информации, когда поступает только сигнал по входу разрешения записи блока 30, осуществляется подключение выходов старших разрядов 36 к обмоткам записи блока 30, поскольку триггерные устройства имеют в цепи обратной связи интегрирующие элементы. За время перемагничивания сердечников эти элементы не успевают изменить свое состояние, поэтому в результате сердечники блока 30 воспринимают состояние триггерных устройств. В режиме, когда необходимо осуществить считывание информации из блока 30 в счетчик 26, вместе с сигналом разрешения записи подается сигнал разрешения считывания. При этом интегрирующие элементы в цепи обратной связи триггерных устройств старших разрядов 36 отключаются, инерционность триггерных устройств становится меньше, чем время перемагничивания магнитных элементов блока 30, в этом случае триггерные устройства воспринимают состояние магнитных сердечников. Для исключения ложного переключения триггерных устройств под действием сигнала помехи, формирующегося на выходе обмоток считывания за счет непрямоугольности петли гистерезиса сердечников, сигнал разрешения считывания должен быть задержан относительно начала сигнала разрешения записи.

Кодовые импульсы, формируемые на выходе формирователя 12, начиная с момента времени t4 (фиг.2 г), через элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 23 и ИЛИ 32 проходят на счетный вход счетчика 26. Разряды счетчика 26 переключаются каждым кодовым сигналом в соответствии с логикой кода Грея: нечетными тактовыми сигналами переключается первый (самый младший) разряд счетчика 26, четными разряд, следующий за самым младшим разрядом с состоянием логической "1". Количество кодовых импульсов в режиме записи соответствует дополнительному коду задаваемой установки, т.е. количество тактовых сигналов (n), которое необходимо подать в счетчик после записи кода до переполнения счетчика (до появления сигнала на выходе дешифратора 35) и величина заданной уставки (tу) связаны соотношением

tу=Т˙n, (1) где Т период тактовых сигналов на входе счетчика 26. В режиме контроля заданной установки период Т равен периоду кодовых импульсов на выходе формирователя 14, в режиме отработки установки период Т равен периоду сигналов на выходе делителя 31 частоты.

В режиме записи кратковременная разблокировка делителя 31 по входу обнуления на время кодового импульса не приводит к появлению импульсов на выходе делителя 31, так как длительность кодового импульса выбирается меньше, чем полупериод импульсной последовательности на выходе делителя 31 частоты. По окончании кодовой последовательности (фиг.2 г, момент времени t5) формирователь 21 с задержкой tз формирует повторный сигнал записи (фиг.2 з), по которому код, записанный в старшие разряды 36 счетчика 26, будет переписан в элементы магнитной памяти блока 30. На этом цикл записи заканчивается, сигналы управления с шины 1 таймера снимаются с задержкой, обеспечиваемой размером фильтрового конденсатора 19, снимается напряжение с источника 18 и со всех остальных элементов, схем и блоков таймера.

С учетом того, что в блок 30 памяти записывается информация только из старших разрядов счетчика 26, а информация, поступившая в режиме записи в младшие разряды 37 счетчика 26 в дальнейшем не используются, появляется возможность допустить искажение кодовой последовательности импульсами помехи. При выборе номинального числа кодовых импульсов в середине зоны нечувствительности старших разрядов (2m-1-1, где m число младших разрядов 37) можно реализовать отсутствие ошибок при записи как в случае появления в кодовой последовательности 2m-1 "лишних" импульсов, так и в случае пропадания (2m-1-1) импульсов в посылке. Необходимо также отметить, что номинальные числа кодовых импульсов для всего ряда уставок должны выбираться так, чтобы коды чисел, записываемых в старшие разряды, были четными. Для выполнения этого условия номинальные значения числа кодовых импульсов должны отстоять одно от другого на величину 2m+1. Это позволяет, во-первых, при выбранной организации счетчика получить постоянную дискретность ряда уставок, во-вторых, организовать обнаружение ошибок, связанных с искажением числа кодовых импульсов помехами за пределами зоны нечувствительности и тем самым значительно повысить достоверность контроля.

В режиме контроля заданной таймеру уставки сигналы управления подаются по шине 2 управления относительно шины 1 (фиг.2 а, б). На шине 3 сигналы отсутствуют. Под действием указанных сигналов протекает ток через диоды 5, 8, резистор 16, при этом на резисторе 16 относительно общей шины 11 таймера выделяются импульсы напряжения, поступающие на вход формирователя 14. На выходе формирователя 12 в режиме контроля сохраняется высокий потенциал (логическая "1"). Так же, как и в режиме записи, осуществляется запитка элементов, схем и блоков таймера через источник 18, при этом напряжение на его вход поступает через диоды 4, 9. На выходе схемы 20 начальной установки формируется импульс начальной установки (фиг.2 в, интервал времени 0-t6). На выходе формирователя 25 по заднему фронту импульса начальной установки формируется импульс считывания (фиг. 2 е, интервал времени t6-t8). Поскольку элемент И 22 по первому входу разрешен потенциалом логической "1" с выхода формирователя 12, сигнал считывания поступает на входы элемента ИЛИ 27 и на вход элемента 29 задержки. С выхода элемента ИЛИ 27 сигнал поступает на вход разрешения записи блока 30 памяти (фиг.2 з, интервал времени t6-t8), с выхода элемента 29 сигнал считывания с задержанным фронтом поступает на вход разрушения считывания блока 30 памяти (фиг.2 ж, интервал времени t7-t8). При подаче указанных сигналов в блок 30 памяти осуществляется считывание информации из магнитных элементов блока 30 в соответствующие старшие разряды 36 счетчика 26, причем считывание происходит только в те разряды счетчика, в которых соответствующие им элементы памяти находятся в состоянии логической "1". В результате считывания старшие разряды 36 счетчика 26 находятся в состояниях, соответствующих величине уставки, записанной в предыдущем цикле записи. Сигнал записи на выходе формирователя 21 в указанном режиме не формируется, делитель 31 частоты, как и в режиме записи, заблокирован по входу обнуления импульсным сигналом с выхода элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 23, поэтому сигналы с выхода делителя 31 на вход элемента ИЛИ 32 в указанном режиме не поступают.

Триггер 28, опрашиваемый импульсом считывания с выхода формирователя 25, пеpеключается в состояние, соответствующее выходу блока 34 свертки. Нулевое состояние триггера 28 соответствует четной информации на выходе блока 34, единичное состояние соответствует нечетной информации на выходе блока 34, что сигнализирует об одиночных неисправностях элементов схемы при записи или считывании информации, а также при неустановке в исходное состояние нечетного числа разрядов счетчика 26. Селекция кодовых сигналов, поступающих в таймер в режиме контроля, а также их нормиpование и инверсия осуществляется с помощью элементов формирователя 14 (стабилитрона 45, конденсатора 50, транзистора 51, резисторов 46-49). Кодовые сигналы, поступающие с выхода формирователя 14, начиная с момента времени t9, через элементы ИСЛЮЧАЮЩЕЕ ИЛИ 23 и 32 поступают на счетный вход счетчика 26. Как и в режиме записи, счетчик 26 с приходом каждого кодового сигнала увеличивает на единицу введенный в него код в соответствии с логикой Грея. При переполнении счетчика (момент времени t10) сигнал с выхода дешифратора 35 через формирователь 15 и диод 18 поступает на шину 2 управления в виде подгрузки шины 2 дополнительным током. Дополнительный ток формируется с помощью усилительных каскадов (транзисторов 52, 53, резисторов 54-58). Указанный сигнал используется для сравнения заданной и полученной при контроле уставки и для принятия решения о готовности таймера к переводу в режим отработки Если в процессе считывания информации из блока 30 в счетчик 26 триггер 28 переключается в состояние логической "1", то контрольный сигнал на выходе дешифратора 35 (и на шине 2 управления таймером) не формируется. В режиме контроля так же, как и в режиме записи, схема таймера нечувствительна к искажению кодовых сигналов в диапазоне от минус (2m-1-1) до 2m-1 импульсов от номинального значения, выбранного в середине зоны нечувствительности.

В режиме отработки уставки процессы начального обнуления и считывания информации в таймере осуществляются так же, как и в режиме контроля. Напряжение управления поступает по шине 3 относительно шин 1 и 2, находящихся в этом режиме под нулевым потенциалом (фиг.2 к). Формирователи 12, 14 в указанном режиме не работают. Напряжение на вход источника 18 поступает через диоды 10, 4, 7. Сигналы обнуления и считывания представлены на фиг.2 л, м, н. В триггер 28 так же, как и в режиме контроля, записывается информация об одиночных отказах элементов счетчика 26 и блока 30 памяти в режимах записи, при обнулении счетчика и считывании в него информации. Поскольку в рассматриваемом режиме на выходах формирователей 12, 14 присутствует потенциал логической "1", на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 23 и на входе обнуления делителя 31 частоты устанавливается сигнал логического "0". Сигналы, поступающие на информационный вход делителя 31 с задающего генератора 33, делятся до тактовой частоты, соответствующей величине уставки (см. формулу (1)). Тактовые сигналы с выхода делителя (диаграмма О) через элемент ИЛИ 32 поступают на счетный вход счетчика 26. Через заданное время отработки (при условии, что триггер 28 находится в состоянии логического "0") на выходе дешифратора 35 и на выходе таймера формируется выходная исполнительная команда.

Таким образом, из описания работы таймера с контролем видно, что за счет организации управления таймером в режимах записи и контроля по двухпроводной линии (шины 1 и 2 управления), организации питания таймера и организации контрольного выхода таймера с использованием указанной двухпроводной линии, организации приведения таймера в исходное состояние при формировании фронта напряжения питания число шин управления таймером уменьшено с шести до трех. На практике это означает, что вместо семижильного кабеля управления может быть использован четырехжильный кабель. При использовании, например, для указанных целей кабеля тира КПЛП (сечение жилы 0,2 мм2) выигрыш в весовой характеристике кабеля на один погонный километр составляет 11,2 кг. При использовании кабеля КПЛП с сечением жилы 0,5 мм2 выигрыш по весу кабеля составляет 21 кг на погонный километр длины. Это обстоятельство позволяет уменьшить стоимость аппаратуры, повысить ее эксплуатационные характеристики.

На предприятии был изготовлен и испытан лабораторный макет таймера с контролем. Частота кодовых сигналов управления таймером была выбрана 500 кГц, амплитуда сигналов 24 В. Выходное напряжение питания источника 7 В. Длительность сигнала начальной установки 10 мс, длительность сигнала считывания на выходе формирователя 25-0,5 мс, задержки фронта сигнала считывания на выходе элемента 29 задержки 4 мкс. Частота задающего генератора 33-32758 Гц, коэффициент пересчета делителя 31-1024, количество младших разрядов 37 счетчика 26 (m) 2, количество старших разрядов 36 счетчика 26 3.

В процессе испытаний контролировалась работоспособность таймера в диапазоне температур минус 50 плюс 50оС. Проведенные испытания показали осуществимость заявляемого объекта и подтвердили его практическую ценность.

| название | год | авторы | номер документа |

|---|---|---|---|

| ТАЙМЕР С КОНТРОЛЕМ | 1991 |

|

SU1832976A1 |

| СЧЕТНОЕ УСТРОЙСТВО | 1992 |

|

RU2040113C1 |

| ШИФРАТОР | 1989 |

|

RU2033691C1 |

| КОММУТАТОР ДЛЯ УПРАВЛЕНИЯ ШАГОВЫМ ДВИГАТЕЛЕМ | 1995 |

|

RU2103716C1 |

| ПОМЕХОУСТОЙЧИВЫЙ СЧЕТЧИК ИМПУЛЬСОВ | 1991 |

|

RU2038692C1 |

| ФОРМИРОВАТЕЛЬ ИМПУЛЬСОВ | 1991 |

|

RU2036550C1 |

| УСТРОЙСТВО ДЛЯ МНОГОКАНАЛЬНОГО ИЗМЕРЕНИЯ ВРЕМЕННЫХ ПАРАМЕТРОВ | 1999 |

|

RU2180450C2 |

| МНОГОКАНАЛЬНОЕ УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ СРЕДНЕКВАДРАТИЧЕСКОГО ЗНАЧЕНИЯ НАПРЯЖЕНИЯ | 2000 |

|

RU2198410C2 |

| ЯЧЕЙКА ПАМЯТИ | 2001 |

|

RU2214037C2 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ЭЛЕКТРОННЫМ ЗАМКОМ | 2002 |

|

RU2209909C1 |

Изобретение относится к автоматике и импульсной технике. Цель изобретения - уменьшение числа шин управления. Таймер с контролем содержит первую 1, вторую 2 и третью 3 шины управления. Шина 1 соединена с катодом диода 4 и с анодами диодов 5, 6, шина 2 с катодом диода 7 и с анодами диодов 8, 9, шина 3 с анодом диода 10. Анод диода 4 соединен с анодом диода 7 и с общей шиной 11 таймера. Катод диода 5 соединен непосредственно с входом формирователя 12 импульсов и через резистор 13 с общей шиной 11. Катод диода 8 соединен непосредственно с входом формирователя 14 импульсов, выходом формирователя 15 импульсов и через резистор 16 с общей шиной 11. Катоды диодов 6, 9, 10 соединены между собой непосредственно и через резистор 17 с входом вторичного источника 18 питания. Вход вторичного источника питания через конденсатор 19 соединен с общей шиной 11. Выход вторичного источника 18 питания соединен с входом схемы 20 начальной установки и с входами питания формирователей 12, 14, 15 импульсов. Выход формирователя 12 импульсов соединен с входом формирователя 21 импульсов, с первым входом элемента И 22 и с вторым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 23. Выход формирователя 14 импульсов соединен с первым входом элемента И 24 и с вторым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 4 23. Выход схемы 20 начальной установки соединен с входом формирователя 25 импульсов и с входом обнуления счетчика 26 в коде Грея. Выход формирователя 21 импульсов соединен с вторым входом элемента И 24, выход которого соединен с первым входом элемента ИЛИ 27. Выход формирователя 25 импульсов соединен с вторым входом элемента И 22 и с тактовым входом триггера 28. Выход элемента И 22 соединен с вторым входом элемента ИЛИ 27 непосредственно и через элемент 29 задержки с входом разрешения считывания блока 30 памяти. Выход элемента ИЛИ 27 соединен с входом разрешения записи блока 30 памяти. Выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 23 соединен с входом обнуления делителя 31 частоты и с первым входом элемента ИЛИ 32. Второй вход элемента ИЛИ 32 соединен с выходом делителя 31 частоты, а выход элемента ИЛИ 32 соединен со счетным входом счетчика 26. Информационный вход делителя 31 частоты соединен с выходом задающего генератора 33. Информационный вход триггера 28 соединен с выходом блока 34 свертки по модулю два, входы которого подключены к соответствующим разрядным выходам счетчика 26. Выход триггера соединен со стробирующим входом дешифратора 35, входы которого соединены с выходами старших разрядов 36 счетчика 26 и с информационными входами блока 30 памяти, а выход соединен с входом формирователя 15 импульсов и является выходом таймера. Входы установки в единицу старших разрядов счетчика соединены с соответствующими выходами блока 30 памяти. 2 ил.

ТАЙМЕР С КОНТРОЛЕМ, содержащий задающий генератор, выход которого соединен с информационным входом делителя частоты, выход которого подключен к первому входу первого элемента ИЛИ, второй вход которого соединен с входом обнуления делителя частоты и с выходом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, первый вход которого подключен к первому входу первого элемента И, второй вход к первому входу второго элемента И и к входу первого формирователя импульсов, выход которого соединен с вторым входом первого элемента И, выход которого подключен к первому входу второго элемента ИЛИ, второй вход которого соединен с входом элемента задержки и с выходом второго элемента И, второй вход которого подключен к выходу второго формирователя импульсов и тактовому входу триггера, выход которого соединен со стробирующим входом дешифратора, информационный вход триггера соединен с выходом блока свертки по модулю два, входы которого подключены к соответствующим разрядным выходам счетчика в коде Грея, счетный вход которого соединен с выходом первого элемента ИЛИ, вход обнуления с входом второго формирователя импульсов, выходы старших разрядов с входами дешифратора и с информационными входами блока памяти, входы установки в единицу старших разрядов счетчика в коде Грея соединены с соответствующими выходами блока памяти, вход разрешения записи которого подключен к выходу второго элемента ИЛИ, вход разрешения считывания к выходу элемента задержки, отличающийся тем, что в него введены три формирователя импульсов, семь диодов, три резистора, конденсатор, вторичный источник питания и узел начальной установки, причем вход третьего формирователя импульсов соединен с катодом первого диода и через первый резистор с анодом второго диода, а выход подключен к второму входу элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, первый вход которого соединен с выходом четвертого формирователя импульсов, вход которого соединен с катодом третьего диода и выходом пятого формирователя импульсов, вход которого соединен с выходом дешифратора, первый вход управления таймера соединен с анодами первого и пятого диодов и с катодом четвертого диода, анод которого соединен через второй резистор с входом четвертого формирователя импульсов, второй вход управления таймера соединен с анодами третьего и шестого диодов и с катодом второго диода, третий вход управления таймера подключен к аноду седьмого диода, катод которого соединен с катодами пятого и шестого диодов и через последовательно соединенные третий резистор и конденсатор с общей шиной и анодами второго и четвертого диодов, вход вторичного источника питания подключен к точке соединения третьего резистора и конденсатора, выход к входу узла начальной установки, выход которой соединен с входом второго формирователя импульсов.

| ТАЙМЕР С КОНТРОЛЕМ | 1986 |

|

SU1505257A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1995-06-19—Публикация

1990-07-17—Подача