Известные бинарно-десятичные пересчетные устройства (декады), работающие по системе 8-f- 1 + 1, состоят из четырех триггеров с прямой и обратной (блокирующей) связями на диодах, причем при счете 10-го импульса срабатывает четвертый каскад и блокируется второй. Блокирование производится по постоянной составляющей без формирования импульсов.

Эти устройства работают устойчиво при разрешающем времени не менее трех миллисекунд. Уменьщение постоянных времени схемных элементов, с целью повыщения временной разрешающей способности, приводит к паразитным явлениям и неустойчивости счета.

С целью устранения этого недостатка известных пересчетных устройств, в предлагаемом пересчетном устройстве осуществлена одновременная блокировка второго и третьего каскадов посредством двойной импульсной обратной связи между анодной ц€пью ч€тв§ртоге каскада и сеточными ц€пями iTOporo и третьего каскадов,

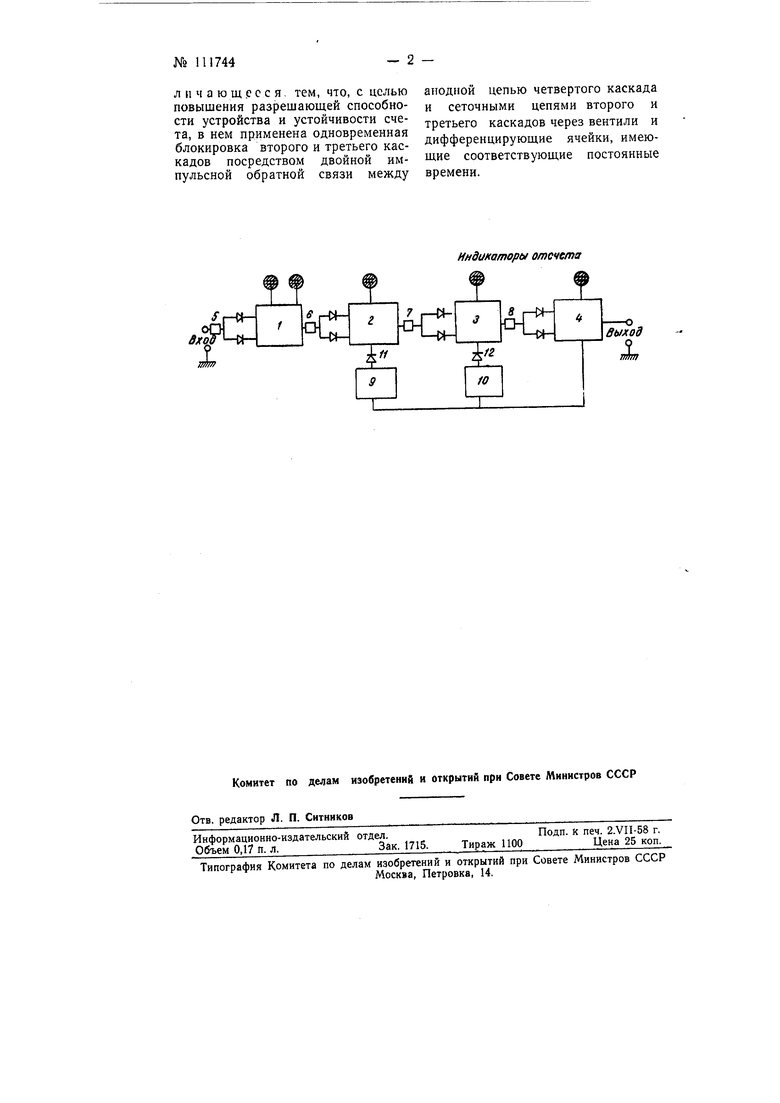

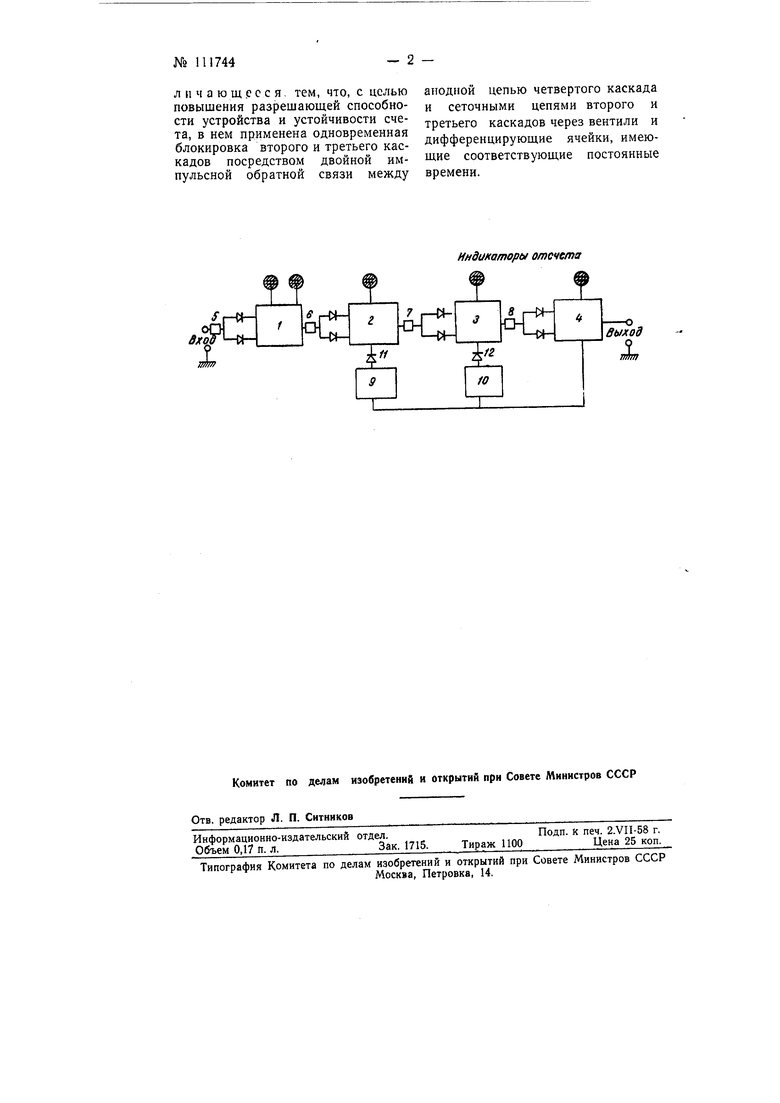

Блок-схема устройства показана на чертеже.

Пересчетное устройство состоит из четырех триггерных каскадов / - 4 с прямой связью при помощи диодов и RC-звеньев 5-8- С целью увеличения устойчивости счета, в устройстве применены две цепи блокирующей импульсной обратной связи - на второй и третий каскады.

Блокирующие импульсы формируются дифференцирующими ячейками 9 1о W малоемкостными полупроводниковыми диодами // и 12. С целью устранения ложных срабатываний пересчетного устройства постоянная времени дифференцирующих ячеек выбирается меньше разрешающего времени декады, но несколько больше постоянной времени прямых междукаскадных переходов 5-6.

Предмет изобретения

Десятичное пересчетное устройстве (декаде) И1 чщтыр§х двончнмх ламповых каскадов, соединенных для счета по системе 8 + 1 -f I, о Т

л II ч а ю щ с с с я. тем, что, с целью повышения разрешающей способности устройства и устойчивости счета, в нем применена одновременная блокировка второго и третьего каскадов посредством двойной импульсной обратной связи между

анодной цепью четвертого каскада и сеточными цепями второго и третьего каскадов через вентили и дифференцирующие ячейки, имеющие соответствующие постоянные времени.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО для КОНТРОЛЯ ПЕРЕДАЧИ ИНФОРМАЦИИ | 1970 |

|

SU269600A1 |

| Кольцевое пересчетное устройство | 1983 |

|

SU1100731A1 |

| Устройство для измерения промежутков времени | 1941 |

|

SU68775A1 |

| Устройство для счета числа импульсов | 1959 |

|

SU125843A1 |

| Устройство для исследования центральной нервной системы | 1988 |

|

SU1810063A1 |

| Счетчик с неразрушающейся информацией | 1989 |

|

SU1651380A1 |

| Устройство регистрации светового изображения | 1986 |

|

SU1415466A1 |

| Автомат для сортирования, например писем | 1959 |

|

SU124724A1 |

| ИМПУЛЬСНЫЙ МОДУЛЯТОР ПОСТОЯННОГО НАПРЯЖЕНИЯ | 1999 |

|

RU2145770C1 |

| УСТРОЙСТВО ДЛЯ НАКОПЛЕНИЯ СПЕКТРОВ ЛиГНИТНОГО РЕЗОНАНСА | 1970 |

|

SU266384A1 |

Авторы

Даты

1958-01-01—Публикация

1955-10-31—Подача