Настоящее изобретение относится к области вычислительной техники и может быть использовано в системах контроля передачи информации.

Известны устройства для контроля передачи информации, содержащие число-имнульскый преобразователь, распределители импульсов, коммутатор, ячейки буферной памяти, реверсивные декады, логическую схему, триггеры, четыре группы схем «И и схемы «ИЛИ.

В этих устройствах принимаемые цифры суммируются и полученная сумма сравнивается с заранее известной контрольной суммой. При передаче и приеме большого массива информации в этих устройствах не обеспечивается достаточно надел ного контроля сравнения накопленной суммы с контрольной суммой.

В предложенном устройстве осуществляется распознавание разрядности принимаемых чисел и производится поразрядное суммирование с учетом переносов. Полученная сумма сравнивается с заранее известной контрольной суммой.

Предложенное устройство отличается от известного тем, чго, с целью повышения достоверности коитроля, выход число-импульсKOIO преобразователя соединен с первыми входами первой группы схем «И, вторые входы которых соединены с соответствующими

выходами первого реверсивного распределителя импульсов, а выходы первой группы схем «И соединены со счетными входа.ми ячеек буферной памяти, выходы ячеек буфериой памяти соединены со входами второй груипы схем «И, управляющие входы которцх соедииены с соответствующими выходами первого реверсивного распределителя импульсов, а выходы второй группы схем «И через схемы «ИЛР

соединены со входами коммутатора, управляющие входы коммутатора соединены с выходами триггеров управления процессом коммутации; выход число-импульсного преобразователя так.же соединен со входами третьей группы схем «li, вторые входы которых соединены с выходом блокирующего триггера, а третьи входы - с соответствующими выходами распределителя импульсов, выходы третьей группы схем «И соединены с первыми раздельными входами реверсивных декад; выход число-импульсного преобразователя также соединен с первыми входами четвертой группы схем «И, вторые входы четвертой группы схем «И соединены с выходом блокирующего триггера, третьи входы - с выходами триггеров распознавания разрядности конгрольной суммы, четвертые входы - с выходом второго реверсивного раснределителя импульсов, а выходы четвертой группы схем «И соединесивных декад, выходы реверсивных декад соединены со входами логической схемы, управляющий вход которой соединен с выходом унравляющего триггера.

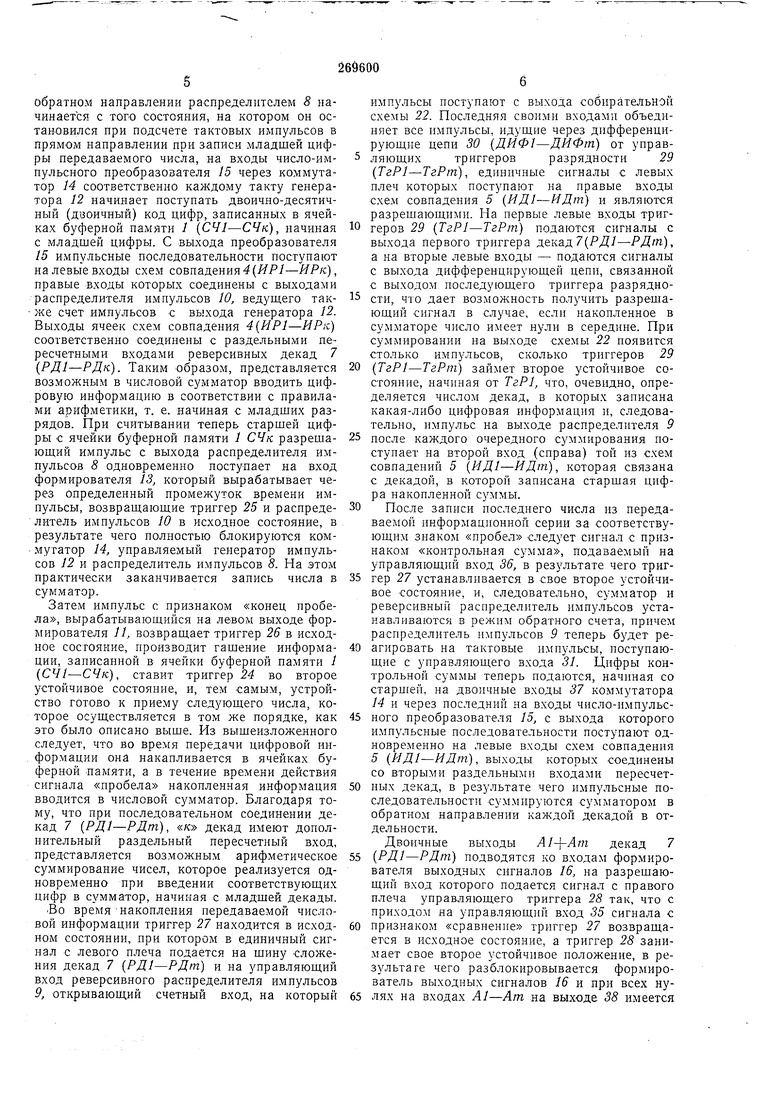

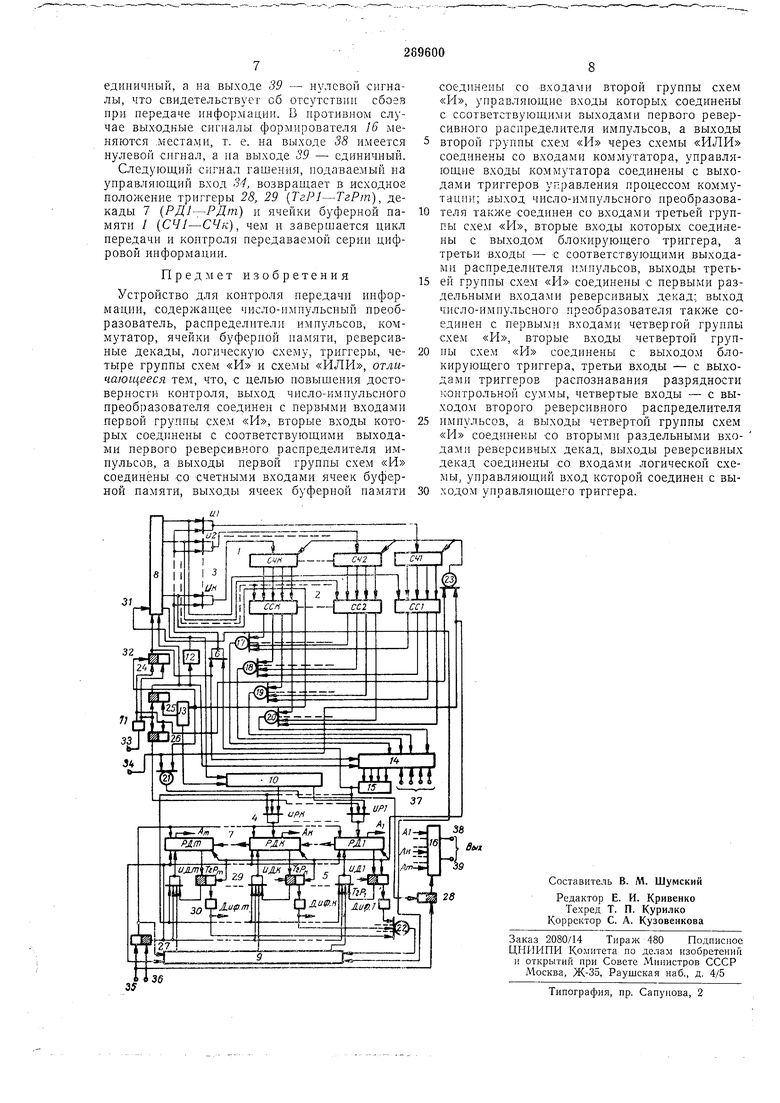

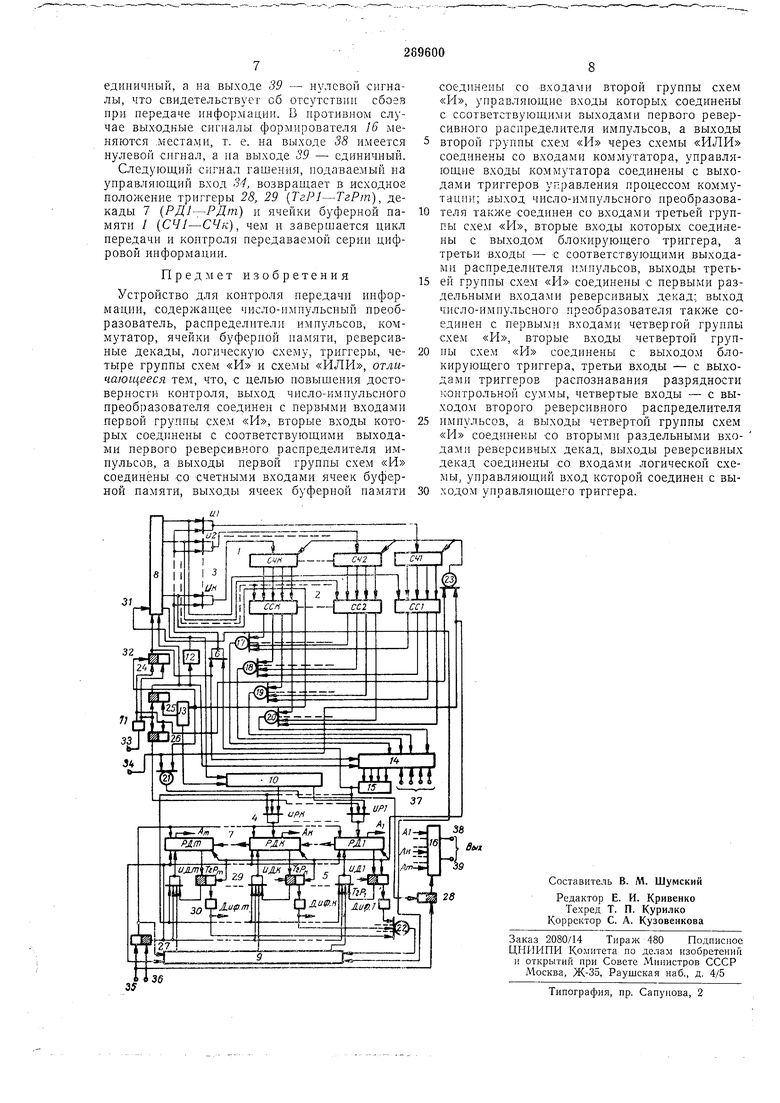

На чертеже изображена функциональная схема предложенного устройства.

Устройство включает в себя ячейки буферной памяти, представляющие собой четырехразрядные двоичные счетчики / (СЧ1-СЧк), схемы совпадения 2 (СС1 - ССк), 3 (И1-Ик), 4 (ИР1-ИРК), 5 (ИД}-ИДт) 6, необходимые для правильной выборки сигналов во времени, последовательно соединенные реверсивные декады 7 (РД1-РДт), имеющие дополнительные раздельные входы и выходы AI-А, реверсивные распределители импульсов 8, 9, распределитель имщльсов Ю, формирователь сигналов с признаком «начало и «конец пробела //, управляемый генератор импульсова 12, формирователь импульсов возврата 13, коммутатор 14, число-импульсный преобразователь 15, формирователь выходных сигналов 16, собирательные схемы 17-23, управляющие триггеры 24-28,

29(ТгР1-ТгРт) и дифференцирующие цепи

30(Диф1-Дифт.

Устройство контроля имеет щесть входов управления 31, 32, 33, 34, 35, 36, четыре двоичных входа для введения цифровой информации 37 и два выхода 38 и 39, на которых формируются сигналы результата сравнения накопленной суммы с контрольной.

Устройство контроля функционирует следующим образом. В исходном состоянии все перечисленные схемы и управляющие триггеры 24-28, 29 (TsPi-ТгРт) находятся в состоянии «О (заштрихованная на чертеже половина триггера проводит). Таким образом, один из входов всех схем совпадений заблокиpOiBa,H нулевым потенциалом с выходом соответствующих управляющих триггеров и распределителей импульсов, в результате чего на их выходах отсутствуют какие-либо сигналы.

Рев-ерсивный распределитель импульсов 8 имеет два управляющих и два счетных входа. На управляющие входы подаются сигналы с левых плеч управляющих триггеров 24 и 25, причем счетные входы блокируются при наличии нулевых сигналов на управляющих входах. Таким образом, реверсивный распределитель импульсов 8 ,в исходном состоянии не реагирует на тактовые импульсы, поступающие на управляющий вход 31. Начало передачи цифровой информации сопровождается подачей сигнала «начало работы на управляющий вход 32, в результате чего триггер 24 переходит в свое второе устойчивое состояние и тем самым разблокировываются левые входы распределителя импульсов 8, схемы совпадения 6 и один из управляющих входов коммутатора 14, обеспечивающий прохождение двоичного кода цифр передаваемой информации на входы число-импульсного преобразователя 15, преобразующего двоичный код цифры в эквивалентное число следующих друг за другом

счетных импульсов. Последние с выхода число-импульсного преобразователя 15 через схему 6 поступают одновременно на первые вхо ды схем совпадений 3 (), вторые входы которых соединены с выходами реверсивного распределителя импульсов 8, на которых поочередно, начиная с первого, появляются разрещающие импульсы в строгом соответствии с тактовыми импульсами. Учитывая, что

каждому передаваемому знаку соответствует тактовый сигнал, число, состоящее из группы цифр, будет записываться в ячейки буферной памяти / (СЧ1-СЧк, начиная со старщего разряда. При этом следует отметить, что здесь

совершенно не играет роли разрядность передаваемых чисел, а важно лишь то, что старшая цифра числа, т. е. старший разряд, записывается в буферную ячейку СЧк, следующая цифра - в буферную ячейку (СЧк-1 и т. д.

Так как каждая ячейка буферной памяти / (СЧ1-СЧк) представляет собой четырехразрядный двоичный счетчик, то с выходов ячеек будет сниматься информация в виде двоичнодесятичного кода, который поступает на входы схем совпадений 2 (СС1-ССк). После передачи младшей цифры числа на управляющий вход 33 подается сигнал «пробел, который является разграничителем передаваемых чисел. Формирователь 11 имеет два выхода,

на правом из них формируется импульс с признаком «начало пробела, а на левом - импульс с признаком «конец пробела. Импульс «начало пробела возвращает триггер 24 в исходное состояние, следовательно, распределитель импульсов 8 перестает реагировать на тактовые импульсы, а схема 6 блокирует сигналы с выхода преобразователя 15.

В то же время импульс «начало пробела переводит триггеры 25 и 26 в их вторые устойчивые состояния, в результате чего разблокируются второй управляющий вход распределителя 8 (при заблокированном первом), управляющий вход управляемого генератора импульсов 12 и второй вход коммутатора 14

(при заблокированном первом ВХОде) и средние входы схем совпадений 4 (ИР.1-ИРк). При тако.м состоянии управляющих триггеров 24, 25, 26 реверсивный распределитель импульсов 8 реагирует не яа тактовые импульсы с

входа управления 31, а на -импульсы с выхода управляемого генератора импульсов. 12, причем подсчет их ведется в обратном направлении. Теперь на входы число-импульсного преобразователя 15 коммутатор 14 пропускает

сигналы с выходов собирательных схем 17, 18, 19, 20, на входы которых поступают сигналы с .выходов схем совпадений 2 (СС1-ССк). На разрешающие входы последних подаются сигналы с выходов распределителя импульсов 8,

следовательно, на каждом такте, определяемом теперь генератором 12, на выходах 17, 18, 19, 20 формируется двоичная информация, равная запасенной информации в какой-либо одной из ячеек буферной памяти (СУ/-СЧк). обратном направлении распределителем 8 начинается с того состояния, на котором он остановился при подсчете тактовых импульсов в прямом направлении при записи младшей цифры передаваемого числа, на входы число-импульсного преобразователя 15 через коммутатор 14 соответственно каждому такту генератора 12 начинает поступать двоично-десятичный (двоичный) код цифр, записанных в ячеиках буферной памяти 1 (СЧ1-СУк), начинаяЮ с младшей цифры. С выхода преобразователя 15 импульсные последовательности поступают на левые входы схем совпадения 4 (ИР1-ИРк, правые входы которых соединены с выходами распределителя импульсов 10, ведущего так- 5 - же счет импульсов с выхода генератора /2. Выходы ячеек схем совпадения 4(ИР1-ИРи соответственно соединены с раздельными пересчетными входами реверсивных декад 7 (РД1-РДк). Таким образом, представляется 20 возможным в числовой сумматор вводить цифровую информацию в соответствии с нравилами арифметики, т. е. начиная с младщих разрядов. При считывании теперь старшей цифры с ячейки буферной памяти 1 СЧк разреща- 25 ющий импульс с выхода распределителя импульсов 8 одновременно поступает на вход формирователя 13, который вырабатывает через определенный промежуток времени импульсы, возвращающие триггер 25 и расиределитель импульсов 10 в исходное состояние, в результате чего полностью блокируются коммутатор 14, управляемый геиератор импульсов 12 и распределитель импульсов 8. На этом практически заканчивается запись числа в 35 сумматор. Затем импульс с признаком «конец нробела, вырабатывающийся на левом выходе формирователя 11, возвращает триггер 26 в исходное состояние, производит гашение информа- 40 ции, зап исанной в ячейки буферной памяти 1 (СЧ1-СЧк), ставит триггер 24 во второе устойчивое состояние, и, тем самым, устройство готово к приему следующего числа, которое осуществляется в том же порядке, как 45 это было описано выше. Из вышеизложенного следует, что во время передачи цифровой информации она накапливается в ячейках буферной памяти, а в течение времени действия сигнала «пробела накопленная информация 50 вводится в числовой сумматор. Благодаря тому, что при последовательном соединении декад 7 (РД1-РДт), «к декад имеют дополнительный раздельный пересчетный вход. представляется возможным арифметическое 55 суммирование чисел, которое реализуется одновременно при введении соответствующих цифр в сумматор, начиная с младшей декады. Во время-накопления передаваемой числовой информации триггер 27 находится в исход- 60 ном состоянии, при котором в единичный сиг30импульсы поступают с выхода собирательной схемы 22. Последняя своими входами объединяет все импульсы, идущие через дифференцирующие цепи 30 (ДИФ1-ДИФт) от управляющих триггеров разрядности 29 (ТгР1-ТгРт), единичные сигналы с левых плеч которых поступают на правые входы схе.м совпадения 5 (ИД1-ИДт) и являются разрещающими. На первые левые входы триггеров 29 (ТгР1-ТгРт) подаются сигналы с выхода первого триггера декад 7(ЯД7-РДт), а на вторые левые входы - подаются сигналы с выхода дифференцирующей цепи, связанной с выходом последующего триггера разрядности, что дает возможность получить разрешающий сигнал в случае, если накопленное в сумматоре число имеет нули в середине. При суммировании на выходе схемы 22 появится столько импульсов, сколько триггеров 29 (ТгР1-ТгРт) займет второе устойчивое состояние, начиная от ТгР1, что, очевидно, определяется числом декад, в которых записана какая-либо цифровая информация и, следовательно, импульс на выходе распределителя 9 после каждого очередного суммирования поступает на второй вход (справа) той из схем совпадений 5 (ИД1-ИДт), которая связана с декадой, в которой записана старшая цифра накопленной суммы. После записи последнего числа из передаваемой информационной серии за соответствующим знаком «пробел следует сигнал с признаком «контрольная сумма, подаваемый на управляющий вход 36, в результате чего триггер 27 устанавливается в свое второе устойчивое состояние, и, следовательно, сумматор и реверсивный распределитель импульсов устанавливаются в режим обратного счета, причем распределитель импульсов 9 теперь будет реагировать на тактовые импульсы, поступающие с управляющего входа 31. Цифры контрольной суммы теперь подаются, начнная со старшей, на двоичные входы 37 коммутатора 14 и через последний на входы число-импульсного преобразователя 15, с выхода которого импульсные последовательности поступают одновременно на левые входы схем совпадения 5 (ИД1-ИДт), выходы которых соединены со вторыми раздельными входами пересчетных декад, в результате чего импульсные последовательности суммируются сумматором в обратном направлении каждой декадой в отдельности. Двоичные выходы декад 7 () подводятся ко входам формирователя выходных сигналов 16, на разрешающии вход которого подается сигнал с правого плеча управляющего триггера 28 так, что с приходом на управляющий в.чод 55 сигнала с признаком «сравнение триггер 27 возвращается в исходное состояние, а триггер 28 занимает свое второе устойчивое положение, в рез льтаге чего разблокировывается формирователь выходных сигналов 16 и при всех ну

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для ввода-вывода информации при обработке физических величин | 1981 |

|

SU966683A1 |

| Анализатор гистограммы отклонений напряжения | 1982 |

|

SU1104530A1 |

| МНОЖИТЕЛЬНОЕ УСТРОЙСТВО | 1967 |

|

SU190658A1 |

| Преобразователь двоичного кода угла в двоично-десятично-шестидесятиричный код градусов,минут,секунд | 1980 |

|

SU960791A1 |

| Многочастотный цифровой фильтр | 1987 |

|

SU1474827A1 |

| Устройство для индикации | 1983 |

|

SU1149306A1 |

| Преобразователь телевизионного стандарта | 1980 |

|

SU1238267A1 |

| Устройство для редактирования | 1982 |

|

SU1117669A1 |

| Устройство для индикации | 1985 |

|

SU1261005A1 |

| Устройство для воспроизведения функций | 1985 |

|

SU1273955A1 |

Даты

1970-01-01—Публикация