мента задержки, выход первого элемента НЕ подключен к выходу первого элемента задержки, выход первого элемента НЕ подключен ко входу второго элемента задержки и к первому входу второго элемента И, второй вход которого подключен к выходу второго элемента задержки, выход пер111вого элемента И подключен к первому входу третьего элемента И, второй вход которого подключен к выходу второго элемента НЕ, вход которого подключен к выходу второго элемента И, выход третьего элемента И подключен к выходу формирователя.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для ввода в микроЭВМ дискретных сигналов | 1990 |

|

SU1786482A1 |

| Однородная вычислительная среда | 1987 |

|

SU1587485A1 |

| Устройство для контроля лоических блоков | 1986 |

|

SU1453409A1 |

| Устройство для выделения центров фигур телевизионного изображения | 1989 |

|

SU1668983A1 |

| Универсальный логический модуль с самоконтролем | 1988 |

|

SU1520504A1 |

| Универсальный логический модуль с самоконтролем | 1988 |

|

SU1644125A1 |

| Универсальный логический модуль | 1985 |

|

SU1312561A1 |

| Устройство для сжатия данных | 1987 |

|

SU1522268A1 |

| Устройство для полиномиального разложения логических функций | 1988 |

|

SU1550507A1 |

| Устройство для вычисления коэффициентов нерекурсивных полосовых фильтров | 1988 |

|

SU1647587A1 |

1. УНИВЕРСАПЬНЬЙ ЛОГИЧЕСКИЙ МОДУЛЬ, содержащий элементы НЕ, причем первый и второй информационные входы модуля подключены ко входам первого и второго элементов НЕ соответственно, отличающийся тем, что, с целью расширения области использования за счет возможности реализации всех логических функций N переменных, модуль дополнительно содержит элементы НЕ, блоки разложения и выходной формирователь сигнала, причем каждый блок разложения логической функции содержит два элемента И и элемент ИЛИ, входы которого подключены к выходам элементов И этого блока разложения соответственно, входы первого элемента И каждого блока разложения подключены к пер-, вому информационному и первому настроечному входам этого блока разложения соответственно, входы второго элемента И каждого блока разложения подключены к второму информационному и второму настроечному входам данного блока разложения соответственно, выход блока разложения первой группы подключен к входу выходного формирователя сигнала, выход которого является выходом МОдуля, информационные входы блока разложения первой подключены к входу и выходу первого элемента НЕ соответственно, настроечные входы блока разложения первой группы подключены к выходам блоков разложения второй группы соответственно, информационные входы блоков разложения 1-й группы С i 2, ...,N-1, где N- количество информационных входов модуля) подключены к входу и выходу i-ro элемента НЕ соответственно, настроечные входы j-ro бло(Л ка разложения i-й группы ( j 1, ..., 2 ) подключены к выходам

1

Изобретение относится к вычислительной технике и может быть использовано при построении блоков цифровых вычислительных машин, а также блоков систем автоматики и управляюnpix систем.

Известен многофункциональный логический модуль, содержащий два элемента НЕ, четыре элемента И, элемент ИЛИ.. Каждый элемент И реализует одну из четырех конституэнт единицы, которые возможны для функций от двух переменных. Срабатывание элементов И происходит при наличии соответствующего разрешающего сигнала настройки. На элементе ИЛИ происходит объединение сигналов конституэнт единиць LI

Недостатком модуля является его функциональная узость (возможность .реализации только переключательной функции от двух переменных).

Кроме того, в схеме модуля возможны гонки сигналов из-за наличия; задержек в реальных элементах.

Наиболее близким к предлагаемому является универсальный логический модуль, содержащий три элемента И, два элемента ИЛИ и два элемента НЕ и имею1ций два информационных входа, два настроечных входа и два выхода, причем первый информационный вход подключен к первым входам первого и второго элементов И и к входу первого элемента НЕ, выход которого подключен к первому входу третьего элемента И, второй вход которого подключен к второму информационному ходу модуля, к второму входу первого элемента И и к входз второго элемента НЕ, выход которого подключен к второму входу второго элемента И, третий вход которого подклю чен к nepBONiy настроечному входу

модуля, второй настроечный вход которого подключен к третьему входу первого элемента И, выход которого подключен к -первым входам первого и второго элементов ИЛИ, вторые входы которых подключены к выходу второго элемента И, выход третьего элемента И подключен к третьему входу второго элемента ИЛИ, выходы первого и второго элементов ИЛИ подключены к выходам модуля соответственнои

Недостатком модуля является ограниченность класса реализуемых функций от двух переменных для каждого из выходов. Кроме того, два настроечных входа позволяют настраивать модуль только на четыре из шестнадцати функций от двух переменных, что приводит к дополнительным затратам оборудования при реализации переключательных функций в базисе четырех функций, реализуемых модулем. При определенных значениях сигналов на настроечных входах и смене значения сигнала на информационном входе возможно прохождение на второй выход модуля ложного сигнала вследствие гонок.

Цель изобретения - расширение области использования за счет реализации всех логических функций переменных.

Поставленная цель достигается тем, что модуль, содержащий элементы НЕ, причем первый и второй информационные входы модуля подключены к входам первого и второго элементов НЕ соответственно, дополнительно содержит элементы НЕ, блоки разложения и выходной формирователь сигнала, причем каждый блок разложения содержит два элемента И и

3

.элемент ИЛИ, входы которого подключены к выходам элементов И этого блока разложения соответственно, входы первого элемента И каждого блока разложения подключены к первому информационному и первому настроечному входам, этого блока разложения соответственно, входы второго элемента И каждого блока разложения подключены ко второму информационному и второму настроечному входам данного блока разложения соответственно, выход блока разложения первой группы подключен к входу выходного формирователя сигналов, выход которого является выходом модуля, информационные входы блока разложения первой группы подключены ко входу и выходу первого элемента НЕ соответственно, настроечные входы блока разложения первой группы подключены к выходам блоков разложения второй группы соответственно, информационные входы блоков разложения i-й группы ( t 2, ..., N-1) подключены ко входу и выходу i-ro элемента НЕ соответственно, настроечные входы j-ro блока разложения i-ой группы (J 1, ...-2) подключены к выходам (2j-1)-ro и 2j-ro блоков разложения ( 1 + О-ой группы соответс венно, информационные входы блоков разложения N-ой группы подключены ко входу и выходу N-ro элемента НЕ соответственно, настроечные входы К-го блока разложения N-ой группы ( k 12 ) подключены к (2К. -1)-му и 2k -му настроечном входам модуля соответственно, входы элементов НЕ с третьего по N-й подключены к соответствующим информационным входам модуля.

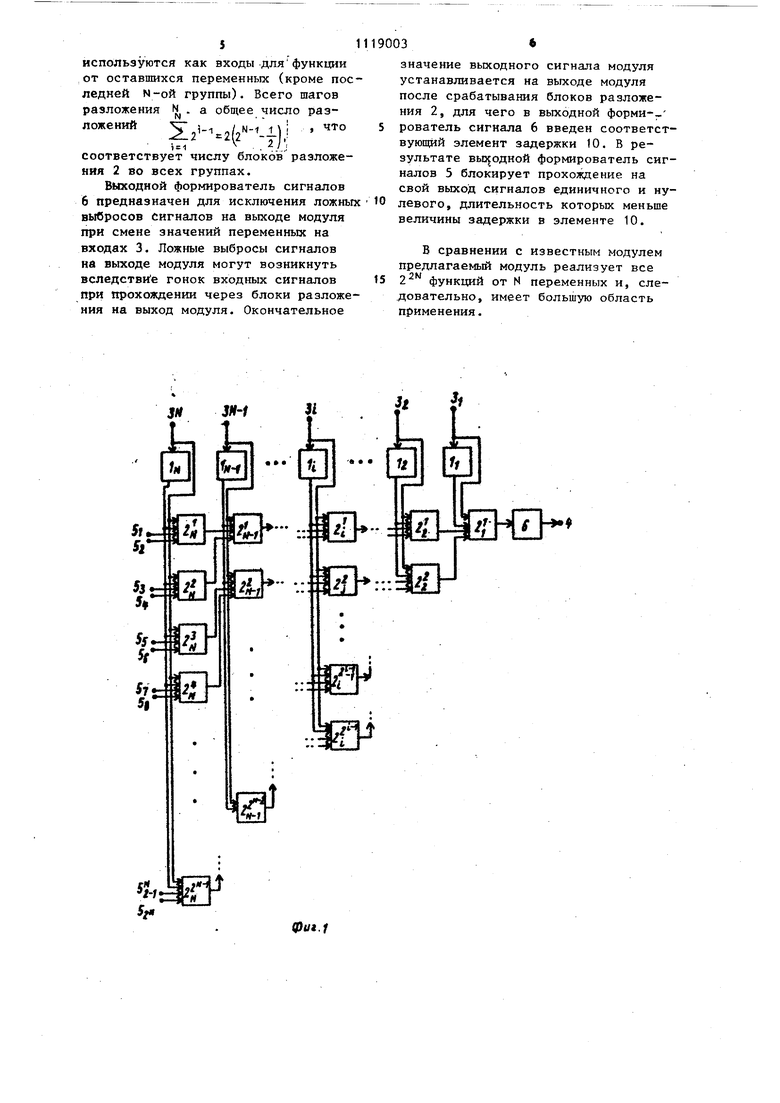

Выходной формирователь сигнала содержит элементы И, НЕ и задержки причем вход формирователя подключен ко входам первого элемента НЕ и первого элемента задержки и первому входу первого элемента И второй вход которого подключен к выходу первого элемента задержки, выход первого элемента НЕ подключен ко входу второго элемента задержки и liJiepBOMy входу второго элемента И, второй вход которого подключен к выходу второго элемента задержки выход первого элемента подключен к первому входу третьего элемента И, второй вход которого подключен

190034

к выходу второго элемента НЕ, вход которого подключен к выходу второго элемента И, выход третьего элемента И подключен к выходу формирователя .

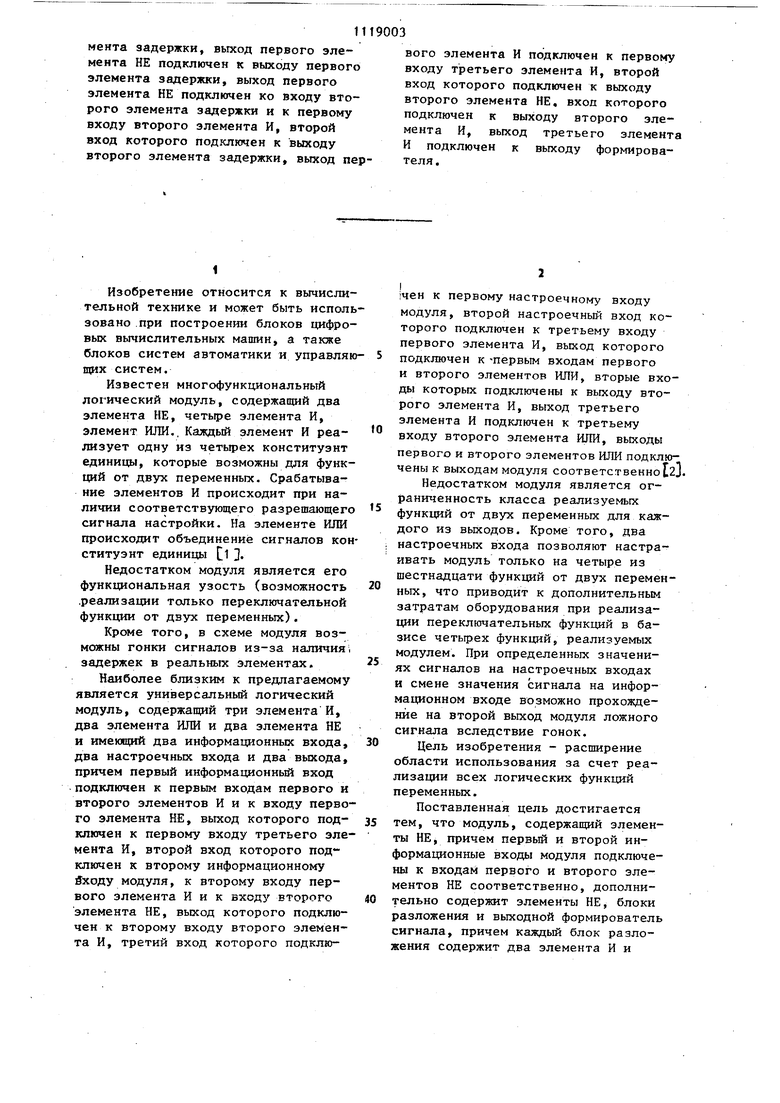

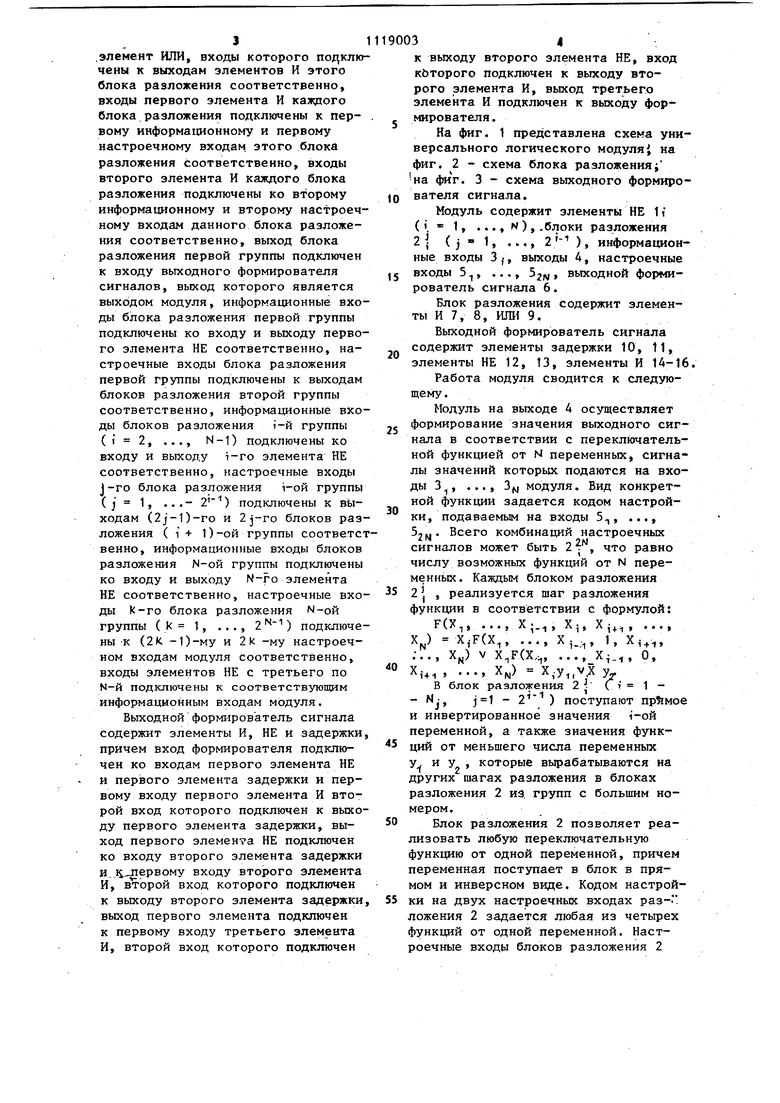

На фиг. 1 представлена схема универсального логического модуляi на фиг. 2 - схема блока разложения на фиг. 3 - схема выходного формироJO вателя сигнала.

Модуль содержит элементы НЕ i ( . 1, ..., N ) , .блоки разложения 2j ( j 1, ..., Z ), информационные входы 3(, выходы 4, настроечные J5 входы 5, ..., 5, выходной формирователь сигнала 6.

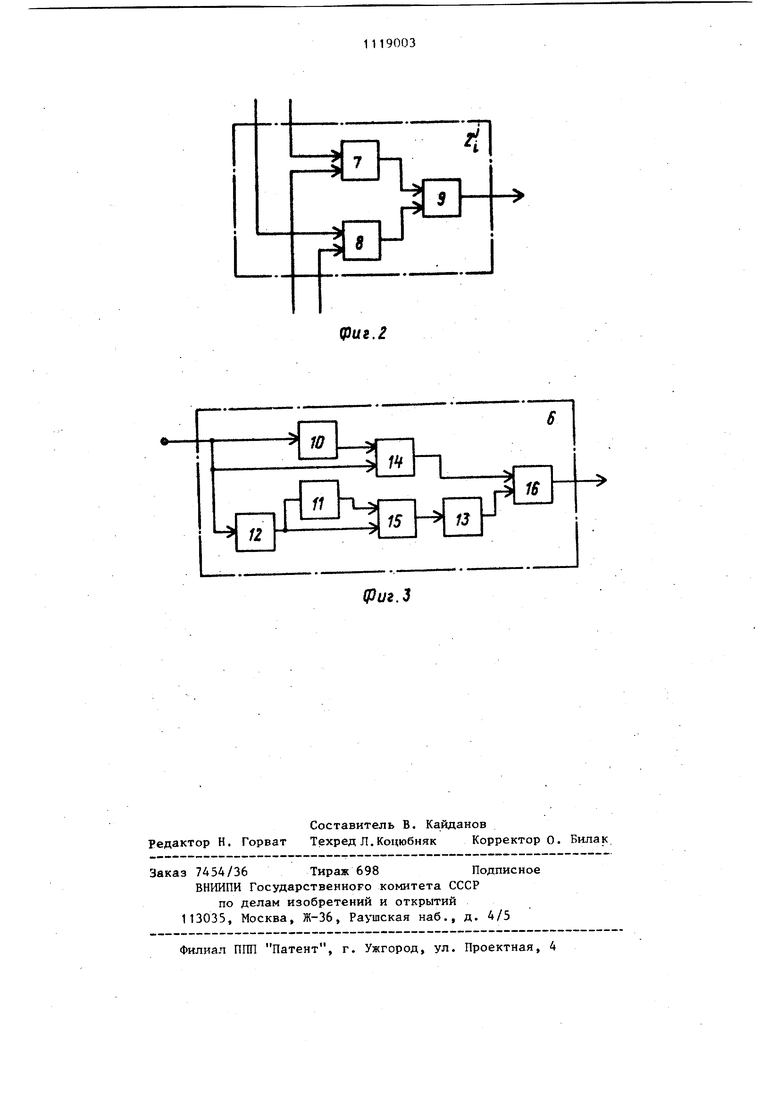

Блок разложения содержит элементы И 7, 8, ИЛИ 9.

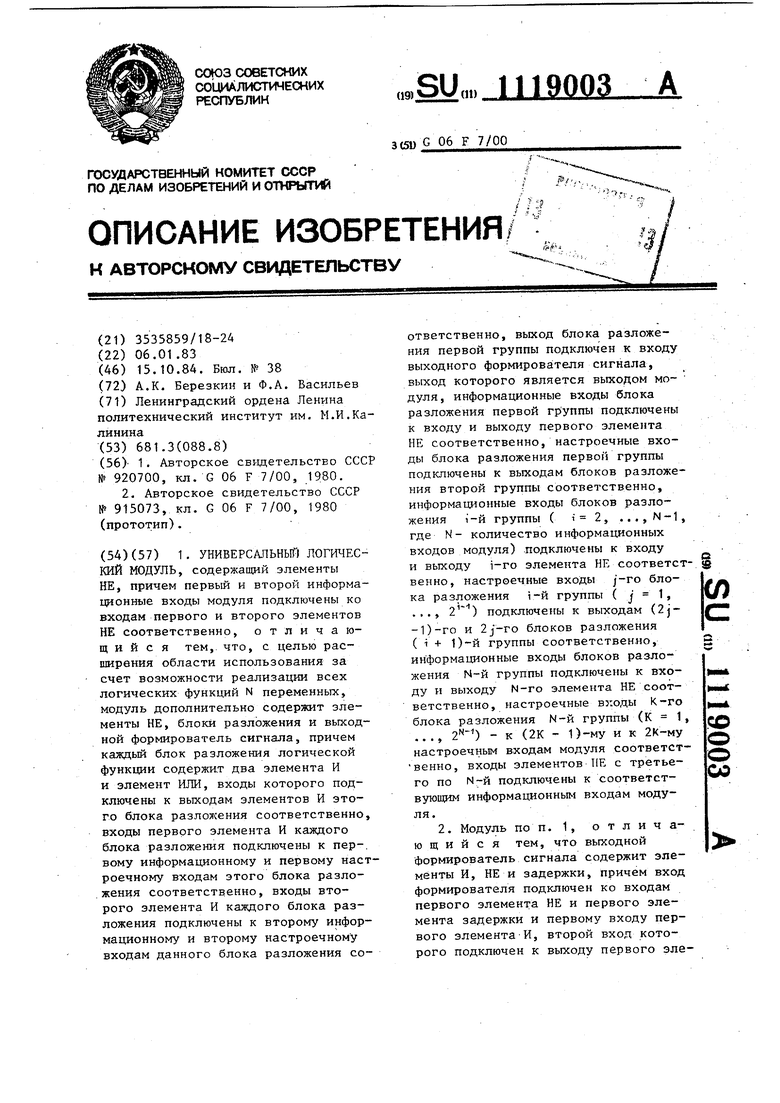

Выходной формирователь сигнала содержит элементы задержки 10, 11, элементы НЕ 12, 13, элементы И 14-16.

Работа модуля сводится к следующему.

Модуль на выходе 4 осуществляет , формирование значения выходного сигнала в соответствии с переклкгчательной функцией от М переменных, сигналы значений которьрс подаются на входы 3, ..., 3 модуля. Вид конкретной функции задается кодом настройки, подаваемым на входы 5, ..., 2ц- Всего комбинаций настроечных сигналов может быть , что равно числу возможных функций от N переменных. Каждым блоком разложения 35 2 , реализуется шаг разложения функции в соответствии с формулой:

F(X,...,X., Xj, ,, ...,

N )1 i-.i i + 1 ... I ы 1 i-i

0 X,,,, ..., Х) X.y.vX у

,.,.- У г ад 2 Ci

1 В блок разложения

j 2 ) поступают прямое и инвертированное значения i-ой переменной, а также значения функ ций от меньшего числа переменных у, и у , которые вырабатываются на других шагах разложения в блоках разложения 2 из. групп с большим номером.

50 Блок разложения 2 позволяет реализовать любую переключательную функцию от одной переменной, причем переменная поступает в блок в прямом и инверсном виде. Кодом настрой55 ки на двух настроечных входах раз-, ложения 2 задается любая из четьфех функций от одной переменной. Настроечные входы блоков разложения 2 5 используются как входы дляфункции от оставшихся переменных (кроме пос ледней N-ой группы). Всего шагов разложения N . а общее число разложений - , / N-1 1 ; , что 5:2-.2() . /.J соответствует числу блоков разложения 2 во всех группах. Выходной формирователь сигналов б предназначен для исключения ложны выбросов сигналов на выходе модуля при смене значений переменных на входах 3. Ложные выбросы сигналов на выходе модуля могут возникнуть вследствие гонок входных сигналов при прохождении через блоки разложе ния на выход модуля. Окончательное

ЗИ ЗН-1

РУ« /

h J

3значение выходного сигнала модуля устанавливается на выходе модуля после срабатывания блоков разложения 2, для чего в выходной форми-рователь сигнала 6 введен соответствующий элемент задержки 10. В результате выз одной формирователь сигналов 5 блокирует прохождение на свой выход сигналов единичного и нулевого, длительность которых меньше величины задержки в элементе 10. В сравнении с известным модулем предлагаемый модуль реализует все 2 функций от N переменных и, следовательно, имеет большую область применения.

фиг. 2

(pui.3

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Многофункциональный логический модуль | 1980 |

|

SU920700A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельство СССР № 915073, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-10-15—Публикация

1983-01-06—Подача