10

f5

1453409

Изобретение относится к автоматике и вычислительной технике и может быть использовано для функцио- нально-пара1 етрического контроля логических элементов, в том числе микросхем и электронных блоков, содержащих логические микросхемы.

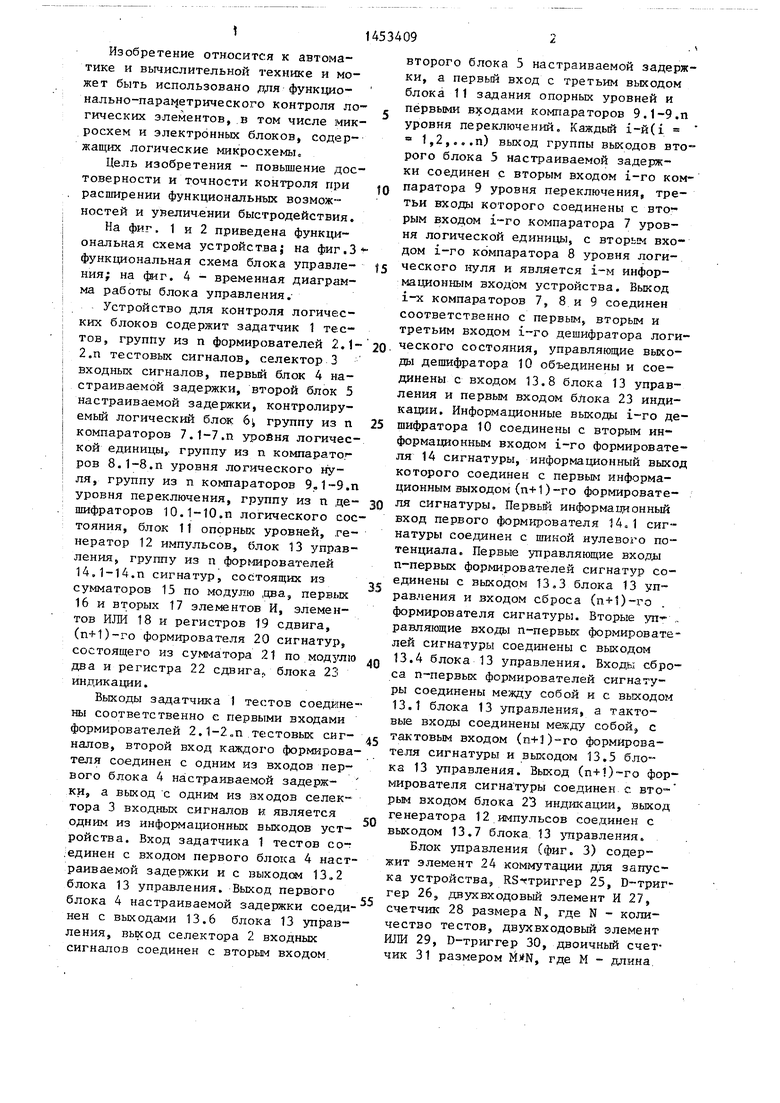

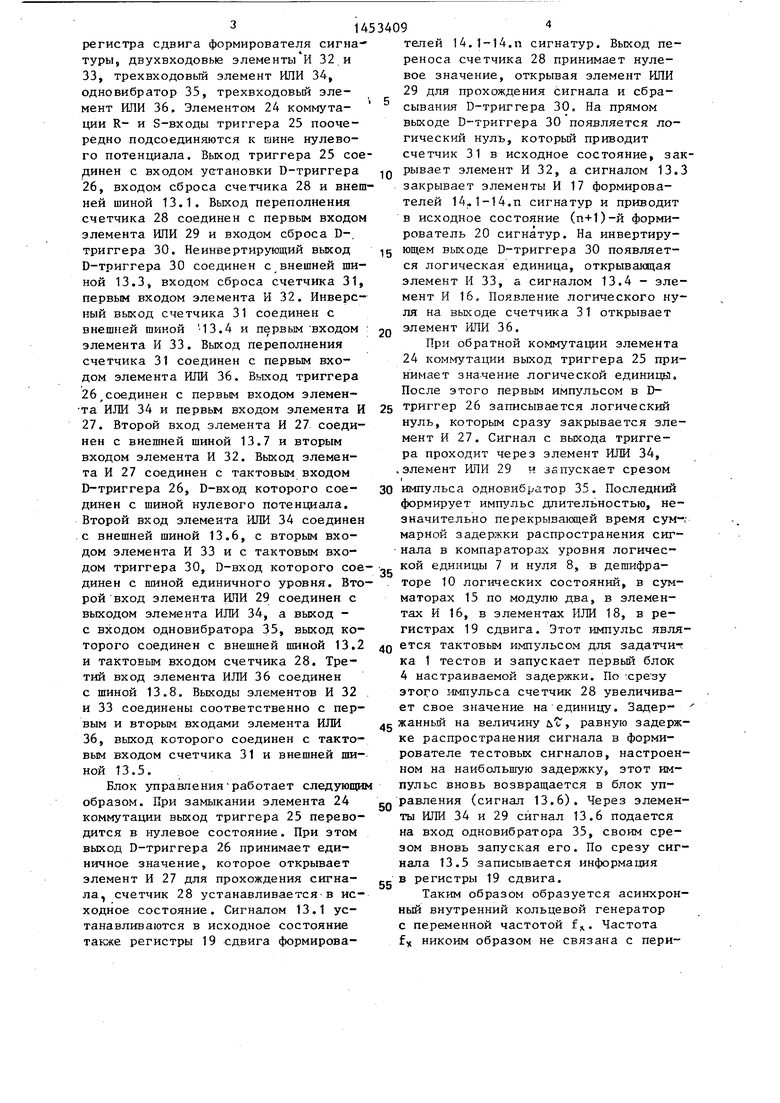

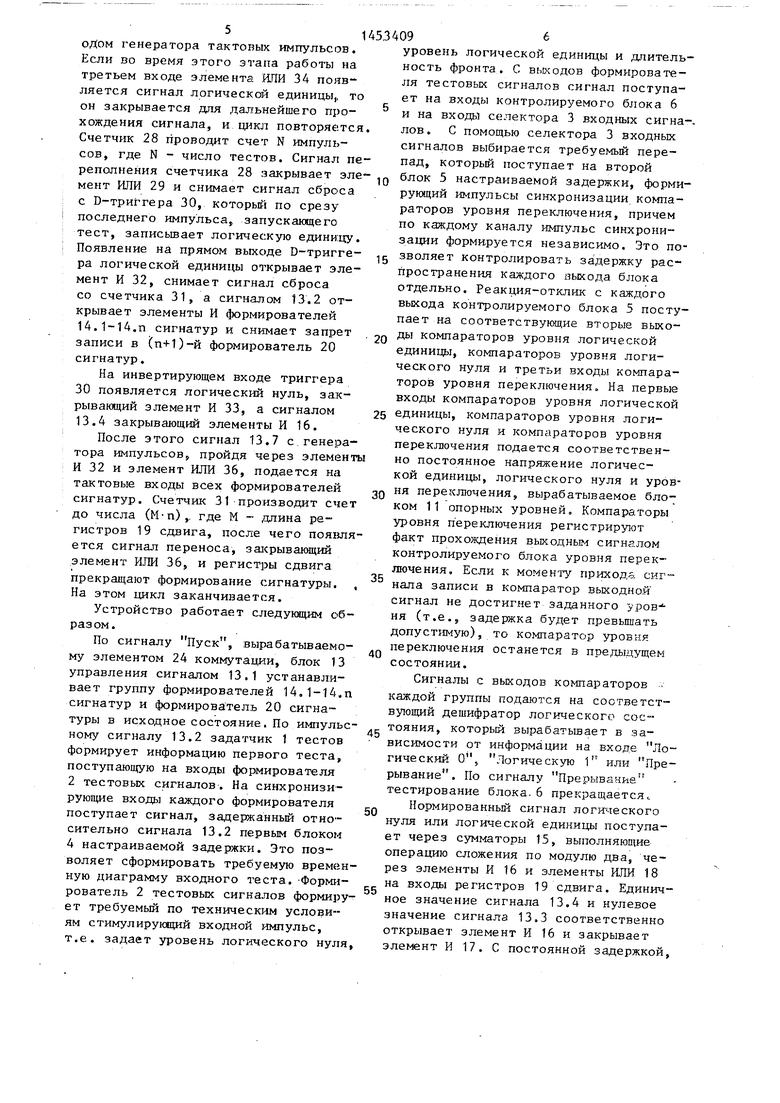

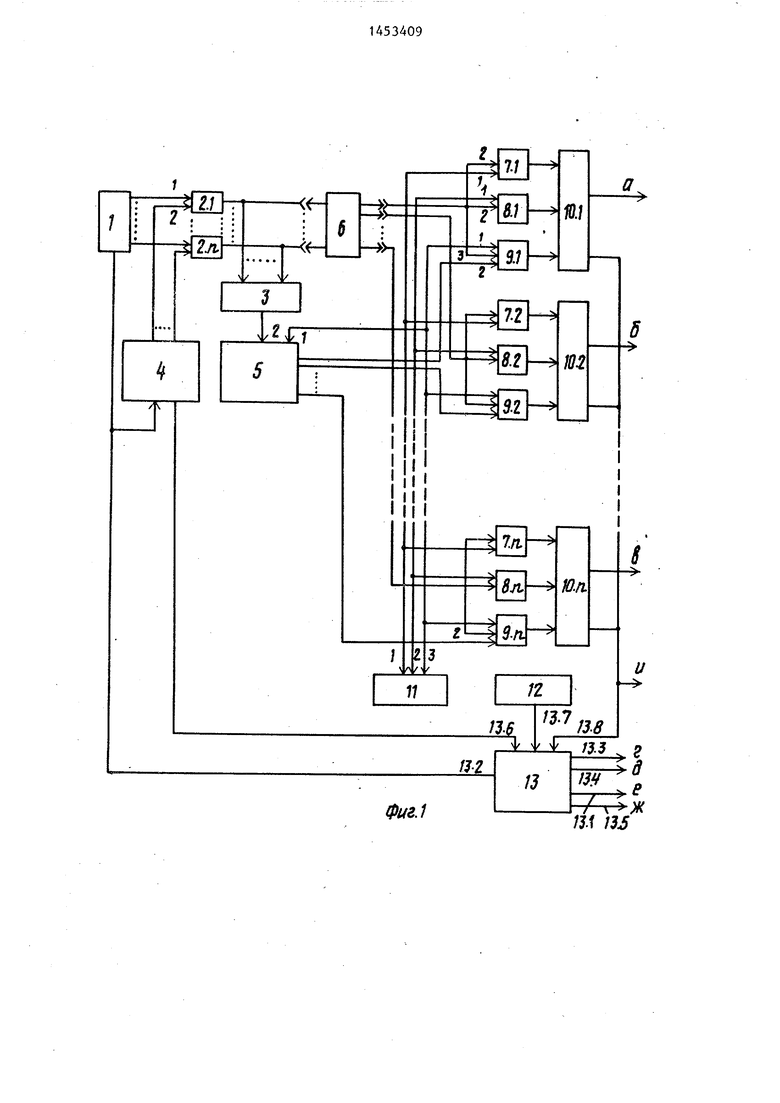

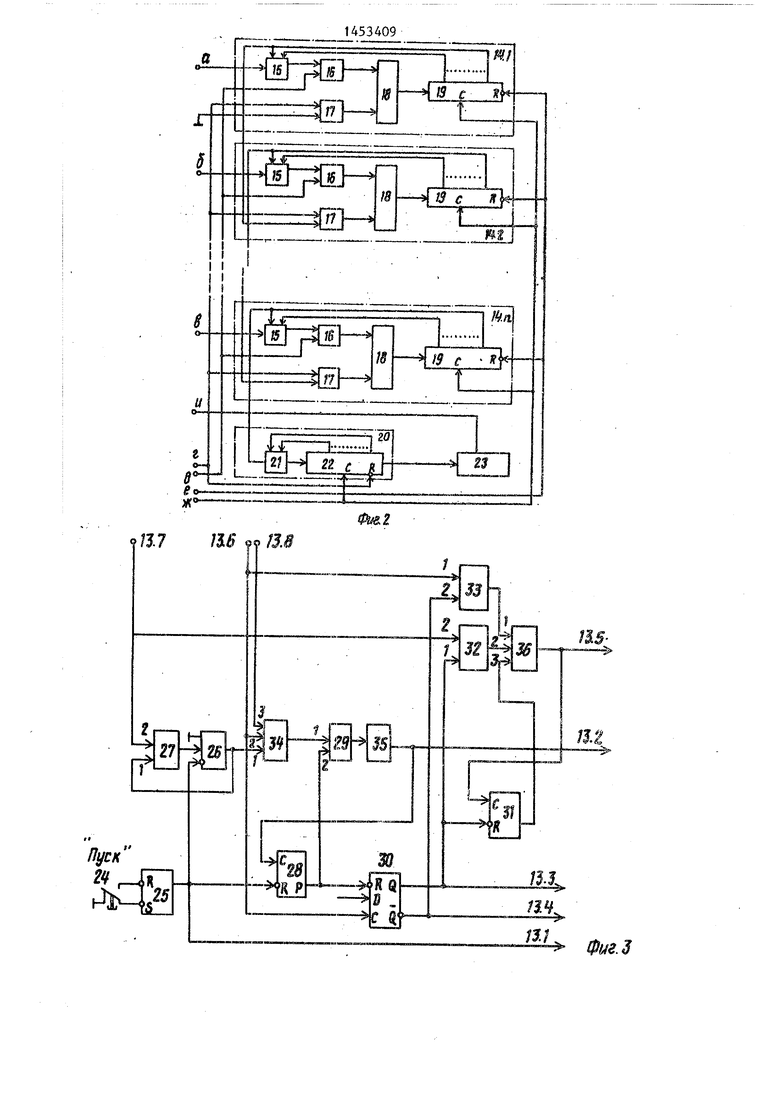

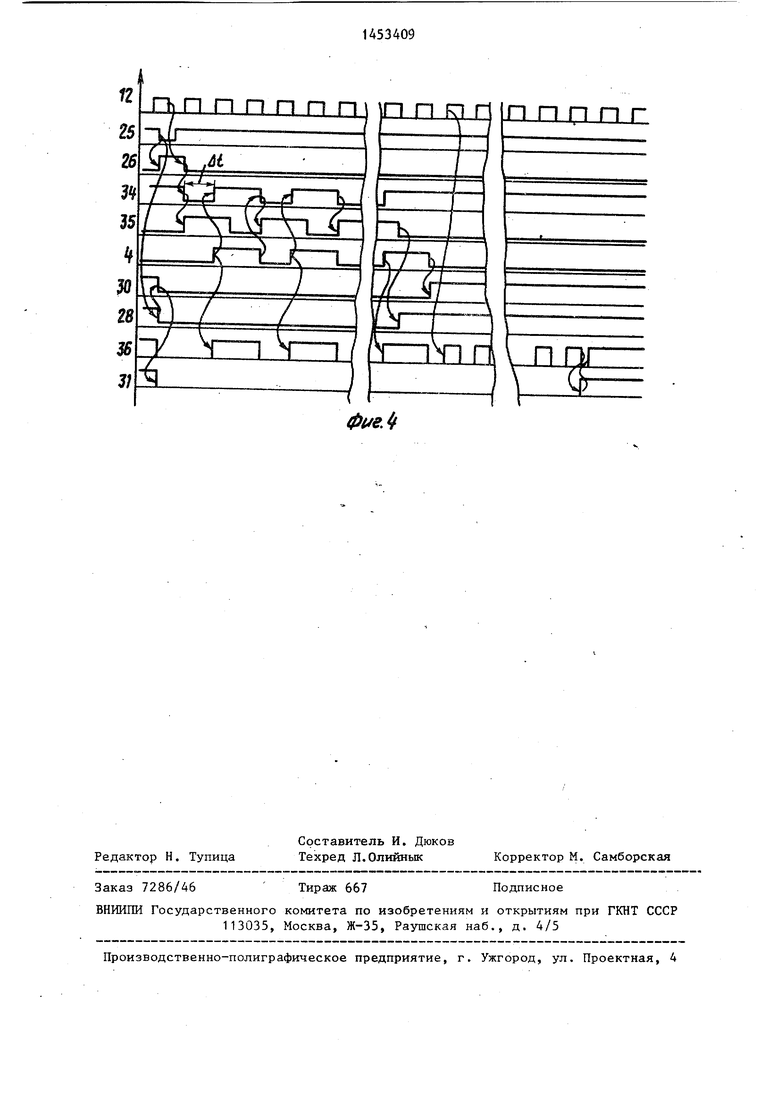

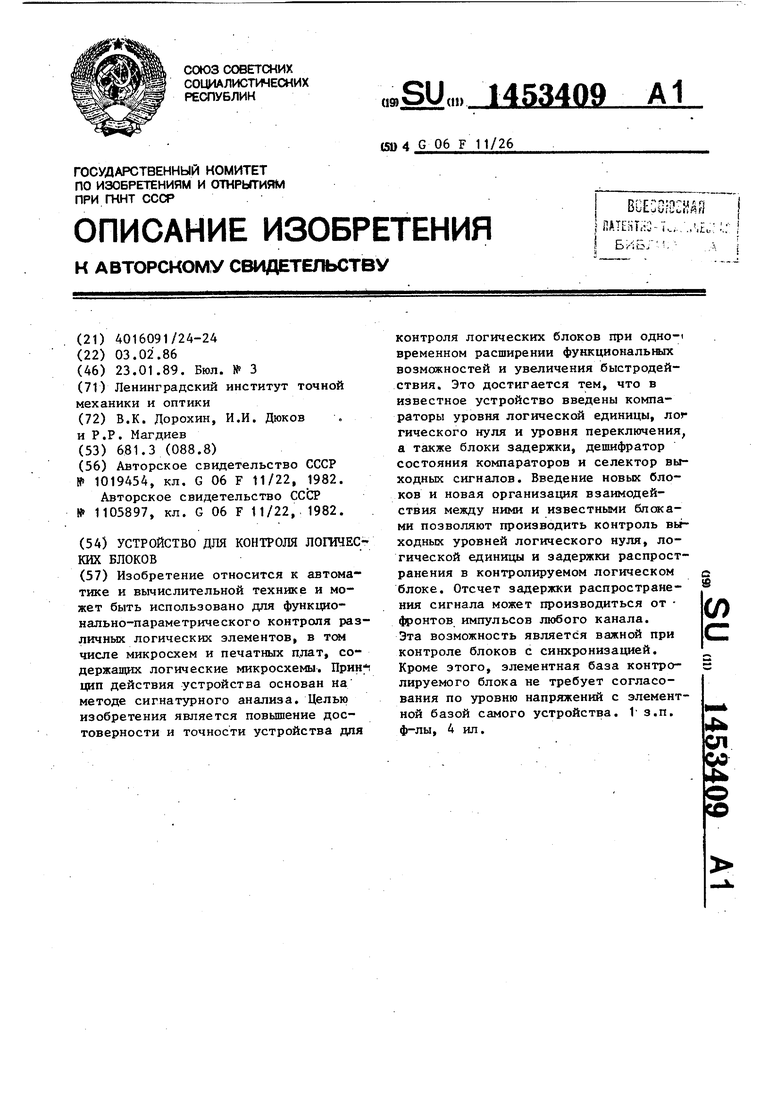

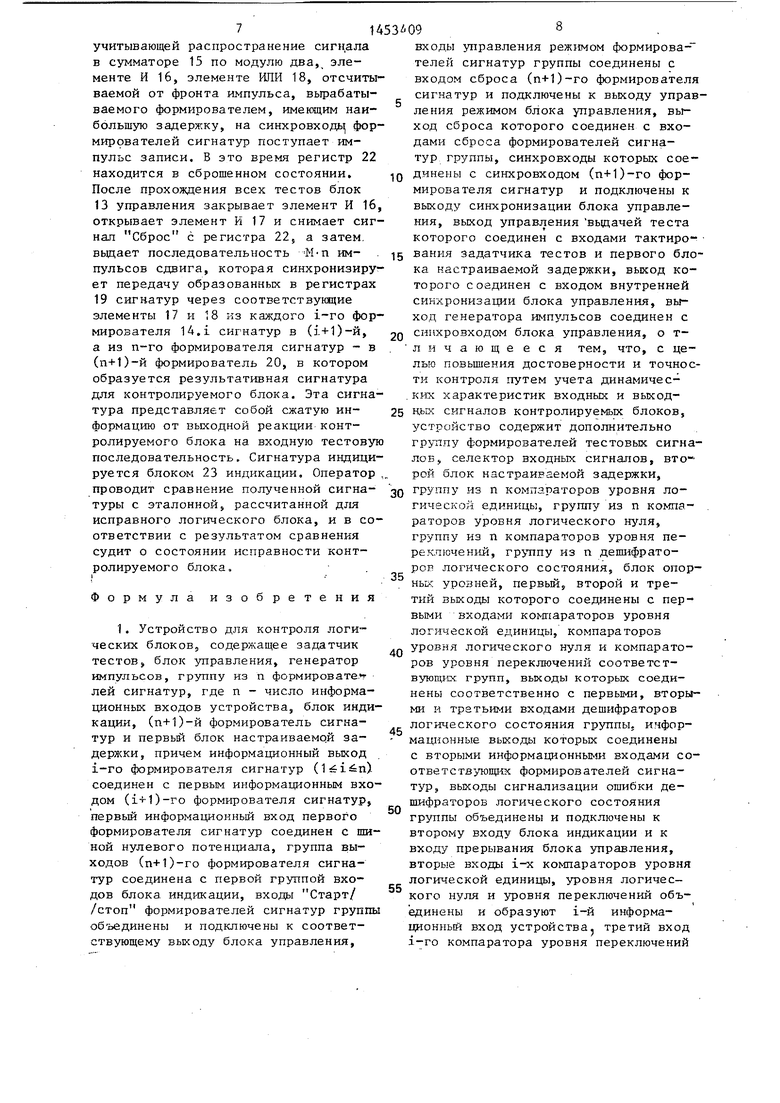

Цель изобретения - повьшение достоверности и точности контроля при . расширении функциональных возможностей и увеличении быстродействия. На фиг. 1 и 2 приведена функциональная схема устройства; на фиг. функциональная схема блока управления; на фиг. 4 - временная диаграмма работы блока управления.

Устройство для контроля логических блоков содержит задатчик 1 тестов, группу из п формирователей 2.1-20 2.П тестовых сигналов, селектор 3 входных сигналов, первый блок 4 настраиваемой задержки, второй блок 5 настраиваемой задержки, контролируемый логический блок 6; группу из п компараторов 7.1-7.П уровня логической единицы,, группу из п компаратог ров 8.1-8.П уровня логического нуля, группу из п компараторов 9.1-9.П уровня переключения, группу из п це- шифраторов 10.1-10.п логического состояния, блок 11 опорных уровней, генератор 12 импульсов, блок 13 управления, группу из п формирователей 14,1-14.п сигнатур, состоящих из сумматоров 15 по модулю даа, первых 16 и вторых 17 элементов И, элементов ИЛИ 18 и регистров 19 сдвига, (n-f-D-ro формирователя 20 сигнатур, состоящего из сумматора 21 по мод-улю два и регистра 22 сдвига, блока 23 индикации.

Выходы задатчика 1 тестов соединены соответственно с первыми входами

второго блока 5 настраиваемой зад ки, а первый вход с третьим выход блока 11 задания опорных уровней первыми входами компараторов 9.1уровня переключений. Каждый 1-й(1 1,2,...п) выход группы выходов рого блока 5 настраиваемой задерж ки соединен с вторым входом i-ro к паратора 9 уровня переключения, тр тьи входы которого соединены с вто рым входом i-ro компаратора 7 уров ня логической единицы, с вторым вх дом i-ro компаратора 8 уровня логи ческого нуля и является информационным входом устройства. Выкод i-x компараторов 7, 8 и 9 соединен соответственно с первым, вторым и третьим входом дешифратора ло ческого состояния, управляющие вых ды дешифратора 10 объединены и сое динены с входом 13.8 блока 13 упра ления и первым входом блока 23 инд кации. Информационные выходы i-ro шифратора 10 соединены с вторым ин формационным входом i-ro формирова ля 14 сигнатуры, информационный вы которого соединен с первым информа ционным выходом (п+1) -г о формировате 30 ля сигнатуры. Первьй информадаонный вход первого формирователя 14.1 сиг натуры соединен с шикой нулевого по тенциала. Первые управляющие входди п-первых формирователей сигнатур со единены с выходом 13.3 блока 13 управления и входом сброса (п+1)-го формирователя сигнатуры. Вторые уп равляющие входы п-первых формироват лей сигнатуры соединены с выходом 13.4 блока 13 управления. Входь; сбр са п первых формирователей сигнатуры соединены между собой и с выходо 13.1 блока 13 управления, а тактовые входы соединены между собой с

25

35

40

50

AJUli ir l J3 .С 1тЗг1

™г:™::„-. ;П,:г,гг° ™™ теля соед™: с о2„иЛз -™,, „ ь.о„о„ ,3.5 .ло- вого блока 4 настраиваемой задержки, а выход С одним из входов селектора 3 входных сигналов и является одним из информационных выходов устройства. Вход задатчика 1 тестов со-г .единен с входом первого блока 4 настраиваемой задержки и с выходом 13„2 блока 13 управления. Выход первого

. /где- ---к;л .::. rIKErSrrEr

л. -- - JJiifcvy vyi A ) -f W ли

КЗ 13 управления. Выход (п+1)-го фор мирователя сигнатуры соединен с вторьм входом блока 23 инджации, выход генератора 12 импульсов соединен с выходом 13.7 блока 13 1шравления.

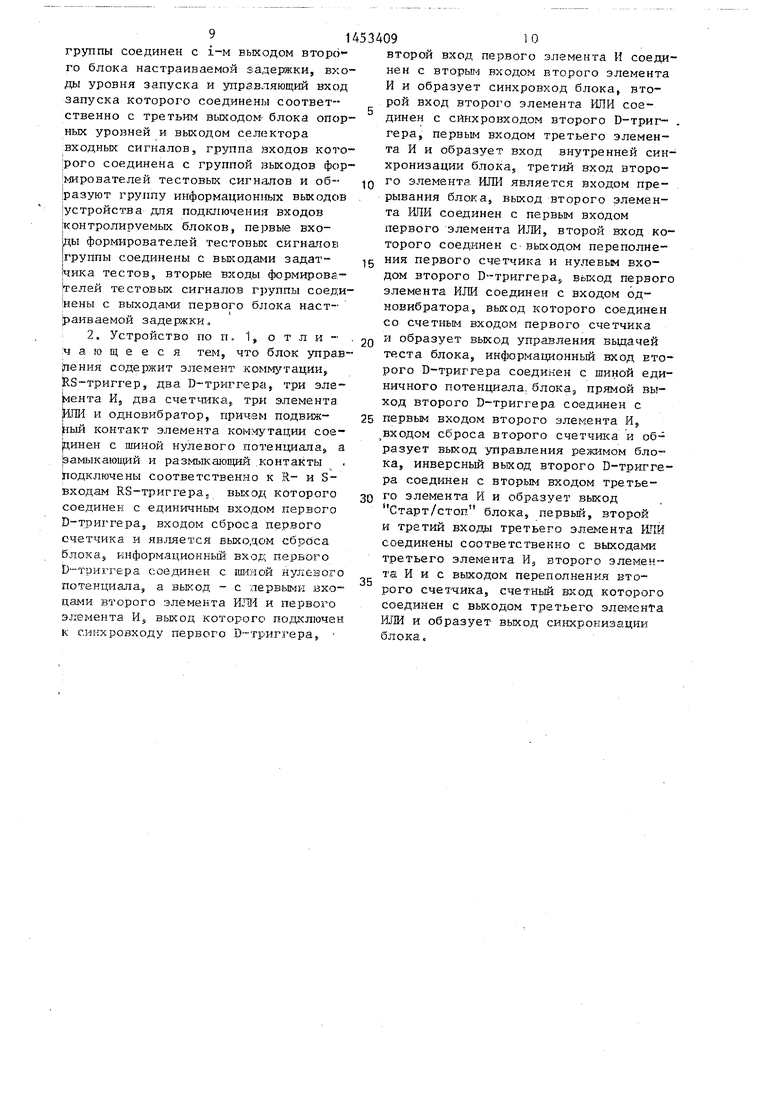

Блок управления (фиг. 3) содержит элемент 24 коммутации для запуска устройства, КЗгтриггер 25, D-триг гер 26, двухвходовьй элемент И 27,

10

f5

20

второго блока 5 настраиваемой задержки, а первый вход с третьим выходом блока 11 задания опорных уровней и первыми входами компараторов 9.19.П уровня переключений. Каждый 1-й(1 1,2,...п) выход группы выходов второго блока 5 настраиваемой задержки соединен с вторым входом i-ro компаратора 9 уровня переключения, третьи входы которого соединены с вторым входом i-ro компаратора 7 уровня логической единицы, с вторым входом i-ro компаратора 8 уровня логического нуля и является информационным входом устройства. Выкод i-x компараторов 7, 8 и 9 соединен соответственно с первым, вторым и третьим входом дешифратора логического состояния, управляющие выходы дешифратора 10 объединены и соединены с входом 13.8 блока 13 управления и первым входом блока 23 индикации. Информационные выходы i-ro дешифратора 10 соединены с вторым информационным входом i-ro формирователя 14 сигнатуры, информационный выход которого соединен с первым информационным выходом (п+1) -г о формировате- 30 ля сигнатуры. Первьй информадаонный вход первого формирователя 14.1 сигнатуры соединен с шикой нулевого потенциала. Первые управляющие входди п-первых формирователей сигнатур соединены с выходом 13.3 блока 13 управления и входом сброса (п+1)-го формирователя сигнатуры. Вторые уп равляющие входы п-первых формирователей сигнатуры соединены с выходом 13.4 блока 13 управления. Входь; сброса п первых формирователей сигнатуры соединены между собой и с выходом 13.1 блока 13 управления, а тактовые входы соединены между собой с

25

35

0

° ™ ™™

-™,, „ ь.о„о„ ,3.5 .ло-

/где- ---к;л л. -- - JJiifcvy vyi A ) -f W ли

КЗ 13 управления. Выход (п+1)-го формирователя сигнатуры соединен с вто рьм входом блока 23 инджации, выход генератора 12 импульсов соединен с выходом 13.7 блока 13 1шравления.

Блок управления (фиг. 3) содержит элемент 24 коммутации для запуска устройства, КЗгтриггер 25, D-триг- гер 26, двухвходовьй элемент И 27,

регистра сдвига формирователя сигна туры, двухвходовые элементы И 32 и 33, трехвходовый элемент ИЛИ 34, одновибратор 35, трехвходовьм элемент ИЛИ 36, Элементом 24 коммутации R- и S-входы триггера 25 поочередно подсоединяются к шине нулевого потенциала. Выход триггера 25 сое динен с входом установки D-триггера

26,входом сброса счетчика 28 и внешней шиной 13.1. Выход переполнения счетчика 28 соединен с первым входом элемента ИЛИ 29 и входом сброса D-, триггера 30. Неинвертирующий выход D-триггера 30 соединен с внешней шиной 13.3, входом сброса счетчика 31, первым входом элемента И 32. Инверсный выход счетчика 31 соединен с внешней шиной 13.4 и первым входом элемента И 33. Выход переполнения счетчика 31 соединен с первым входом элемента РШИ 36. Выход триггера 26 соединен с первым входом элемента ИЛИ 34 и первьм входом элемента И

27.Второй вход элемента И 27 соединен с внешней шиной 13.7 и вторым входом элемента И 32. Выход элемента И 27 соединен с тактовым входом D-триггера 26, D-вход которого соединен с шиной нулевого потенциала. Второй вход элемента ИЛИ 34 соединен

.с внешней шиной 13.6, с вторым входом элемента И 33 и с тактовым входом триггера 30, D-вход которого соединен с шиной единичного уровня. Второй вход элемента ИЛИ 29 соединен с выходом элемента ИЛИ 34, а выход - с входом одновибратора 35, выход которого соединен с внешней шиной 13,2 и тактовым входом счетчика 28. Третий вход элемента ИЛИ 36 соединен с шиной 13.8. ВьЕходы элементов И 32 и 33 соединены соответственно с первым и вторым входами элемента ИЛИ 36, выход которого соединен с тактовым входом счетчика 31 и внешней шиной 13.5.

Блок управления работает следующи образом. При замыкании элемента 24 коммутации выход триггера 25 переводится в нулевое состояние. При этом выход D-триггера 26 принимает единичное значение, которое открывает элемент И 27 для прохождения сигнала, счетчик 28 устанавливается-в исходное состояние. Сигналом 13,1 устанавливаются в исходное состояние также регистры 19 сдвига формирова0

5

телей 14.1-14.П сигнатур. Выход переноса счетчика 28 принимает нулевое значение, открывая элемент ИЛИ 29 для прохождения сигнала и сбрасывания D-триггера 30, На прямом выходе D-триггера 30 появляется логический нуль, который приводит счетчик 31 в исходное состояние, закрывает элемент И 32, а сигналом 13.3 закрывает элементы И 17 формирователей 14,1-14.п сигнатур и приводит в исходное состояние (п+1)-й формирователь 20 сигнатур. На инвертиру- 5 ющем выходе D-триггера 30 появляется логическая единица, открывавшая элемент И 33, а сигналом 13.4 - элемент И 16, Появление логического нуля на выходе счетчика 31 открывает элемент Ш1И 36.

При обратной коммутации элемента 24 коммутации выход триггера 25 принимает значение логической единица. После этого первым импульсом в D- триггер 26 записывается логический нуль, которым сразу закрывается элемент И 27. Сигнал с выхода триггера проходит через элемент ИЛИ 34, элемент ИЛИ 29 и запускает срезом

I

импульса одновибратор 35. Последний формирует имщшьс длительностью, незначительно перекрываюцей время сум-; марной задержки распространения сигнала в компараторах уровня логической единицы 7 и нуля 8, в дешифраторе 10 логических состояний, в сумматорах 15 по модулю два, в элементах И 16, в элементах ИЛИ 18, в регистрах 19 сдвига. Этот импульс является тактовым импульсом для задатчиг ка 1 тестов и запускает первый блок 4 настраиваемой задержки. По срезу этого импульса счетчик 28 увеличивает свое значение на единицу. Задер- с жанный на величину л о , равную задержке распространения сигнала в формирователе тестовых сигналов, настроенном на наибольшую задержку, этот импульс вновь возвращается в блок управления (сигнал 13,6). Через элементы ИЛИ 34 и 29 сигнал 13.6 подается на вход одновибратора 35, своим срезом вновь запуская его. По срезу сигнала 13.5 записывается информация в регистры 19 сдвига.

Таким образом образуется асинхронный внутренний кольцевой генератор с переменной частотой f. Частота fy никоим образом не связана с пери0

5

0

0

5

одом генератора тактовык импульсов. Если во время этого этапа работы на третьем входе элемента ИЛИ 34 появляется сигнал логической единицы,, т он закрывается для дальнейшего прохождения сигнала, и цикл повторяетс Счетчик 28 проводит счет N импульсов, где N - число тестов. Сигнал преполнения счетчика 28 закрывает элмент ИЛИ 29 и снимает сигнал сброса ; с D-триггера 30, которьй по срезу последнего импульса, запускающего

тест, записьюает логическую единицу ; Появление на прямом выходе D-триггера логической единицы открывает элемент И 32, снимает сигнал сброса со счетчика 31, а сигналом 13.2 открывает элементы И юрмирователей 14.1-14.п сигнатур и снимает запрет записи в tn+D-A формирователь 20 сигнатур.

На инвертирующем входе триггера 30 появляется логический нуль, закрывающий элемент И 33, а сигналом 13.4 закрывающий элементы И 16.

После этого сигнал 13.7 с генератора импульсов, пройдя через элемент И 32 и элемент ИЛИ 36, подается на тактовые входы всех формирователей сигнатур. Счетчик 31 производит счет до числа (М п),. где М - длина регистров 19 сдвига, после чего появляется сигнал переноса, закрывающий элемент ИЛИ 36, и регистры сдвига прекращают формирование сигнатуры. На этом цикл заканчивается.

Устройство работает следующим образом.

По сигналу Пуск, вырабатываемому элементом 24 коммутации, блок 13 управления сигналом 13.1 устанавливает группу формирователей 14.1-14.п сигнатур и формирователь 20 сигнатуры в исходное состояние. По импульсному сигналу 13.2 задатчик 1 тестов формирует информацию первого теста, поступающую на входы формирователя 2 тестовых сигналов. На синхронизирующие входы каждого формирователя поступает сигнал, задержанный относительно сигнала 13.2 первым блоком 4 настраиваемой задержки. Это позволяет сформировать требуемую временную диаграмму входного теста. -Формирователь 2 тестовых сигналов формирует требуемый по техническим условиям стимулирующий входной импульс, т.е. задает уровень логического нуля.

. 1453409

10

30

0

5

уровень логической единицы и длительность фронта. С вькодов формирователя тестовых сигналов сигнал поступает на входы контролируемого блока 6 и на входы селектора 3 входных сигна-. лов. С помощью селектора 3 входных сигналов выбирается требуемый перепад, которьй поступает на второй блок 5 настраиваемой задержки, формирующий импульсы синхронизации компараторов уровня переключения, причем по каждому каналу импульс синхронизации формируется независимо. Это по- 5 зволяет контролировать задержку распространения каждого выхода блока отдельно. Реакция-отклик с каждого выхода контролируемого блока 5 поступает на соответствующие вторые выхо- 20 ДЫ компараторов уровня логической единицы, компараторов уровня логического нуля и третьи входы компараторов уровня переключения. На первые входы компараторов уровня логической 25 единицы, компараторов уровня логического нуля и компараторов уровня переключения подается соответственно постоянное напряжение логической единицы, логического нуля и уровня переключения, вырабатываемое блоком 11 опорных уровней. Компараторы уровня переключения регистрируют факт прохождения выходным сигналом контролируемого блока уровня переключения. Если к моменту приходе, сигнала записи в компаратор выходной сигнал не достигнет заданного уровня (т.е., задержка будет превьшать допустимую), то компаратор уровня переключения останется в предьщущем состоянии.

Сигналы с выходов компараторов .. каждой группы подаются на соответствующий дешифратор логического состояния, который вырабатьшает в зависимости от информации на входе Логический О, Логическую Г или Прерывание. По сигналу Прерывание тестирование блока.6 прекращается.

Нормированньй сигнал лопгяеского нуля или логической единицы поступает через сумматоры 15, выполняющие операцию сложения по модулю два, через элементы И 16 и элементы ИЛИ 18 на входы регистров 19 сдвига. Единичное значение сигнала 13.4 и нулевое значение сигнала 13.3 соответственно открывает элемент И 16 и закрывает элемент И 17. С постоянной задержкой.

35

0

5

учитывающей распространение сигнала в сумматоре 15 по модулю два,, элементе И 16, элементе ИЛИ 18, отсчитываемой от фронта импульса, вырабатываемого формирователем, имеющим наибольшую задержку, на синхровходь формирователей сигнатур поступает импульс записи. В это время регистр 22 находится в сброшенном состоянии. После прохождения всех тестов блок 13 управления закрывает элемент И 16, открывает элемент И 17 и снимает сигнал Сброс с регистра 22, а затем, вьщает последовательность М-п импульсов сдвига, которая синхронизирует передачу образованных в регистрах 19 сигнатур через соответствунщие элементы 17 и 18 из каждого i-ro формирователя 14,1 сигнатур в (1+1)-й, а из п-го формирователя сигнатур - в (п+1)-й формирователь 20, в котором образуется результативная сигнатура для контролируемого блока. Эта сигнатура представляет собой сжатую информацию от выходной реакции контролируемого блока на входную тестовую последовательность. Сигнатура индицируется блоком 23 индикации. Оператор проводит сравнение полученной сигнатуры с эталонной, рассчитанной для исправного логического блока, и в соответствии с результатом сравнения судит о состоянии исправности контролируемого блока.

Формула изобретения

1. Устройство для контроля логических блоков, содержащее задатчик тестовJ блок управления, генератор импульсов, группу из п формировате.т лей сигнатур, где п - число информационных входов устройства, блок индикации, (п+1)-й формирователь сигнатур и первьй блок настраиваемой задержки, причем информационный вькод i-ro формирователя сигнатур (1-г1бп) соединен с первым информационным входом (i-s-O-ro формирователя сигнатур, первый информационный вход первого формирователя сигнатур соединен с шиной нулевого потенциала, группа выходов (п+1)-го формирователя сигнатур соединена с первой группой входов блока индикации, входы Старт/ /стоп формирователей сигнатур группы об ьединены и подключены к соответствующему выходу блока управления.

входы управления режимом формирователей сигнатур группы соединены с входом сброса (п+1)-го формирователя сигнатур и подключены к выходу управления режимом блока управления, выход сброса которого соединен с входами сброса формирователей сигнатур группы, синхровходы которых соединены с синхровходом (п+1)-го формирователя сигнатур и подключены к выходу синхронизации блока управле0

5

0

которого соединен с входами тактиро- 5 вания задатчика тестов и первого блока настраиваемой задержки, выход которого соединен с входом внутренней синхронизации блока управления, выход генератора импульсов соединен с 0 синхровходом блока управления, о т- личающе еся тем, что, с целью повышения достоверности и точности контроля путем учета динамичес- .ких характеристик входных и выход- 5 ных сигналов контролируемых блоков, устройство содержит дополнительно группу формирователей тестовых сигналов, селектор входных сигналов, второй блок настраиваемой задержки, группу из п компараторов уровня логической единицы, группу из п компа- , раторов уровня логического нуля, группу из п компараторов уровня переключений, группу из п дeшliфpaтo- роЕ логического состояния, блок опорных уровней, первьй, второй и третий выходы которого соединены с пер- выми входами компараторов уровня логической единицы, компараторов уровня логического нуля и компараторов уровня переключений соответствующих групп, выходы которых соединены соответственно с первыми, вторыми и третьими входами дешифраторов логического состояния группы, информационные выходы которых соединены с вторыми информационными входами соответствующих формирователей сигнатур, выходы сигнализации ошибки дешифраторов логического состояния группы объединены и подключены к второму входу блока индикации и к входу прерывания блока управления, вторые входы i-x компараторов уровня логической единицы, уровня логического нуля и уровня переключений объ- (вдинены и образуют i-й информационный вход устройства, третий вход i-ro компаратора уровня переключений

5

0

5

91

группы соединен с i-м вькодом второго блока настраиваемой задержки, вхо ды уровня запуска и управляющий вход запуска которого соединены соответственно с третьим выходом- блока опорных уровней и вькодом селектора входных сигналов, группа )зходов кото- ;рого соединена с группой выходов фор- |1дарователей тестовых сигналов и об- ;разуют группу информационных выходов |устройства для подключения входов |контролируемых блоков, первые вхо- |ды формирователей тестовых сигналов |Группы соединены с вызсодами задат- ика тестов, вторые входы формирователей тестовых сигналов группы соеди- ;нены с выходами первого блока наст- аиваемой задержки,

2. Устройство по П:, 1, о т л и - :ч а ю щ е е с я тем, что блок jmpa.B- |пения содержит элемент коммз тации, НЗ-триггер, два В-триггера, три зле- И, два счетчика,, три элемента Или и одновибратор, причем подвиж- ый контакт элемента коммутации сое- |динен с шиной нулевого потенциала а Замыкающий и размыкаюпщй .контакты подключены соответственно к R и S- входам КЗ-триггера, выход которого соединен с единичным входом первого 0 триггера, входом сброса первого счетчика и яв.пяется выходом сброса блока, информационньш вход первого 0--триггера соединен с шиной нулевого потенциала, а выход - с первьт-ж входами второго элемента ИЖ и первого элемента И, выход которого подключен к синхровходу первого D-триггера,

5340910

второй вход первого элемента И соединен с вторызч входом второго элемента И и образует синхровход блока, второй вход второго элемента ИЛИ соединен с сйнхровходом второго D-триг- гера, nepHbitvi входом третьего элемента И и образует вход внутренней синхронизации блока, третий вход второ 0 го элемента ИЛИ является входом прерывания блока, выход второго элемента ИЛИ соединен с первым входом первого элемента ИЛИ, второй вход которого соединен с- выходом переполне15 ния первого счетчика и нулевым входом второго В-триггера,, выход первого элемента ИЛИ соединен с входом од- новибратора, выход которого соединен со счетным входом первого счетчика 20 и образует выход управления выдачей теста блока, информационньй вход второго D-триггера соединен с шиной единичного потенциала, блока, прямой выход второго D-триггера соединен с

25 первым входом второго элемента И, входом сброса второго счетчика и образует выход -управления режимом блока, инверсный выход второго D-триггера соединен с вторым входом третьего элемента И и образует выход Старт/стоп блока, первьй, второй и третий входы третьего элемента 1ШИ соединены соответственно с выходами третьего элемента И, второго элемента Ни с выходом переполнения второго счетчика, счетньй вход которого соединен с выходом третьего элемента ИЛИ и образует выход синхронизации блока.

30

35

/J.f /35

31

п п п n г

л

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для функционально-параметрического контроля логических элементов | 1982 |

|

SU1140065A1 |

| Устройство для функционально-параметрического контроля логических элементов | 1985 |

|

SU1302220A2 |

| Устройство для контроля микропроцессорных цифровых блоков | 1986 |

|

SU1383364A1 |

| Устройство для контроля цифровых блоков | 1984 |

|

SU1264186A1 |

| Устройство для функционально-параметрического контроля логических элементов | 1987 |

|

SU1562864A1 |

| Устройство для функционально-параметрического контроля логических элементов | 1982 |

|

SU1067453A1 |

| Устройство для контроля цифровых блоков | 1986 |

|

SU1343417A1 |

| Устройство для контроля логических блоков | 1982 |

|

SU1105897A1 |

| Устройство для определения свойств полноты логических функций | 1984 |

|

SU1170446A1 |

| Устройство для контроля логических блоков | 1991 |

|

SU1833879A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано для функционально-параметрического контроля различных логических элементов, в тс числе микросхем и печатных п.лат, содержащих логические микросхемы. 11рин 1 цип действия устройства основан на методе сигнатурного анализа. Целью изобретения является повышение достоверности и точности устройства для контроля логических блоков при одно-i временном расширении функциональных возможностей и увеличения быстродействия. Это достигается тем, что в известное устройство введены компараторы уровня логической единицы, лог гического нуля и уровня переклнзчения, а также блоки задержки, дешифратор состояния компараторов и селектор выходных сигналов. Введение новых блоков и новая организация взаимодействия между ними и известными блоками позволяют производить контроль выходных уровней логического нуля, логической единицы и задержки распространения в контролируемом логическом блоке. Отсчет задержки распространения сигнала может производиться от фронтов импульсов любого канала. Эта возможность является важной при контроле блоков с синхронизацией. Кроме этого, элементная база контролируемого блока не требует согласования по уровню напряжений с элементной базой самого устройства. V з.п, ф-лы, 4 ил. с «б (Л с: Ji СП СО

Ф(е.

Редактор Н. Тупица

Составитель И. Дюков Техред Л.Олийяык

Заказ 7286/46

Тираж 667

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., д. 4/5

Корректор М. Самборская

Подписное

| Устройство для контроля многовыходных цифровых узлов | 1982 |

|

SU1019454A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для контроля логических блоков | 1982 |

|

SU1105897A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-01-23—Публикация

1986-02-03—Подача