для подключения к управляющим электр дам основных тиристоров. 2. Устройство для управления тиристорным регулятором мощности, содержащее задатчик угла управления, синхронизирующий блок, подключенный к генератору линейно изменяющегося напряжения, нуль-орган, выходные кас кады, отличающееся тем, что, с целью расширения функциональных возможностей, оно снабжено нелинейным блоком, реализующим функцио . нальную зависимость oi f(), в соот ветствии с выражением 2 sin 2oi- sin l 2 sin 2|3- sin 4p, задатчиком уровня, двумя блоками вычитания, четырьм компараторами, шестью формирователями коротких импульсов, четырьмя пара ми элементов И, двумя элементами ИЛИ и элементом НЕ, причем выход задатчика угла управления /i соединен с входом нелинейного блока, с первым входом первого блока вычитания и с первым входом первого компаратора, выход нелинейного блока соединен с первым входом второго блока вычитания и с первым входом второго компаратора, вторые входы блоков вычитания соединены с выходом задатчика уровня, а их выходы соединены с первыми входами третьего и четвертого 11 7 компараторов, вторые входы всех компараторов соединены с выходом генератора линейно изменяющегося напряжения, выход каждого компаратора через соответствующий формирователь коротких импульсов подключен к первым входам элементов И одноименных пар, вторые входы первых элементов И каждой пары соединены с выходом нульоргана непосредственно, а вторых элементов И каждой пары - через элемент НЕ, выходы элементов И первой и четвертой пар предназначены для (Подключения через выходные каскады к управляющим электродам коммутирующих тиристоров, выходы первых элементов И второй и третьей пар подключены к первому и второму входам первого элемента ИЛИ, выходы вторых элементов И этих пар подключены к первому и второму входам второго элемента ИЖ, третий вход первого элемента ИЛИ через соответствующий формирователь коротких импульсов подключен к выходу нуль-органа, третий вход второго элемента ИЛИ через соответствующий формирователь коротких импульсов - к выходу элемента НЕ, выходы элементов ИЛИ предназначены для подключения к управляющим электродам основных тиристоров.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления электродвигателем воздуховсасывающего агрегата пылесоса | 1990 |

|

SU1734183A1 |

| Устройство для управления @ -фазным тиристорным преобразователем | 1988 |

|

SU1739453A1 |

| Устройство для автоматического регулирования температуры | 1988 |

|

SU1645945A1 |

| Устройство для управления вентильным электродвигателем, выполненным на базе синхронной машины | 1987 |

|

SU1636978A1 |

| Широтно-импульсный N-фазный инвертор | 1989 |

|

SU1815776A1 |

| Устройство для импульсно-фазового управления @ - фазным тиристорным преобразователем | 1988 |

|

SU1739454A1 |

| Регулятор электрической мощности переменного тока(его варианты) | 1981 |

|

SU983690A1 |

| Устройство для оптимизации фотосинтеза растений | 1989 |

|

SU1690611A1 |

| Цифровое устройство для коммутации симистора | 1982 |

|

SU1039005A1 |

| Измеритель нелинейности импульсовпилООбРАзНОгО НАпРяжЕНия | 1979 |

|

SU805207A1 |

1, Устройство для управления тиристорным регулятором мощности, содержащее задатчик угла управления, синхронизирующий блок, подключенный к генератору линейно изменяющегося напряжения, нуль-орган, выходные каскады, отличающееся тем, что, с целью расширения функциональных возможностей, оно снабжено нелинейным блоком, реализующим функциональную зависимость oL () в соответствии с выражением 2 sin 2 ti- sin 4 о(. 2 sin 2уь sin kg, блоком суммирования, двумя блоками вычитания, четырьмя компараторами, шестью формирователями коротких импульсов, четырьмя парами элементов И, двумя элементами ИЛИ, элементом НЕ, амплитудным деуектором с делителем на выходе, причем выход задатчика угла управления -v. соединен с входом нелинейного блока и с первыми входами блока суммирования и первого блока вычитания, первый вход второго блока вычитания соединен с выходом нелинейного блока, второй вход через амплитудный детектор с делителем на выходе - с выходом генератора линейно изменяющего напряжения, вторые входы блока суммирования и первого блока вычитания соединены с выходом делителя, выходы блока суммирования и блоков вычитания соединены с первыми входами соответственно первого, второго и третьего компараторов, вход четвертого компаратора подключен к выходу нелинейного блока, вторые входы всех компараторов подключены к выходу генератора линейно изменяющегося напряжения, выход каждого компаратора через соответствующий формирователь коротких импульсов Подключен к первым входам элементов И одноименных пар, вторые входы первых элементов И каждой пары соединены с выходом нуль-органа непосредственно, а вторых элементов И каждой пары - через элемент НЕ, выходы элементов Н первой и четвертой пар предназначены для подключения через выходные каскады к управляющим электродам коммутирующих тиристоров, выходы первых элементов И второй и третьей пар подключены к первому и второму входам первого элемента ИЛИ, выходы вторых элементов И этих пар подключены к первому и второму входам второго элемента ИЛИ, третий вход первого элемента ИЛИ через соответствующий формирователь коротких импульсов подключен к выходу нуль-органа, третий вход второго элемента ИЛИ через соответствую1ций формирователь коротких импульсов - к выходу элемента НЕ, выходы элементов ИЛИ предназт1ачены

Изобретение относится к электротехнике, в частности к бесконтактным регуляторам мощности на тиристорах.

Известен регулятор мощности, обес печивающий регулирование действующего значения напряжения на нагрузке в широких пределах fl 3.

Недостатком известного регулятора является то, что он даже при чисто активной нагрузке генерирует в сеть широкий спектр гармонических составляющих тока, что может привести к серьезньм нарушениям в работе стандартного оборудования, искажению формы напряжения сети, перенапряжениям на косинусных конденсаторах и т.д.

Наиболее близким к предлагаемому по технической сущности является

устройство для управления тиристорным регулятором мощности, содержащее задатчик угла, синхронизирующий блок, генератор линейно изменяющегося напряжения, нуль-орган, формирователь коротких импульсов, элементы И, выходные каскады. Устройство вьщает управляющий импульс на тиристор, имеющий на аноде положительный потенциал, с запаздыванием С2 }.

Недостатком данного устройства является то, что оно не может обеспечить управление с обеспечением высокого порядка высших гармоник в

кривой потребляемого jOKa.

Цель изобретения - расширение функциональных возможностей устройства.

Поставленная цель достигается

тем, что в первом варианте устройство для управления тирнсторным регулятором мощности, содержащее задатчик угла управления, синхронизирующий блок, подключенный к генератору линейно изменяющегося напряжения, нуль-орган, выходные каскады, снабжено нелинейным блоком, реализующим функциональную зависимость (i (f в соответствии с выражением 2 sin 2oiisin 4л 2 sin sin 4j-, блоком сзгммирования, двумя блоками вычитания, четырьмя компараторами, шестью формирователями коротких импульсов, четырьмя парами элементов И, двумя элементами ИЛИ, элементами НЕ и амплитудным детектором с делителем на выходе, причем выход задатчика угла управления у соединен с входом нелинейного блока и с первыми входами блока суммирования и первого блока вычитания, первьй вход второго блока вычитания соединен с выходом нелинейного блока, второй вход через амплитудный детектор с делителем на выходе - с выходом генератора линейно изменяющегося напряжения, вторые входы блока суммирования и первого блока вычитания соединены с выходом делителя, выходы блока суммирования и блоков вычитания соединены с первыми входами соответственно первого, второго и третьего компараторов, вход четвертого компаратора подключен к выходу нелинейного блока, вторые входы всех компараторов подключены к выходу генератора линейно изменяю- 35 ра щегося напряжения, выход каждого компаратора через соответствук)щий фо мирователь коротких импульсов подклю чен к первым входам элементов И одно именных пар, вторые входы первых элементов И каждой пары соединены с выходом нуль-органа непосредственно-, а вторых элементов И каждой пары через элемент НЕ, выходы элементов И первой и четвертой пар предназначены для подключения через выходные каскады к управляющим электродам коммутирующих тиристоров, выходы пер вых элементов И, второй и третьей пар подключены к первому и второму входам первого элемента ИЛИ, выходы вторых элементов И этих пар подк;йоче ны к первому и второму входам второго элемента ИЛИ, третий вход первого элемента ИЛИ через соответствующий формирователь коротких импульсов подключен к выходу нуль-органа, третий вход второго элемента ИЛИ через

соответствующий формирователь коротких импульсов - к выходу элемента НЕ, выходы элементов ИЛИ предназначены для подключения к управляющим электродам основных тиристоров.

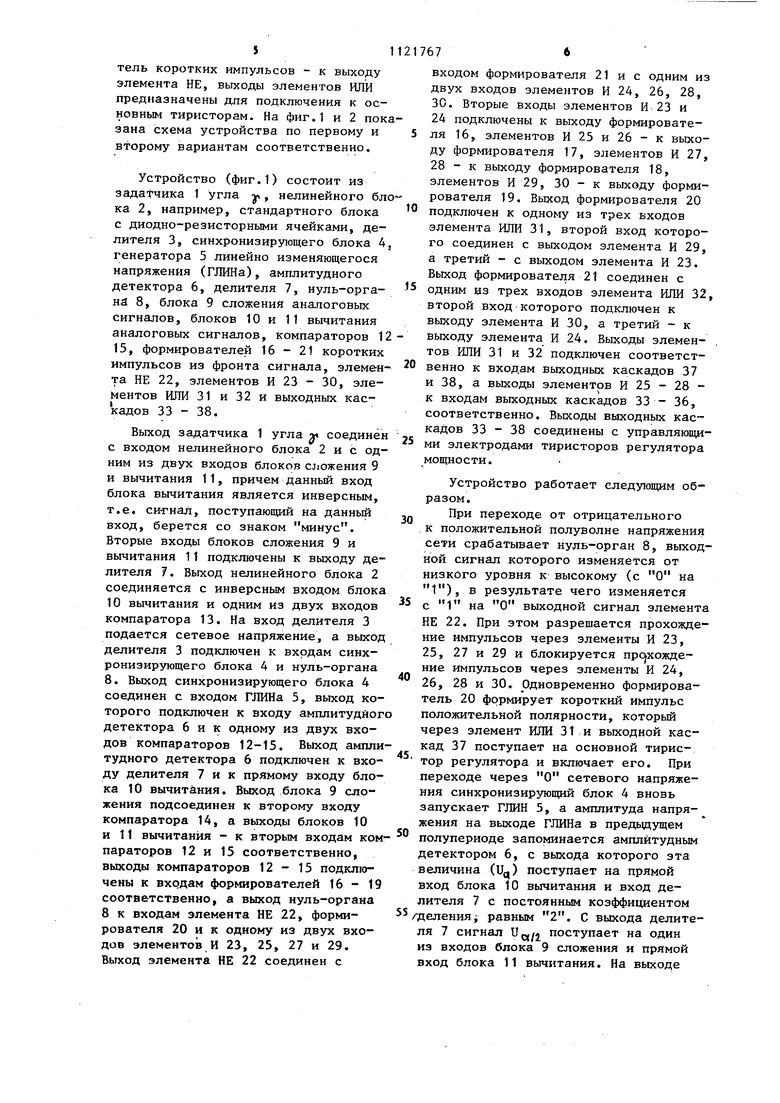

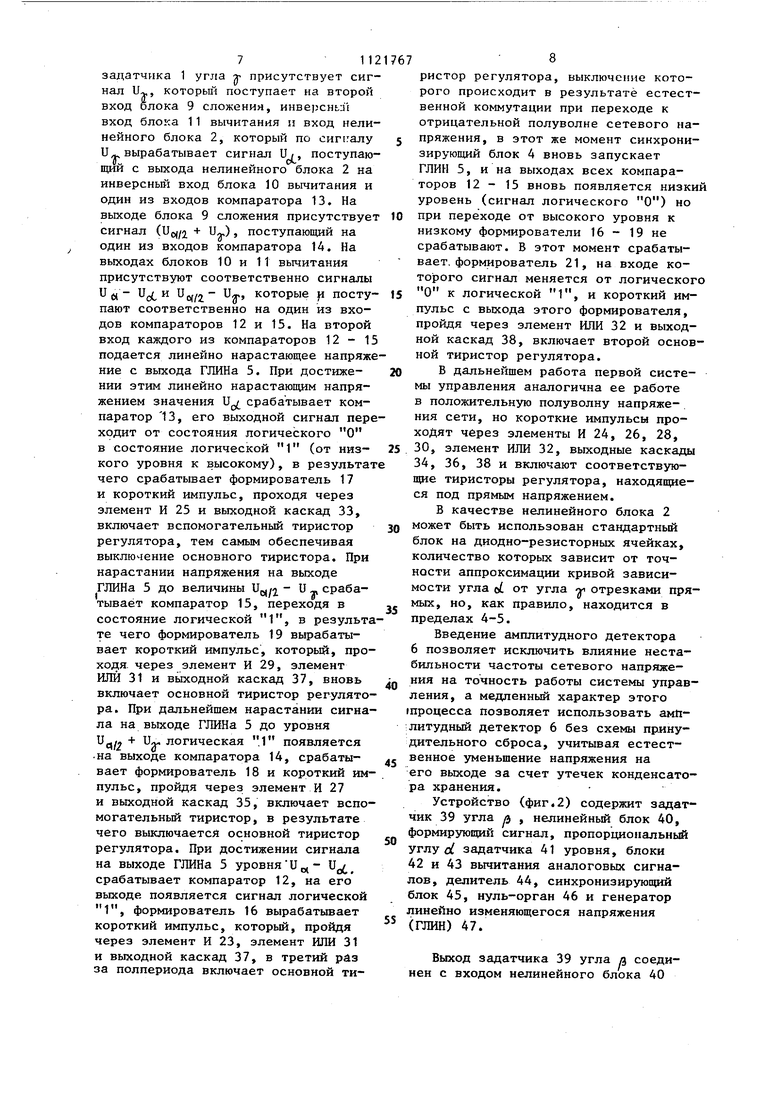

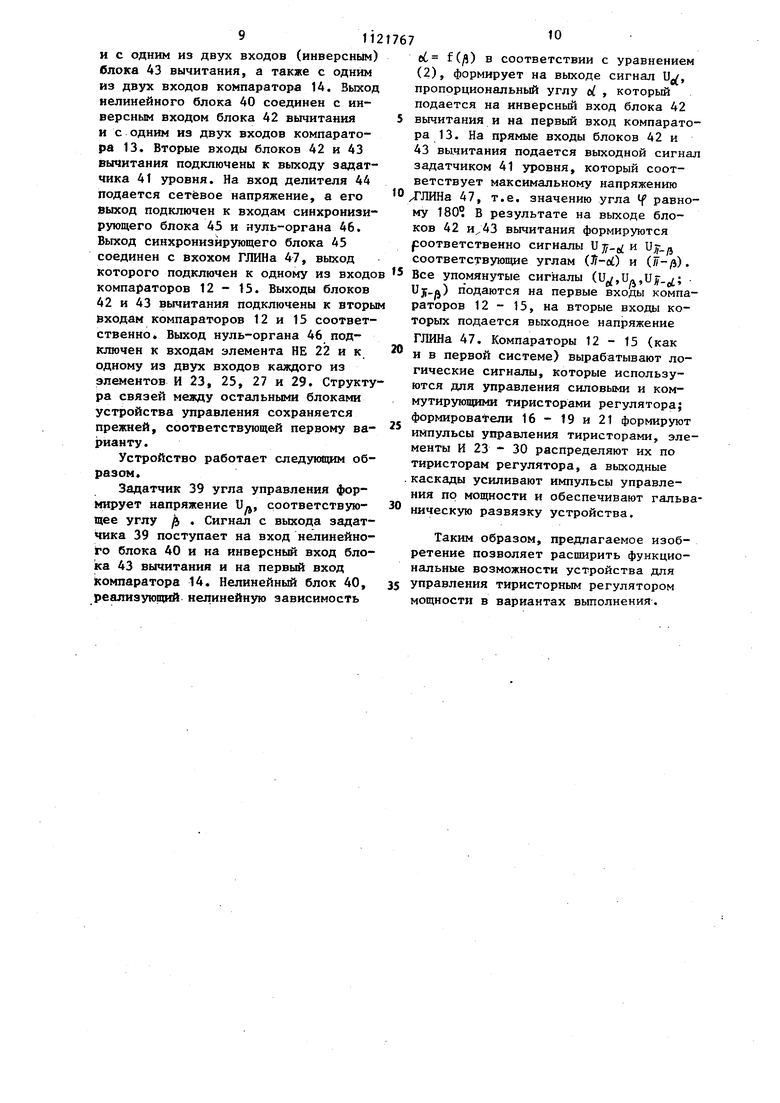

По второму варианту устройство для управления тиристорным регулятором мощности, содержащее задатчик угла управления, синхронизирующий блок, подключенньш к генератору линейноизменяющегося напряжения, нульорган, выходные каскады,снабжено нелинейным блоком, реапизующим функциональную зависимость oL f.(ft) в соответствии с выражением 2 sin 2cfisin 4ci 2 sin 2/i - sin 4уз, задатчиком уровня, двумя блоками вычитания, четырьмя компараторами, шестью формирователями коротких импульсов, четьфьмя парами элементов И, двумя элементами ИЛИ и элементом НЕ, причем выход задатчика угла управления соединен с входом нелинейного блока, с первым входом первого блока вычитания и с первым входом первого компаратора, выход нелинейного блока соединен с первым входом второго блока вычитания и с первым входом второго компаратора, вторые входы блоков вычитания соединены с выходом задатчика уровня, а их выходы соединены с первыми входами третьего и четвертого компараторов, вторые входы компараторов соединены с выходом генерато- линейноизменяющегося напряжения. выход каждого компаратора через соответствующий формирователь коротких импульсов подключен к первым входам элементов И одноименных пар, вторые входы первых элементов И каждой пары соединены с выхЬдом Нуль-органа непосредственно, а вторых элементов И каждой пары - через элемент НЕ, выходы элементов И первой и четвертой пар предназначены для подключения через выходные каскады к управляющим электродам коммутирующих тиристоров, выходы первых элементов И второй и третьей пар подключены к первому и второму входам первого элемента ИЛИ, выходы вторых элементов И этих пар подключены к первому и второму входам второго элемента ИЛИ, третий вход первого элемента ИЛИ через соответствующий формирователь коротких импульсов подключен к выходу нульоргана, третий вход второго элемента ШШ через соответствуюпщй формирователь коротких импульсов - к выходу элемента НЕ, выходы элементов ИЛИ предназначены для подключения к основным тиристорам. На фиг.1 и 2 пок зана схема устройства по первому и второму вариантам соответственно. Устройство (фиг.1) состоит из задатчика 1 угла у, нелинейного бл ка 2, например, стандартного блока с диодно-резисторными ячейками, делителя 3, синхронизирующего блока А генератора 5 линейно изменяющегося напряжения (ГЛИНа), амплитудного детектора 6, делителя 7, нуль-органЯ 8, блока 9 сложения аналоговых сигналов, блоков 10 и 11 вычитания аналоговых сигналов, компараторов 1 15, формирователей 16-21 коротких импульсов из фронта сигнала, элемен та НЕ 22, элементов И 23 - 30, элементов ИЛИ 31 и 32 и выходных каскадов 33 - 38. Выход задатчика 1 угла у соединен с входом нелинейного блока 2 и с одним из двух входов блоков сложения 9 и вычитания 11, причем данный вход блока вычитания является инверсным, т.е. сигнал, поступающий на данный вход, берется со знаком минус. Вторые входы блоков сложения 9 и вычитания 11 подключены к выходу делителя 7. Выход нелинейного блока 2 соединяется с инверсным входом блока 10 вычитания и одним из двух входов компаратора 13. На вход делителя 3 подается сетевое напряжение, а выход делителя 3 подключен к входам синхронизирующего блока 4 и нуль-органа 8. Выход синхронизирующего блока 4 соединен с входом ГЛИНа 5, выход которого подключен к входу амплитудйог детектора 6 и к одному из двух входов компараторов 12-15. Выход ампли тудного детектора 6 подключен к входу делителя 7 и к прямому входу блока 10 вычитания. Выход блока 9 сложения подсоединен к второму входу компаратора 14, а выходы блоков 10 и 11 вычитания - к вторым входам ком параторов 12 и 15 соответственно, выходы компараторов 12 - 15 подключены к входам формирователей 16 - 19 соответственно, а выход нуль-органа 8 к входам элемента НЕ 22, формирователя 20 и к одному из двух входов элементов И 23, 25, 27 и 29. Выход элемента НЕ 22 соединен с входом формирователя 21 и с одним из двух входов элементов И 24, 26, 28, 30. Вторые входы элементов И 23 и 24 подключены к выходу формирователя 16, элементов И 25 и 26 - к выходу формирователя 17, элементов И 27, 28 - к выходу формирователя 18, элементов И 29, 30 - к выходу формирователя 19. Выход формирователя 20 подключен к одному из трех входов элемента ИЛИ 31, второй вход которого соединен с выходом элемента Е 29, а третий - с выходом элемента И 23. Выход формирователя 21 соединен с одним из трех входов элемента ИЛИ 32, второй вход которого подключен к выходу элемента И 30, а третий - к выходу элемента И 24. Выходы элементов ИЛИ 31 и 32 подключен соответственно к входам выходных каскадов 37 и 38, а выходы элементов И 25 - 28 к входам выходных каскадов 33 - 36, соответственно. Выходы выходных каскадов 33 - 38 соединены с управляющими электродами тиристоров регулятора мощности. Устройство работает следующим образом. При переходе от отрицательного к положительной полуволне напряжения сети срабатывает нуль-орган 8, выходной сигнал которого изменяется от низкого уровня к высокому (с О на 1), в результате чего изменяется с 1 на О выходной сигнал элемента НЕ 22. При этом разрешается прохождение импульсов через элементы И 23, 25,27 и 29 и блокируется прс хождение импульсов через элементы И 24, 26,28 и 30. Одновременно формирователь 20 формирует короткий импульс положительной полярности, которьй через элемент ИЛИ 31 и выходной каскад 37 поступает на основной тиристор регулятора и включает его. При переходе через О сетевого напряжения синхронизирующий блок 4 вновь запускает ГЛИН 5, а амплитуда напряжения на выходе ГЛИНа в предыдущем полупериоде запоминается амплитудным детектором 6, с выхода которого эта величина (и,,) поступает на прямой вход блока 10 вычитания и вход делителя 7 с постоянным коэффициентом -деленияу равным 2. С выхода делителя 7 сигнал U поступает на один из входов блока 9 сложения и прямой вход блока 11 вычитания. На выходе 711 задатчика 1 угла у присутствует сигнал U-,, который поступает на второй вход блока 9 сложения, инверснъм вход блока 11 вычитания и вход нелинейного блока 2, который по сиггалу и«, вырабатывает сигнал U/, поступающий с выхода нелинейного блока 2 на инверсный вход блока 10 вычитания и один из входов компаратора 13, На выходе блока 9 сложения присутствует сигнал (ис(д + U,j,), поступающий на один из входов компаратора 14. На выходах блоков 10 и 11 вычитания присутствуют соответственно сигналы и « d- о(/г у которые поступают соответственно на один из входов компараторов 12 и 15. На второй вход каждого из компараторов 12 - 15 подается линейно нарастающее напряже ние с выхода ГЛИНа 5. При достижении этим линейно нарастающим напряжением значения U срабатывает компаратор 13, его выходной сигнал пере ходит от состояния логического О в состояние логической 1 (от низкого уровня к высокому), в результат чего срабатывает формирователь 17 и короткий импульс, проходя через элемент И 25 и выходной каскад 33, включает вспомогательный тиристор регулятора, тем самым обеспечивая выключение основного тиристора. При нарастании напряжения на выходе ГЛИНа 5 до величины x срабатывает компаратор 15, переходя в состояние логической 1, в результа те чего формирователь 19 вырабатывает короткий импульс, который, проходя, через элемент И 29, элемент ИЛИ 31 и выходной каскад 37, вновь включает основной тиристор регулятора. При дальнейшем нарастании сигнала на выходе ГЛИНа 5 до уровня Ug,/. + V логическая 1 появляется на выходе компаратора 14, срабатывает формирователь 18 и короткий импульс, пройдя через элемент И 27 и выходной каскад 35, включает вспомогательный тиристор, в результате чего выключается основной тиристор регулятора. При достижении сигнала на выходе ГЛИНа 5 уровняи, U. срабатывает компаратор 12, на его выходе появляется сигнал логической 1, формирователь 16 вырабатывает короткий импульс, который, пройдя через элемент И 23, элемент ИЛИ 31 и выходной каскад 37, в третий рАз за полпериода включает основной ти8ристор регулятора, выключение которого происходит в результате естественной коммутации при переходе к отрицательной полуволне сетевого напряжения, в этот же момент синхронизирующий блок 4 вновь запускает ГЛИН 5, и на выходах всех компараторов 12 - 15 вновь появляется низкий уровень (сигнал логического О) но при переходе от высокого уровня к низкому формирователи 16 - 19 не срабатывают. В этот момент срабатывает, формирователь 21, на входе которого сигнал меняется от логического О к логической 1, и короткий импульс с выхода этого формирователя, пройдя через элемент ИЛИ 32 и выходной каскад 38, включает второй основной тиристор регулятора. В дальнейшем работа первой системы управления аналогична ее работе в положительную полуволну напряже-. ния сети, но короткие импульсы проходят через элементы И 24, 26, 28, 30, элемент ИЛИ 32, выходные каскады 34, 36, 38 и включают соответствующие тиристоры регулятора, находящиеся под прямым напряжением. В качестве нелинейного блока 2 может быть использован стандартный блок на диодно-резисторных ячейках, количество которых зависит от точности аппроксимации кривой зависимости угла о( от угла -у отрезками прямых, но, как правило, находится в пределах 4-5. Введение амплитудного детектора 6 позволяет исключить влияние нестабильности частоты сетевого напряжения на точность работы системы управления, а медленный характер этого процесса позволяет использовать амплитудный детектор 6 без схемы принудительного сброса, учитывая естественное уменьшение напряжения на его выходе за счет утечек конденсатора хранения. Устройство (фиг.2) содержит задатчик 39 угла л , нелинейный блок 40, формирующий сигнал, пропорциональный углу 0 задатчика 41 уровня, блоки 42 и 43 вычитания аналоговых сигналов, делитель 44, синхронизирующий блок 45, нуль-орган 46 и генератор линейно изменяющегося напряжения (ГЛИН) 47. Выход задатчика 39 угла я соединен с входом нелинейного блока 40

и с одним из двух входов (инверсным) блока 43 вычитания, а также с одним из двух входов компаратора 14. Выход нелинейного блока 40 соединен с инверсным входом блока 42 вычитания и с одним из двух входов компаратора 13. Вторые входы блоков 42 и 43 вычитания подключены к выходу задатчика 41 уровня. На вход делителя 44 подается сетевое напряжение, а его выход подключен к входам синхронизирующего блока 45 и нуль-органа 46. Выход синхронизирующего блока 45 соединен с вхохом ГЛИНа 47, выход которого подключен к одному из входо компараторов 12 - 15. Выходы блоков 42 и 43 вычитания подключены к вторы входам компараторов 12 и 15 соответственно. Выход нуль-органа 46 подключен к входам элемента НЕ 22 и к одному из двух входов каждого из элементов И 23, 25, 27 и 29. Структура связей между остальными блоками устройства управления сохраняется прежней, соответствующей первому варианту.

Устройство работает следукмцим образом.

Задатчик 39 угла управления формирует напряжение U, соответствующее углу jb . Сигнал с выхода задатчика 39 поступает на вход нелинейного блока 40 и на инверсный вход блока 43 вычитания и на первый вход Компаратора 14. Нелинейный блок 40, реализующий нелинейную зависимость

е f() в соответствии с уравнением (2), формирует на выходе сигнал Uj, пропорциональный углу at , который подается на инверсный вход блока 42

вычитания и на первый вход компаратора 13. На прямые входы блоков 42 и 43 вычитания подается выходной сигнал задатчиком 41 уровня, который соответствует максимальному напряжению

47, т.е. значению угла if равному 180° В результате на выходе блоков 42 вычитания формируются соответственно сигналы и Uj- соответствующие углам (J/-oi) и (л-).

5 Все упомянутые сигналы (U,Ua, Uy.ft) подаются на первые входы компараторов 12 - 15, на вторые входы которых подается выходное напряжение

ГЛИНа 47. Компараторы 12-15 (как и в первой системе) вырабатывают логические сигналы, которые используются для управления силовыми и коммутирующими тиристорами регулятора; формирователи 16 - 19 и 21 формируют импульсы управления тиристорами, элементы И 23 - 30 распределяют их по тиристорам регулятора, а выходные каскады усиливают импульсы управления по мощности и обеспечивают гальваническую развязку устройства.

Таким образом, предлагаемое изобретение позволяет расширить функциональные возможности устройства для управления тиристорным регулятором мощности в вариантах вьшолнеиия.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Поскробко А.А., Вратолюбов В.В | |||

| Бесконтактные коммутирующие и регулирующие устройства, М., Энергия, 1978, с, 21 | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Там же, с, 48-50. | |||

Авторы

Даты

1984-10-30—Публикация

1982-07-21—Подача