2. Устройство по п. 1, отличающееся тем, что, с целью повьшения точности задания режима испытаний, последовательно с диодом ячейки включены соединенные параллельно дополнительные диод и накопительный реактор, причем дополни1128203

тельный диод подключен по отношению к полюсам источника питания идентично диоду -ячейки.

3. Устройство по пп. 1 и 2, отличающееся тем, что . при испытании транзисторов одинаковым током К N /2 .

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ПИТАНИЯ НАГРУЗКИ ПОСТОЯННЫМ ТОКОМ | 1989 |

|

RU2031512C1 |

| РЕГУЛЯТОР ПОСТОЯННОГО НАПРЯЖЕНИЯ И СПОСОБ УПРАВЛЕНИЯ ИМ | 2019 |

|

RU2713464C1 |

| Автоматическая фотовспышка | 1987 |

|

SU1510111A1 |

| Импульсный регулятор постоянного напряжения | 2018 |

|

RU2689804C1 |

| Устройство для нагрузочных испытаний силовых транзисторов | 1980 |

|

SU938217A1 |

| ВЫСОКОВОЛЬТНЫЙ ПРЕОБРАЗОВАТЕЛЬ НАПРЯЖЕНИЯ | 2002 |

|

RU2231903C2 |

| Устройство для испытания силовых транзисторов | 1980 |

|

SU920584A1 |

| ПРЕОБРАЗОВАТЕЛЬ ЧАСТОТЫ | 2020 |

|

RU2751534C1 |

| ТЯГОВЫЙ ЭЛЕКТРОПРИВОД ПОСТОЯННОГО ТОКА | 1994 |

|

RU2100222C1 |

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ СИЛОВЫМ ТРАНЗИСТОРНЫМ КЛЮЧОМ | 1997 |

|

RU2133553C1 |

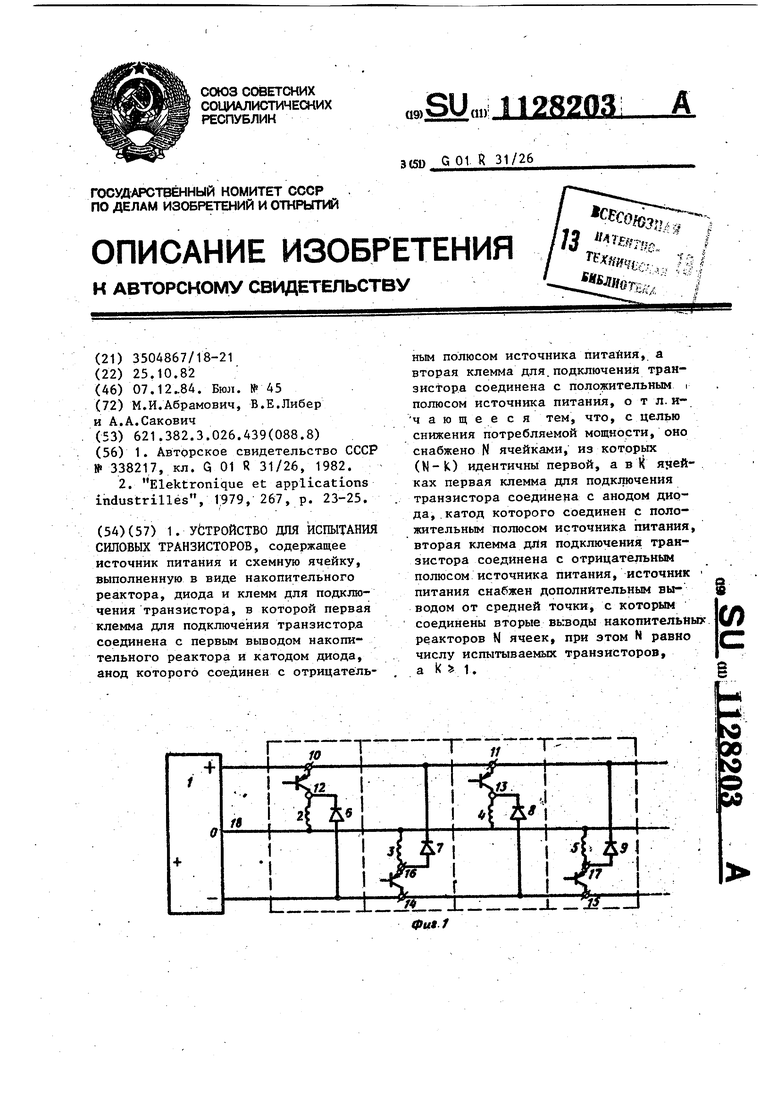

1.УЬТРОЙСТВО ДОЯ ИСПЫТАНИЯ СИЛОВЫХ ТРАНЗИСТОРОВ, содержащее источник питания и схемную ячейку, выполненную в виде накопительного реактора, диода и клемм для подключения транзистора, в которой первая клемма для подключения транзистора соединена с первым выводом накопительного реактора и катодом диода, анод которого соединен с отрицатель о/е 4f J3 17 /tC.-;,. 111 ным полюсом источника питайия, а вторая клемма для.подключения транзистора соединена с положительным i полюсом источника питания, о т л. ичающееся тем, что, с целью снижения потребляемой мощности, оно снабжено N ячейками, из которьпс (N-fc) идентичны первой, а в янейках первая клемма для подключения транзистора соединена с анодом дирда, катод которого соединен с положительным полюсом источника питания, вторая клемма дЯя подключения транзистора соединена с отрицательным полюсом источника питания, источник питания снабжен дополнительным выводом от средней точки, с которым (Л соединены вторые выводы накопительные реакторов N ячеек, при этом N равно числу испытываемых транзисторов, а К 1.

Изобретение относится к силовой электронике и может быть использовано для нагрузочных испытаний сИ ловых транзисторов в режиме насы-, щения - одном из основных режимов и ,работы. ,.

Известно устройство для нагрузочных испытаний силовых транзисторов в режиме насыщения, содержащее два источника испытательного Тока, один источник испытательного напряжения и одинаковые схемные ячейки, соединенные между.собой последовательно образующие четьфе контура из диодов и испытьюаемых транзисторор l .

К недостаткам такого .устройства можно отнести то, что одновременно должны испытываться не менее 12-16 транзисторов, транзисторы и диоды, входящие в каждый контур, должны по бираться по йрямому падению напряжения, на всех транзисторах может быть задан один: режим испытаний.

Наиболее близким техническим решением к изобретению является устройство, содержащее источник питания постоянным напряжением, нагрузочное -сопротивление и схемную ячейку.из соединенных в общей точке накопительного реактора, диода и испытываемого транзистора, первая клемма для подключения транзистора соединена с первым выводом накопительного реактора и катодом диода, анод которого соединен с отрицатель ньтм полюсом источника питания z .

Такое устройство имеет чрезмерньй расход электроэнергии и значительную массу и габариты, так как источник питания и нагрузочное сопротивление должны соответствовать суммарной мощности испытываемых тразистаров.

Цель изобретения - уменьшение потребляемой мощности. .

Поставленная цель достигается тем, что устройство для испытания силовых транзисторов, содержащее источник питания и схемную ячейку, выполненную в виде накопительного реактора, диода и клемм для подключения транзистора , в которой первая клемма для подключения транзистора соединена с первым накопительного реактора и катодом диода, анод которого соединен с отрицательным полюсом источника питания, а вторая клемма для подключения транзистора соединена с положительным полюсом ис-точиика питания ..снабжено N ячейками, из которых (N-K) идентичны первой, а в К ячейках первая клемма для подключения транзистора соединена с анодом диода, катод которого соединен с положитель Hbgi полюсом источника питания, вторая клемма для подключения транзистора соединена с отрицательным полюсом источника питания, источник питания снабжен дополнительным выводом от средней точки с которьм соединены вторые выводы накопительных реакторов N ячеек, при этом N равно числу испытываемых транзисторов, а К 1.

Кроме Toroi с целью повьппенйя точности задания режима испытаний, поседовательно с диодом ячейки включены соединенные параллельно дополнительные диод и накопительный реактор, причем дополнительньй диод подключен по отношению к полюсам источника питания идентично диоду ячейки.

Кроме того, при испытании транзисторов одинаковым током К N/2.

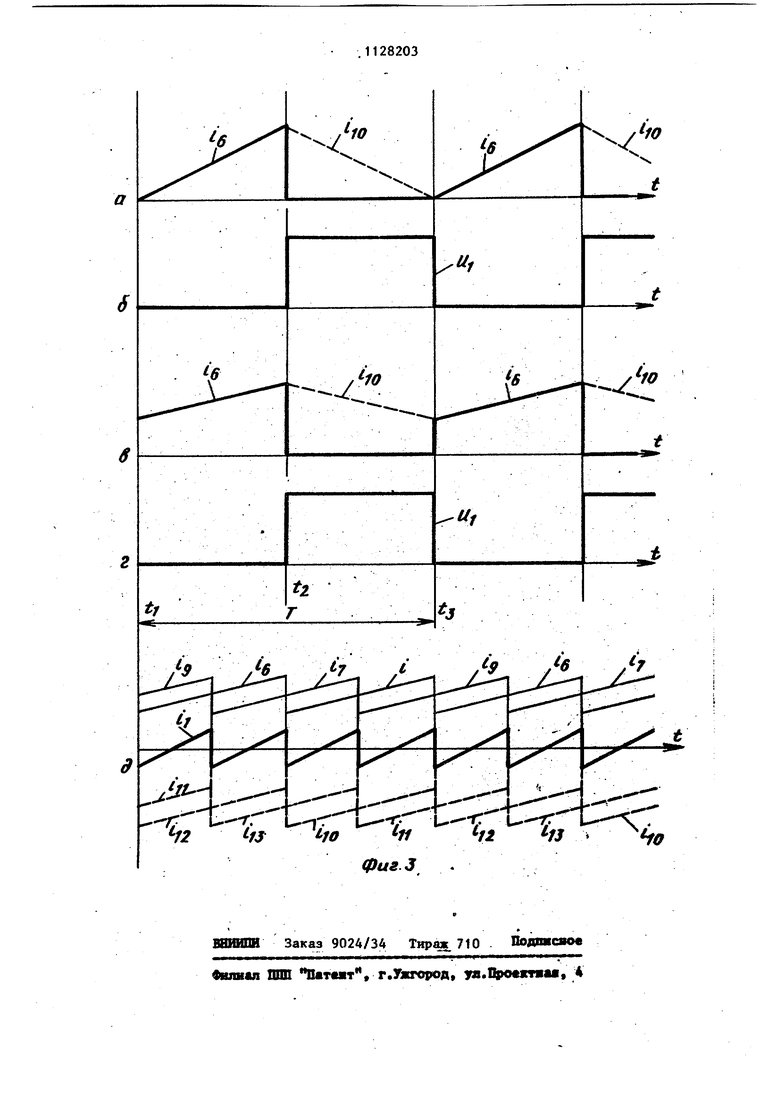

На фиг. t показана принципиальная схема устройства; на фиг. 2 - принципиальная схема устройства: с дополнительными диодами и реакторами; на фиг. 3 - эпюры токов и напряжений на испытываемых транзисторах, эшоры токов накопительных реакторов и эпюры тока, потребляемого от источника питания.

Устройство для испытания силовых транзисторов (фиг. 1) содержит источник 1 питания и четыре ячейки, каждая ячейка содержит накопительный реактор 2-5, диод 6-9 и клеммы для подключения транзистора, в двух ячей-t5 ках первая клемма 10, 11 для подключения транзистора соединена с первым выводом накопительного реактора и катодом диода, анод которого соединен с отрицательным полюсом источника 1 20 питания,, а вторая клемма 12, 13 для подключения транзистора,,- с положительным полюсом источника 1 питания В двух других ячейках первая клемма для подключения транзистора -14, 15 соединена с анодом диода, катод которогосоединен с Положительным полюсом источника 1 питания, а вторая клемма 16, 17 для подключения . транзистора - с отрицательным полюсом источника 1 питания, источник 1 питания снабжен дополнительньм выводом 18 от средней точки, с кото рым соединены вторые выводы накопительных реакторов ячеек. На фиг. 2, кроме того, последова тельно с диодами 6-9 включены соеди ненные попарно параллельно дополнительные диоды 19-22 и реакторы 23-26. Работа устройства приведена на примере первой ячейки. В момент i отпирается транзистор и через него накопительньй реактор ,2 начинает постепенно нарастать испытателънь1й. ток tj (фиг. За). В момент 12 транзистор запираетс ток Ц обрьгаается, а накопительного реактора 2 (ток сброса) на нает убывать, протекай в том же нап равлении по цепи: диод 6 - накопите ный реактор 2 и вьшод 18. При эхом на интервале i2 через диод 6 к транзистору прикладывается испыта тельное н апряжение 0) источника 1 питания (фиг., 3 б). В момент tj , когда убывающий ток о становится равным нулю, снова отп

рается транзистор, ток начинает нарастать и цикл работы повторяется с периодом Т t:j-ti.

В описанном режиме ток транзистора 1/ в момент отпирания равен нулю, а следовательно, и потери при включении можно принять равными нулю.

Если требуется испытывать транзисторы с учетом как коммутационных потерь привыключении, так и потерь при включении, то транзистор отпирают в моменты ,iv Ц и т.д. (фиг. 3 в), когда убывающий ток 1 -накопительного реактора 2 не достиг нулевого значения. В последнем режиме при отпирании транзистор может испытывать значительное дополнительное воздействие за счет обратного тока диода 6, например при испытании, мощных высоковольт ных транзисторов, когда в качестве диода 6 не может быть использован диод Шоттки или быстродействующий диод, имеющие относительно небольшой выброс обратного тока. Для ограничения такого воздействия .последовательно в цепь диода 6 включены соединенные попарно параллельно дополнительые диод 9 и реактор 23 (фиг. 2). На интервале t, - t 2 устройство работает так, как описано. В момент ia транзистор запирается и ток сброса начинает протекать по соединенным последовательно диодам 6 и 19, а в реакторе 23 появляется постепенно нарастающий ток i , который, достигая величины Q , приводит к выключению диода 19. Запирающая способность диода 19 восстанавливается и в Момент ia , когда транзистор вновь включается, обратный ток диода 6 протекает через реактор 23 и ограничен. Устройство позволяет проводить не пытания при как больших, так и мёньших напряжениях источника питания. Первое обеспечиваемся, если обмотка реактора 2 имеет отпайку, к которой подключен диод 6, второе - если к отпайке обмоткй подключен силовой электрод испытываемого транзистора Остальные ячейки работают так:-же, как и первая ячейка. Переключение ячеек производится поочередно с интервалом времени T/N. При этом токи сброса накопительных реакторов 2 и А ( i, и i,, ) первой группы ячеек (фиг. 3 д) в значительной Mejpe комПенсяруют потребляемые транзисторами других ячеек испытательные токи. Ток

/ источника 1 питания равен разности мгновенных значений токов сброса и испытательных токов. Источник 1 питания может быть выполнен в виде выпрямителя с емкостным фильтром, емкость которого пропускает переменную составляющую тока (, .Мощность, потребляемая от источника 1 питания, мала по сравнению с мощностью испытываемых транзистч ров и в основном определяется мощностью активных потерь в полупроводниковых и реактивных элементах устройства. Это определяет малый расход электроэнергии и малые массу и габариты. Это особенно важно при одновременном испытании на , надежность большого числа приборов.

В устройстве одновременно может использоваться любое число транзисторов. Для каждого транзистора режим испытаний может быть задан.независимо от режимов испытаний других транзисторов.

.6

.

ho

V

б

(б

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| ПЕТЛЯ ДЛЯ НАКЛАДНЫХ ДВЕРОК МЕБЕЛИ | 0 |

|

SU338217A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Elektronique et applications industrilles, 1:979, 267, p | |||

| Прибор для равномерного смешения зерна и одновременного отбирания нескольких одинаковых по объему проб | 1921 |

|

SU23A1 |

Авторы

Даты

1984-12-07—Публикация

1982-10-25—Подача