Изобретение относится к электронной промышленности и может быть использовано при испытаниях силовых транзисторов. , .

Известны устройства для испытаний силовых транзисторов, одно из которых, позволяющее определять цараметры испытуемых транзисторов путем пропускания кратковременных ишуль : сов тока, содержит источник постоянного напряжения, нагрузочное сотгротивление и блок управления. Два одновременно испытуемых транзистора, подключены параллельно источнику постоянного напряжения через нагрузочное сопротивление цепями эмиттер коллектор, а цепи эмиттер-база транзисторов подключены к блоку управле НИН l .

Недостаток такого устройства заключается в том, что чрезмерные пртег ри мощности в нагрузочном сопротивлении по.зволяют испытывать транзисторы только в кратковременном режиме и поэтому оно не может быть использовано для длительных испытаний. Однако длительные испытания одновременно большого числа силовых транзисторов в режимах, соответствующих реальным условиям их ирименения в схемах

инверторов, необходимы для прогнозирования надежности силовых транзисторов и выявления срока их службы.

Наиболее близким техническим решением к предлагаемому, позволяющим воспроизводить режи1 и, соответствующие реальным условиям применения силовых транзисторов в схемах инверторов, является устройство, содержащее

10 ячейки из соединенных последовательно Пар диодов, анодами подключенных к отрицательному поЛюсу источника постоянного испытательного напряжения, катодами - к его положительно15му полюсу, а общей точкой - к точке соединения эмиттеров и коллекторов пар соединенных последовательно испытуемых транзисторов ячейки, цепи база - эмиттер каждого из которых

20 подключены к блоку управления. Источник постоянного испытательного напряжения может быть выполнен по известной схеме, содержащей, например, силовой трансформатор, выпрямитель

25 и фильтр на стороне выпрямительного тока/ и к нему испытуемые транзисторы подключены через настроечный конденсатор и нагрузочное сопротивление. При таком исполнении устройства,

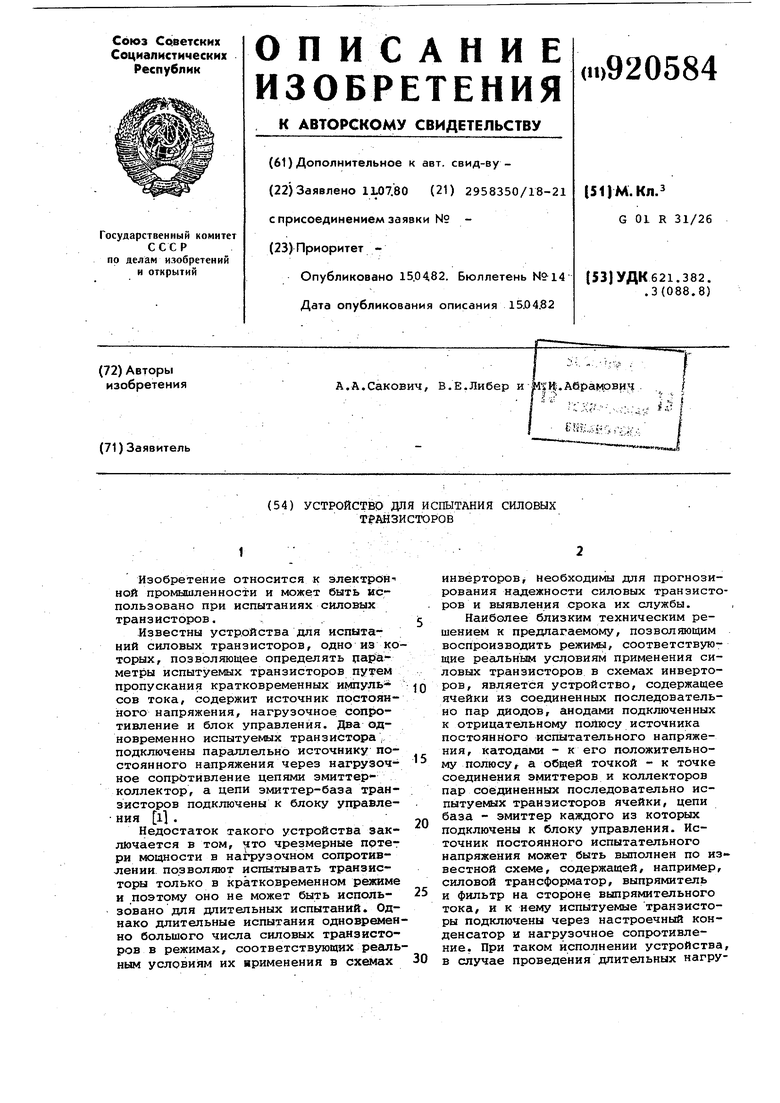

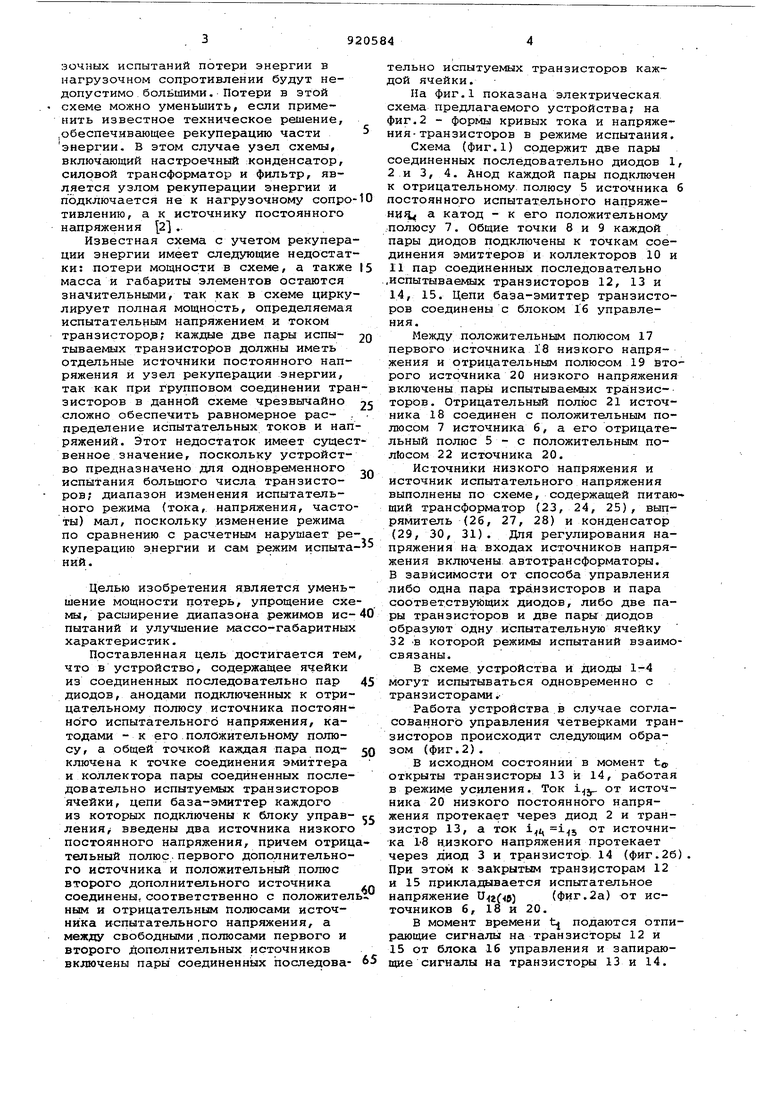

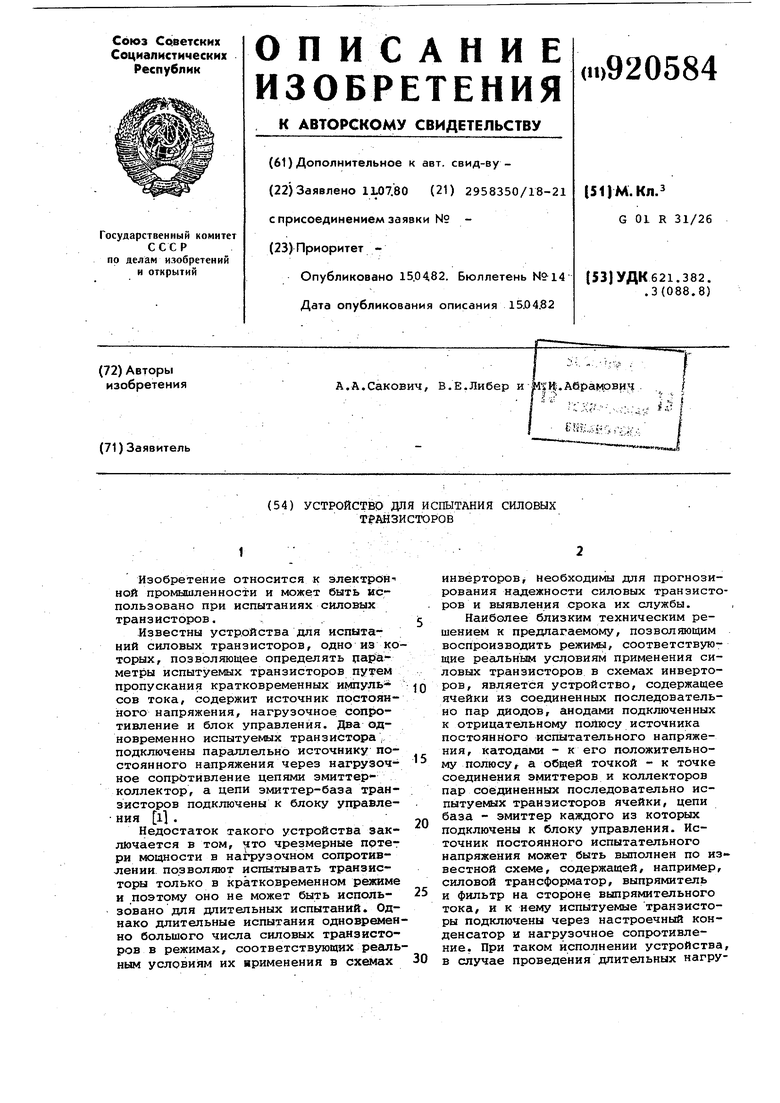

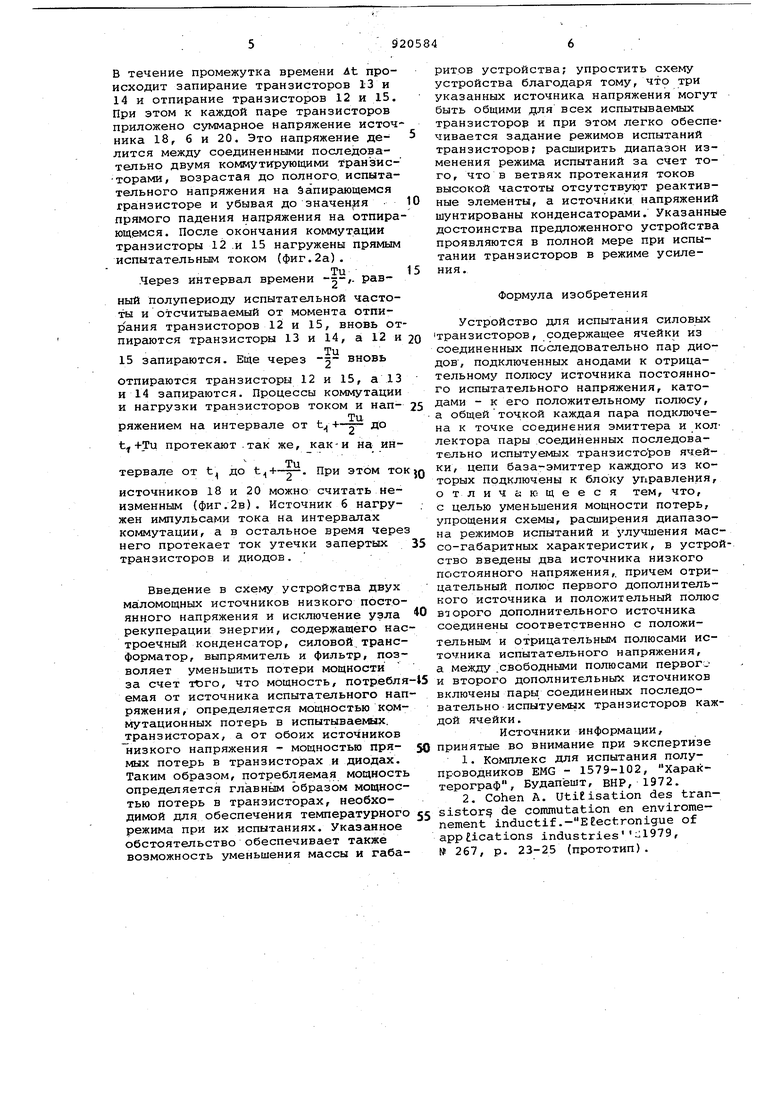

30 в случае проведения длительных нагрузонных испытаний потери энергии в нагрузочном сопротивлении будут недопустимо большими. Потери в этой схеме можно уменьшить, если применить известное техническое решение, .обеспечивающее рекуперацию части энергии. В этом случае узел схемы, включающий настроечный :Конденсатор, силовой трансформатор и фильтр, является узлом рекуперации энергии и подключается не к нагрузочному сопро тивлению, а к источнику постоянного напряжения 2 . Известная схема с учетом рекупера ции энергии имеет следующие недостат ки: потери мощности в схеме, а также масса и габариты элементов остаются значительными, так как в схеме цирку лирует полная мощность, определяемая испытательным напряжением и током транзисторов; каждые две пары испытываемых транзисторов должны иметь отдельные источники постоянного напряжения и узел рекуперации энергии, так как при групповом соединении тра зисторов в данной схеме чрезвычайно сложно обеспечить равномерное распределение испытательных токов и нап ряжений. Этот недостаток имеет сущес венное значение, поскольку устройство предназначено для одновременного испытания большого числа транзисторов; диапазон изменения испытательного режима (тока, напряжения, часто ты) мал, поскольку изменение режима по сравнению с расчетным нарушает ре куперацию энергии и сам режим испыта ний. Целью изобретения является умень шение мощности потерь, упрощение сх мы, расширение диапазона режимов ис пытаний и улучшение массо-габаритны характеристик. Поставленная цель достигается те что в устройство, содержёодее ячейки из соединенных последовательно пар диодов, анодами подключенных к отри цательному полюсу источника постоян ного испытательного напряжения, катодами - к его положительному полюсу, а общей точкой каждая пара подключена к точке соединения эмиттера и коллектора пары соединенных после довательно испытуемых транзисторов ячейки, цепи база-эмиттер каждого из которых подключены к блоку управ ления/ введены два источника низкого постоянного напряжения, причем отриц тельный полюс.первого дополнительно го источника и положительный полюс второго дополнительного источника соединены, соответственно с положител ным и отрицательнЕлм полюсами источника испытательного напряжения, а между свободными.полюсами первого и второго дополнительных источников включены пары соединенных последовательно испытуемых транзисторов каждой ячейки. На фиг,1 показана электрическая схема предлагаемого устройства; на фиг.2 - формы кривых тока и напряжения- транзисторов в режиме испытания. Схема (фиг.1) содержит две пары соединенных последовательно диодов 1, 2 и 3, 4. Анод каждой пары подключен к отрицательному, полюсу 5 источника 6 постоянного испытательного напряженн51 а катод - к его положительному .полюсу 7. Общие точки 8 и 9 каждой пары диодов подключены к точкам соединения эмиттеров и коллекторов 10 и 11 пар соединенных последовательно .испытываемых транзисторов 12, 13 и 14, 15. Цепи база-эмиттер транзисторов соединены с блоком 16 управления, .. Между положительным полюсом 17 первого источника 18 низкого напряжения и отрицательным полюсом 19 второго источника 20 низкого напряжения включены пары испытываемых транзисторов. Отрицательный полюс 21 источника 18 соединен с положительным полюсом 7 источника 6, а его отрицательный полюс 5 - с положительным пол1осом 22 источника 20. Источники низкого напряжения и источник испытательного напряжения выполнены по схеме, содержащей питающий трансформатор (23, 24, 25), выпрямитель (26, 27, 28) и конденсатор (29, 30, 31). Для регулирования напряжения на входах источников напряжения включены автотрансформаторы. В зависимости от способа управления либо одна пара тра.нзисторов и пара соответствующих диодов, либо две пары транзисторов и две пары диодов образуют одну испытательную ячейку 32 .в которой режимы испытаний взаимосвязаны. В схеме устройства и диоды 1-4 могут испытываться одновременно с транзисторами.Работа устройства в случае согласованного управления четверками транзисторов происходит следующим образом (фиг,2). В исходном состоянии в момент to. открыты транзисторы 13 и 14, работая в режиме усиления. Ток от источника 20 низкого постоянного напряжения протекает через диод 2 и транзистор 13, а ток , i.(5 от источника 18 низкого напряжения протекает через диод 3 и транзисто р 14 (фиг.26). При этом к закрытым транзисторам 12 и 15 прикладывается испытательное напряжение ) (фиг.2а) от источников 6, 18 и 20. В момент времени tj подаются отпирающие сигналы на транзисторы 12 и 15 от блока 16 управления и запирающие сигналы на транзисторы 13 и 14. В течение промежутка времени At происходит запирание транзисторов 13 и 14и отпирание транзисторов 12 и 15. При этом к каждой паре транзисторов приложено суммарное напряжение источ ника 18, б и 20. Это напряжение делится между соединенными последовательно двумя коммутирующими транзис торами/ возрастая до полного, испытательного напряжения на Запирающемся транзисторе и убывая до значен 1я прямого падения напряжения на отпира ющемся. После окончания коммутации транзисторы 12 .и 15 нагружены прямым испытательным током (фиг.2а). Ти .Через интервал времени Р ный полупериоду испытательной частоты и отсчитываемый от момента отпирания транзисторов 12 и 15, вновь от пираются транзисторы 13 и 14, а 12 и 15запираются. Еще через -j вновь отпираются транзисторы 12 и 15, al3 и 14 запираются. Процессы коммутации и нагрузки транзисторов током и напряжением на интервале от t ДО протекают .так же, как-и на ин Ти тервале от t до . При этом TO источников 18 и 20 можно считать неизменным (фиг.2в). Источник 6 нагружен импульсами тока на интервалах коммутации, а в остальное время чере него протекает ток утечки заперТЕзИс транзисторов и диодов. Введение в схему устройства двух ма ломощных источников низкого постоянного напряжения и исключение узла рекуперации энергии, содержащего нас троечный конденсатор, силовой,трансформатор, выпрямитель и фильтр, позволяет уменьшить потери мощности за счет того, что мощность, потре6ля емая от источника испытательного нап ряжения, определяется мощностью коммутационных потерь в испытываемых, транзисторах, а от обоих источников низкого напряжения - мощностью прямых потерь в транзисторах и диодах. Таким образом, потребляемая мощность определяется главным образом мощностью потерь в транзисторах, необходимой для обеспечения температурного режима при их испытаниях. Указанное обстоятельство обеспечивает также возможность уменьшения массы и габаТиритов устройства; упростить схему устройства благодаря тому, что три указанных источника напряжения могут быть общими для всех испытываемых транзисторов и при этом легко обеспечивается задание режимов испытаний транзисторов расширить диапазон изменения режима испытаний за счет того, что в ветвях протекания токов высокой частоты отсутствуют реактивные элементы, а источники напряжений шунтированы конденсаторгши. Указанные достоинства предложенного устройства проявляются в полной мере при испытании транзисторов в режиме усиления. Формула изобретения Устройство для испытания силовых транзисторов, содержащее ячейки из соединенных последовательно пар диодов, подключенных анодами к отрицательному полюсу источника постоянного испытательного напряжения, катодами - к его положительному полюсу, а общей точкой каждая пара подключена к точке соединения эмиттера и коллектора пары соединенных последовательно испытуемых транзисторов ячейки, цепи база-эмиттер каждого из которых подключены к блоку управления, отличающееся тем, что, с целью уменьшения мощности потерь, упрощения схемы, расширения диапазона режимов испытаний и улучшения массо-габаритных характеристик, в устройство введены два источника низкого постоянного напряжения,, причем отрицательный полюс первого дополнительного источника и положительный полюс второго дополнительного источника соединены соответственно с положительным и отрицательным полюсами источника испытательного напряжения, а между .свободными полюсами первоги второго дополнительных источников включены пары соединенных последовательно испытуемых транзисторов каждой ячейки. Источники информации, принятые во внимание при экспертизе 1.Комплекс для испытания полупроводников EMG - 1579-102, Характерограф, Будапешт, ВНР, 1972. 2.Cohen А. Utilisation des transistor de commutation en enviromenement inductif.- EEectronigue of applications industries-1979, № 267, p. 23-25 (прототип). J2

18

зг

32

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для нагрузочных испытаний силовых транзисторов | 1980 |

|

SU938217A1 |

| Устройство для испытания силовых транзисторов | 1982 |

|

SU1128203A1 |

| Устройство для нагрузочных испытаний полупроводниковых вентилей | 1975 |

|

SU597998A1 |

| СТАБИЛИЗАТОР ВЫПРЯМЛЕННОГО НАПРЯЖЕНИЯ | 1996 |

|

RU2137284C1 |

| Коммутатор | 1980 |

|

SU949815A1 |

| ПРЕОБРАЗОВАТЕЛЬ ЧАСТОТЫ С РЕГУЛИРУЕМЫМ ВЫПРЯМИТЕЛЕМ НАПРЯЖЕНИЯ | 2019 |

|

RU2732283C1 |

| ИМПУЛЬСНЫЙ СТАБИЛИЗАТОР НАПРЯЖЕНИЯ | 1992 |

|

RU2007825C1 |

| НАГРУЗОЧНО-ПИТАЮЩЕЕ УСТРОЙСТВО | 2009 |

|

RU2406097C1 |

| ТЯГОВЫЙ ЭЛЕКТРОПРИВОД ПОСТОЯННОГО ТОКА | 1994 |

|

RU2100222C1 |

| Импульсный регулятор постоянного напряжения | 1988 |

|

SU1601712A1 |

го ,

I 25

Авторы

Даты

1982-04-15—Публикация

1980-07-11—Подача