1

Изобретение относится к электронной технике и может быть использовано, для нагрузочных испытаний силовых транзисторов.

Известно устройство, позволяющее воспроизводить нагрузочные режимы силовых транзисторов, содержащее две пары соединенных последовательно диодов и две пары соединенных последовательно транзисторов, подключенных свободными концами к источнику испытательного постоянного напряжения, а средними точками через узел, содержащий настроечный конденсатор, трансформатор и фильтрк нагрузочному сопротивлению Ul.

Главным недостатком такого устройства, при проведении длительных испытаний, является неприемлемая величина мощности потерь в .нагрузочном сопротивлении.

Потери можно уменьшить, если применить известное техническое решение, обеспечивающее рекуперацию части энергии потерь. В этом случае узел с настроечным конденсатором, трансформатором и фильтром подключается не к нагрузочному сопротивлению, а к источнику испытательного напряжения.

При таком исполнении устройства мощность потерь, а также масса и габариты его элементов остаются

10 достаточно большими, так как в схеме циркулирует полная мощность, определяемая испытательным током и напряжением транзисторов, диапазон изменения испытательного режима по

15 отношению к расчетному мал из-за возможности нарушения режима рекуперации, кроме того каждые пары испытываемых транзисторов должны иметь отдельные источники испытательного

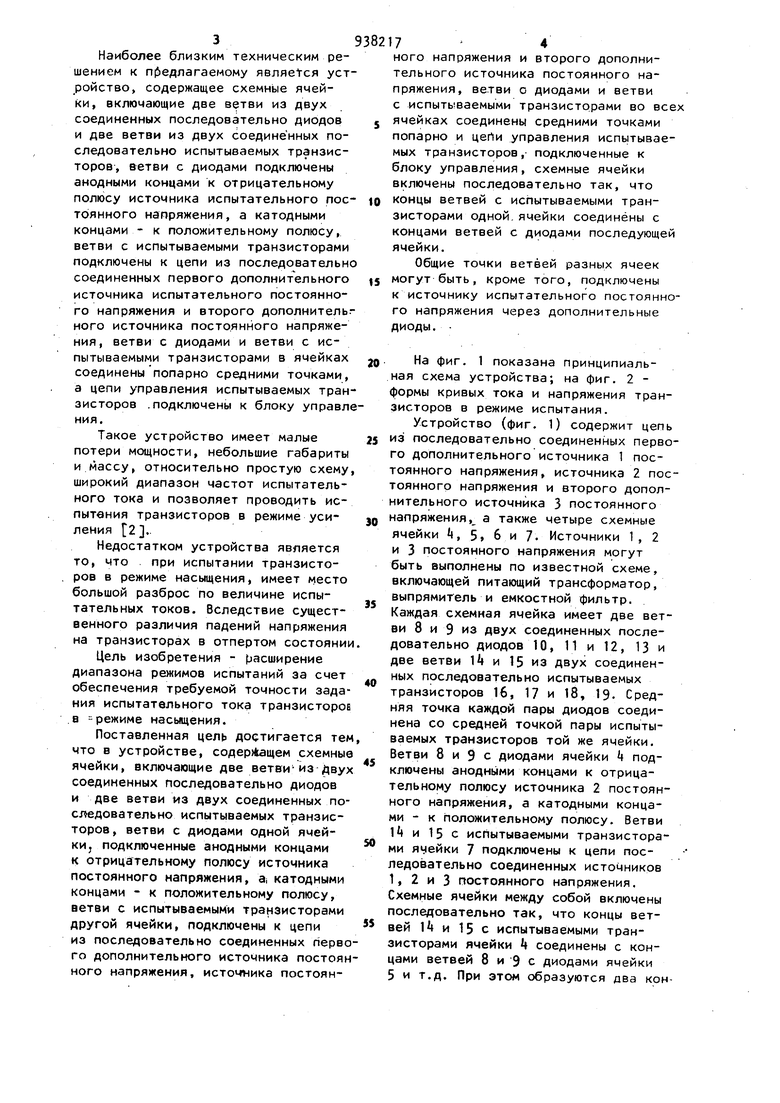

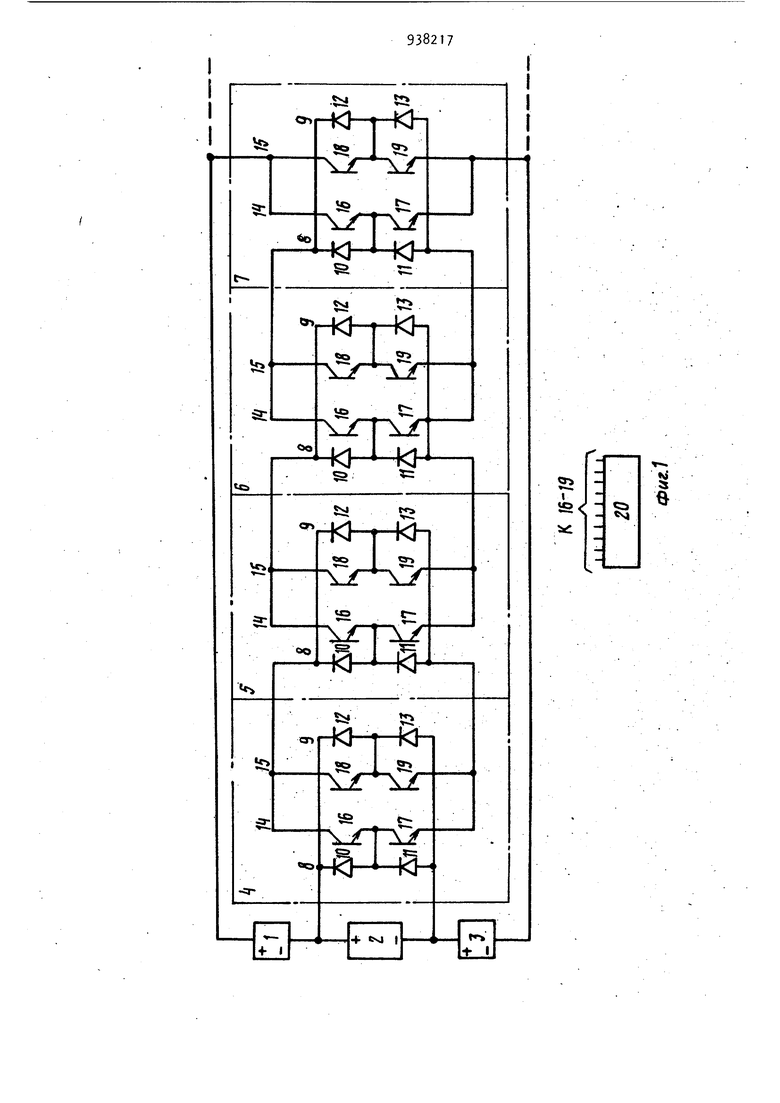

20 напряжения и узел рекуперации энергий для обеспечения равномерного распре деления испытательных токов и напряжений. Наиболее близким техническим решением к предлагаемому является устройство, содержащее схемные ячейки, включающие две ветви из двух соединенных последовательно диодов и две ветви из двух соединенных последовательно испытываемых транзисторов, ветви с диодами подключены анодными концами к отрицательному полюсу источника испытательного постЪянного напряжения, а катодными концами - к положительному полюсу, ветви с испытываемыми транзисторами подключены к цепи из последовательно соединенных первого дополнительного источника испытательного постоянного напряжения и второго дополнитель.ного источника постоянного напряжения, ветви с диодами и ветви с испытываемыми транзисторами в ячейках соединены попарно средними точками, а цепи управления испытываемых транзисторов .подключены к блоку управле ния. Такое устройство имеет малые потери мощности, небольшие габариты и массу, относительно простую схему широкий диапазон частот испытательного тока и позволяет проводить испытания транзисторов в режиме усиления 2.. Недостатком устройства является то, что при испытании транзисторов в режиме насыщения, имеет место большой разброс по величине испытательных токов. Вследствие существенного различия падений напряжения на транзисторах в отпертом состоянии Цель изобретения - расширение диапазона режимов испытаний за счет обеспечения требуемой точности задания испытательного тока транзисторов в режиме насыщения. Поставленная цель достигается тем что в устройстве, содержащем схемные ячейки, включающие две ветви-из Двух соединенных последовательно диодов и две ветви из двух соединенных последовательно испытываемых транзисторов , ветви с диодами одной ячейки, подключенные анодными концами к отрицательному полюсу источника постоянного напряжения, ai катодными концами - к положительному полюсу, ветви с испытываемыми транзисторами другой ячейки, подключены к цепи из последовательно соединенных перво го дополнительного источника постоян ного напряжения, источника постоянного напряжения и второго дополнительного источника постоянного напряжения, ветви о диодами и ветви с испытываемыми транзисторами во всех ячейках соединены средними точками попарно и цег1и управления испытываемых транзисторов,- подключенные к блоку управления, схемные ячейки включены последовательно так, что концы ветвей с испытываемыми транзисторами одной,ячейки соединены с концами ветвей с диодами последующей ячейки. Общие точки ветвей разных ячеек могут быть, кроме того, подключены к источнику испытательного постоянного напряжения через дополнительные диоды. На фиг. 1 показана принципиальная схема устройства; на фиг. 2 формы кривых тока и напряжения транзисторов в режиме испытания. Устройство (фиг. 1) содержит цепь из последовательно соединенных первого дополнительного источника 1 постоянного напряжения, источника 2 постоянного напряжения и второго дополнительного источника 3 постоянного напряжения, а также четыре схемные ячейки i, 5 6 и 7. Источники 1, 2 и 3 постоянного напряжения могут быть выполнены по известной схеме, включающей питающий трансформатор, выпрямитель и емкостной фильтр. Каждая схемная ячейка имеет две ветви 8 и 9 из двух соединенных последовательно диодов 10, 11 и 12, 13 и две ветйи }k и 15 из двух соединенных последовательно испытываемых транзисторов 16, 17 и 18, 19. Средняя точка каждой пары диодов соединена со средней точкой пары испытываемых транзисторов той же ячейки. Ветви 8 и 9 с диодами ячейки k подключены анодными концами к отрицательному полюсу источника 2 постоянного напряжения, а катодными концами - к положительному полюсу. Ветви I и 15 с испытываемыми транзисторами ячейки 7 подключены к цепи последовательно соединенных источников 1, 2 и 3 постоянного напряжения. Схемные ячейки между собой включены последовательно так, что концы ветвей 1 и 15 с испытываемыми транзисторами ячейки k соединены с концами ветвей 8 и 9 с диодами ячейки 5 и т.д. При этом образуются два кон5тура из последовательно соединенны испытываемых транзисторов и диодов Первый контур включает приборы 16 и 10 всех ячеек, второй - прибо 18и 12, третий - приборы 11 и 17, четвертый - приборы 13 и 19. Первы два контура подключены к первому дополнительному,источнику 1 постоя ного напряжения, а вторые два конт ра - к второму дополнительному источнику 3 постоянного напряжения. Цепи управления испытываемых транзисторов 16-19 подключены к блоку 20 управления. Работа устройства происходит следующим образом. В момент времени tjj открыты тра зисторы 16 и 19 ячеек k-J. Испытательный ток от дополнител ного источника 1 протекает по пёрв му контуру, из последовательно сое диненных транзисторов 16 и диодов 10 (фиг. 2а), а испытательный ток второго дополнительного источника протекает по четвертому контуру и Зх соединенных последовательно транзисторов 19 и диодов .13 всех ячеек. Через открытые транзисторы 16 и диоды 10 к закрытым транзисторам 17 и 18 прикладывается плюс а через отпертые tpaнзиcтopa 19 и диоды 13 минус испытательного напряжения от цепи из трех исто НИКОВ 1, 2 и 3 постоянного напряжения. На интервале времени 5 O под действием сигналов блока 20 управления пара открытых транзисторов 16и 19, например, в ячейке 6, зап рается, а пара закрытых транзистор 17и 18 отпирается. При этом напряжение цепи с источниками 1, 2 и 3 делится.между отпирающимися и запирающимися транзисторами, возрастая до полного испытательного, напряжени на транзисторах 16 и 19 и убываяi транзисторах 17 и 18 до величины, равной их прямому падению напряжени в открытом состоянии (фиг. 2а, б) Ток запираемых транзисторов 16, 19убь1вает до нуля, а отпираемых транзисторов17, 18 возрастает до величины испытательного тока. Спустя время равное полупериоду - испытательного тока от.момента t (момент t) в ячейке 6 вновь отпираются транзисторы 16 и 19 транзисторы 17 и 18 запираются. В момент ti коммутация заканчивается 76 Спустя время Tj, момента t (момент Ы вновь отпираются транзисторы 17 и 18, а транзисторы 16 и 19 запираются. Далее процесс повторяется с периодом Tj. Процесс коммутации пар транзисторов, и-нагрузка из испытательным током и напряжением в остальных ячейках происходит аналогично описанному выше. Для получения требуемой мощности потерь в испытываем1з(х транзисторах, моменты коммутации транзисторов в разных ячейках не должны совпадать. В противном случае испытательное (коммутирующее) напряжение будет делиться между всеми парами одновремённо коммутируемых транзисторов. Требуемая мощность потерь в испытываемых транзисторах при одновременной коммутации их в разных ячейках может быть обеспечена, если общие точки ветвей разных ячеек подключены к источнику 2 постоянного напряжения через дополнительные диоды. Ток каждого из источников 1 и 3 можно считать неизменным и равным току одного испытываемого транзистора, а напряжение - равным сумме падения напряжения на отпертых приборах одного контура. Напряжение источника 2 составляет основную долю испытательного напряжения одного транзистора, а ток на межкоммутационных интервалах равен току утечки запертых транзисторов и диодов, а на интервалах коммутации - импульсам сквозного тока (рис. 2в) через ветви 14, 15 с транзисторами при их коммутации. Включение всех схемных ячеек устройства последовательно и создание при этом четырех контуров из последовательно соединенных нескольких диодов и нескольких испытываемых транзисторов позволяет, несмотря на различия падений напряжения на отдельных приборах при протекании испытательного тока, получить достаточно близ| ие по величине суммарные падения напряжения на контурах. Это позволяет, при питании от общего источника постоянного напряжения, задать в каждом контуре испытательный ток транзисторов в режиме насыщения с требуемой точность и тем самым расширить диапазон режимов испытаний. Формула изобретения Устройство для нагрузочных испытаний силовых транзисторов, со793

держащее схемные ячейки, включающие две ветви из двух соединенных последовательно диодов и две ветви из двух соединенных последовательно испытываемых транзисторов, ветви с диодами одной ячейки подключены анодными концами к отрицательному полюсу источника постоянного напряжения, а катодными концами - к поло жите/ ьному полюсу, ветви с испытываемыми транзисторами другой ячейки подключены к цепи из последовательно соединенных первого дополнительного источника постоянносо напряжения, источника постоянного напряимения и второго дополнительного источника постоянного напряжения, вет ви с диодами и ветви с испытываемыми 1 транзисторами во всех ячейках соединены средними точками попарно,

8

а цепи уп|)авления испытываемых транзисторов подключены к блоку управления, отличающееся тем, что, с целью расширения диапазона режимов испытаний) схемные ячейки включены последовательно так, что концы ветвей с испытательными транзисторами одной ячейки соединены с концами ветвей с диодами последующей ячейки.

Источники информации, принятые во внимание при экспертизе

1.А. Cohen.. Uti1Isation des Transistor de commutatfon en environement inductif Electronigue

of appiications Industielles, 1979, № 267, p. 23-25, рис, 6.

2.Авторское свидетельство СССР

no заявке № 2958350/21, кл. G 01 R 31 1980.

в

Cf/(f/a)J

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для испытания силовых транзисторов | 1980 |

|

SU920584A1 |

| Устройство для испытания силовых транзисторов | 1982 |

|

SU1128203A1 |

| Устройство для испытания вентилей | 1976 |

|

SU661434A1 |

| Устройство для испытаний полупроводниковых вентилей | 1977 |

|

SU661438A1 |

| Устройство для нагрузочных испытаний полупроводниковых вентилей | 1975 |

|

SU597998A1 |

| УСТРОЙСТВО ДЛЯ ИСПЫТАНИЯ ВЕНТИЛЬНЫХ ПРИБОРОВ | 1972 |

|

SU436302A1 |

| Преобразователь постоянного напряжения в переменное (его варианты) | 1982 |

|

SU1141540A1 |

| Инвертор | 1976 |

|

SU623244A1 |

| АКТИВНЫЙ ДЕМПФЕР | 2015 |

|

RU2703717C2 |

| Источник питания для технологических установок постоянного тока | 1990 |

|

SU1742968A1 |

Pwe7

Авторы

Даты

1982-06-23—Публикация

1980-08-04—Подача