Изобретение относится к электроизмерениям и может быть использовано в многоцелевых измерительных преобразователях сигналов произвольной формы.

Известен измерительный преобразователь, содержащий множительный блок, оба входа умножения которого подключены к входной шине, вход деления - к выходной шине, а выход через резистор к первому входу дифференциального усилителя и через конденсатор - к. общей шине, выход дифференциального усилителя подключен к выходной шине и второму входу дифференциального усилителя 1.

Недоста тком известного измерительного преобразователя являются его ограниченные функциональные возможности, так как он предназна чен только для преобразования сигнала по уровню среднеквадратическог значения.

Наиболее близким по технической сущности к изобретению является измерительный преобразователь, содержащий множительный блок, первый дифференциальный усилитель, к одному из входов которого подключен первый резистор и обкладка первого конденсатора, другая обкладка которого соединена с выходом первого дифференциального усилителя, второй усилитель, выход которого через второй резистор подключен к первому входу первого сумматора, а вход к вькодной 1шне, связанной через первый диод с выходом первого дифференциального усилителя, а через третий резистор - с первым входом второго сумматора, при этом каждьй первый выход каждого из сумматоров через резистор подключен к выходу сЬответственно третьего и четвертого усилителя, входы которых подключены к входной шине, выходы сумматоров соединены соответственно с эходами пятого и шестого усилителей а выходы пятого и шестого усилителей подключены к первому и второму входам множительного блока, выход которого соединен со свободным выхо дом первого резистора, кроме того, первый конденсаторзашунтирован вторым диодом, включенным согласно с первым диодом 2.

Недостаток такого, устройства ограниченные функциональные возможности.

132244г

Цель изобретения - расширение функциональных возможностей.

Поставленная цель достигается тем, что в измерительный преобразо5 ватель сигналов, содержащий множительный блок, первьй дифференциальный усилитель, первый вход которого соединен с его выходом через первый .конденсатор, а также непосредствен10 но - с первым резистором, второй

усилитель, второй резистор, допол нительно введены три двухпозиционных коммутатора, источник опорного напряжения, управляемый блок выборкиfS хранения, блок управления и второй конденсатор, при этом второй усилитель выполнен с управляемым коэффициентом усиления, первый вход первого коммутатора соединен с входной

20 шиной, его второй вход - с выходной шиной и выходом управляемого блока выборки-хранения, выход - с первым входом второго коммутатора и первым входом множительного блок-а, второй

5 вход второго коммутатора соединен с источником опорного напряжения, а выход - со .вторым входом множительного блока, выход которого подключен к входу второго усилителя, вы0 ход которого соединен с входом

третьего коммутатора, первый выход которого соединен со свободным выводом первого резистора, а второй через второй резистор со вторым

входом первого дифференциального усилителя, соединенным через второй ,конденсатор с общей шиной, выход первого дифференциального усилителя подключен к входу блока выборки-хра- нения, а соответствующие выходы

блока управления соединены с управляющими входами коммутаторов, второ го усилителя и блока выборки-хранения.

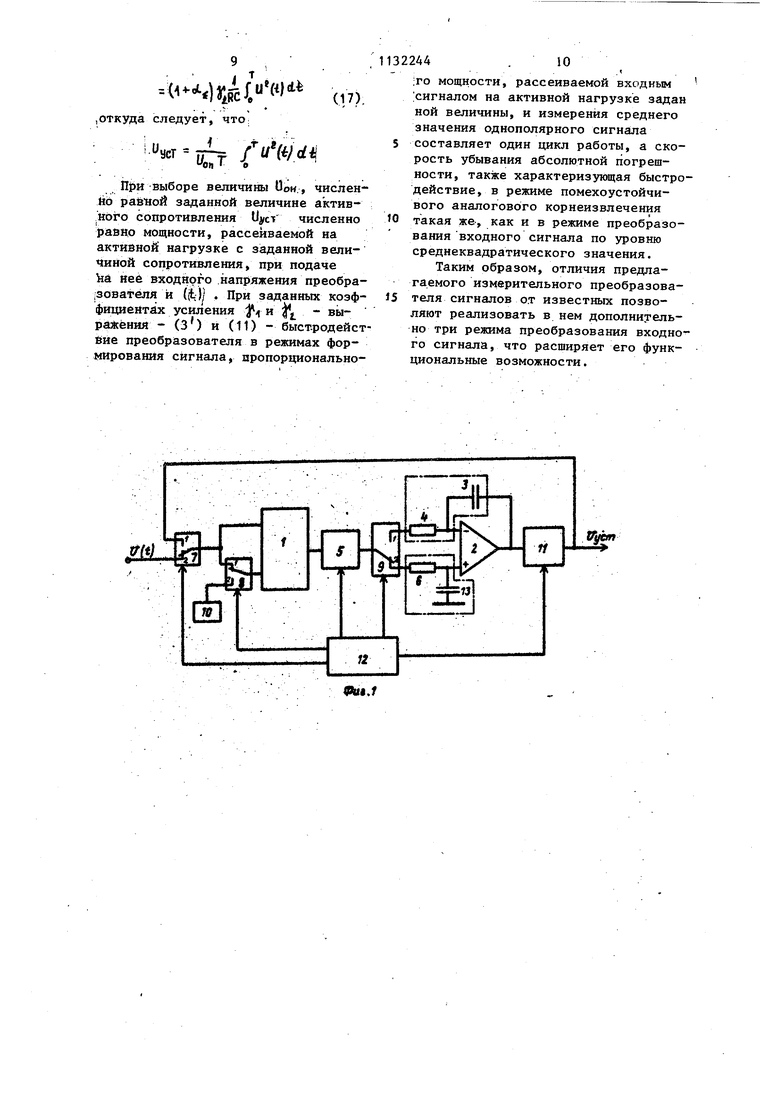

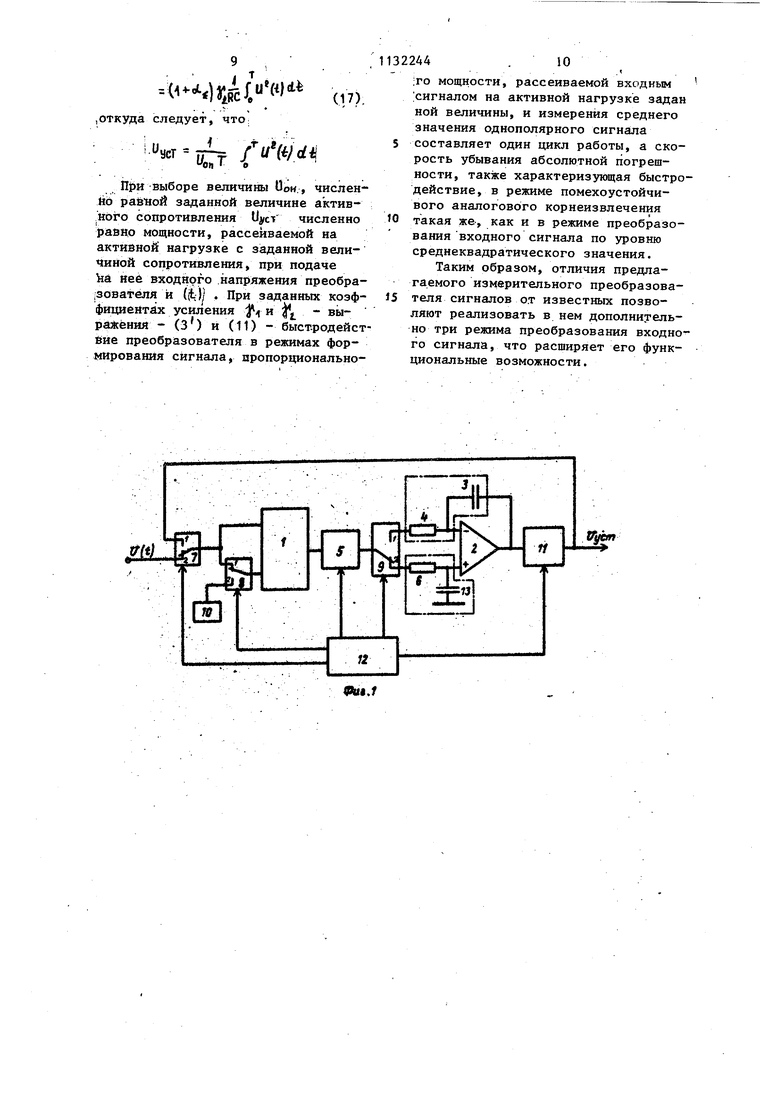

На фиг. 1 приведена блок-схема измерительного преобразователя сигналов, на фиг. 2 - временная диаграмма напряжения на выходе перфого дифференциального усилителя.

0 Измерительный преобразователь

сигналов содержит множительный блок 1, первый дифференциальньй усилитель 2, первый вход которого соединен с его выходом через первый кон5 денсатор 3, а также непосредственно - с первым резистором 4, второй усилитель 5, второй резистор в. В преобразователь дополнительно введены три двухпозиционных коммутатора 7-9, источник опорного напряжения 10, управляемый блок выборкихранения 11, .блок управления 12 и второй конденсатор 13. Второй усилитель 5 выполнен с управляемым коэффициентом усиления. Первый вход первого коммутатора 7 соединен с входной шиной, его второй вход - с вы.ходной шиной и выходом управляемого блока выборки-хранения 11, выход с первым входом второго коммутатора 8 и первым входом множительного блока 1, второй вход второго коммутатор.а 8 соединен с источником опорного напряжения 10, а выход - со вторым блоком множительного блока 1 выход которого подключен к входу второго усилителя 5, выход которого соединен с входом третьего коммутатора 9, первый выход которого соединен со свободным выводом первого резистора А, а второй - через второй резистор 6 со вторым входом первого дифференциального усилителя 2, соединенным через второй конденсатор 13 с общей шиной, выход первого дифференциального усилителя 2 подключен к входу блока выборкихранения 11 j а соответствующие выходы блока управления 12 соединены с управляющими входами коммутаторов 7-9, второго усилителя 5 и блока выборки-хранения 11.

Измерительный преобразователь сигналов работает следующим образом.

При преобразовании входного сигнала по уровню его среднеквадр атического значения в первом такте по команде с блока управления 12 коммутаторы 7 и 9 устанавливаются в положение 2, а коммутатор 8 в положение 1. Входной сигнал X(t) возводится в квадрат в множительном блоке 1, усиливается усилителем 5, интегрируется интегратором, обраsoBaifHbiM резистором 6, конденсатором 13 и дифференциальным усилителем 2,

Значение выходного сигнала дифференциального усилителя 2 определяется соотношением U;b..--Uo.HHT..)(l.t..)dt, (1) 55 где U(t)- напряжение входного сигнала ,

UQ - начальное напряжение, заполненное в блоке выборки-хранения 11, в частном случае оно может быть равно нулю, АННТ - погрешность интегрирова« ния, определяемая вторым резистором 6, вторым конденсатором 13 и первым дифференцирующим усилителемМб - погрешность квадратирования, определяемая множиI тельным блоком,

,- управляемый коэффициент усиления второго усилителя 5, .

Т - длительность периода интегрирования , - сопротивление резисторов

6 и А;,С - емкость конденсаторов 3 и 13.

Во втором такте коммутаторы 7 и 9 переводятся в положение 1 и описанному преобразованию подвергается напряжение, запомненное в блоке выборки-хранения 11. Значение вы ходного напряжения дифференциального усилителя 2 определяется соотношением (1) с учетом того, что его знак изменяется на обратный.

В конце второго такта от блока управления 12 на блок выборки-хранения 11 поступает управлякмций сигнал в результате чего в нем запоминаетс напряжение, равное сумме напряжений, полученных в первом и во второ тактах:

. ,. ( 2-)r,)dt-0 i:)A ;uodt (г)

1 р . о(.„„,)(ил„в;.

где

Первый и второй такты составляют один цикл работы преобразователя. Через h +1 циклов, где п- О, 1, 2..., выходное напряжение преобразователя составляет i,,y, (,,r,()ii -O r /UUn t. ° (3j

Через несколько циклов преобразования выходное напряжение преобразователя принимает установившееся значение, поскольку процесс измерения сходится. При преобразовании входного сигнала по уровню его сред неквадратического значения коэффициент усиления усилителя 5 устанавливается равным

JLc

1 2

()

..

Uwdx / верхняя граница диапагдезона преобразования В установившемся режиме Преобразования

UBblXh-l BMXycT.

и выражение в квадратных скобах соотношения (3) равно нулю, поэтому

т о

U3b,x.,cT.7- Ju4tjdt;

-Jf/u

(t)dt Uebix-tjcT.

Из соотношения (5) следует, что на преобразование входного сигнала по уровню среднеквадратического значения не влияют погрешности элементов преобразователя, так как преобразование входного сигнала выходного напряжения производится в одном и том же канале, состоящем из ОДНИХ и тех же элементов.

Абсолютная погрешность определяется соотношением

i h-U4CT- i-fenuo-Uycr.) f6;

Если выходное напряжение Uyti находится в середине диапазона преоб|разования

UycT .

то в каждом цикле преобразования абсолютная погрешность уменьшается в 2 раза ,

Un-UycT y fUo-UscT), а, например, через пять циклов грешность уменьшается в 32 раза.

1322446

Кроме преобразования входного сигнала по уровню среднеквадратического значения измерительный преобразователь работает в режиме преоб5 -разования однополярного входного сигнала по уровню среднего значения, в режиме помехоустойчивого аналогового извлечения квадратного корня «и в режиме формирования сигнала, пропорционального мощности, рассеиваемой заданным активным сопротивлением, к которому приложено входное напряжение.

Преобразование входного однополярного сигнала по уровню среднего значения производится следующим образом.

В первом такте коммутаторы 7-9

устанавливаются в положение 2 Коэффициент усиления усилителя 5 устанавливается равньпу Тг. и производится интегрирование при помощи резистора 6, конденсатора 13 и дифференциального усилителя 2 в течение периода времени Т . Приращение выходного сигнала дифференциального усилителя по отношению к начальному напряжению Uo , запомненному в блоке выборки-хранения 11, составляет

. у

uU,-( + d)( (rj о

где ион - напряжение источника опорного напряжения 10. Во втором такте коммутаторы 7 и 9 переводятся в положение 1, на выходе дифференциального усилителя 2 формируется приращение напряжения 0 обратного знака

4Uiz(n-flC jy jUoHUodt. (8J

. - В конце второго такта по команде блока управления .12 выходное напряжение дифференциального усилителя 2 запоминается в блоке выборки-хранения

UijcT .и .приращения напряжения в первом и втором тактах становятся равны

55 (l+rt- jt JpJUoMUscT.fllt 1 ii /11, j onUltldl Л откуда следует, что U4CT-r4--fu(t)dLt (W) о т.е. выходное напряжение преобразователя равно среднему значению однополярного входного сигнала. -Для получения максимального быст родействия коэффициент усил.ения устанавливает равным PC . ) (Ю Для выполнения помехоустойчивого преобТразования входного сигнала по уровню, пропорциональному квадратному корню, в первом такте комму таторы 7-9 устанавливаются в положение 2. Положительное приращение выходного напряжения дифференциальHoVo усилителя 2 составляет AUft-(.-jy J J uoHU(t)dt- /UHSihu}tclt (12) где UKJ - амплитуда помехи, О - частота помехи. Период повторения Tf, устанавливается равным периоду напряжения помехи. Поскольку помехи, как прави ло, являются результатом наводки от сети питания с частотой, например, 50 Гц, то 7и- 0,02 с. Во втором такте коммутаторы 7-9 переводятся в прложение 1. При этом входной сигнал возводится множитель ным блоком 1 Б квадрат, а отрицательное приращение выходного напряжения дифференциального усилителя составляет AUnM()y,}Vdt Ii) «

в конце второго такта алгебраическая сумма приращения суммируется с ранее запомненным напряжением и запоминается в блоке выборки-хранения 11. По достижении вьпсодным напряжением установившегося значения приращения становятся равны, причем

И

Junmu).

(16)

В конце второго такта выходное напряжение дифференциального усилителя 2 запоминается в блоке выборки-; хранения 11.

В установившемся -режиме U, . 5 UH + 1 поэтому из выражений (15) и (16) следует

()у, 48 так как этот интеграл представляет собой среднее значение синусоидального напряжения. ()r,/ia T /t--fnot),uaMt оо откуда UycTrl/Uonf-flKtldt В описанном режиме измерительный преобразователь может быть использован в сочетании с квадратичным датчиком входного сигнала в условиях помех напряжения промьгашенной частоты. В режиме формирования сигнала, пропорционального мощности на активном сопротивлении заданной , коммутаторы 7 и 9 устанавливаются в положение 2, а коммутатор 8 - в положение 1. Коэффициент усиления усилителя 5 устанавливается равным fi . Производится интегрирование входного сигнала в течение периода Т . Приращению выходного,напряжения дифференциального усилителя 2 в первом такте каждого цикла составляет т АУп (.,- rufi)di RC Во втором такте коммутатор 8, устанавливается в положение 2, а коммутатор 9 - в положение 1. Приращение выходного напряжения дифференциального усилителя 2 имеет обратный знак и сйставляет Al/r,H(-oL)y,|ye.U,-olt

.откуда следует, что1

.1.,«/

.и

СГг

. При выборе величины UOM., численЙ6 равной заданной величине актив.Hoi7o сопротивления 0,0 численно равно мощности, рассеиваемой на активной нагрузке с заданной величиной сопротивления, при подаче ka неб входного напряжения преобра;30вателя и (;) . При заданных козффициейтах усиления f , и , - выралёния - (З) и (11) - быст-родейст8Ие преобразователя в режимах формирования сигнала, иропорционально13224410

;го мощности, рассеиваемой входным

(17) ;сигналом на активной нагрузке задан ной величины, и измерения среднего значения однополярного сигнала 5 составляет один цикл работы, а скорость убывания абсолютной погрешности, также характеризующая быстродействие, в режиме помехоустойчивого аналогового корнеизвлечения

0 такая же, как и в режиме преобразования входного сигнала по уровню среднеквадратического значения.

Таким образом, отличия предлагаемого измерительного преобразователя сигналов от известных позволяют реализовать в нем дополнительно три режима преобразования входного сигнала, что расширяет его функциональные возможности.

| название | год | авторы | номер документа |

|---|---|---|---|

| Измерительный преобразователь дифференциального емкостного датчика | 1990 |

|

SU1781637A1 |

| Цифровой омметр | 1982 |

|

SU1046707A1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1350831A1 |

| Преобразователь емкости в частоту | 1988 |

|

SU1628013A1 |

| Цифроаналоговая следящая система | 1989 |

|

SU1700536A1 |

| ПРЕОБРАЗОВАТЕЛЬ ЛИНЕЙНЫХ ПЕРЕМЕЩЕНИЙ В ЦИФРОВОЙ КОД | 2005 |

|

RU2298193C1 |

| МНОГОКАНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ СИГНАЛОВ РЕЗИСТИВНЫХ ДАТЧИКОВ ВО ВРЕМЕННОЙ ИНТЕРВАЛ | 1994 |

|

RU2097777C1 |

| ВОЛОКОННО-ОПТИЧЕСКИЙ ИЗМЕРИТЕЛЬ УГЛОВОЙ СКОРОСТИ | 2012 |

|

RU2497077C1 |

| Аналоговое запоминающее устройство | 1985 |

|

SU1320847A1 |

| УСТРОЙСТВО ИЗМЕРЕНИЯ ПОТЕНЦИАЛОВ ЭЛЕКТРОХИМИЧЕСКОЙ ЗАЩИТЫ | 2005 |

|

RU2308702C2 |

ИЗМЕРИТЕЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ ОТГНАЛОВ, содержащий множительный блок, первый дифференциальный усилитель, первый вход которого со единен с его выходом через первый конг денсатор, а также непосредственно с первым резистором, второй усилитель, второй резистор, отличающийся тем, что, с целью расширения функциональных возможностей, в него дополнительно введены три двухпозиционных коммутатора, ; источник опорного { апряжения, управляемый блок выборки-хранения, блок Г управления и второй конденсатор, при этом второй усилитель выполнен с управляемым коэффициентом усиления, первьй вход первого коммутатора соединен с входной шиной, его второй вход - с выходной шиной и выходом управляемого блока выборки-хранения, выход - .с первым входом-второго коммутатора и первым входом множительного блока, второй вход второго коммутатора соединены с источником опорного напряжения, а выход - со вторым входом множительного блока, выход которого подключен к входу второго усилителя, выход которого -соединен с входом третьего коммутатора, первый выход которого соединен со свободным выводом первого резис(Л тора, а.второй - через второй резистор со вторым входом первого ди4 ференциального усилителя, соединенным через второй конденсатор с общей шиной, выход первого дифференциального усилителя подключен к входу блока выборки-хранения, а соответоэ ствующие выходы блока управления to 1C соединены с управляющими входами коммутаторов, второго усилителя и 4 блока выборки-хранения. 11

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Справочник по нелинейным | |||

| схемам | |||

| Под ред | |||

| Д.Шейнгольда | |||

| М., Мир, 1977, с | |||

| Ручная тележка для реклам | 1923 |

|

SU407A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Заявка Великобритании № 1378251, кл | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| ПРИБОР ДЛЯ ЗАПИСИ И ВОСПРОИЗВЕДЕНИЯ ЗВУКОВ | 1923 |

|

SU1974A1 |

Авторы

Даты

1984-12-30—Публикация

1983-03-03—Подача