выходы которого являются коллекторами соответственно первого и второго транзисторов,которые соединены соответственно с первыми выводами первого и второго резисторов, вторые выводы которых объединены и являются третьим входом дифференциального усилительного каскада, эмиттеры первого и второго транзисторов соединены соот ветственно с первым и вторым выводами третьего резистора и являются соответственно пятым и четвертым входами дифференциального усилительного каскада,

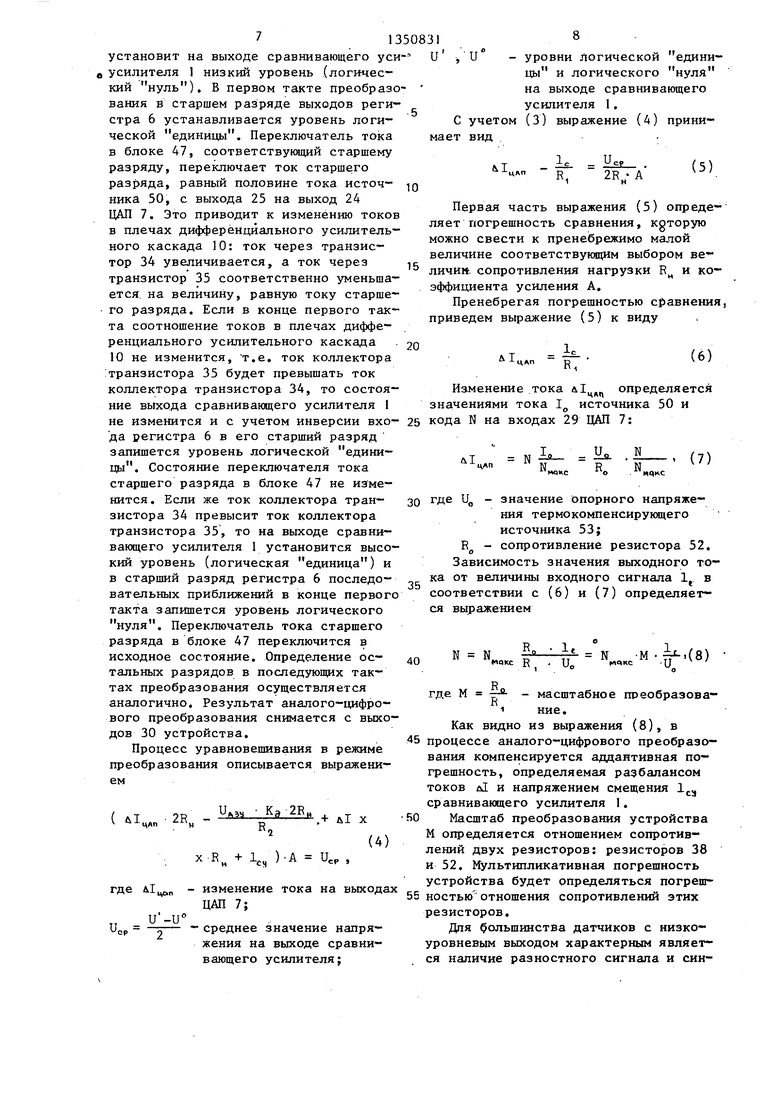

3. Преобразователь по п„ 1, отличающийся тем, что преобразователь напряжения в ток выполнен на пяти резисторах, двух источниках начального тока первом и втором транзисторах, коллекторы которых являются соответственно первым и вторым вы ходами преобразователя напряжения в ток, эмиттеры первого транзистора соединены с первым выводом резистора, выходом первого источника начального тока, эмиттер второго транзистора соединен с вторым выводом первого резистора и выходом второго источника начального .тока, входы первого и второго источников начального тока объединены с первыми выводами второго и третьего резисторов и являются первым входом преобразователя напряжения в ток, второй вывод второго резистора соединен непосредственно с базой первого -тр зистора и через четвертый резистор соединен с общей шиной, второй вывод третьего резистора соединен с базой второго транзистора и с первым Выводом пятого резистора, второй вывод которого является вторым входом преобразователя напряжения в ток...

4 Преобразователь по п. 1, о тл.ичающийся тем, что цифро- торах одинакового типа проводимости.

Изобретение относится к измерительной и вычислительной технике и может .быть использовано в электроизмерительных приборах, измерительно-вычислительных и управляющих комплексах.

50831

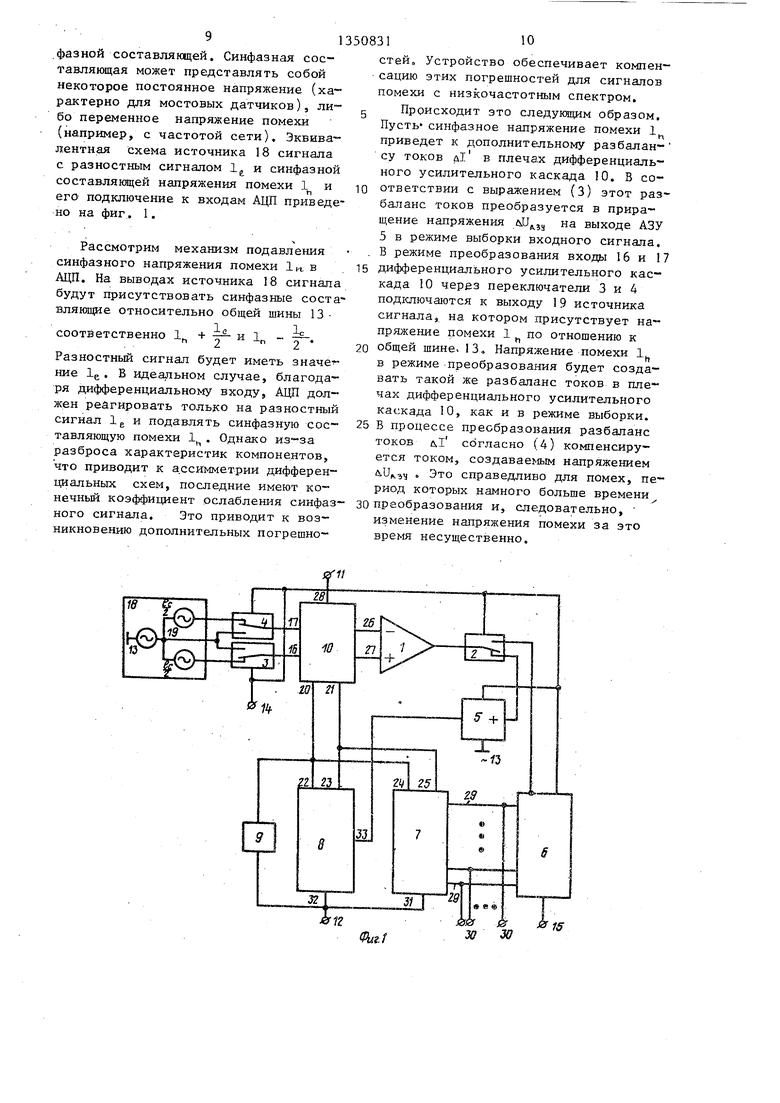

аналоговый преобразователь выполнен на блоке преобразования уровня напряжения, п переключателях, где п - число разрядов преобразования, блоке фиксации уровня напряжения на п+1 транзисторах, резистивной матрице-типа R-2R, источнике стабильного тока на дополнительном транзисторе, двух резисторах, диоде, стабилитроне, анод которого объединен с первым выводом первого резистора и является вторым входом цифроаналогового преобра- . зователя, катод объединен с катодом диода, анод которого через второй резистор соединен с общей шиной и не- по:средственно с базой дополнительного транзистора, эмиттер которого соединен с вторым выводом первого резистора , а коллектор через резистив- ную матрицу R - 2R соединен с соответствующими эмиттерами ri+1 транзисторов, базы которых объединены и являются шиной напряжения фиксации, коллектор первого транзистора соединен с общей шиной, а коллекторы п транзисторов соединены соответственно с информационны1 1и входами п переключателей, первые и вторые входы ключателей, первые и вторые выходы которых соответственно объединены и являются соответственно первым и вторым выходами цифро-аналогового преобразователя, управляющие входы п переключателей соединены с соответствующими . выходами блока преобразования уровня напряжения, входы которого являются первыми входами цифроаналогового преобразователя.

5. Преобразователь по пп. 2-4, отличающийся тем, что транзисторы дифференциального усилительного каскада, преобразователя напряжения в ток и цифроаналогового преобразователя выполнены на транзисЦелью изобретения явля-ется повышение точности преобразования.

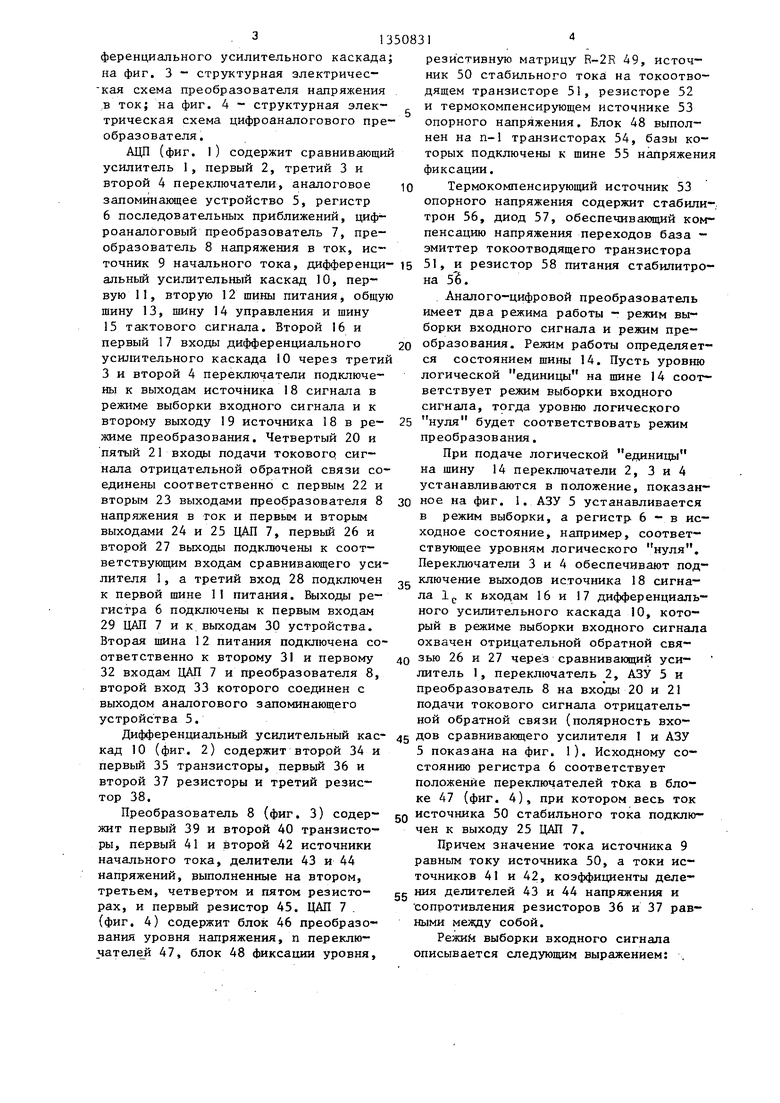

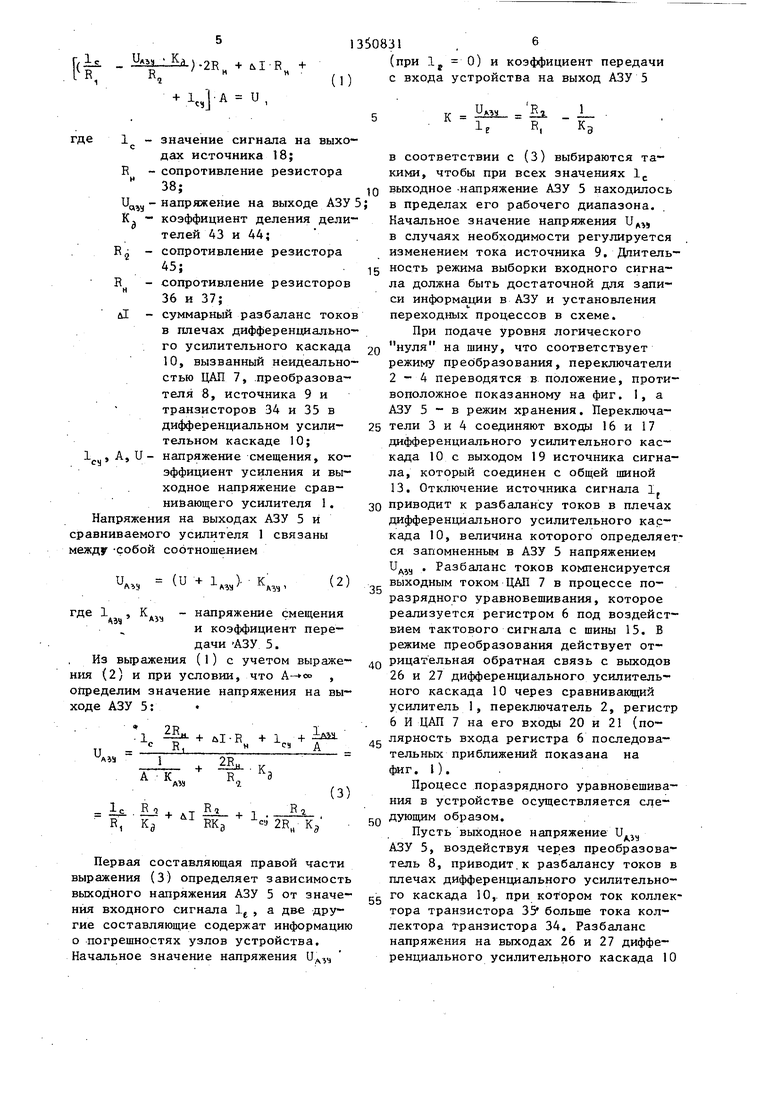

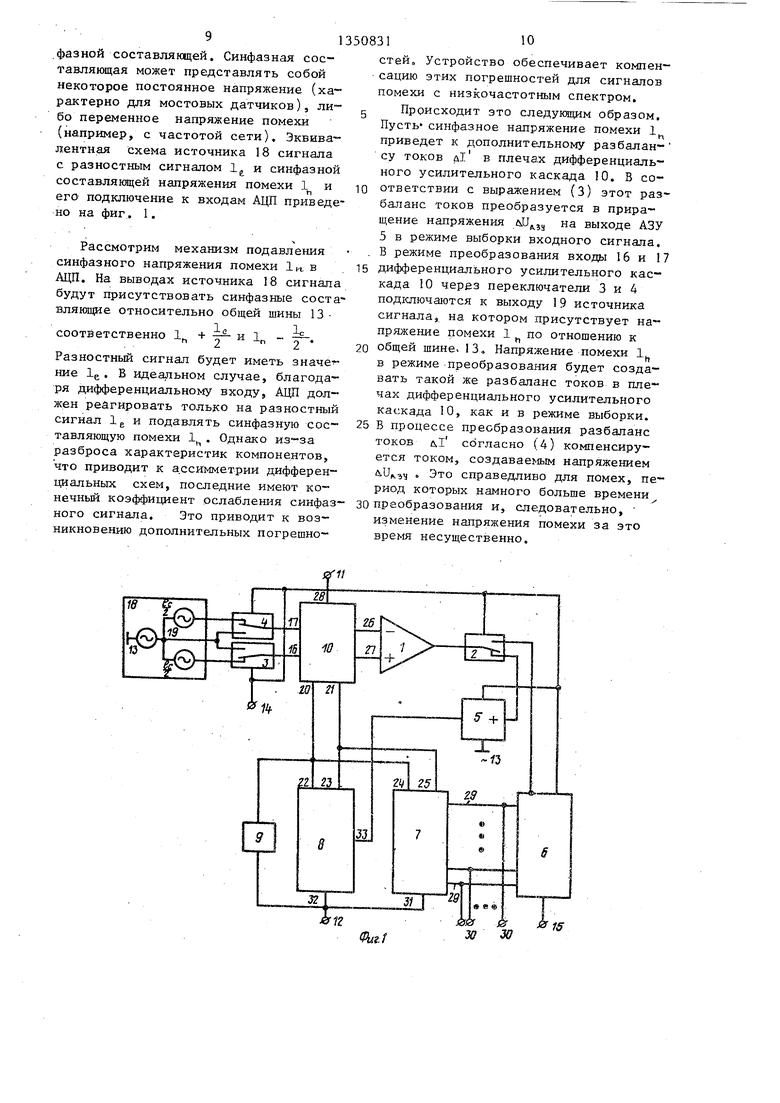

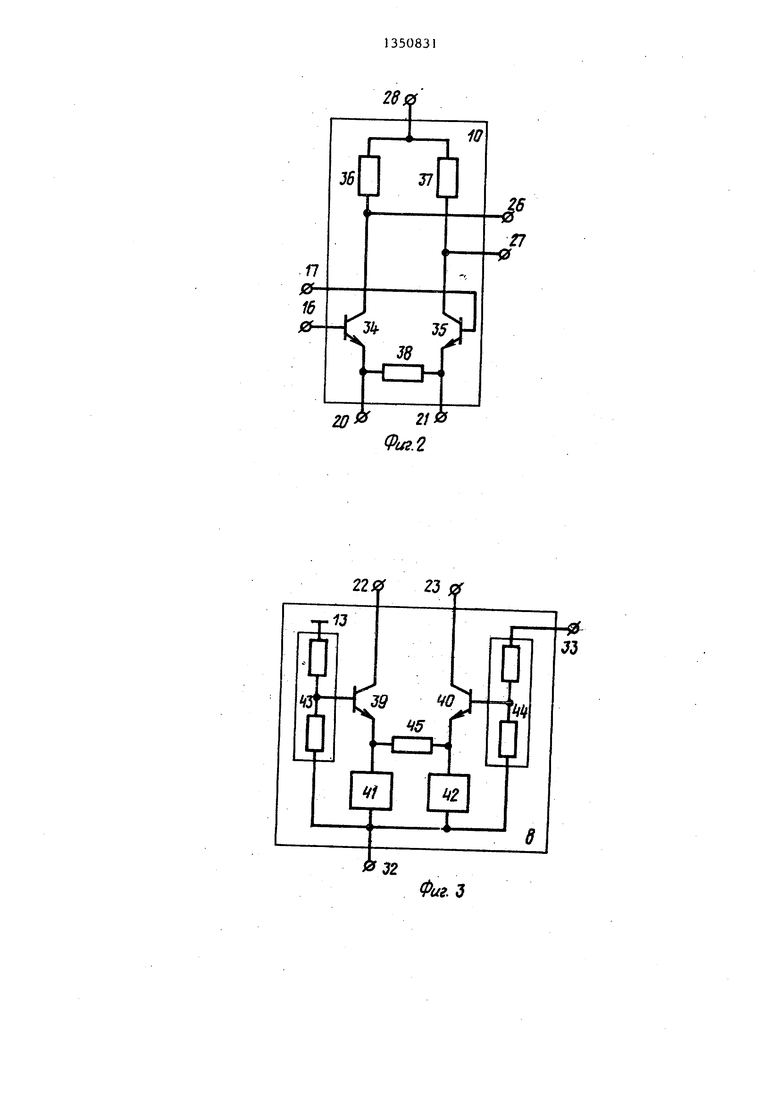

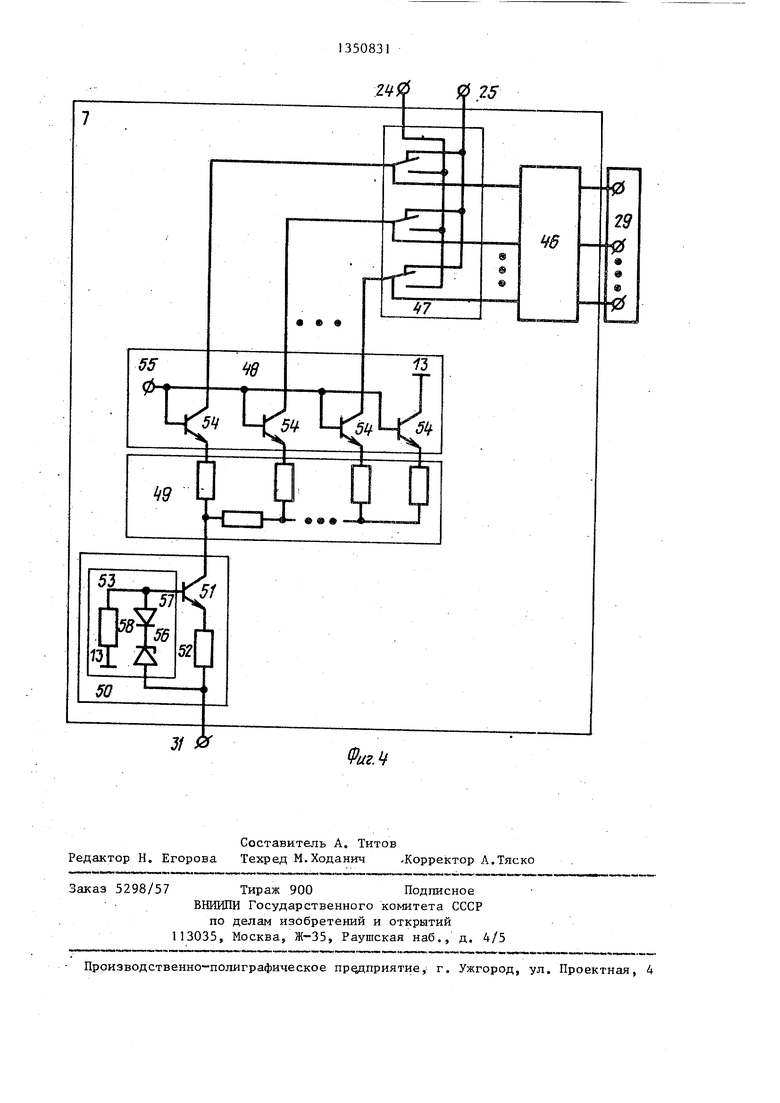

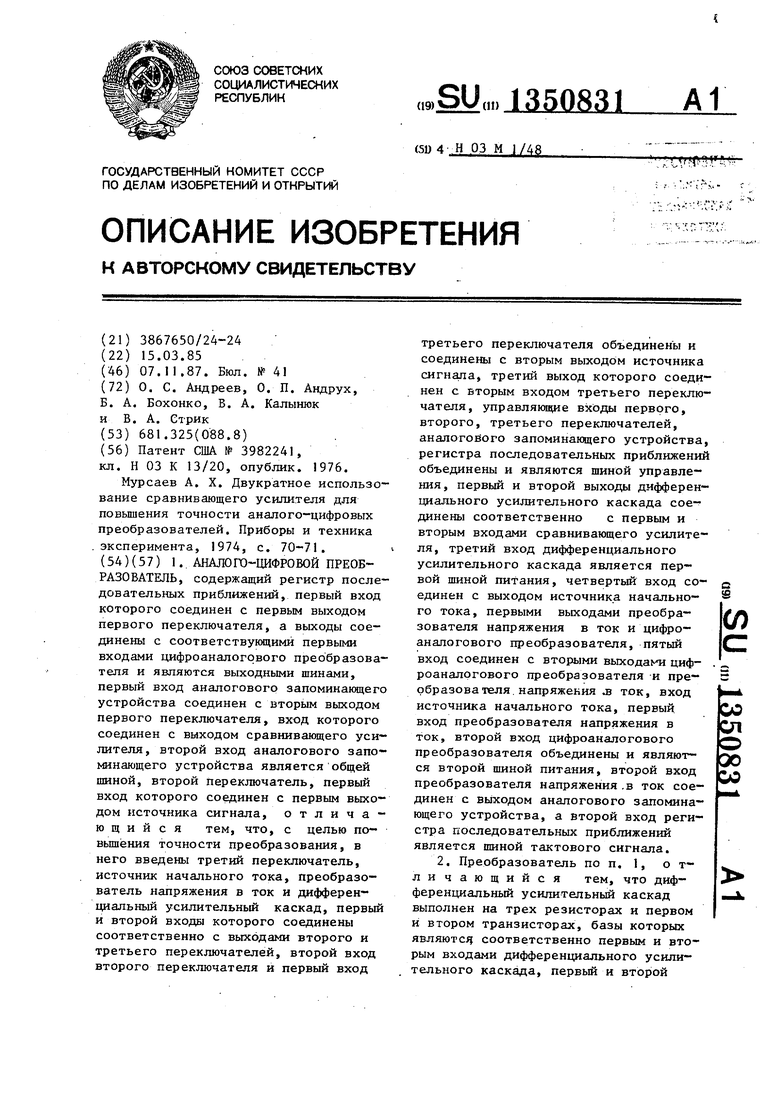

На фиг.. 1 п эиведена функциональная схема устройства; на фиг. 2 - структурная электрическая схема дифференциального усилительного каскада; на фиг. 3 структурная электричес- кая схема преобразователя напряжения в ток; на фиг. 4 структурная электрическая схема цифроаналогового пре образователя.

АЦП (фиг. I) содержит сравнивающий усилитель 1, первый 2, третий 3 и второй 4 переключатели, аналоговое запоминающее устройство 5, регистр 6 последовательных приближений, циф роаналоговый преобразователь 7, преобразователь 8 напряжения в ток, ис25

точник 9 начального тока, дифференци- 15 51, и резистор 58 питания стабилитро- альный усилительный каскад 10, первую 11, вторую 12 шины питания, общую шину 13, шину 14 управления и щину 15 тактового сигнала. Второй 16 и первый 17 входы дифференциального 20 усшштельного каскада 10 через третий 3 и второй 4 переключатели подключены к выходам источника 18 сигнала в режиме выборки входного сигнала и к второму выходу 19 источника 18 в режиме преобразования. Четвертый 20 и пятый 21 входы подачи токовогр сигнала отрицательной обратной связи соединены соответственно с первым 22 и вторым 23 выходами преобразователя 8 напряжения в ток и первым и вторым выходами 24 и 25 ЦАП 7, первый 26 и второй 27 выходы подключены к соот- ветствуюш 1м входам сравнивающего усилителя 1, а третий вход 28 подключен к первой шине II питания. й.1ходы регистра 6 подключены к первым входам 29 ЦАП 7 и к выходам 30 устройства. Вторая шина 12 питания подключена соответственно к второму 31 и первому 32 входам ЦАП 7 и преобразователя 8, второй вход 33 которого соединен с выходом аналогового запоминающего устройства 5.

30

35

на 5.

Аналого-цифровой преобразователь имеет два режима работы - режим выборки входного сигнала и режим преобразования. Режим работы определяется состоянием шины 14. Пусть уровню логической единицы на шине 14 соответствует режим выборки входного сигнала, тргда уровню логического нуля будет соответствовать режим преобразования.

При подаче логической единицы на шину 14 переключатели 2, 3 и 4 устанавливаются в положение, показанное на фиг. 1. АЗУ 5 устанавливается в режим выборки, а регистр 6 - в исходное состояние, например, соответствующее уровням логического нуля. Переключатели 3 и 4 обеспечивают подключение выходов источника 18 сигнала 1 к входам 16 и 17 дифференциаль40

ного усилительного каскада 10, который в режиме выборки входного сигнала охвачен отрицательной обратной связью 26 и 27 через сравнивающий усилитель 1, переключатель 2, АЗУ 5 и преобразователь 8 на входы 20 и 21 подачи токового сигнала отрицательной обратной связи {полярность вхоДифференциальный усилительный кас- 45 Д° сравнивающего усилителя 1 и АЗУ кад 10 (фиг. 2) содержит второй 34 и

5 показана на фиг. 1). Исходному состоянию регистра 6 соответствует положение переключателей тОка в блоке 47 (фиг. 4), при котором весь ток источника 50 стабильного тока подключен к выходу 25 ЦАП 7.

первый 35 транзисторы, первьй 36 и второй 37 резисторы и третий резистор 38.

Преобразователь 8 (фиг. 3) содержит первый 39 и второй 40 транзисторы, первый 41 и второй 42 источники начального тока, делители 43 и 44 напряжений, выполненные на втором, третьем, четвертом и пятом резисторах, и первый резистор 45. ЦАП 7 . (фиг. 4) содержит блок 46 преобразования уровня напряжения, п переключателей 47, блок 48 фиксации уровня.

резистивную матрицу R-2R 49, источник 50 стабильного тока на токоотво- дящем транзисторе 51, резисторе 52 и термокомпенсирующем источнике 53 опорного напряжения. Блок 48 выполнен на п-1 транзисторах 54, базы которых подключены к шине 55 напряжения фиксации.

Термокомпенсирующий источник 53 опорного напряжения содержит стабилитрон 56, диод 57, обеспечивающий компенсацию напряжения переходов база - эмиттер токоотводящего транзистора

51, и резистор 58 питания стабилитро-

на 5.

Аналого-цифровой преобразователь имеет два режима работы - режим выборки входного сигнала и режим преобразования. Режим работы определяется состоянием шины 14. Пусть уровню логической единицы на шине 14 соответствует режим выборки входного сигнала, тргда уровню логического нуля будет соответствовать режим преобразования.

При подаче логической единицы на шину 14 переключатели 2, 3 и 4 устанавливаются в положение, показанное на фиг. 1. АЗУ 5 устанавливается в режим выборки, а регистр 6 - в исходное состояние, например, соответствующее уровням логического нуля. Переключатели 3 и 4 обеспечивают подключение выходов источника 18 сигнала 1 к входам 16 и 17 дифференциаль1520

40

45 Д° сравнивающего усилителя 1 и АЗУ

50

55

5 показана на фиг. 1). Исходному состоянию регистра 6 соответствует положение переключателей тОка в блоке 47 (фиг. 4), при котором весь ток источника 50 стабильного тока подключен к выходу 25 ЦАП 7.

Причем значение тока источника 9 равньм току источника 50, а токи источников 41 и 42, коэффициенты деления делителей 43 и 44 напряжения и сопротивления резисторов 36 и 37 равными между собой.

выборки входного сигнала описывается следующим выражением: ,

.

ил

к.

к„

)-2К„ + IR„ +

(1)

1350831,6

(при Ij 0) и коэффициент передачи

)

с входа устройства на выход АЗУ 5

+ 1

J-A

и

К -

де

R

R,

R

ul - значение сигнала на выходах источника 18; - сопротивление резистора 38;

U,,j - напряжение на выходе АЗУ 5; К, - коэффициент деления дели телей 43 и А4; сопротивление резистора 45;

сопротивление резисторов 36 и 37;

суммарный разбаланс токов в плечах дифференциального усилительного каскада 10, вызванный неидеально- стью ЦАП 7, .преобразователя 8, источника 9 и транзисторов 34 и 35 в дифференциальном усилительном каскаде 10; , А, U- напряжение смещения, коэффициент усиления и выходное напряжение сравнивающего усилителя 1. Напряжения на выходах АЗУ 5 и равниваемого усилителя 1 связаны ежду -собой соотношением

-сч

(и +

«.)

К

АЪЧ

(2)

где 1

AJS

К

Ai4

напряжение смещения и коэффициент передачи АЗУ 5.

Из выражения (1) с учетом выражения (2) и при условии, что , определим значение напряжения на выходе АЗУ 5: «

и

AM

R.

Первая составляющая правой части выражения (3) определяет зависимость выходного напряжения АЗУ 5 от значения входного сигнала 1, а две другие составляющие содержат информацию о погрешностях узлов устройства. Начальное значение напряжения

в соответствии с (З) выбираются такими, чтобы при всех значениях Ij, выходное -напряжение АЗУ 5 находилось в пределах его рабочего диапазона. Начальное значение напряжения U. в случаях необходимости регулируется изменением тока источника 9, Длительность режима выборки входного сигнала должна быть достаточной для записи информации в АЗУ и установления переходных процессов в схеме.

При подаче уровня логического нуля на шину, что соответствует режиму преобразования, переключатели 2-4 переводятся в положение, противоположное показанному на фиг. 1, а АЗУ 5 - в режим хранения. Переключа-

тели 3 и 4 соединяют входы 16 и 17 дифференциального усилительного каскада 10 с выходом 19 источника сигнала, который соединен с общей шиной 13. Отключение источника сигнала 1

приводит к разбалансу токов в плечах дифференциального усилительного каскада 10, величина которого определяется запомненным в АЗУ 5 напряжением

и

Разбаланс

. л. а -олапч. ТОКОВ компенсируется выходным током ЦАП 7 в процессе по

разрядного уравновешивания, которое реализуется регистром 6 под воздействием тактового сигнала с шины 15. В режиме преобразования действует отрицательная обратная связь с выходов 26 и 27 дифференциального усилительного каскада 10 через сравнивающий усилитель 1, переключатель 2, регистр 6 И ЦАП 7 на его входы 20 и 21 (полярность входа регистра 6 последовательных приближений показана на фиг. 1).

Процесс поразрядного уравновешивания в устройстве осуществляется следующим образом.

Пусть выходное напряжение ,, АЗУ 5, воздействуя через преобразователь 8, приводит.к разбалансу токов в плечах дифференциального усилительного каскада 10,. при котором ток коллектора транзистора 35 больше тока коллектора транзистора 34. Разбаланс напряжения на выходах 26 и 27 дифференциального усилительного каскада 10

71350831

установит на выходе сравнивающего уси- U , U « усилителя 1 низкий уровень (логический нуль). В первом такте преобразо- вания в старшем разряде выходов регистра 6 устанавливается уровень логиС уч мает ви

ческой единицы. Переключатель тока в блоке 47, соответствукиций старшему разряду, переключает ток старшего разряда, равный половине тока источника 50, с выхода 25 на выход 24 ЦАП 7. Это приводит к изменению токов в плечах дифферёндйального усилительного каскада 10: ток через транзистор 34 увеличивается, а ток через транзистор 35 соответственно уменьшается, на величину, равную току старше- го разряда. Если в конце первого такта соотношение токов в плечах дифференциального усилительного каскада 10 не изменится, т.е. ток коллектора транзистора 35 будет превышать ток коллектора транзистора 34, то состояние выхода сравнивающего усилителя 1

не изменится и с учетом инверсии вхо- 25 кода N на входах 29 ЦАП 7: да регистра 6 в его старший разряд

цы. Состояние переключателя тока старшего разряда в блоке 47 не изменится . Если же ток коллектора тран- зистора 34 превысит ток коллектора транзистора 35, то на выходе сравнивающего усилителя 1 установится высо кий уровень (логическая единица) и в старший разряд регистра 6 последовательных приближений в конце первог такта запишется уровень логического нуля. Переключатель тока старшего разряда в блоке 47 переключится в исходное состояние. Определение остальных разрядов в последующих тактах преобразования осуществляется аналогично. Результат аналого-цифрового преобразования снимается с выходов 30 устройства.

Процесс уравновешивания в режиме преобразования описывается выражением

токов ftl и напряжением смещения 1

( 61

ЦАП

2К„ Кэ 2R(

Rn

,+ &I X

x-R + 1,;)-А и„

(4)

с ч

где л1

цоп

CS

сравнивающего усилителя 1. ВО Масштаб преобразования устройства М определяется отношением сопротивлений двух резисторов: резисторов 38 и 52. Мультипликативная погрешность

устройства будет определяться погреш- - изменение тока на выходах ,-с ностью отношения сопротивлении этих

резисторов.

Для 0ольшинства датчиков с низкоуровневым выходом характерным является наличие разностного сигнала и сини -и

UCP т- среднее значение напряжения на выходе сравнивающего усилителя;

8

, U

уровни логической цы

,

единии логического нуля на выходе сравнивающего усилителя 1,

С учетом (3) выражение т вид

(4)

приниМ

ЦАП

1 R.

(5)

10

Первая часть выражения (5) определяет погрешность сравнения, кдторую можно свести к пренебрежимо малой величине соответствующим выбором ве- личи сопротивления нагрузки R и коэффициента усиления А.

Пренебрегая погрешностью сравнения, приведем выражение (5) к виду

20

/М.

1 R,

(6)

Изменение тока л1щ„ определяется значениями тока 1„ источника 50 и

N

N

Us

R,

N

N

(7)

ИЧКС

Д о R

- значение опорного напряжения термокомпенсирукнцего источника 53;

R - сопротивление резистора 52. Зависимость значения выходного тока от величины входного сигнала 1 в соответствии с (6) и (7) определяется выражением

Д о R

N N

.(8)

зо Д о R

где М

R

- масштабное преобразование.

Как видно из выражения (8), в 45 процессе аналого-цифрового преобразования компенсируется адцантивная погрешность, определяемая разбалансом

токов ftl и напряжением смещения 1

(4)

.фазной составляющей. Синфазная составляющая может представлять собой некоторое постоянное напряжение (характерно для мостовых датчиков), либо переменное напряжение помехи (например, с частотой сети). Эквивалентная схема источника 18 сигнала с разностным сигналом 1 и синфазной составляющей напряжения помехи 1 и его подключение к входам АЦП приведено на фиг. 1.

ч

Рассмотрим механизм подавления синфазного напряжения помехи 1и, в АЦП. На выводах источника 18 сигнала будут присутствовать синфазные соста вляющие относительно общей шины 13соответственно 1 + -г

Разностньй сигнал будет иметь значе- - ние Ig. В идеальном случае, благодаря дифференциальному входу, АЦП должен реагировать только на разностный сигнал 1е и подавлять синфазную составляющую помехи 1. Однако из-за разброса характеристик компонентов, что приводит к а.ссимметрии дифференциальных схем, последние имеют ко- нечньй коэффициент ослабления синфазного сигнала. Это приводит к возникновению дополнительных погрешно-

1 IE- -i-n 2

тейа Устройство обеспечивает компенацию этих погрешностей для сигналов омехи с низкочастотным спектром.

Происходит это следукщим образом. Пусть- синфазное напряжение помехи 1 приведет к дополнительному разбалан- су токов д1 в плечах дифференциального усилительного каскада 10. В со-

ответствии с выражением (3) этот разбаланс токов преобразуется в приращение напряжения выходе АЗУ 5 в режиме выборки входного сигнала. В режиме преобразования входы 16 и 17

ди(54)еренциального усилительного каскада 10 через переключатели 3 и 4 подключаются к выходу 19 источника сигнала, на котором присутствует напряжение помехи 1 по отношению к

общей шине 13. Напряжение помехи 1 в режиме преобразования будет создавать такой же разбаланс токов в плечах дифференциального усилительного каскада 10, как и в режиме выборки.

В процессе преобразования разбаланс токов ul согласно (4) компенсируется током, создаваемым напряжением 6.U,v, . Это справедливо для помех, период которых намного больше времени преобразования и, следовательно, изменение напряжения помехи за это время несущественно.

Г/

15

Фиг.1

20 21f

Фиг. 2

220 23 бГ

032

Фиг. J

0 25

J/ 0

Составитель А. Титов Редактор Н. Егорова Техред М.Ходанич .Корректор Л.Тяско

Заказ 5298/57 Тираж 900Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

(Риг.

| название | год | авторы | номер документа |

|---|---|---|---|

| Биполярный цифро-аналоговый преобразователь | 1985 |

|

SU1292184A1 |

| СОСТАВНОЙ БЫСТРОДЕЙСТВУЮЩИЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 2006 |

|

RU2311731C1 |

| Аналого-цифровой преобразователь | 1989 |

|

SU1691962A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ ПОСЛЕДОВАТЕЛЬНОГО ДЕЙСТВИЯ | 2003 |

|

RU2245000C2 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 1991 |

|

RU2060578C1 |

| Стабилизатор постоянного регулируемого тока | 1990 |

|

SU1728853A1 |

| ПОЛУПРОВОДНИКОВАЯ ИНТЕГРАЛЬНАЯ СХЕМА | 1991 |

|

RU2104601C1 |

| МНОГОКАНАЛЬНЫЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1973 |

|

SU400021A1 |

| Последовательно-параллельный аналого-цифровой преобразователь | 1987 |

|

SU1547059A1 |

| Преобразователь напряжения в код Грея | 1984 |

|

SU1182687A1 |

| Патент США № 3982241, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Планшайба для точной расточки лекал и выработок | 1922 |

|

SU1976A1 |

| Мурсаев А | |||

| X | |||

| Двукратное использо вание сравнивающего усилителя для повьшения точности аналого-цифровых преобразователей | |||

| Приборы и техника эксперимента, 1974, с | |||

| Деревянный торцевой шкив | 1922 |

|

SU70A1 |

Авторы

Даты

1987-11-07—Публикация

1985-03-15—Подача