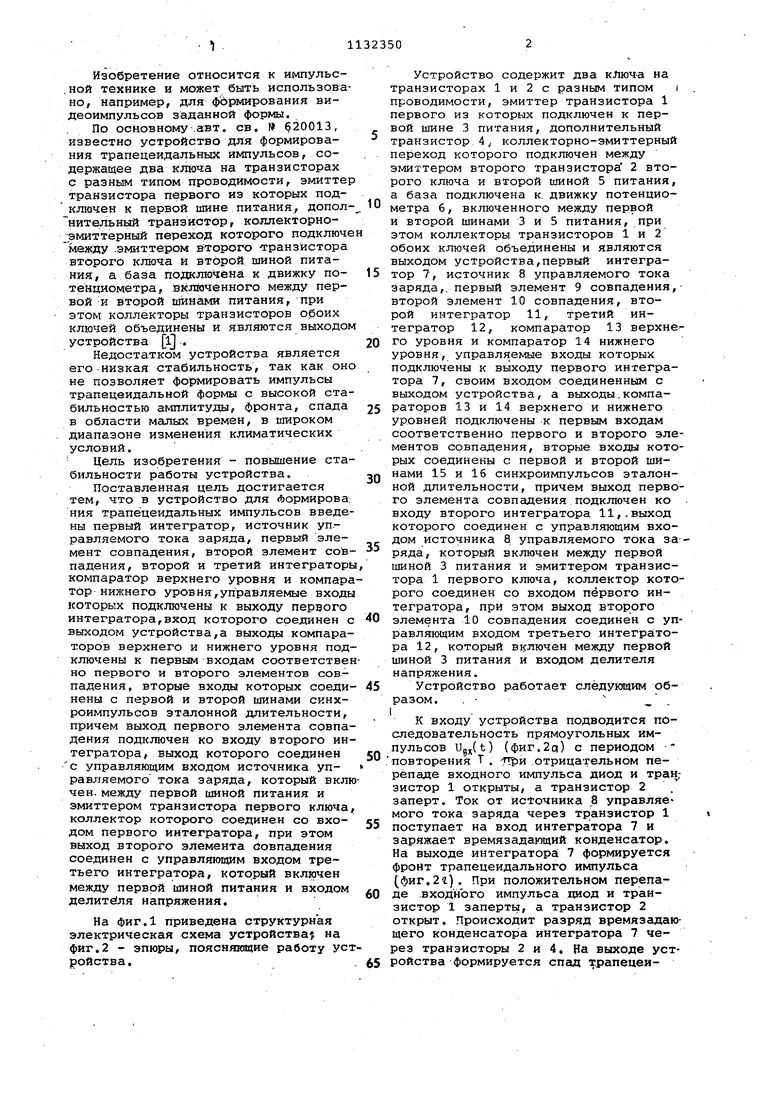

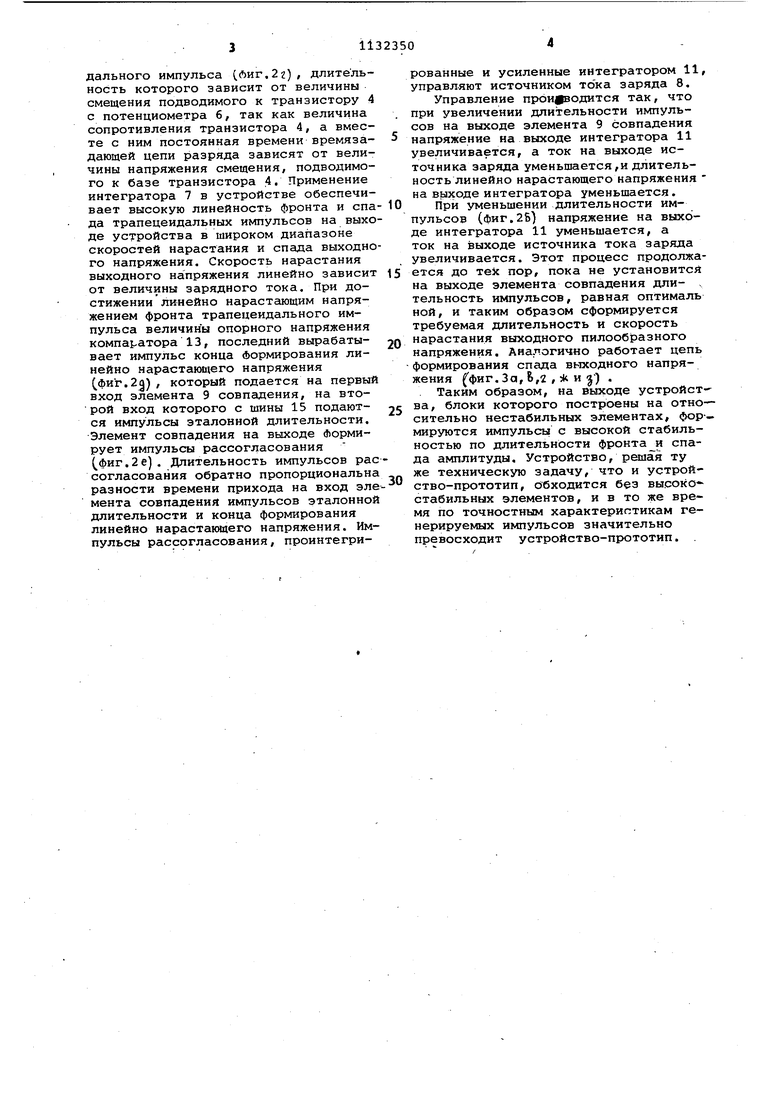

Изобретение относится к импульс,ной технике и может быть использова но, например, для формирования видеоимпульсов заданной формы. По основному-,авт, св. №620013, известно устройство для формирования трапецеидальных импульсов, содержащее два ключа на транзисторах с разным типом проводимости, эмиттер транзистора первого из которых подключен к первой шине питания, допол нительный транзистор, коллекторно эмиттерный переход; которого подключе меяоду .эмиттером в торого транзистора звторого ключа и второй шиной питания, а база подключена к движку потенциометра, включенного между первой И второй шинами питания, при этом коллекторы транзисторов обоих ключей объединены и являются выходом устройства ij . Недостатком устройства является его низкая стабильность, так как оно не позволяет формировать импульсы трапецеидальной формы с высокой стабильностью амплитуды, фронта, спада в области малых времен, в широком диапазоне изменения климатических условий, Цель изобретения - повышение ста бильности работы устройства. Поставленная цель достигается тем, что в устройство для Лормирова; ния трапецеидальных импульсов введе ны первый интегратор, источник уп.равляемого тока заряда, первый элемент совпадения, второй элемент сов падения, второй и третий интеграторы компаратор верхнего уровня и компара тор нижнего уровня,управляемые входы которых подключены к выходу первого интегратора,вход которого соединен с выходом устройства,а выходы компараторов верхнего и нижнего уровня под ключены к первым входам соответстве но первого И второго элементов совпадения, вторые входы которых соеди нены с первой и второй шинами синхроимпульсов эталонной длительности, причем выход первого элемента совпадения подключен ко входу второго интегратора , выход которого соединен с управляющим входом источника управляемого тока заряда, который вклю чен, между первой шиной питания и эмиттером транзистора первого ключа коллектор которого соединен со входом первого интегратора, при этом выход второго элемента Совпадения соединен с управляющим входом третьего интегратора, который включен между первой шиной питания и входом делителя напряжения. На фиг.1 приведена структурная электрическая схема устройства на фиг.2 - эпюры, поясняющие работу уст ройства. Устройство содержит два ключа на транзисторах 1 и 2 с разным типом i проводимости, эмиттер транзистора 1 первого из которых подключен к первой шине 3 питания, дополнительный транзистор 4 коллекторно-эмиттерный переход которого подключен между эмиттером второго транзистора 2 второго ключа и второй шиной 5 питания, а база подключена к. движку потенциометра 6, включенного между первой и второй шинами 3 и 5 питания, при этом коллекторы транзисторов 1 и 2 обоих ключей объединены и являются выходом устройства,первый интегратор 7, источник 8 управляемого тока заряда,, первый элемент 9 совпадения, второй элемент 10 совпадения, второй интегратор 11, третий интегратор 12, компаратор 13 верхнего уровня и компаратор 14 нижнего уровня, управляемые входы которых подключены к выходу первого интегратора 7, своим входом соединенным с выходом устройства, а выходы,компараторов 13 и 14 верхнего и нижнего уровней подключены к первым входам соответственно первого и второго элементов совпадения, вторые входы которых соединены с первой и второй шинами 15 и 16 синхроимпульсов эталонной длительности, причем вь1ход первого элемента совпадения подключен ко входу второго интегратора 11,,выход которого соединен с управляющим входом источника а управляемого тока заряда, который включен между первой шиной 3 питания и эмиттером транзистора 1 первого ключа, коллектор которого соединен со входом первого интегратора, при этом выход второго элемента 10 совпадения соединен с управляющим входом третьего интегра тора 12, который включен между первой шиной 3 питания и входом делителя напряжения. Устройство работает следующим образом. . I .. К входу устройства подводится последовательность прямоугольных импульсов Ug(t) (фиг.2а) с периодом повторения Т . -при .отрицательном перепаде входного импульса диод и тран,зистор 1 открыты, а транзистор 2 заперт. Ток от источника 8 управляемого тока заряда через транзистор 1 поступает на вход интегратора 7 и заряжает времязадающий конденсатор. На выходе интегратора 7 формируется фронт трапецеидального импульса (фиг.2г). При положительном перепаде .входного импульса диод и транзистор 1 заперты, а транзистор 2 открыт. Происходит разряд времязадающего конденсатора интегратора 7 через транзисторы 2 и 4, На выходе устройства формируется спад трапецеидальнего импульса (Лиг.2г), длительность которого зависит от величины смещения подводимого к транзистору 4 с потенциометра б, так как величина сопротивления транзистора 4, а вместе с ним постоянная времени времязадающей цепи разряда зависят от величины напряжения смещения, подводимого к базе транзистора 4, Применение интегратора 7 в устройстве обеспечивает высокую линейность фронта и спада трапецеидальных импульсов на выходе устройства в широком диапазоне скоростей нарастания и спада выходного напряжения. Скорость нарастания выходного напряжения линейно зависит от величины зарядного тока. При достижении линейно нарастающим напряжением фронта трапецеидального импульса величины опорного напряжения компаратора 13, последний вырабатывает импульс конца Формирования линейно нарастающего напряжения (фиг.2), который подается на первый вход элемента 9 совпадения, на второй вход которого с шины 15 подаются импульсы эталонной длительности. Элемент совпадения на выходе Формирует импульсы рассогласования (фиг.2е). Длительность импульсов рассогласования обратно пропорциональна разности времени прихода на вход элемента совпадения импульсов эталонной длительности и конца формирования линейно нарастающего напряжения. Импульсы рассогласования, проинтегрированные и усиленные интегратором 11, управляют источником тока заряда 8. Управление прои одится так, что при увеличении длительности импульсов на выходе элемента 9 совпадения 5 напряжение на выходе интегратора 11 увеличивается, а ток на выходе источника заряда уменьшается,и длительность линейно нарастающего напряжения на выходе интегратора уменьшается.

0 При уменьшении длительности импульсов (фиг.2Б) напряжение на выходе интегратора 11 уменьшается, а ток на выходе источника тока заряда увеличивается. Этот процесс продолжа5 ется до TeJc пор, пока не установится на выходе элемента совпадения дли- , тельность импульсов, равная оптималь ной, и таким образом сформируется требуемая длительность и скорость

Q нарастания выходного пилообразного напряжения. Диалогично работает цепь - формирования спгода выходного напряжения фиг. За, &,2 , и ) .

Таким образом, на выходе устройст

5 ва, блоки которого построены на отно- сительно нестабильных элементах, фор-мируются импульсы с высокой стабильностью по длительности фронтами спада амплитуды. Устройство, решая ту же техническую задачу, что и устрой0ство-прототип, обходится без высоко-стабильных элементов, и в то же время по точностным характеристикам генерируемых импульсов значительно превосходит устройство-прототип. .

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРЕОБРАЗОВАТЕЛЬ НАПРЯЖЕНИЯ В ИНТЕРВАЛ ВРЕМЕНИ | 1991 |

|

RU2032269C1 |

| УСТРОЙСТВО ДЛЯ БЕСКОНТАКТНОГО ИЗМЕРЕНИЯ ИМПУЛЬСНЫХ ТОКОВ | 1990 |

|

RU2024025C1 |

| ФОРМИРОВАТЕЛЬ ИМПУЛЬСОВ ТОКА (ВАРИАНТЫ) | 2024 |

|

RU2821721C1 |

| Формирователь импульсов | 1980 |

|

SU944091A1 |

| Стабилизированный конвертор | 1979 |

|

SU892425A1 |

| ПРЕОБРАЗОВАТЕЛЬ МАСШТАБА ВРЕМЕНИ | 2001 |

|

RU2210783C2 |

| СЧЕТЧИК ЭЛЕКТРИЧЕСКОЙ ЭНЕРГИИ | 2001 |

|

RU2190860C2 |

| Формирователь импульсов | 1987 |

|

SU1522388A1 |

| Электронный коммутатор | 1990 |

|

SU1781448A1 |

| Стабилизированный преобразователь напряжения | 1985 |

|

SU1300608A2 |

УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ТРАПЕЦЕИДАЛЬНЫХ ИМПУЛЬСОВ по авт. св. 620013, отличающеес я тем, что, с целью повышения стабильности работы устройства, в ,иего введены первый интегратор, источник управлямого тока заряда, первый элемент совпадения, второй элемент совпадения, второй и третий интеграторы, компаратор верхнего уровня и компаратор нижнего уровня, уп-. равляемые входы котррых подключены к выходу первого интегратора, вход которого соединен с выходом устройства, а выходы компараторов верхнего и нижнего уровня подключены к первым входам соответственно первого и второго элементов совпадения, вторые входы которых соединены с первой и второй шинами синхроимпульсов эталонной длительности, причем выход первого элемента совпадения подклю« чен ко входу второго интегратора, выход которого соединен с управляющим входом источника управляемого тока заряда, который включен между первой шиной питания и эмиттером транзистора первого ключа, коллектор которого соединен со входом первого интегратора, при этом выход второго элемента совпадения соединен с управлякицим входом третьего интегратора, который включен между первой шиной питания и входом делителя напряжения .

Авторы

Даты

1984-12-30—Публикация

1982-04-23—Подача