.пит.

J.1

3.2

| название | год | авторы | номер документа |

|---|---|---|---|

| Формирователь центра тяжести импульсов | 1983 |

|

SU1129581A1 |

| УСТРОЙСТВО ЗАЩИТЫ СВЕТОДИОДОВ ОТ ПЕРЕГРУЗОК | 2013 |

|

RU2572378C2 |

| Устройство для моделирования электромагнитных процессов в асинхронных машинах | 1989 |

|

SU1681315A1 |

| Формирователь центра тяжести импульсов | 1986 |

|

SU1374173A2 |

| Стабилизированный преобразователь напряжения постоянного тока | 2024 |

|

RU2833008C1 |

| ДВУХТАКТНЫЙ ТРАНЗИСТОРНЫЙ ПРЕОБРАЗОВАТЕЛЬ | 2008 |

|

RU2367081C1 |

| Устройство для ультразвукового контроля качества материалов | 1983 |

|

SU1133544A1 |

| Резистивный узел сеточной модели | 1983 |

|

SU1120366A1 |

| МАЛОГАБАРИТНЫЙ ШИРОТНО-ИМПУЛЬСНЫЙ МОДУЛЯТОР, УСТОЙЧИВЫЙ К ВОЗДЕЙСТВИЮ ИОНИЗИРУЮЩИМ ИЗЛУЧЕНИЕМ | 2013 |

|

RU2557479C2 |

| Стабилизатор напряжения постоянного тока | 2024 |

|

RU2826844C1 |

Изобретение относится к импульсной технике и может быть использовано в устройствах обработки сигналов преимущественно с тахометрических датчиков и предназначено для формирования импульсов из пульсирующего сигнала с дрейфующей постоянной составляющей. Цель изобретения - повышение стабильности и расширение функциональных возможностей - достигается путем обеспечения удвоения частоты входного сигнала и возможности использования дифференциального входа. Формирователь импульсов содержит компараторы 1 и 2, делитель 3 опорных напряжений, RS-триггер 4, логический элемент 5, фильтр 6, интегратор 7 и элемент 8 сложения. Изобретение позволяет расширить область устойчивости работы и повысить быстродействие формирователя. Формирователь может быть реализован в интегральном исполнении на одном кристалле с датчиком, например, с магнитотранзистором. 2 з.п. ф-лы, 5 ил.

Вход

ГН

4

)tod

00 00

фиг Л

10

15

20

Изобретение относится к импульсной технике и может быть использовано в устройствах обработки сигналов, преимущественно с тахометрических датчиков, и предназначено для форми- 5 рования импульсов из пульсирующего сигнала с дрейфующей постоянной составляющей ,

Цель изобретения - повышение стабильности и расширение функциональных возможностей за счет обеспечения удвоения частоты входного -сигнала и возможности использования дифферен- циального входа.

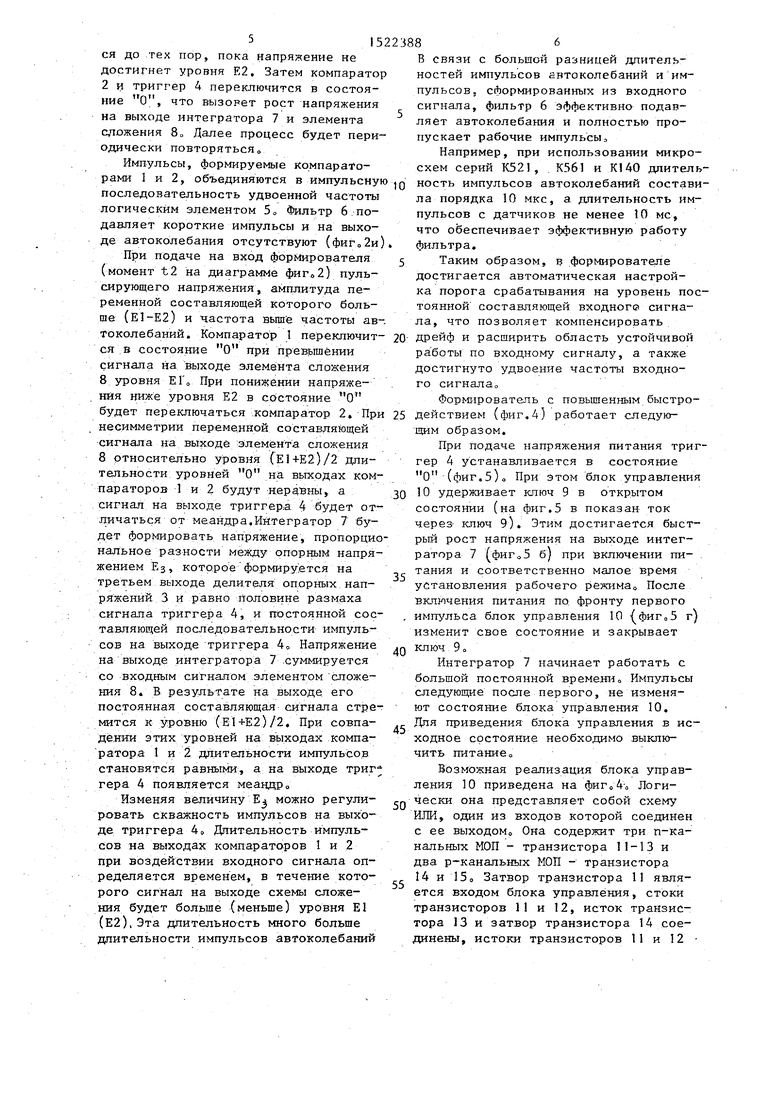

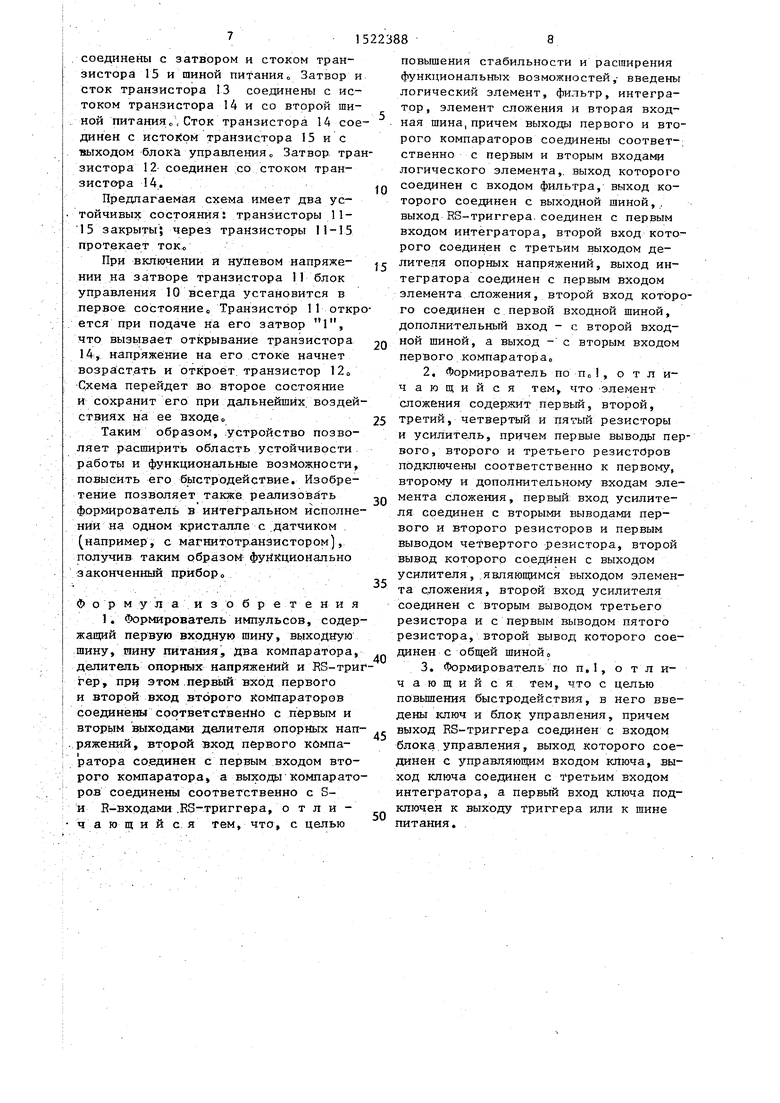

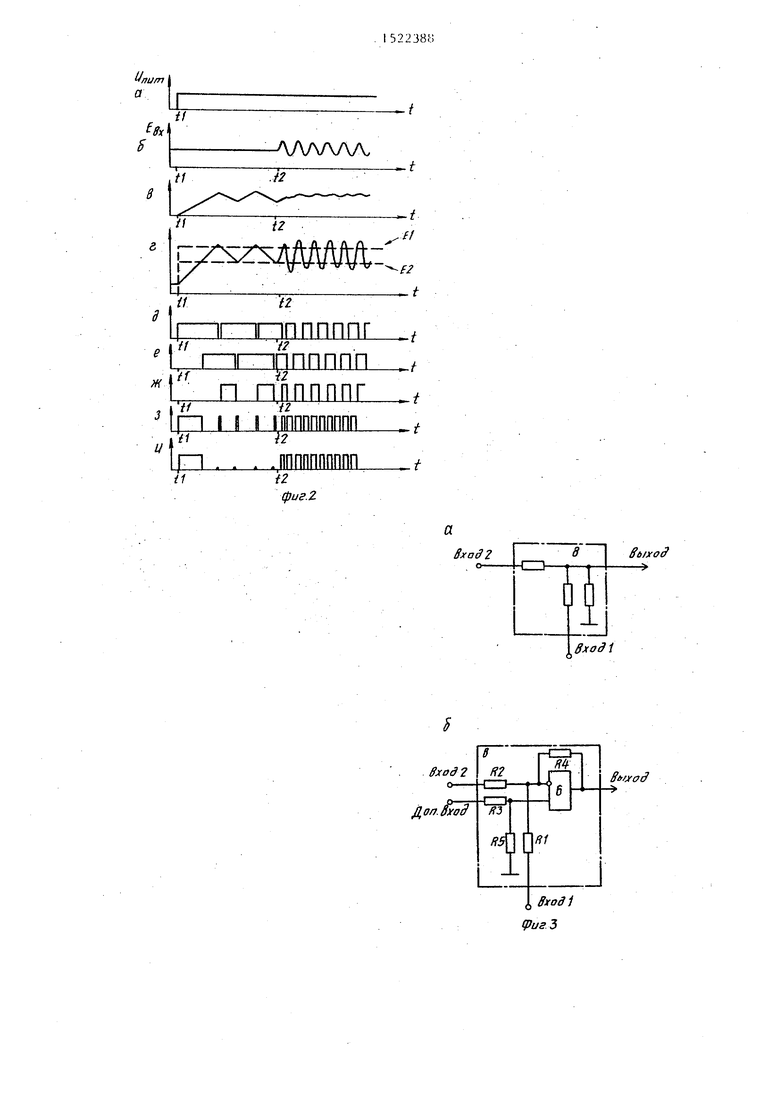

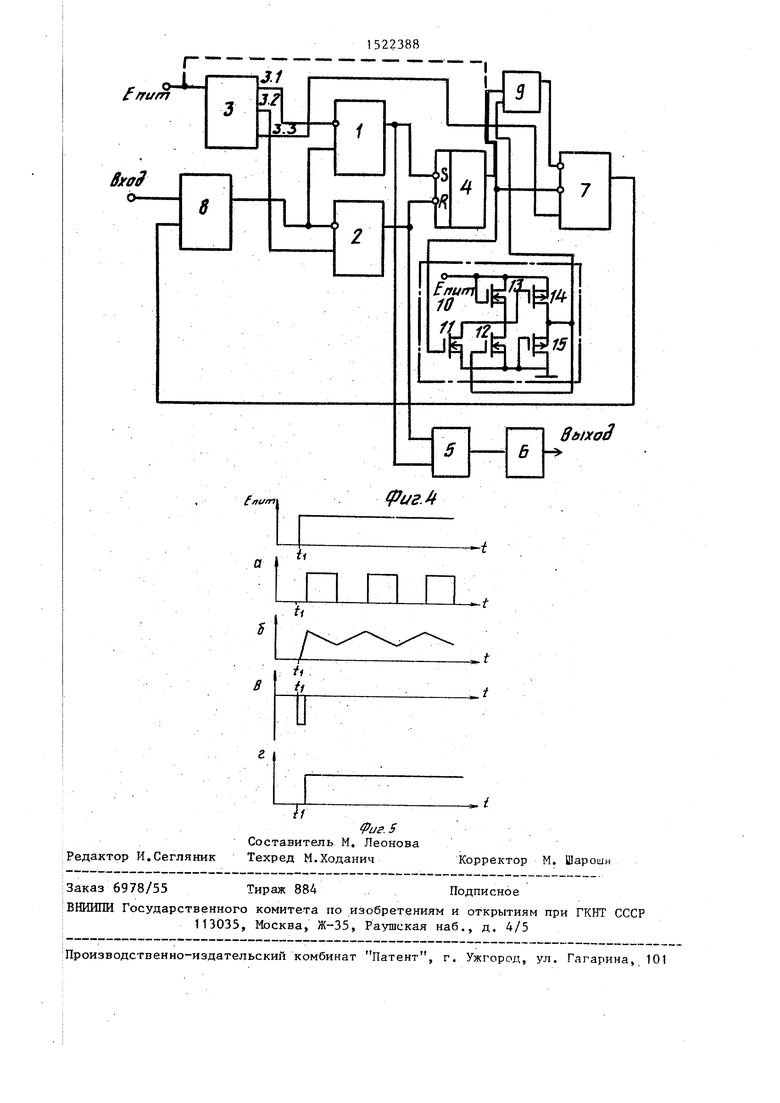

На фиг.1 представлена функциональ- . пая схема формирователя импульсов; на фиг,2 - временная диаграмма, поясняющая его работу; на фиг„3(а,б) - примеры реализации элементов слохе- нр1я; на фиг.4 - функциональная схема формирователя импульсов с повышенным быстродействием; на фиг„5 - временные диаграмм1;Г, поясняющие его работуо

Фop шpoвaтeль импульсов (фиг,. 1) co-jc держит первый 1 и в.торой 2 компараторы, делитель 3 опорных напряжений, RB- триггер 4,- логический элемент 5, . .фильтр 6, интегратор 7 и элемент 8 сложения, входную и выходную щины, причем первый вход компаратора 1 и второй вход компаратора 2 подключены соответственно к первому и второму выходам делителя 3, второй вход компаратора 2 подключен к первому входу компаратора 2, выходы компаратора 1 и 2 подключены соответственно к входам S и R триггера 4, и соответственно к первому и второму входам логического элемента 5, выход которого через фильтр 6 соединен с выходной шинойо Выход триггера 4 подключен к первому входу интегратора 7, -второй вход которого соединен с третьим выходом делителя 3, а выход - к первому входу элемента 8 сложения, вто рой вход которого соединен с входной шиной, а выход подключен ко второму входу компаратора 1«

В формирователе можно использовать различные элементы сложения, для организации дифференциального входа ис- подьзуется элемент сложения (фиг.3б) который содержит пять резисторов и операционный усилитель,, На выходе элемента 8 сложения формируется сигнал, пропорциональный сумме сигналов между вторым и дополнительным входами и первым входом. Коэффициент пере30

40

45

0

5

0

c

0

0

5

дачи входного сигнала определяется резисторами R2-R4, для сигнала с выхода интегратора 7 резисторами R 1 и R 4.

1Т)ормирователь импульсов (фиг.4) лополнительно содержит ключ 9, блок 10 управления, причем выход триггера 4 подключен ко входу блока 10 управления, выход которого подключен к управляющему входу ключа 9, выход ключа 9 соединен с третьим входом интегратора 7, первый вход ключа 9 подсоединен к выходу триггера 4 или к тине питания (пунктир).

Логический элемент 5 выполняет функцию И-НЕ (фиг. 2з) в случае отрицательной логики элемент 5 выполняет функцию ИЛИ-НЕ.

Устройство работает следующим образом

В -исходном состоянии на выходе всех элементов установлено напряжение 0(фиго2)„ В момент t 1 подается напряжение .питания ЕПИГ На. выходе интегратора 7 Гфиг.2 в) в этот момент сохраняется напряжение О, а на выходе схемы сложения 8 (фиг.2 г) реализованной, например, в соответствии с фиг.З а) устанавливается напряжение, меньшее, чем Е 2, которое формируется на втором выходе делителя опорных напряжений 3, в результате чего на выходах компараторов 1 и 2(фиг, 2 д,е и триггера 4 соответственно; устанавливаются состояния 1, О, О, О на входе интегратора 7 вызывает линейный рост напряжения на его выходе и на выходе элемента сложения В фиг,2 г).

При достижении напряжением уровня Е 2, компаратор 2 установится в состояние 1. -Роста напряжения будет продолжаться до уровня Е 1, который формируется на первом выходе делителя 3. Затем компаратор 1 переключится в О и переключит триггер 4 в 1. Это вызовет линейный спад напря- жения на выходе интегратора 7 и элемента сложения В. Напряжение станет меньше Е1 и компаратор 1 установится в состояние логической I Таким образом, на выходе компаратора 1 формируется импульс, длительность О которого будет определяться задержками компаратора -1, триггера 4., элемента сложения 8 и быстродействием интегратора 7 Состояние триггера 4 сохранится и спад будет продолжаться до тех пор, пока напряжение не достигнет уровня Е2. Затем компаратор 2 и триггер 4 переключится в состояние О, что вызовет рост напряжения на выходе интегратора 7 и элемента сложения 8о Далее процесс будет периодически повторяться.

Импульсы, формируемые компараторами 1 и 2, объединяются в импульсную последовательность удвоенной частоты логическим элементом 5о Фильтр 6 подавляет короткие импульсы и на выходе автоколебания отсутствуют (фиго2и)

При подаче на вход формирователя (момент t2 на диаграмме ) пульсирующего напряжения, амплитуда переменной составляющей которого больше (Е1-Е2) и частота вьш е частоты ав-.

токолебаний. Компаратор 1 переключит- 20 Дрейф и расширить область устойчивой О

работы по входному сигналу, а также достигнуто удвоение частоты входного сигнала

Формирователь с повышенным быстрося в состояние U при превышении сигнала на выходе элемента сложения 8 уровня ЕГо При понижении напряжения ниже уровня Е2 в состояние О

будет переключаться .компаратор 2. При 25 действием (фиг,4) работает следун - несимметрии переменной составляющей щим образом.

При подаче напряжения питания триггер 4 устанавливается в состояние О (фиг.5)о При этом блок управления

30

сигнала на выходе элемента сложения 8 относительно уровня (Е1+Е2)/2 длительности уровней О на выходах компараторов 1 и 2 будут неравны а ,сигнал на выходе триггера 4 будет отличаться от меандра.Ийтегратор 7 будет формировать напряжение, пропорциональное разности мезкду опорным напряжением ЕЗ, которое формируется на третьем выходе делителя опорных напряжений 3 и равно поло.вине размаха сигнала триггера 4, и постоянной составляющей последовательности импульсов на выходе триггера 4 Напряжение на выходе интегратора 7 .суммируется со входным сигналом элементом сложе- гшя 8. В результате на выходе его постоянная соетавля1ощая сигнала стремится к уровню (Е1+Е2)/2. При совпадении этих уровней на выходах компаратора 1 и 2 длительности импульсов становятся равными;, а на выходе триг гера 4 появляется меандро

Изменяя величину EJ можно регулировать скважность импульсов на выходе триггера 4о Длительность импульсов на выходах компараторов 1 и 2 при воздействии входного сигнала определяется временем, в течение которого сигнал на выходе схемы сложения будет больше (меньше) уровня Е1 (Е2), Эта длительность много больше длительности импульсов автоколебаний

35

10 удерживает ключ 9 в открытом состоянии (на фиг.5 в показан ток через- ключ 9). Этим достигается быстрый рост напряжения на выходе интегратора 7 |фиго5 б) при включении питания и соответственно малое время установления рабочего режима После включения питания по. фронту первого , импульса блок управления 10 -(фиг,5 г)

изменит свое состояние и закрывает 4Q ключ 9 о

Интегратор 7 начинает работать с большой постоянной временно Импульсы следующие после первого, не изменяют состояние блока управления 10. Для приведения блока управления в исходное состояние необходимо выключить питаниео

Возможная реализация блока управления 10 приведена на фиг,4-о Логически она представляет собой схему ИЛИ, один из входов которой соединен с ее выходом Она содержит три п-ка- нальных МОП - транзистора П-13 и два р-канальных МОП - транзистора 14 и 15о Затвор транзистора 11 является входом блока управления, стоки транзисторов 11 и 12, исток транзистора 13 и затвор транзистора 14 соединены, истоки транзисторов 11 и 12

45

50

55

.

23886

В связи с большой разницей дпитель- ностей импульсов автоколебаний и импульсов, сформированных из входного сигнала, фliльтp 6 эффективно подавляет автоколебания и полностью пропускает рабочие импульсыа

Например, при использовании микросхем серий К521, К561 и К140 дпитель- )Q ность импульсов автоколебаний составила порядка 10 МКС, а длительность импульсов с датчиков не менее 10 мс, что обеспечивает эффективную работу фильтра.

5 Таким образом, t формирователе достигается автоматическая настройка порога срабатывания на уровень постоянной составляющей входного сигнала, что позволяет компенсировать

Дрейф и расширить область устойчивой

работы по входному сигналу, а также достигнуто удвоение частоты входного сигнала

Формирователь с повышенным быстро0

5

10 удерживает ключ 9 в открытом состоянии (на фиг.5 в показан ток через- ключ 9). Этим достигается быстрый рост напряжения на выходе интегратора 7 |фиго5 б) при включении питания и соответственно малое время установления рабочего режима После включения питания по. фронту первого , импульса блок управления 10 -(фиг,5 г)

изменит свое состояние и закрывает Q ключ 9 о

Интегратор 7 начинает работать с большой постоянной временно Импульсы следующие после первого, не изменяют состояние блока управления 10. Для приведения блока управления в исходное состояние необходимо выключить питаниео

Возможная реализация блока управления 10 приведена на фиг,4-о Логически она представляет собой схему ИЛИ, один из входов которой соединен с ее выходом Она содержит три п-ка- нальных МОП - транзистора П-13 и два р-канальных МОП - транзистора 14 и 15о Затвор транзистора 11 является входом блока управления, стоки транзисторов 11 и 12, исток транзистора 13 и затвор транзистора 14 соединены, истоки транзисторов 11 и 12

5

0

5

соединены с затвором и стоком транзистора 15 и шиной питания Затвор и сток транзистора 13 соединены с истоком транзистора 14 и со второй ши- ной питания о,Сток транзистора 14 соединен с истоком транзистора 15 и с выходом блока управления Затвор, транзистора 12- соединен со стоком тран- зисто ра 14.

Предлагаемая схема имеет два устойчивых состояния: транзисторы 11- 15 закрыты; через транзисторы 11-15 протекает токс

При включении и нулевом напряже- j НИИ на затворе транзистора П блок управления 10 всегда установится в первое состояниео Транзистор 11 откроется при подаче на его затвор 1, что вызывает открывание транзистора JQ 14i, напряжение на его стоке начнет возрастать и откроет, транзистор 12о Схема перейдет во второе состояние и сохранит его при дальнейших, воздействиях на ее входе 25

Таким образом, устройство позволяет распщрить область устойчивости работы и функциональные возможности, повысить его быстродействие. Изобретение позволяет также реализова ть п формирователь в интегральном исполнении на одном кристалле с .датчиком (например, с магнитотр.анэистором), получив таким образом фуйкционально законченный прибор

Форм у л а и 3 о б р е т е н и я

50

ч а ю щ и и с я тем, что, с целью

Q

п

5

0

повышения стабильности и расширения функциональных возможностей,- введены логический элемент, фильтр, интегратор, элемент сложения и вторая входная шина,причем выходы первого и второго компараторов соединены соответ-; ственно с первым и вторым входами логического элемента,, выход которого соединен с входом фильтра, выход которого соединен с выходной шиной,, выход RS-триггера соединен с первым входом интегратора, второй вход которого соединен с третьим выходом делителя опорных напряжений, выход интегратора соединен с первым входом элемента сложения, второй вход которого соединен с первой входной щиной, дополнительный вход - с второй входной шиной, а выход - с вторым входом первого компаратора

2,Формирователь по По 1, отличающийся там, что элемент сложения содержит первый, второй, третий, четвертый и пятый резисторы

и усилитель, причем первые выводы первого, второго и третьего резисторов подключены соответственно к первому, второму и дополнительному входам элемента сложения, первый: вход усилителя соединен с вторыми выводами первого и второго резисторов и первым выводом четвертого резистора, второй вывод которого соединен с выходом усилителя,.являющимся выходом элемента сложения, второй вход усилителя соединен с вторым выводом третьего резистора и с первым выводом пятого резистора, второй вывод которого соединен с общей шиной

вход

ffrt/fJl

./

ггг о-

в

7

//WA //

Ч йта/4

- -

ВшхоЗ

/

| Хоровиц П | |||

| и Хилл У | |||

| Искусство схемотехники | |||

| М.: Мир, 1984, То1, Со 421, рис, 7.1 | |||

| Там же, Tol с, 272, рисо 4,23о |

Авторы

Даты

1989-11-15—Публикация

1987-09-23—Подача