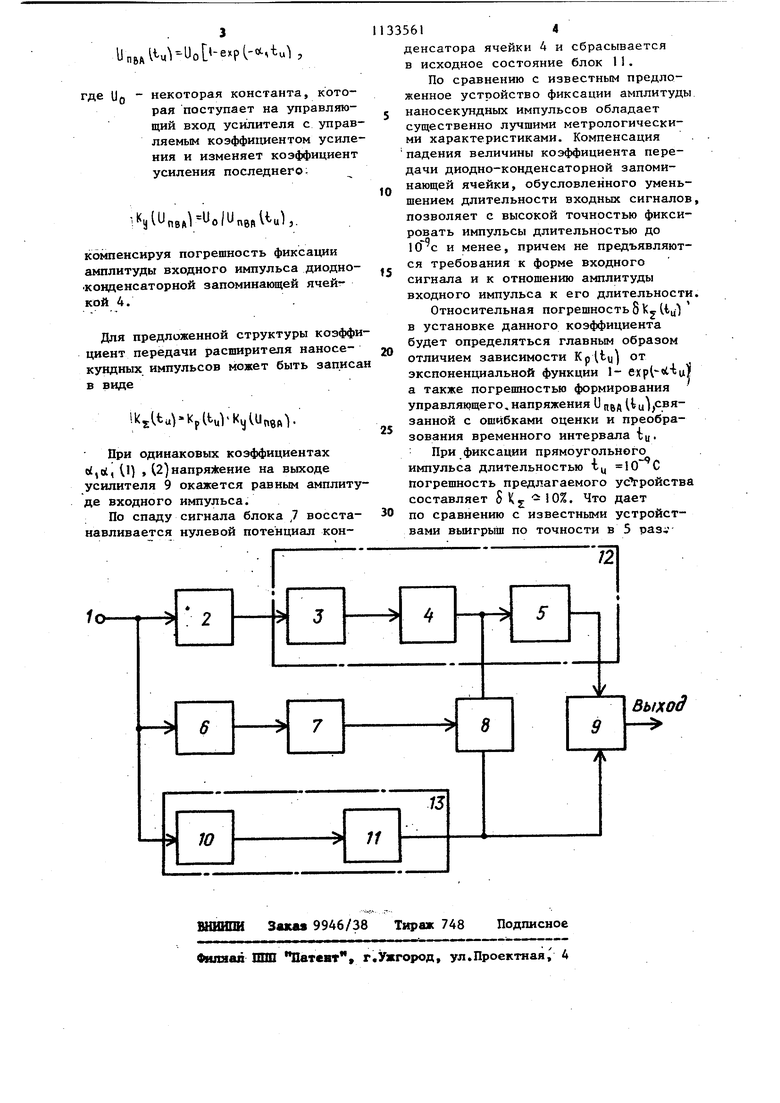

Изобретение относится к измерительной технике и может быть исполь зовано для аналогового преобразования одиночных и редко повторяющихся импульсов в вольтметрах, многоканал ных амплитудных анализаторах и другой информационно-измерительной аппаратуре, предназначенной для прецизионного анализа параметров сверхкоротких оптических и электрических сигналов. Наиболее близким к предлагаемому является устройство фиксации амплитуды импульсов, в котором предусмот рена компенсация погрешности недоза ряда д иодно-конденсаторной запомина ющей ячейки. Известное устройство содержит основной и компенсирующий каналы выполненные по схеме диодно-конденсаторных запоминающих наполнителей, выхрды которых соответственно соеди нены с первым и вторым входами вычислительного блока, в который вход компаратор и интегратор. Выход интегратора является выходом устройства и соединен с входом компенсирующего канала, а входная клемма соединена через пороговый и формир щие блоки с разрядным блоком ij . Недостатком известного устройства является ограниченная область применения, поскольку оно может фиксировать амплитуду входного импульса при условии, что отношение амплитуд импульса к его длительности есть постоянная величина. Цель изобретения - расширение диапазона фиксации амплитуды импуль сов различной длительности. Цель достигается тем, что в устройство, содержащее основной и компе сирующие каналы, выходами соответственно соединенные с первым и вто- рым входами вычислителя,выход которо го является выходом устройства, при этом основной канал выполнен в виде последовательно соединенных первого буферного каскада, диодноконденсаторной запоминающей ячейки и второго буферного каскада, входна шина через последовательно соединен ные пороговый и формирующий блоки соединена с входом блока разряда, выходы которого соответственно соединены с выходом диодно-конденсаторной запоминающей ячейки и выходо компенсирующего канала, введена линия, задержки., включенная между 61 . 1 входной шиной и входом основного канала, а входная шина соединена с входом компенсирующего канала, состоящего из последовательно соединенных блоков фиксации длительности и преобразования время - амплитуда, а в качестве вычислителя используют усилитель с управляемым коэффициентом усиления, второй вход которого является управляющим.. На чертеже представлена принципиальная схема устройства. Устройство содержит входную шину 1, линию 2 задержки, первый буферный каскад 3, диодно-конденсаторную запоминающую ячейку 4, второй буферный каскад 5, пороговый блок 6, формирующий блок 7, блок 8 разряда. Вычислитель на усилителе 9 с управляемым коэффициентом усиления, блок 10 фиксации длительности, блок 11 преобразования время - амплитуда, основной и компенсирующий каналы 12 и 13. Фиксируемый импульс с шины 1 поступает на входы порогового блока 6, блока 10 и через линию задержки 2 и первый буферный каскад 3 - на вход диодно-конденсаторной ячейки 4. Выходной сигнал порогового блока 6 запускает блок 7, в результате чего выключается блок 8 и амплитудное значение входного импульса фиксируется на время работы блока 7 в диодно-конденсаторной ячейке. 4. DB Kpiiu)Uex -expUtu) J где Uj,- амплитуда входного сигнала; Kpl-l )- коэффициент передачи диодноконденсаторной запоминающей ячейки (ДКЗУ). коэффициент определяемый параметрами ДКЗУ; длительность входного импульса. Через второй буферный каскад 5 расширенный импульс, поступает на вход усилителя 9 с управляемым коэффициентом усиления. Одновремен-. но блок 10 вырабатывает стандартизованный по амплитуде импульс с длительностью, равной длительности рас-Ширяемого импульса. С помощью блока 1I, последняя преобразуется в уровень постоянного напряжения УпйАМ-ио -е р1- -ЬиЬ где ио некоторая константа, которая поступает на управляющий вход усилителя с управ ляемым коэффициентом усил ния и изменяет коэффициен усиления последнего; it niUnBftHolU g tJ,. компенсируя погрешность фиксации амплитуды входного импульса диодно конденсаторной запоминающей ячейкой 4. Для предложенной структуры коэфф циент передачи расширителя наносекундных импульсов может быть запис в виде IksUa kpim.KyiUneftV При одинаковых коэффициентах U) (2}напряЧсение на выходе усилителя 9 окажется равным амплит де входного импульса. По спаду сигнала блока ,7 восста навливается нулевой потенциал кон5614денсатора ячейки 4 и сбрасывается в исходное состояние блок 11. По сравнению с известным предложенное устройство фиксации амплитуды наносекундных импульсов обладает существенно лучшими метрологическими характеристиками. Компенсация падения величины коэффициента передачи диодно-конденсаторной запоминающей ячейки, обусловленного уменьшением длительности входных сигналов, позволяет с высокой точностью фиксировать импульсы длительностью до 10 с и менее, причем не предьявляются требования к форме входного сигнала и к отношению амплитуды входного импульса к его длительности. Относительная погрешность 8 Ку ( в установке данного коэффициента будет определяться главным образом отличием зависимости от экспоненциальной функции 1- а также погрешностью формирования управляющего,напряжения U цбд lt;u)занной с ошибками оценки и преобразования временного интервала tu При фиксации прямоугольного импульса длительностью погрешность предлагаемого усТройства составляет 8 К j . Что дает по сравнению с известными устройствами выигрыш по точности в 5 pasi

| название | год | авторы | номер документа |

|---|---|---|---|

| Двухканальный расширитель импульсов | 1979 |

|

SU822330A1 |

| Пиковый детектор | 1979 |

|

SU849083A2 |

| Стабилизатор постоянного напряжения | 1978 |

|

SU811226A1 |

| Амплитудно-временной преобразователь | 1975 |

|

SU527822A1 |

| УСТРОЙСТВО для ПРЕОБРАЗОВАНИЯ АМПЛИТУДЫ НАНОСЕКУНДНЫХ ИМПУЛЬСОВ | 1969 |

|

SU254562A1 |

| Высоковольтный стабилизированный источник питания постоянного тока | 1983 |

|

SU1081630A1 |

| УСТРОЙСТВО для ИЗМЕРЕНИЯ ФЛЮКТУАЦИИ АМПЛИТУДЫ НА ВЕРШИНЕ ИМПУЛЬСНОГО СИГНАЛА | 1967 |

|

SU192856A1 |

| Пиковый детектор | 1975 |

|

SU813268A2 |

| Аналоговое запоминающее устройство | 1981 |

|

SU1015445A1 |

| Устройство для контроля канала связи | 1987 |

|

SU1478351A1 |

УСТРОЙСТВО ДЛЯ ФИКСАЦИИ АМПЛИТУДЫ НАНОСЕКУНДНЫХ ИМПУЛЬСОВ, содержащее основной и компенсирующий каналы, выходами соответственно соединенные с первым и вторым входами вычислителя, выход которого является выходом устройства, при этом Ьсновной канал выполнен в виде последовательно соединенных первого буферного каскада, диодно-кокденсаторной запоминающей ячейки и второго буферного каскада, входная шина через последовательно соединенные пороговый и формирующий блоки соединена с входом блока разряда, выходы которого соответственно соединены с выходом диодно-конденсаторной запоминающей ячейки и выходом компенсирующего канала, отличающееся тем, что, с целью расшипения диапазона фиксации амплитуды импульсов различной длительности, в него введена линия задержки, включеннаямежду входом основного канала и входной шиной, которая соединена с входом компенсирующего канала, состоящего из последовательно сое(Л диненных блоков фиксации длительности и преобразования время амплитуда, а в качестве вьшислителя используют усилитель с управлемым г коэффициентом усиления, второй вход которого является управляющим.

Выход

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| ИМПУЛЬСНЫЙ ВОЛЬТМЕТР | 1972 |

|

SU425116A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1985-01-07—Публикация

1982-07-05—Подача