Изобретение относится к технике электросвязи, в частности к переда дан(;ых, и предназначено для повышения помехоустойчивости приема пу тем снижения влияния межсимвольных искажений, возникающих из-за часто ных искажений в тракте передачи. Известен корректор, содержащий ционированную через такт аналогову линию задержки на N +М тактов, вход и отводы которой через регули руемые аттенюаторы связаны с вычи гающими входами сумматора, причем N-и отвод через постоянный резистор связан с суммирующим входом упомянутого сумматора, выход которого присоединен параллельно к сум мирующему входу определителя ошибк коррекции, к входу формирователя знака посыпок и к входу регенерато ра посыпок, выход которого подключен к вычитающему входу упомянутог определителя ошибки коррекции. Устройство содержит также N +М формирователей составляющей межсим вольной помехи (СМП), в состав каж дого И8 которых входят последовательно соединенные сумматор по модулю два, один из входов которого соединен с выходом регистра задерж ки на N тактов, на вход которого подан нак ошибки коррекции с выхода определителя ошибки коррекции усредняющий реверсивный счетчик, аккумулятор (накапливающий реверсивный счетчик, цифроаналоговый преобразователь) и упомянутый регу лируемый аттенюатор, другой вход сумматора по модулю два и другой вход регулируемого аттенюатора первого формирователя СМП присоеди нены соответственно к входу сдвигаищего регистра с общей задер кой на V +М тактов, на вход кото рого подан знак посылки с выхода .формирователя знака посылки, и к вход линии задержки. Другой вход сумматора по модулю два и другой вход регулируемого аттенюатора второго формирователя СМП подключены соответственно к выходу первой ячейки сдвигающего регистра и к первому отводу линии задержки и т.д. до N -го отвода линии задержки и, до N -го выхода N -и ячейки сдвигакяцего регистра, для которых форм роватедь СШ не предусмотрен, друг гой вход сумматора по модулю два и другой вход егулируеМого атте83нюатора (М+1)-го формирователя присоединены соответственно к выходу (М+1)-й ячейки сдвигающего регистра и к (W -fO-My отводу линии задержки и т.д. до другого входа сумматора по модулю два и другого входа регулируемого аттенюатора последнего (К) +М)-го формирователя СМП, подключенных соответственно к выходу ( Н+М)-й ячейки сдвигающего регистра и к (N +М)-му отводу (выходу) линии задержки Л . Однако это устройство не обеспечивает требуемой точности коррекции и достаточно сложно. Наиболее близким к предложенному по технической сущности и достигаемому результату является корректор, содержащий сдвигакяций регистр, формирователи составляющей межсимвольной помехи, каждый из которых состоит из последовательно соединенных сумматора по модулю два, элемента И, второй вход которого является входом импульсов тактовой частоты, реверсивного счетчика, дешифратора приращений, накопителя и перемножителя, и последовательно соединенные :дифровую линию задержки, вход которой связан с входом сдвигающего регистра через пороговую схему, сумматор, злемент стробирования с запоминанием и амплитудный дискриминатор, вход и выход которого соединены соответственно с входами определителя ошибки коррекции, выход которого подключен к первым входам сумматоров по модулю два, вторые входы которых соединены соответственно с выходами сдвигающего регистра и с вторыми входами соответствующих перемнржителей, выходы котррык соединены с входами вычитания сумматора И. Однако известное устройство не обеспечивает высокой точности коррекции. Цепь изобретения - повьшгение точности коррекции. Поставленная цель достигается Тем, что в корректор, содержащий сдвигающий регистр, формирователи составляющей межсимвольной помехи, каждый из которых состоит из последовательно соединенных сумматора по модулю два, злемента И, второй вход которого является входом импульсов тактовой частоты, реверсивного счетчика, дешифратора прираще3

НИИ, накопителя и перемножителя,

и последовательно соединенные цифрвую линию задержки, вход которой связан с входом сдвигающего регистра через пороговую схему, сумматор элемент стробирования с запоминанием и амплитудный дискриминатор, вход и выход которого соединены соответственно с входами определителя ошибки коррекции, выход которого подключен к первым входам сумматоров по модулю два, вторые входы которьк соединены соответственн с выходами сдвигающего регистра и с вторьв4и входами соответствующих пёремножителей, выходы которых соединены с зкодами вычитания сумматора, введен элемент ИЛИ, при этом выход каждого дешифратора приращений соединен с соответствующим входом элемента ИЛИ, выход которого подключен к вторым входам реверсивных счетчиков.

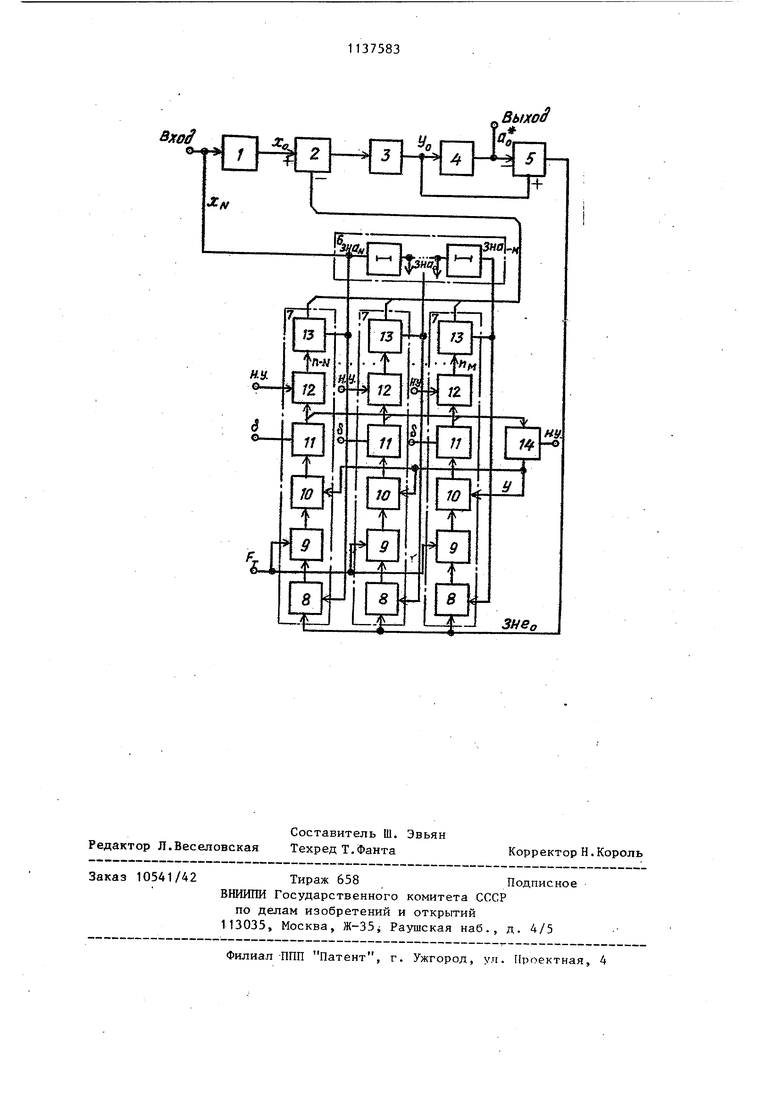

На чертеже представлена структурная электрическая схема корректора. Корректор содержит щ ровую лишпо 1 задержки с общей задержкой на N тактов, сумматор 2, элемент 3 стробирсшания с запоминанием, акг1литуд1шй дискриминатор 4, определитель 5 ошибки коррекции , сдвигающий регистр б с общей задержкой на N +М тактов, фор1шрователи 7 :(М, кащдый из которых состоит из :последовательно соединенных суммаJTopa 8 по модулю два, элемента И 9 Iреверсивного счетчика 10, дешифратора 11 приращений, совмещенного с -умнояителем на шаг коррекции, накопителя 12 и перемножителя 13, а также элемент ШШ 14, при этснм пороговая схема мезкду входом линии 1 задержки и входом сдвигающего регистра 6 на чертеже не показана.

Корректор работает следукядам образом. V

П1жнимаемый сигнал, преобразованный в последовательность i oroразрядных кодовых слоев, поступает на вход цифровой линии 1 задержки, задерживающей сигнал на М тактов, и параллельно через пороговую схему на вход сдвигающего регистра 6 с о0щей задержкой на N +М тактов. Л -разрядная комбинация принимаемого сигнала Х , именяцаяся на выходе Щ1ФРОВОЙ линии 1 задержку, после компенсации составляющих межсимвольной помехи в сумматоре 2

7583Л

поступает на выход корректора в виде

2 -разрядной комбинации как результат стробирования в элементе 3 стробирования с запоминанием. 2 -разрядная комбинация с выхода элемента 3 стробирования с запоминанием поступает на суммирующий вход определителя 5 ошибки коррекции и параллельно на вход амплитудного д дискриминатора 4, содержащего логические цепи, при помощи которых вносится решение, к какому из уровней (О или 1) ближе всего располагается откорректированный сигнал т.е. амплитудный дискриминатор 4 вьщает оценку а сигналу J .

Аналогично пороговая схема, установленная между входом линии 1 задержки и входом сдвигающего регистра 6, вьщает оценку а входного сигнала X ц вместе с ее знакйм зн Q | . Определитель 5 ошибки коррекции, формируя разность между сигналом ( и оценкой QO , выдает ошибку коррекции бд вместе со знаком зн 6 . В соответствии с принятым знаковым алгоритмом для нахождения отсчета hj импульсной реакции на выходе корректора необходимо перемножить знак ошибки коррекции на знак посыпки О , взятые с соответствующими задержками. Такое перемножение двоичных сигналов реализуется в сумматоре 8 по модулю два. Анализ показывает, что от задержки знака ошибки коррек5 1ЩИ на требуемое число тактов мажно отказаться за счет формирования посьшок а , осуществляемого с входа корректора, т.е. использовать только задержанные посыпки зн $1 имеющиеся в сдвигающем регистре 6.

Таким образом, максимально прав.доподобная оценка соответствующего отсчета приведенной импульсной реакции на выходе корректора 5 получается путем накопления приращений в соответствующем накопителе 12 формирователя 7 СИЛ, а приращения получаются в результате усреднения при ПОМО1191 реверсивного счетчика 10 большого количества произведений вида

,, CD

формируемых сумматором 8 по модулю 45 два формирователя 7 СМЛ.

. В соответствии с выражением (1) на один из входов каждого из сумматоров 8 по модулю два всех формироSвателей 7 СМП подан знак ошибки зн 6(5 с выхода определителя 5 ошибк коррекции и на другой вход сумматора 8 по модулю два - знак соответствующей посылки й1 , снимаемый с выхода соответствующей ячейки сдвигающего регистра 6. На входы (сложения и вычитания) реверсивного счетчика 10 поступают импульсы тактовой частоты Р , которые пропускает соответствующий элемент И 9. В начале процесса коррекции содержимое каждого из реверсивных счетчиков 10 и каждого из накопителей 12 всех формирователей 7 СМП устанавливается в начальное состояние по сигналу Н.у. (начальная установка). Для правильной работы корректора необходимо исключить рлучаи переполнения любого из накопителей 12 всех формирователей 7 СМП. В результате усреднения произведений вида (1) наступает момент, когда срабатывает дешифратор 11 при ращений, совмещенный с умножителем на шаг коррекции. В соответствии с этим содержимое соответствующего накопителя 12 изменяется на « 6 или - 8 , где 8 - шаг коррекции; При ПОМО1Щ1 элемента ИЛИ 14, объедин ющего выходы каждого из дешифраторо 11 приращения, совмещенных с умножителями на таг коррекции, всех формирователей 7 СМП, осуществляетс установка в начальное состояние каждого из реверсивных счетчиков 10всех формирователей 7 СМП, если хотя бы один из дешифраторов 11приращения фиксирует переполнение какого-либо реверсивного счетчика 10, что повьш1ает точность коррекции. С выхода накопителя 12 снимается Z -разрядная комбинация соответветствующего отсчета fj приведенной выходной импульсной реакции, поступающая на один из входов соот36ветствующего перемножителя 13 формирователя 7 СМП, на другой вход которого подается оценка зн а; посылки с выхода соответствующей ячейки сдвигающего регистра 6. Результат перемножения поступает на соответствующий вычитающий вход сумматора 2. На выходе сумматора 2 в результате коррекции состав ляющих межсимвольной интенференции образуется сумма в виде V-Xo-..iej, где j - отсчет приведенной импульсной реакции на вьжоде корректора, связанный с отсчетом импульсной реакции как e..o-, -И i U bj , Содержимое каждого из накопителей 12 формирователей 7 СМП в соответствии с итерационным процессом работы корректора изменяется до тех пор, пока сигнал ошибки коррекции, имеющий.ся на выходе определителя 5 ошибки коррекции, не станет равным нулю. Таким образом, повышается точность работы корректора за счет стирания информации о старой ошибке коррекции, когда хотя бы один из реверсивных счетчиков 10 достигает границы счета, во всех реверсивных счетчиках. Применение предлагаемого устройства позволяет увеличить точность коррекции путем исключения ложного набора отсчетов импульсной реакции и обеспечения независимости изменения содержимого каждого из накопителей от изменения содержимого других накопителей. Элемент ИЛИ, объединяюир1й выходы всех дешифраторов приращения, позволяет уменьшить в 3-4 раза. емкость каждого из реверсивных счетчиков.

КОРРЕКТОР, содержащий сдвигающий реги

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для адаптивной настройки корректора межсимвольных искажений | 1977 |

|

SU743212A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Лаки Р.В | |||

| Методы адаптивной коррекции для систем передачи цифровых данных | |||

| Приспособление для получения кинематографических стерео снимков | 1919 |

|

SU67A1 |

Авторы

Даты

1985-01-30—Публикация

1981-12-25—Подача