Изобретение относится к электросвязи и может использоваться для :адаптивной коррекции межсимвольной интерференции в принимаемых сигналах данных. Известен адаптивный корректор ци ровых сигналов, содержащий последовательно соединенные аналого-цифровой преобразователь, запоминающий блок, цифровой перемножитель, сумма тор-накопитель и блок адаптивной настройки tl J. Недостаток известного устройства заключается в том, что для вьщеления тактовой синхронизации используется неоткорре тированный входной сигнал, что ухудшает работу системы синхронизации, а при больших линейных искажениях сигнала (глазковая диаграмма закрыта) делает ее невозможной. Позтому устройство обладает малой помехоустойчивостью и мальпч диапазоном корректируемых линейных искажений принимаемого сигнала. Наиболее близким по технической сущности к предлагаемому является адаптивный цифровой корректор, содержащий последовательно соединенны первый аналого-цифровой преобразователь, первый оперативный з4поминающий блок,цифровой перемножитель и сумматор-накопитель, а также второй оперативный запоминакнций блок, управляемый генератор, блок адаптивной настройки и блок управления причем выход сумматора-накопителя соединен с первьм входом блока адаптивной настройки, второй вход которого соединен с вторым выходом первого оперативного запоминающего блока, первый выход блока адаптивной настройки соединен с вторым вхо дом цифрового перемножителя, первые управляющие входы первого и второго оперативных запоминающих блоков сое динены сбответственно с первым и вт рым выходами-блока управления, третий и четвертый выходы Которого сое динены с третьим и четвертым входам блока адаптивной настройки,а выход управляемого генератора соедине с входом блока управления 2. Данное устройство характеризуется малым диапазоном корректируемых линейных искажений принимаемого сигнала из-за недостаточно зффектив ной работы схемы синхронизации в на чальный период адаптивной настройки корректора. Информация, о фазе вьвдел 9 ется из восстановленного на выходе корректора аналогового сигнала,-который в начальный период настройки неоткорректирован и не отличаетоот входного. При больших линейных искажениях сигнала моменты его переходов через ноль сильно смещены и случайны, что не позволяет схеме синхронизации определить фазу тактовых импульсов и установить синхронизацию. Цель изобретения - расширение диа пазона корректируемых линейных искажений сигнала и, как следствие, повышение помехоустойчивости за счет улучшения совместной работы схем синхронизации ,и 1даптации. Для достижения поставленной цели в адаптивней цифровой корректор, содержащий последовательно соединенные первьй аналого-цифровой преобразователь, первый оптативный запоминающий блок, цифровой перемножитель и сумматор-накопитель, а также второй оперативный запоминающий блок, управляемый генератор, блок адаптивной настройки и блок управления, причем выход сумяатора-накопителя соединен с первым входом блока адаптивной настройки, второй вход которого соединен с вторым выходом первого оперативного запоминающего блока, первьА выход блока адаптивной настройки соединен с вторым входом цифрового переннсякителя, первые управлякнцие входы первого и второго оперативных запоьшнающих блоков соединены соответственно с первым и вторы выходами блока управления, третий и четвертый выходы которого соединены третью и четвертьм входами блока адаптивной настройки, а выход управляемого генератора соединен с входом блока управления, введены второй аналого-цифровой преобразователь, регистр сдвига, цифровой вычитель, два триггера, счетчик и дешифратор, при этом сигнальный вход первого аналого-цифрового преобразователя соединен с сигнальным входом второго аналого-цифрового преобразователя, выход которого соединен с входом второго оперативного запоминающего блока, выход которого соединен с первым входом цифрового пере 1ножителя, выход сумматора-накопителя соединен с сигнал Hbw входом регистра сдвига, первый ж йторой выходы которого соединены с

первым и вторым входами цифрового вычитателя, выход которого соединен с йервым входом первого триггера, выход которого соединен с первым входом управляемого генератора, второй вход первого триггера соединен с пятым выходом блока управления, а второй вход управляемого генератора соединён с первым входом счетчика и с шестым выходом блока управления, выход управляемого генератора соединен с первым входом второго триггера, выход которого соединен с вторым входом счетчика, выход которого соединен с входом дешифратора, первый выход которого соединен с вторым входом второго триггера, а второй и третий выходы соединены соответственно с управляющими входами первого и второго аналого-цифровых преобразователей, вторые управляющие входы первого и второго оперативньос запоми- , нающих блоков и управляющий вход реги- стра сдвига соединены с седьмым выходом блока управления, восьмой выход которого соединен с пятым входом блока адаптивной настройки.

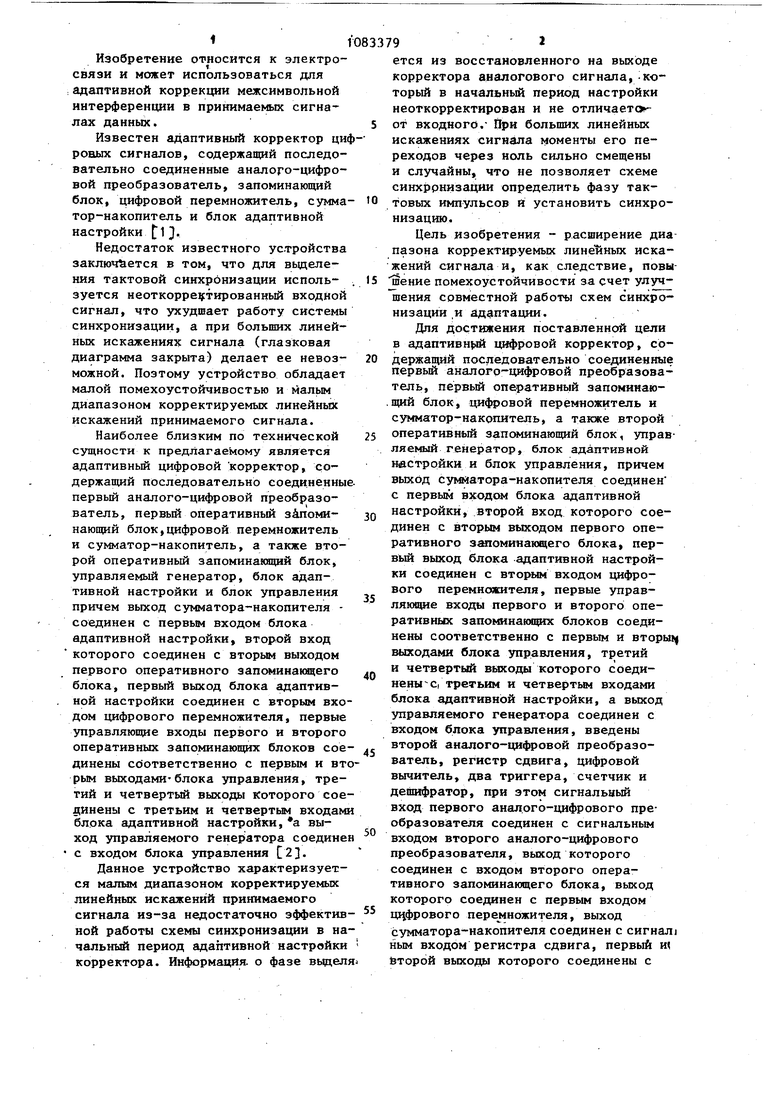

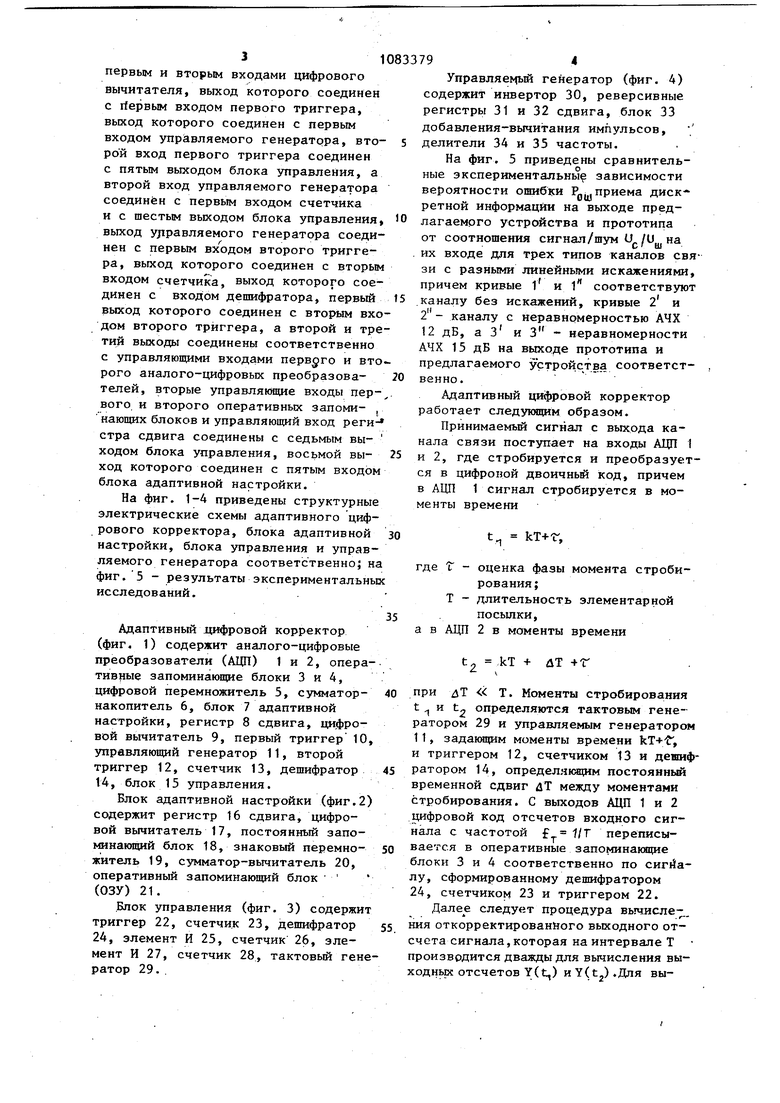

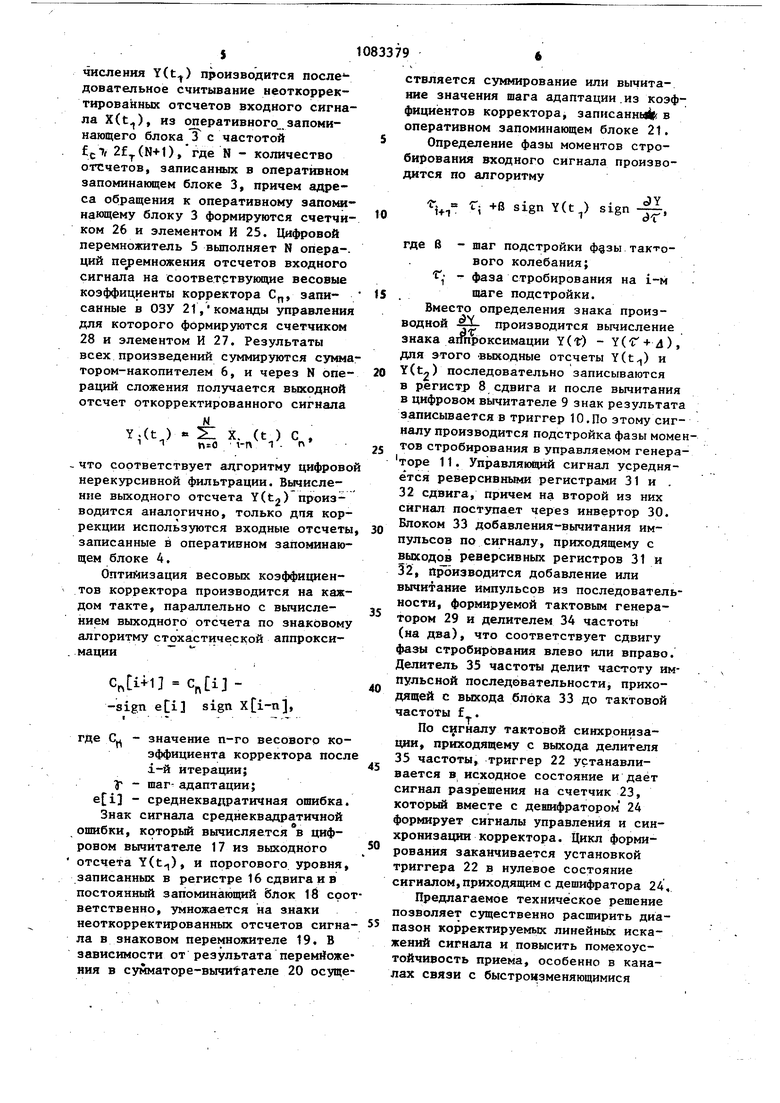

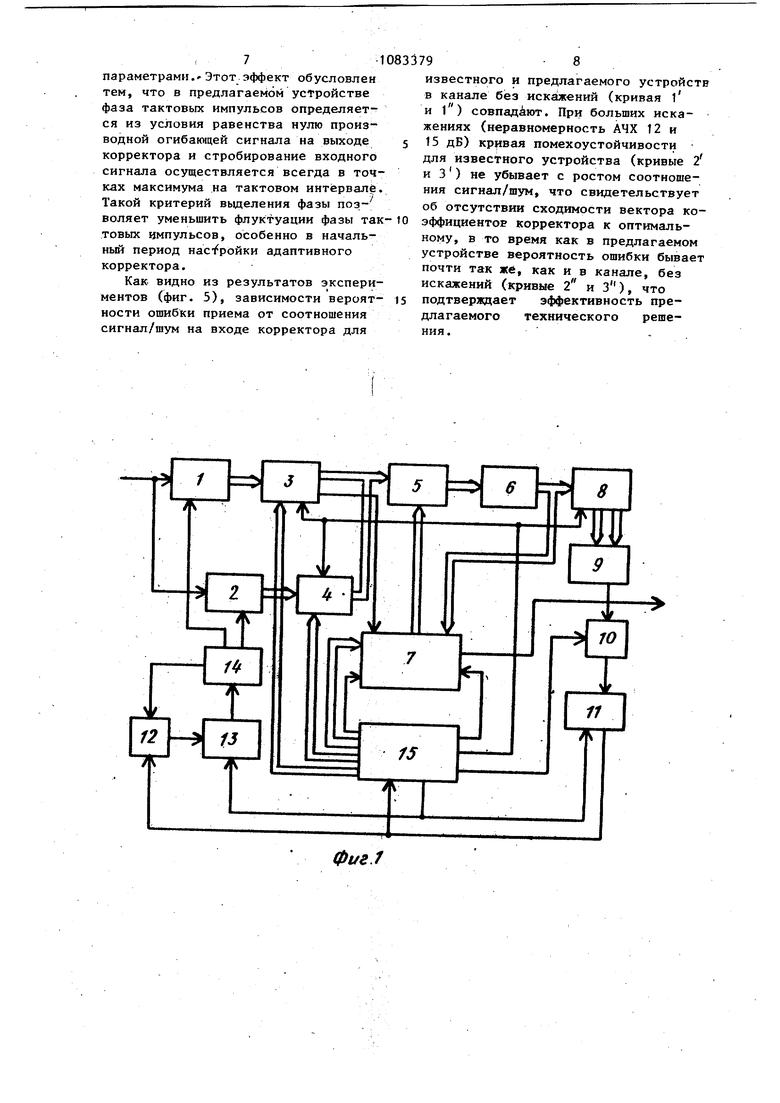

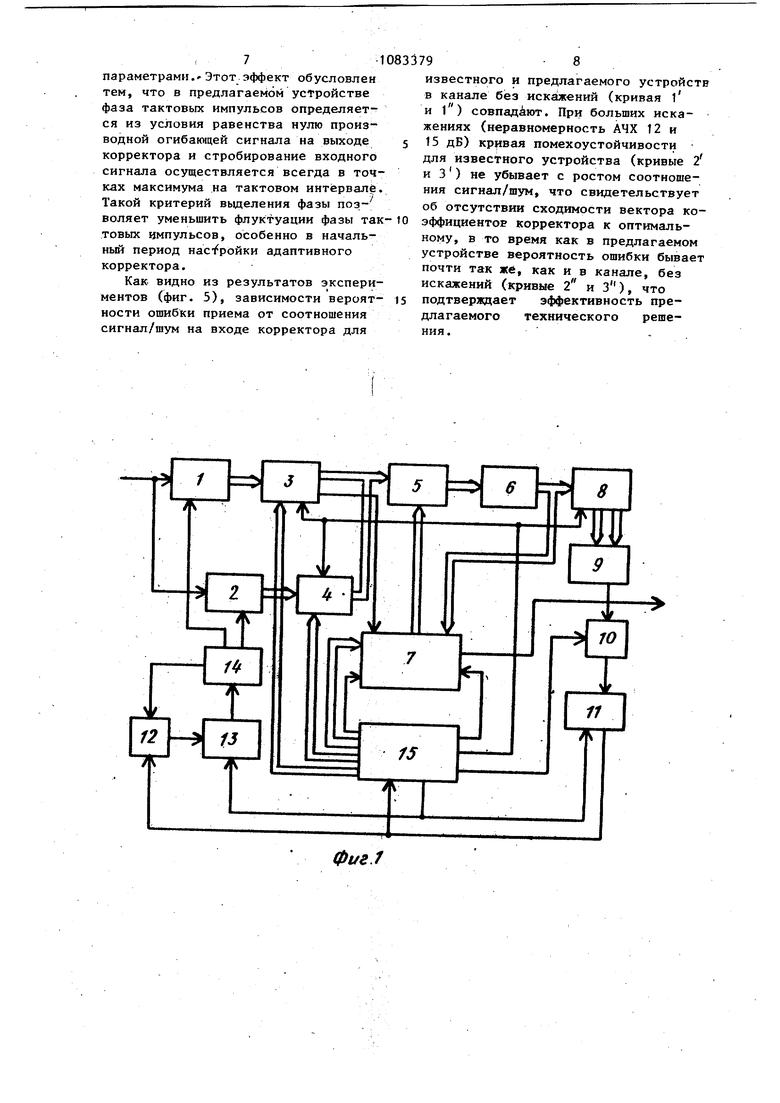

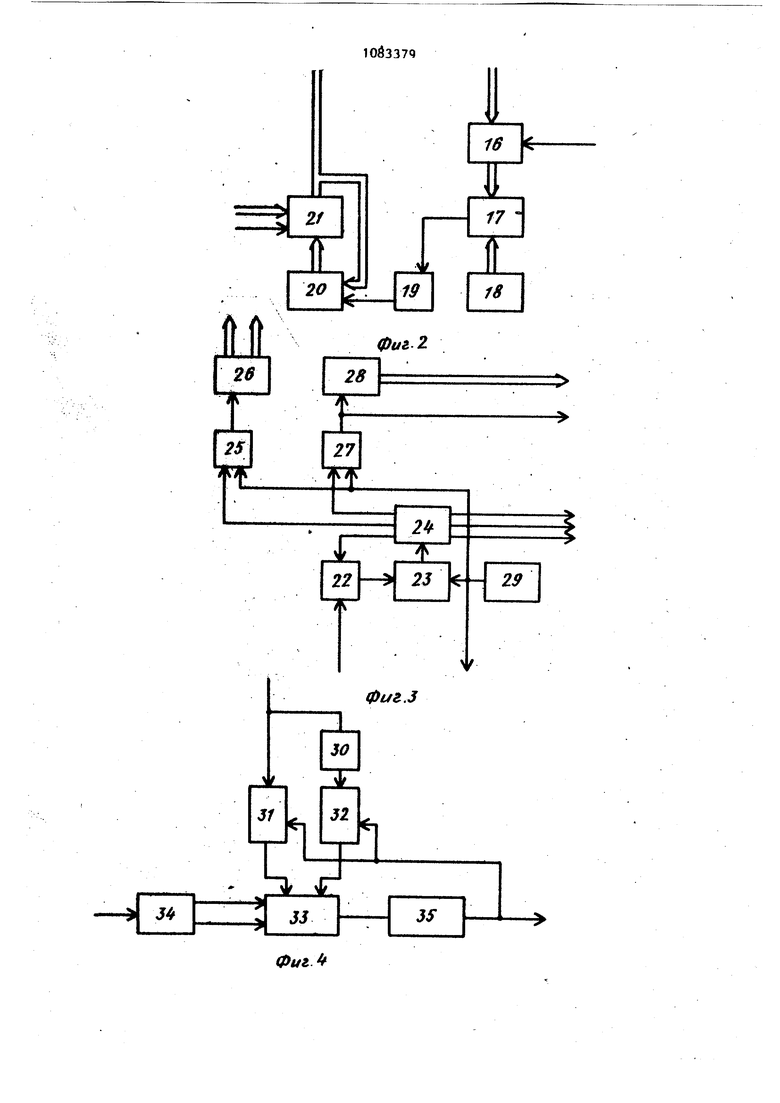

На фиг. 1-4 приведены структурные электрические схемы адаптивного цифрового корректора, блока адаптивной настройки, блока управления и управляемого генератора соответственно} на фиг.5 - результаты экспериментальных исследований.

Адаптивный цифровой корректор (фиг. 1) содержит аналого-цифровые преобразователи (АЦП) 1 и 2, оперативные запоминающие блоки 3 и 4, цифровой перемножитель 5, сумматорнакопитель 6, блок 7 адаптивной настройки, регистр 8 сдвига, цифровой вычитатель 9, первый триггер 10, управляющий генератор 11, второй триггер 12, счетчик 13, дешифратор 14, блок 15 управления.

Блок адаптивной настройки (фиг.2) содержит регистр 16 сдвига, цифровой вычитатель 17, постоянный запоминающий блок 18, знаковый перемножитель 19, сумматор-вьгчитатель 20, оперативный запоминающий блок (ОЗУ) 21.

.Кпок управления (фиг. 3) содержит триггер 22, счетчик 23, дешифратор 24, элемент И 25, счетчик 26, элемент И 27, счетчик 28, тактовый генератор 29.

Управляемый генератор (фиг. 4) содержит инвертор 30, реверсивные регистры 31 и 32 сдвига, блок 33 добавления-вычитания импульсов, делители 34 и 35 частоты.

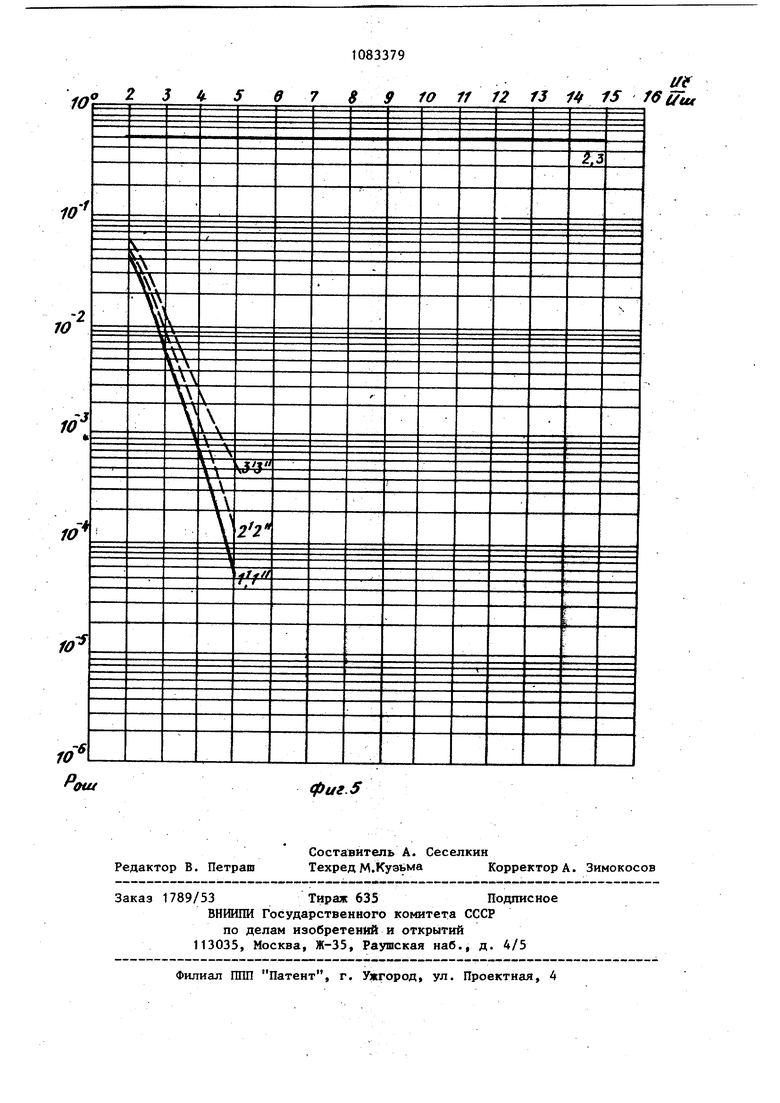

На фиг. 5 приведены сравнительные экспериментальны зависимости вероятности ошибки Р.щ приема дискретной информации на выходе предлагаемого устройства и прототипа от соотношения сигнал/шум на . их входе для трех типов каналов связи с разными линейными искажениями, причем кривые l и 1 соответствуют каналу без искажений, кривые 2 и каналу с неравномерностью АЧХ 12 дБ, а З и 3 - неравномерности АЧХ 15 дБ на выходе прототипа и предлагаемого устройства соответственно.

Адаптивный цифровой корректор работает следукнцим образом.

Принимаемый сигнал с выхода канала связи поступает на входы АЦП 1 и 2, где стробируется и преобразуется в цифровой двоичный код, причем в АЦП 1 сигнал стробируется в моменты времени

t kT+r,

где Т - оценка фазы момента стробирования;Т - длительность элементарной

посьшки, а в АЦП 2 в моменты времени

ty kT + ДТ +r

при Т Т. Моменты стробирования t и t2 определяются тактовым генератором 29 и управляемым генератором 11, заданедим моменты времени kT+T, и триггером 12, счетчиком 13 и дешифратором 14, определякярям постоянный временной сдвиг дТ между моментами стробирования. С выходов АЦП 1 и 2 цифровой код отсчетов входного сигнала с частотой f 1/Т переписывается в оперативные запоминакмцие блоки 3 и 4 соответственно по сигйалу, сформированному дешифратором 24, счетчиком 23 и триггером 22.

Далее следует процедура вычисле-;, ния откорректированного выходного отсчета сигнала, которая на интервале Т производится дважды для вычисления выходньк отсчетов Y(t,) и Y(tp .Для вычисления y(t) производится nocne довательное считывание неоткорректированных отсчетов входного сигнала X(t), из «эп еративного.запоминающего блока 3 с частотой f.l 2f(N+1), где N - количество отсчетов, записанных в оперативном запоминающем блоке 3, причем адреса обращения к оперативному аапоыи наклцему блоку 3 формируются счетчиком 26 и элементом И 25. Цифровой перемножитель 5 выполняет N опера-ций пед)емножения отсчетов входного сигнала на соответствующие весовые коэффициенты корректора С„, эаписанные в ОЗУ 21,команды управления для которого формируются счетчиком 28 и элементом И 27. Результаты всех произведений суммирзпотся сумма тором-накопителем 6, и через N операций сложения получается вькодной отсчет откорректированного сигнала N Y.(t) X. (t ) i-n 1 что соответствует алгоритму цифрово нерекурсивной фильтрации. Вычисление выходного отсчета Y(t2) производится аналогично, только дпя коррекции используются входные отсчеты записанные и оперативном запоминающем блоке 4. Оптийизация весовых коэффициентов корректора производится на каж дом такте, параллельно с вычислением выходного отсчета по знаковом алгоритму стохастической аппроксимации -sign eCi sign , I - .-.. - где С.Д - значение n-го весового ко эффициента корректора пос i-й итерации; ТГ - шаг- адаптации; - среднеквадратичная ошибка Знак сигнала среднеквадратичной ошибки, которьй вычисляется в цифровом вычитателе 17 из выходного отсчета Y(t-,), и порогового уровня записанных в регистре 16 сдвигай в постоянный запоминающий ёлок 1б со ветственно, умножается на знаки неоткорректированных отсчетов сигн ла в знаковом перемножителе 19, В зависимости от результата перемйож ния в cyммaтope-вычиtaтвлe 20 осущ ствляется суммирование или вычитание значения шага адаптации.из коэффициентов корректора, записанн14Ь в оперативном запоминающем блоке 21. Определение фазы моментов стробирования входного сигнала производится по алгоритму , Г- +В sign Y(t) sign-|I. где и - шаг подстройки ф§зы тактового колебания; фаза стробирования на i-м щаге подстройки. Вместо определения знака производной - производится вычисление знака аштроксимации Y(f) -(), для этого выходные отсчеты Y(t) и Y(tj,) последовательно записываются в регистр 8 сдвига и после вычитания в цифровом вычитателе 9 знак результата записывается в триггер 10,По этому сигналу производится подстройка фазы моментов стробирования в управляемом генераторе 11. Управляющий сигнал усредняется реверсивными регистрами 31 и . 32 сдвига, причем на второй из них сигнал поступает через инвертор 30. Блоком 33 добавления-вычитания импульсов по сигналу, приходящему с вькодов реверсивных регистров 31 и 32, Производится добавление или вычитание импульсов из последовательности, формируемой тактовым генератором 29 и делителем 34 частоты (на два), что соответствует сдвигу фазы стробирьвания влево или вправо. Делитель 35 частоть делит частоту импульсной последовательности, приходящей с выхода блока 33 до тактовой частоты f . По сигналу тактовой синхронизащш, приходящему с выхода делителя 35 частоты, триггер 22 устанавливается в исходное состояние и даёт сигнал разрешения на счетчик 23, который вместе с дешифратором 24 формирует сигналы управления и синхронизации корректора. Цикл формирования заканчивается установкой триггера 22 в нулевое состояние сигналом,приходящим с дешифратора 24, Предлагаемое техническое решение позволяет существенно расширить диапазон корректируемых линейньк искажений сигнала и повысить помехоустойчивость приема, особенно в каналах связи с быстроизменяющимися

параметрами. Этот эффект обусловлен тем, что в предлагаемом устройстве фаза тактовых импульсов определяется из условия равенства нулю производной огибающей сигнала на выходе корректора и стробирование входного сигнала осуществляется всегда в точках максимума на тактовом интервал. Такой критерий вьщеления фазы позволяет уменьшить флуктуации фазы так товых импульсов, особенно в начальньй период настройки адаптивного корректора.

Как видно из результатов экспериментов (фиг. 5), зависимости вероятности ошибки приема от соотношения сигнал/шум на входе корректора для

известного и предлагаемого устройств в канале без искажений (кривая 1 и Г) совпадают. При больших искажениях (неравномерность АЧХ 12 и 15 дБ) кривая помехоустойчивости для известного устройства (кривые 2 и 3) не убывает с ростом соотношения сигнал/шум, что свидетельствует об отсутствии сходимости вектора коэффициентов корректора к оптимальному, в то время как в предлагаемом устройстве вероятность ошибки бывает почти так же, как и в канале, без искажений (кривые 2 и З), что подтверждает эффективность предлагаемого технического решения.

| название | год | авторы | номер документа |

|---|---|---|---|

| Адаптивный цифровой корректор | 1987 |

|

SU1506558A2 |

| Адаптивный цифровой корректор | 1979 |

|

SU794734A1 |

| Устройство для приема дискретной информации | 1987 |

|

SU1501298A1 |

| АДАПТИВНЫЙ ЦИФРОВОЙ ЧАСТОТНЫЙ ДИСКРИМИНАТОР | 2000 |

|

RU2166773C1 |

| Устройство для разделения направлений передачи в дуплексных системах связи | 1986 |

|

SU1332542A2 |

| КОРРЕЛЯЦИОННЫЙ ИЗМЕРИТЕЛЬ ВРЕМЕННЫХ СДВИГОВ СЛУЧАЙНЫХ СИГНАЛОВ | 2012 |

|

RU2500025C2 |

| КОРРЕЛЯЦИОННЫЙ ИЗМЕРИТЕЛЬ ВРЕМЕННЫХ СДВИГОВ СЛУЧАЙНЫХ СИГНАЛОВ | 2012 |

|

RU2502128C2 |

| УСТРОЙСТВО ДЛЯ КОМПЕНСАЦИИ АМПЛИТУДНО-ЧАСТОТНЫХ ИСКАЖЕНИЙ В ЛИНЕЙНЫХ ТРАКТАХ С ИСПОЛЬЗОВАНИЕМ ДВУХМЕРНЫХ МЕТРИЧЕСКИХ ПРОСТРАНСТВ | 2006 |

|

RU2342781C2 |

| Адаптивный корректор для системы передачи многоуровневых сигналов | 1975 |

|

SU559399A1 |

| Устройство для обнаружения сигналов и измерения их параметров | 1987 |

|

SU1478145A1 |

АДАПТИВНЫЙ ЦИФРОВОЙ КОРРЕКТОР, содержащий последовательно соединенные первый аналого-цифровой преобразователь, первый оперативный запоминающий блок, цифровой перемножитель и сумматор-накопитель, а также второй оперативный запоминающий блок, управляемый генератор, блок адаптивной настройки и блок управления, причем выход сумматоранакопителя соединен с первым входом блока адаптивной настройки, второй вход которого соединен с вторым выходом первого оперативного запоминающего блока, первый выход блока адаптивной настройки соединен с вторым входом цифрового перемиожителя, первые управляющие входы первого и второго оперативных Запоминающих блоков соединены соответственно с первым и вторым выходами блока управления, третий и четвертый выходы которого соединены с третьим и четвертым входами блока адаптивной настройки, а выход управляемого генератора соединен с входом блока управления, отлич -ощийся тем, что, с целью расщирения диапазона корректируемых линейных искажений сигнала, в него введены второй аналого-цифровой преобразователь, регистр сдвига, цифровой вычитатель, два триггера, счетчик и дешифратор, при этом сигнальньм вход первого аналого-цифрового преобразователя соединен с сигнальным входом второго аналого-цифрового преобразователя, выход которого соединен с вхо дом второго оперативного запоминающего блока, выход которого соединен с первым входом цифрового перемножителя, выход сумматора-накопителя соединен с сигнальным входом регистра сдвига, первый и второй выходы которого соединены с первым и вторым входами цифрового вьиитателя, выход которого соединен с первым входом первого триггера, выход кото(О рого соединен с первым входом управляемого генератора, второй вход первого триггера соединен с пятым выходом блока управления, а второй вход управляемого генератора соединен с первым входом счетчика и с шестым выходом блока управления,выход эо ее со управляемого генератора соединен с первым входом второго триггера, выход которого соединен с вторым входом счетчика, выход которого соеди | нен с входом дешифратора, первый вы;о ход которого соединен с вторым входом второго триггера, а второй и третий выходы соединены соответственно с управляющими входами первого и второго аналого-цифровых преобразователей, вторые управляющие входы первого и второго оперативных запоминающих блоков и управляюпщй вход регистра сдвига соединены с седьмым выходом блока управления, восьмой выход которого соединен с пятым входом блока адаптивной настройки.

ф1/г1

да:

J«

JJ

0Ut

фиг.З

3S 2 5 4 5 в 7 S 9 W

ЙГ

2

rJ

10

10

LtlL

U ir 12 13 i 15 16 i/ut

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Адаптивный цифровой корректор | 1975 |

|

SU519869A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1984-03-30—Публикация

1982-12-02—Подача