2.Устройство по П.1, отличающееся тем, что блок ввделения амплитуды ближней станции выполнен в виде первого и второго однотактных параллельных N -разрядных регистров, выходы которых соответственно подключены к первому и второму входам компаратора, выход которого подключен к R -входу R5 -триггера непосредственно, а к его $-входу через элемент НЕ, прямой

и инверсный выходы R5 -триггера соответственно через первые входы первого и второго элементов И подключены к С -входам первого и второго однотактных параллельных N-разрядных регистров, 33-входы которых запараллелены и являются входом блока вьщеления амплитуды ближней станции, запараллеленные вторые входы элементов И и запараллеленные R-входы однотактных параллельных М-разрядных регистров являются управляющим входом блока вьщеления амплитуды ближней станции, выходом которого является выход второго однотактного параллельного N -разрядного регистра.

3.Устройство по П.1, отличающееся тем, что блок определения перегрузки вьшолнен в виде первого и второго компараторов

и первого и второго источников опорного сигнала, при этом первый вход первого компаратора является входом блока определения перегрузки,второй вход первого компаратора подключен к выходу первого источника опорного сигнала, выход второго источника опорного сигнала подключен к первому входу второго компаратора, второй вход которого подключен к первому входу первого компаратора,а выходы компараторов являются выходом блока определения перегрузки.

4. Устройство по П.1, отличающееся тем, что блок накопления вьтолнен в виде первого и второго элементов И, первые входы которых являются входом блока накопления, а выходы подключены соответственно к 5 -входу и R -входу К5-триггера, выход которого подключен к входу управления реверсом М-разрядного реверсивного счетчика, выход которого является выходом блока накопления, и делителя частоты, выход которого соединен с запараллеленными вторыми входами элементов и непосредственно, а с С-входом М -разрядного реверсивного счетчика через последовательно соединенные элемент задержки и ключ, при этом вход делителя частоты и R-вход М -разрядного реверсивного счетчика являются управляющим входом блока накопления, а первьй, второй и третий управляющие входы ключа подключены соответственно к первьм входам первого и второго элементов И и к выходу элемента ИЛИ, М входов которого подключены к выходу М -разрядного реверсивного счетчика.

| название | год | авторы | номер документа |

|---|---|---|---|

| Акустооптический частотомер | 1988 |

|

SU1626092A1 |

| Цифроаналоговый преобразователь | 1987 |

|

SU1503072A1 |

| Устройство для измерения коэффициента прямоугольности амплитудно-частотной характеристики радиоприемников | 1991 |

|

SU1755384A1 |

| Устройство для измерения коэффициента прямоугольности амплитудно-частотной характеристики радиоприемников | 1990 |

|

SU1755383A1 |

| Измеритель шумов | 1990 |

|

SU1723535A1 |

| Способ локальной радиотелефонной связи и система для его осуществления | 1991 |

|

SU1831767A3 |

| Устройство для измерения уровня радиопомех | 1987 |

|

SU1506396A1 |

| Устройство для измерения ширины спектра сигнала радиопередатчиков на различных уровнях | 1988 |

|

SU1576868A1 |

| Устройство для измерения коэффициента прямоугольности амплитудно-частотной характеристики радиоприемника | 1985 |

|

SU1354135A1 |

| Широкодиапазонный логарифмический аналого-цифровой преобразователь | 1988 |

|

SU1580557A1 |

1. УСТРОЙСТВО ИЗМЕРЕНИЯ ВРЕМЕННЫХ ИНТЕРВАЛОВ, содержащее полосовой фильтр и последовательно соединенные режекторный фильтр, первый дискретный .аттенюатор, аналого-цифровой преобразователь и вычислитель, первьй выход которого подключен к управляющему входу аналого-цифрового преобразователя, а также блок регулировки усиления, вход которого соединен с выходом аналого-цифрового преобразователя,а выход - с управляющим входом первого дискретного аттенюатора, и второй дискретный аттенюатор, о тличающее-ся тем, что, с целью повышения его точности, мезкду выходом блока регулировки усиления и управляющим входом второго дискретного аттенюатора введены последовательно соединенные блок вьщеления амплитуды ближней станции, блок определения перегрузки и блок накопления, при этом выход второго (Л дискретного аттенюатора соединен с входом режекторного фильтра через полосовой фильтр, а управляющие входы блока вьделения амплитуды ближней станции и блока накопления соединены с вторым входом вычислителя. 4 4 О О

Изобретение относится к радионавигации и может использоваться в приемоиндикаторах импульсно-фазовых радионавигационных систем (ИФРНС).

Известно устройство изменения временных интервалов приемоиндикатора ИФРНС Лоран-С, содержащее последовательно включенные входной полосовой, фильтр, режекторньй фильтр, дискретный аттенюатор, выходной Фильтр и вычислитель .

В данном устройстве установленные на входе полосовой и режекторный фильтры ограничивают динамический диапазон и при приеме сигналов ближней станции могут возникнуть перегрузки, снижающие точность измерения.

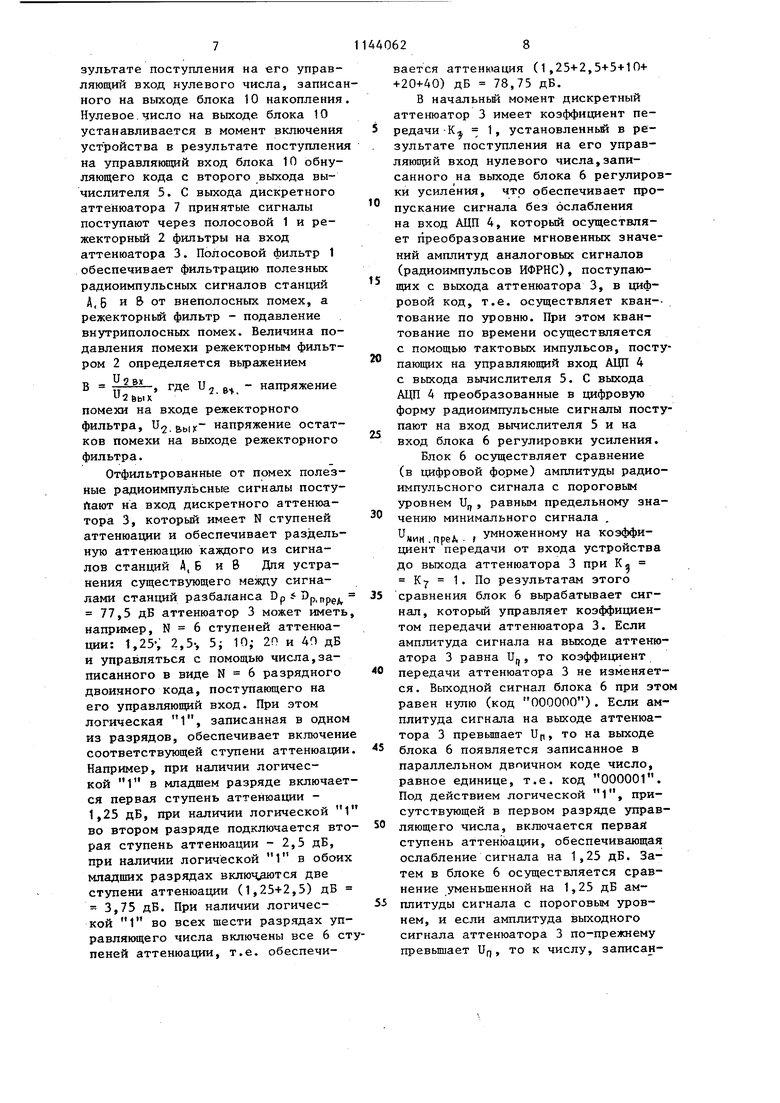

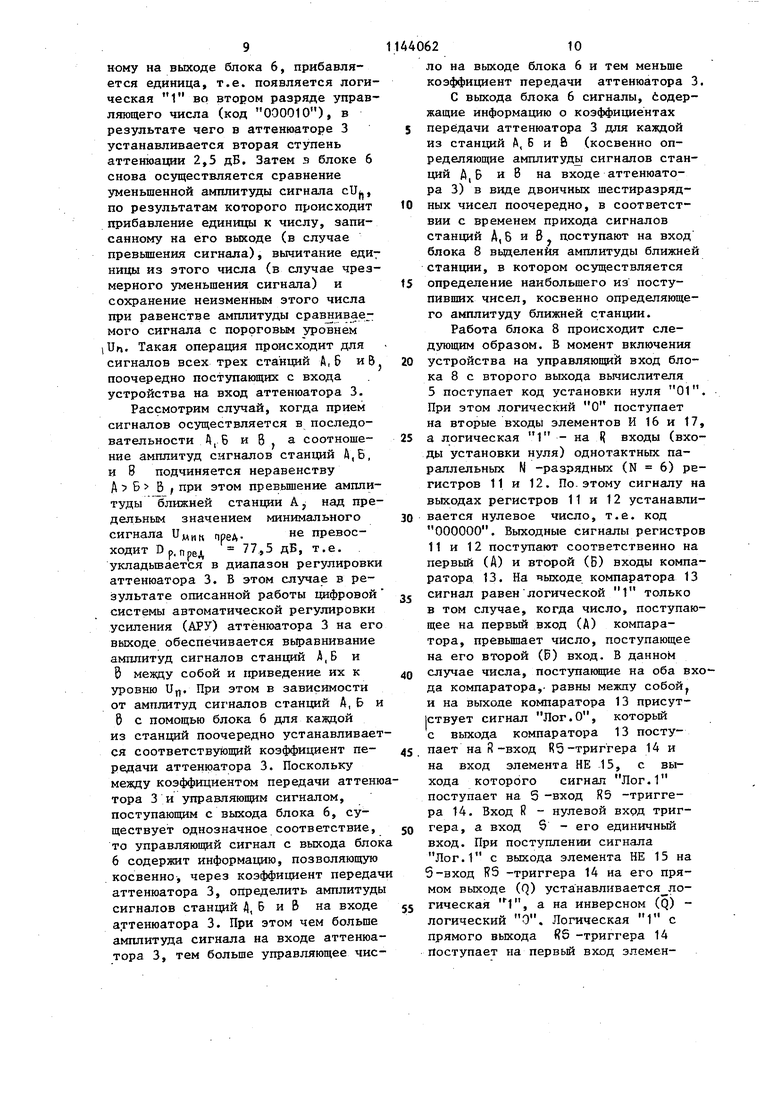

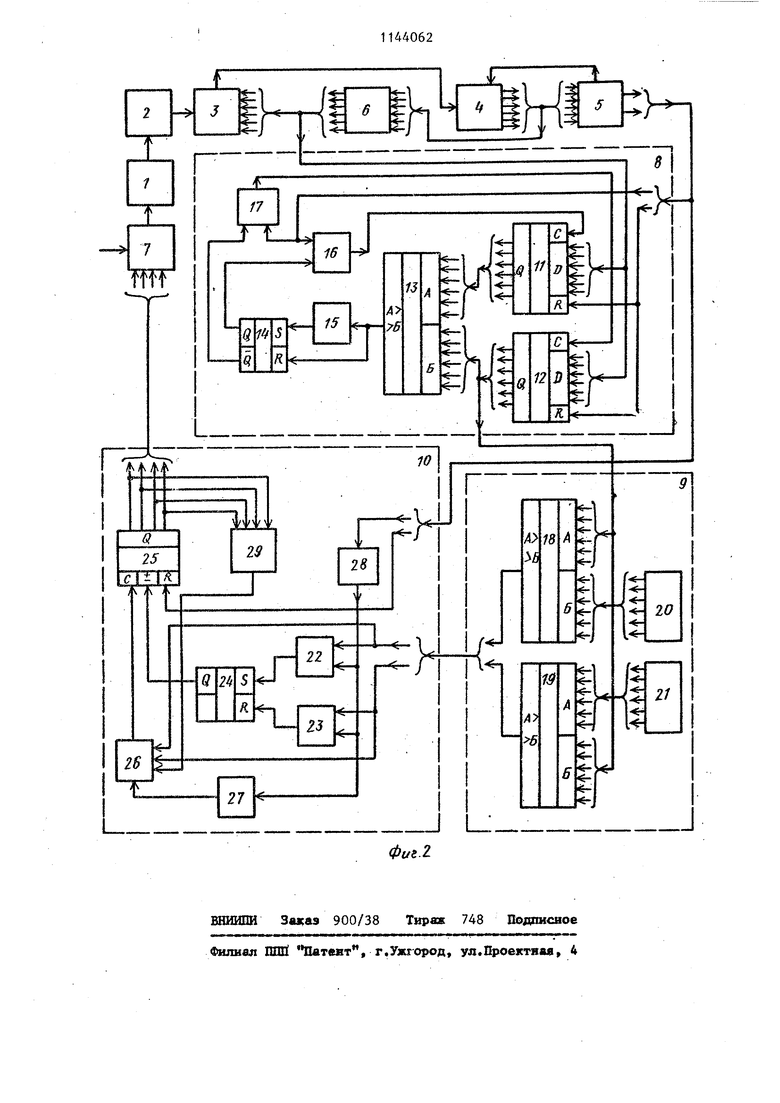

Наиболее близким техническим решением к изобретению является устройство измерения временных интервалов, содержащее полосовой фильтр и последовательно соединенные режекторный фильтр, первый дйс кретный аттенюатор, аналого-цифровой преобразователь и вычислитель первый выход которого подключен к управляющему входу аналого-цифрово го преобразователя, а также блок регулировки усиления, вход которого соединен с выходом аналого-цифрового преобразователя, а выход с управляющим входом первого дискретного аттенюатора, и второй дискретный аттенюатор 2 . Однако известное устройство име ет недостаточную точность измерений. Цель изобретения - повьшение точности. Поставленная цель достигается тем, что в устройство измерения временных интервалов, содержащее полосовой фильтр и последовательно соединенные режекторный фильтр, первый дискретный аттенюатор,аналого-цифрово преобразователь и вы числитель, первьй выход которого подключен к управляющему входу ан лого-цифрового преобразователя, а также блок регулировки усиления, вход которого соединен с выходом аналого-цифрового преобразователя а выход - с управляющим входом первого дискретного аттенюатора,и второй дискретный аттенюатор,мезкд выходом блока регулировки усилени и управляющим входом второго дискретного аттенюатора введены посл довательно соединенные блок вьщел ния амплитуды ближней станции,бло определения перегрузки и блок накопления, при этом выход второго дискретного аттенюатора соединен с входом режекторного фильтра через полосовой фильтр, а управляющие входы блока вьделения амплиту ды ближней станции и блока накопления соединены с вторым выходом вычислителя. I Блок вьщеления амплитуды ближней стан1щи вьшолнен в виде первого и второго однотактньк параллельных N -разрядных регистров, вы ходы которых соответственно подключены к пepвo 4ly. и второму входам компаратора, выход которого подклю чен к R -входу R5-триггера непосредственно, а к его 6 -входу через элемент НЕ, прямой и инверсный выходы RS-триггера соответстве 624 но через первые входы первого и второго элементов И подключены к С-входам первого и второго однотактньк параллельных N -разрядных регистров, I) -входы которых запараллелены и являются входом блока вьщеления амплитуды ближней станцииi запараллеленные вторые входы элементов И и запараллеленные -входы однотактных параллельных N-разрядных регистров являются управляющий входомблока вьщеления амплитуды ближней станции, выходом которого является выход второго однотактного параллельного М -разрядного регистра. Блок определения перегрузки выполнен в виде первого и второго компараторов и первого и второго источников, опорного сигнала, при этом первьй вход первого компаратора является входом блока определения перегрузки, второй вход первого ком- паратора подключен к выходу первого источника опорного сигнала, выход второго источника опорного сигнала подключен к первому входу второго компаратора, второй вход которого подключен к первому входу первого компаратора, а выходы компараторов являются выходом блока определения перегрузки. Кроме того, блок накоштения вы- полнен в виде первого и второго элементов И, первые вхфды которых являются входом блока накопления, а выходы подключены соответственно к 5 -входу и R -входу -триггера, выход которого подключен к входу управления реверсом М -разрядного реверсивного счетчика, выход которого является выходом блока накопления, и делителя частоты, выход которого соединен с запараллеленными вторыми входами элементов И непосредственно, а с С -входом W-разрядного реверсивного счетчика через последовательно соединенные элемент задержки и ключ, при этом вход делителя частоты и R-вход Д-разрядного счетчика являют ся уп- равлярщим входом блока накопления, а первьй, второй и третий управляющие входы ключа подключены соответственно к первым входам первого и второго элементов И и к выходу элемента ИЛИ, М входов которого под ключены к выходу М -разрядного реверсивного счетчика. На фиг.1 представлена структурная электрическая схема предлагаемого устройства на фиг.2 - вариант его реализации. Устройство (фиг.1) содержит полосовой фильтр 1, режекторньй фильтр 2, первый дискретный аттенюатор 3, аналого-цифровой преобра зователь (АЦП) 4, вычислитель 5, блок 6 регулировки усиления, второ дискретньй аттенюатор 7, блок 8 вьщ ления амплитуды ближней станции, блок 9 определения перегрузки и бл 10 накопления. Блок 8 ввделения амплитуды ближ ней станции (фиг.2) содержит первьй и второй однотактные параллель ные N -разрядные регистры 11 и 12, компаратор 13, RS -триггер 14, элемент НЕ 15 и элементы И 16 и 17.. Блок 9 определения перегрузки (фиг.2) содержит первьй и второй компараторы 18 и 19 и источники 20 и 21 опорного сигнала. Блок 1 О накопления (фиг.2) содержит элементы И 22 и 23, R5-триг гер 24, М -разрядный реверсивный счетчик 25, ключ 26, элемент 27 за , держки, делитель 28 частоты и элемент ИЛИ 29. Устройство работает следующим образом. На вход устройства от антенны поступают принятые из эфира последовательности радиоимпульсных сигналов ИФРНС, излучаемые ведущей (А и двумя ведомыми (Б и В) наземными станциями ИФРНС, а также сигналы помехи. Зона приема сигналов станций /1,Б и В является рабочей зоной устройства. В общем случае амплиту ды принятых в рабочей зоне сигналов станций А,б и Б отличаются од на от другой в зависимости от расстояний между станциями А, Б и В местоположением предлагаемого устройства. При этом в любой одной то ке рабочей зоны соотношение (разбаланс) между принимаемыми сигналами максимальной, т.е. ближней, станции и сигналами , минимальной, т.е. дальней, станции определяемое как Dp 20 ig может превьшать значения Dp предЗначение В p. пред определяется геометрией расположения передающих ртанций. Общий динамический диапазон сиг- налов, т.е. соотношение между предельным значением максимального сигнала и g пред, и предельным значением минимального сигнала мич. прел принимаемым в разных точках зоны, например вблизи от передающей станции и на максимальном удалении от нее, составляет вели- . и uake прел чину D5, пред 20 fg мин. прел При этом DO пред I pnpeA,. Устройство с-дополнительно введенной цепью (фиг.2) предназначено для работы в условиях, когда p.frpejv. 115 дБ, Т) р. 77,5 дБ. С входа устройства (фиг.2) принятые радиоимпульсные сигналы и сигналы помех поступают на вход дискретного аттенюатора 7, обеспечивающего изменение общего динамического диапазона устройства с помощью аттенюации сигналов на D. : D j.,.Dp.opg 37,5 дБ. Для этого аттенюатор 3 может имет, например,М 4 ступени аттенюации: 2,5; 5, 10 и 20 дБ, и управляться с помощью числа, записанного в виде М 4 разрядного двоичного кода. При этом логическая 1, записанная в одном из разрядов, обеспечивает включение соответствующей ступени аттенюации. Например, при наличии логической 1 в мпадшем разряде включается первая ступень аттенюации - 2,5 дБ, при наличии логической 1 во втором разряде подключается вторая ступень аттенюации - 5 дБ при наличии логической 1 в общих младших разрядах включаются две ступени аттенюации (2,5+5) дБ 7,5 дБ. При наличии логической 1 во всех четырех разрядах управляющего числа включены все четьфе ступени аттенюации, т.е. обеспечивается аттенюация на (2,5+5+10+20) дБ 37,5 дБ. При наличии логического О во всех четырех разрядах управляющего числа все ступени аттенюации выключены и аттенюатор 7 имеет максимальньш коэффициент передачи, равный единице, т.е. К; 1. В начальный момент дискретньй аттенюатор 7 имеет коэффициент передачи Ку 1, установленный в результате поступления на его управляющий вход нулевого числа, записа ного на выходе блока 10 накопления Нулевое,число на выходе блока 10 устанавливается в момент включения устройства в результате поступлени на управляющий вход блока 10 обнуляющего кода с второго выхода вычислителя 5. С выхода дискретного аттенюатора 7 принятые сигналы поступают через полосовой 1 и режекторный 2 фильтры на вход аттенюатора 3. Полосовой фильтр 1 обеспечивает фильтрацию полезных радиоимпульсных сигналов станций А, 5 и & от внеполосных помех, а режекторньй фильтр - подавление внутриполосных помех. Величина подавления помехи режекторным фильтром 2 определяется выражением -, где и 2 64 - напряжение 2ьых помехи на входе режекторного фильтра, и.аык напряжение остатков помехи на выходе режекторного фильтра. Отфильтрованные от помех полезные радиоимпульсные сигналы постуЛают на вход дискретного аттенюатора 3, который имеет N ступеней аттенюации и обеспечивает раздельную аттенюацию каждого из сигналов станций А,Б и 8 Для устранения существующего между сигналами станций разбаланса Вр5Вр,„р 77,5 дБ аттенюатор 3 может иметь например, N 6 ступеней аттенюации: 1,25, 2,5-, 5i 10; 20 и 40 дБ и управляться с помощью числа,записанного в виде N 6 разрядного двоичного кода, поступающего на его управляющий вход. При этом логическая 1, записанная в одном из разрядов, обеспечивает включени соответствующей ступени аттенюации Например, при наличии логической 1 в младшем разряде включает ся первая ступень аттенюации 1,25 дБ, при наличии логической во втором разряде подключается вт рая ступень аттенюации - 2,3 дБ, при наличии логической 1 в обои младщих разрядах включаются две ступени аттенюации (1,25+2,5) дБ -- 3,75 дБ. При наличии логической 1 во всех шести разрядах уп равляющего числа включены все 6 с пеней аттенюации, т.е. обеспечивается аттенюация (1 ,25+2,5+5-«-10+ +20+40) дБ 78,75 дБ. В начальньй момент дискретный аттенюатор 3 имеет коэффициент передачи -К 1, установленньй в результате поступления на его управляющий вход нулевого числа,записанного на выходе блока 6 регулировки усиления, что обеспечивает пропускание сигнала без ослабления на вход АЦП 4, который осуществляет преобразование мгновенных значений амплитуд аналоговых сигналов (радиоимпульсов ИФРНС), поступающих с выхода аттенюатора 3, в цифровой код, т.е. осуществляет кван-тование по уровню. При этом квантование по времени осуществляется с помощью тактовых импульсов, поступающих на управляющий вход АЦП 4 с выхода вычислителя 5. С выхода АЦП 4 преобразованные в цифровую форму радиоимпульсные сигналы поступают на вход вычислителя 5 и на вход блока 6 регулировки усиления. Блок 6 осуществляет сравнение (в цифровой форме) амплитуды радиоимпульсного сигнала с пороговым уровнем и, равным предельному значению минимального сигнала , мин пред, I умноженному на коэффициент передачи от входа устройства до выхода аттенюатора 3 при К. К 1. По результатам этого сравнения блок 6 вьрабатывает сигнал, который управляет коэффициентом передачи аттенюатора 3. Если амплитуда сигнала на выходе аттенюатора 3 равна и, то коэффициент передачи аттенюатора 3 не изменяется . Выходной сигнал блока 6 при этом равен нулю (код 000000). Если амплитуда сигнала на выходе аттенюатора 3 превьшает Up, то на выходе блока 6 появляется записанное в параллельном двпичном коде число, равное единице, т.е. код 000001. Под действием логической 1, присутствующей в первом разряде управляющего числа, включается первая ступень аттенюации, обеспечивающая ослабление сигнала на 1,25 дБ. Затем в блоке 6 осуществляется сравнение уменьщенной на 1,25 дБ амплитуды сигнала с пороговым уровнем, и если амплитуда выходного сигнала аттенюатора 3 по-прежнему превышает Up, то к числу, записан91

ному на выходе блока 6, прибавляется единица, т.е. появляется логическая 1 во втором разряде управляющего числа (код 000010), в результате чего в аттенюаторе 3 устанавливается вторая ступень аттенюации 2,5 дБ, Затем з блоке 6 снова осуществляется сравнение уменьшенной амплитуды сигнала cUt, по результатам которого происходит прибавление единицы к числу, записанному на его выходе (в случае превьшения сигнала), вычитание еди7 ницы из этого числа (в случае чрезмерного уменьшения сигнала) и сохранение неизменным этого числа при равенстве амплитуды сравниваеого сигнала с пороговым уровнем n. Такая операция происходит для игналов всех трех станций А, 6 иВ оочередно поступающих с входа стройства на вход аттенюатора 3. Рассмотрим случай, когда прием игналов осуществляется в последоательности А, Б и 8 J а соотношеие амплитуд сигналов станций Д,Б, В подчиняется неравенству А Б Ъ f при этом превьш1ение амплитуды ближней станции Aj над предельным значением минимального сигнала пред. не превосходит Dp. npgj, 77.,5 дБ, т.е. укладывается в диапазон регулировки аттенюатора 3. В этом случае в результате описанной работы цифровой системы автоматической регулировки усиления (АРУ) аттенюатора 3 на его выходе обеспечивается выравнивание амплитуд сигналов станций А, Б и Ь между собой и приведение их к уровню и. При этом в зависимости от амплитуд сигналов стангдай А, & и Ь с помощью блока 6 для каждой из станций поочередно устанавливается соответствующий коэффициент передачи аттенюатора 3. Поскольку между коэффициентом передачи аттенюатора 3 и управляющим сигналом, поступающим с выхода блока 6, существует однозначное соответствие, то управляющий сигнал с выхода блока 6 содержит информацию, позволяющую косвенно, через коэффициент передачи аттенюатора 3, определить амплитуды сигналов станций 4, Б и В на входе аттенюатора 3. При этом чем больше амплитуда сигнала на входе аттенюатора 3, тем больше управляющее чис06210

ло на выходе блока 6 и тем меньше коэффициент передачи аттенюатора 3. С выхода блока 6 сигналы, йодержащие информацию о коэффициентах передачи аттенюатора 3 для каждой из станций А, Б и 8 (косвенно определяющие амплитуды сигналов станций Д| В и 8 на входе аттенюатора 3) в виде двоичных шестиразрядных чисел поочередно, в соответствии с временем прихода сигналов станций А,В и 6. поступают на вход блока 8 ввделенйя амплитуды ближней станции, в котором осуществляется

определение наибольшего из поступивших чисел, косвенно определяющего амплитуду ближней станции.

Работа блока 8 происходит следующим образом. В момент включения

устройства на управляющий вход блока 8 с второго выхода вычислителя 5 поступает код установки нуля 01. При этом логический О поступает на вторые входы элементов И 16 и 17,

а логическая 1 - на Ч входы (входы установки нуля) однотактных параллельных N -разрядных (N 6) регистров 11 и 12. По.этому сигналу на выходах регистров 11 и 12 устанавливается нулевое число, т.е. код

000000. Выходные сигналы регистров 11 и 12 поступают соответственно на первый (А) и второй (Б) входы компаратора 13. На чыходе компаратора 13

сигнал равен логической 1 только в том случае, когда число, поступающее на первый вход (А) компаратора, превьш1ает число, поступающее на его второй (5) вход. В данном

случае числа, поступающие на оба вхо да компаратора, равны между собойj и на выходе компаратора 13 присутствует сигнал Лог.О, которьй с выхода компаратора 13 поступает на R-вход R5-триггера 14 и на вход элемента НЕ 15, с выхода которого сигнал Лог.1 поступает на S -вход R5 -триггера 14. Вход R - нулевой вход триггера, а вход 5 - его единичный вход. При поступлении сигнала Лог.1 с выхода элемента НЕ 15 на 5-вход RS -триггера 14 на его прямом выходе (Q) устанавливается логическая 1, а на инверсном (Q) логический О. Логическая Г с прямого выхода R5 -триггера 14 Поступает на перзьй вход элемен.11 . та И 16, а логический О с инверс ного выхода RS -триггера 14 на первьй вход элемента И 17. Поскольку первоначально на вторые входы элементов И 16 и 17 с утгравляющего входа блока 8 поступает логический О, то выходные сигналы элементов И 16 и 17 равны логическому О. Сигналы Лог.О с выходов элементов И 16 и 17 поступают на С -входы регистров 11 и 12, на выходах которых при этом сохраняются нулевые выходные сигналы . После отработки системы АРУ аттенюатора 3 с выхода блока 6 на информационный вход блока 8, т.е. на ID -входы регистров 11 и 12, поступает записанное в виде шестиразрядного параллельного двоичного кода управляющее число, косвенно определяюп1ее амплитуду сигнала станции А а с второго выхода вычислителя 5 на управляющий вход блока 8 - тактовый импульс, представляющий собой двоичное число 10, записанное в виде двухразряд ного параллельного двоичного кода. При этом на вторые входы . элементов И 16 и 17 поступает сигнал Лог.1, в результате чего на-выходе элемента И 16 появляется логическая 1. Под действием логической 1, поступившей с выхода элемента И 16 на С -вход регист ра 11, на выходе регистра 11 вмест нулевого числа записывается управляющее число с выхода блока 6, кос венно определяющее амплитуду сигна ла станции А на входе аттенюатор 3, Это число поступает на первьй вход компаратора 13, на второй вхо которого поступает нулевое число с выхода регистра 12. Поскольку управляющее число, определяющее амплитуду сигнала станции А боль ше нуля, на выходе компаратора 13 появляется сигнал Лог. Г , который поступает на R -вход R5 -триггера 14, устанавливая тем самым на его прямом выходе (Q) логический О, на инверсном (Q) - логическую 1. С инверсного выхода R5 -триггера 14 сигнал Лог.1 поступает на первьй вход элемента И 17. На втором такте работы блока 8 с выхода блока 6 на D -входы регис 62 ров 11 и 12 поступает управляющеечисло, соответствующее сигналу станции Bj а с второго выхода вычислителя 5 на управляющий вход блока 8 поступает тактовьй импульс - двоичное число 10, записанное в параллельном двоичном коде. При этом на вторые входы элементов И 16 и 17 поступает сигнал Лог.1, в результате чего на выходе элемента И 17 появляется логическая 1. Под действием логической 1, поступившей с выхода элемента И 17 на С -вход регистра 12, на выход которого, вместо нулевого числа записывается управляющее число с выхода блока 6, косвенно определяющее амплитуду сигнала станции 6 . Это число поступает на второй вход компаратора 13, на первый вход которого с выхода регистра 11 поступает число, определяющее амплитуду станции А, Поскольку амплитуда сигнала станции Д больше амплитуды сигнала станции Б на выходе компаратора 13 сохраняется логическая 1. Сигнал Лог.1 с выхода компаратора 13 поступает на R-вход fi5 -триггера 14, устанавливая тем самым на его прямом (Q) выходе логический О, а на инверсном (Q) - логическую 1. С инверсного выхода R5-триггера 14 сигнал Лог.1 поступает на первый вход элемента И 17. На третьем такте работы блока 8 с выхода блока 6 на D -входы регист ров 11 и 12 поступает управляющее число, определяющее амплитуду сигнала станции а с второго выхода вьиислителя 5 на управляющий вход блока 8 поступает тактовьй импульс - двоичное число 10. При этом на вторые входы элементов И 16 и 17 поступает сигнал Лог.1, в результате чего на выходе элемента И 17 появляется логическая 1. Под действием логической 1, поступающей с выхода элемента И 17 на С -вход регистра 12, на выходе регистра 12 записывается управляющее число с выхода блока 6, определяющее амплитуду сигнала станции 8. Это число поступает на второй вход компаратора 13, на первый вход которого с выхода регистра 11 поступает число, определяющее амплитуду станции Д. Поскольку амплитуда сиг131

нала станции А больше амплитуды сигнала станции 6 на выходе компаратора 13 сохраняется сигнал Лог.1, который поступает на . -вход RS-триггера 14, устанавливая тем самым на его прямом (Q) выходе логический О, а на инверс ном (Q) - логическую 1. С инверсного выхода RS-триггера 14 сигнал Лог.1 поступает на первьй вход элемента И 17.

На четвертом такте работы блока 8 с выхода блока 6 на D -входы регистров 11 и 12 вновь поступает управляющее число, соответствующее амплитуде сигнала станции Д а с второго выхода вычислителя 5 на управляющий вход блока 8 поступает тактовый импульс - двоичное число 10. При этом на вторые входы элементов И 16 и 17 поступает сигнал Лог.1, в результате чего на

входе элемента И 17 появляется логическая 1. Под действием логической 1, поступившей с выхода элемента И 17 на С -вход регистра 12, на выход регистра 12 за1шсывается управляющее число с выхода блока 6, определяющее амплитуду сигнала станции А, Это число поступает на второй вход компаратора 13, на первый вход которого с вькода регистра 11 также поступает число, определяющее амплитуду стантдан А , Поскольку числа, поступающие на оба входа компаратора 13, равны между собой, на выходе компаратора 13 появляется сигнал Лог.О, который поступает на вход элемента НЕ 15, с его выхода поступает на 5 -вход R5 -триггера 14, устанавливая тем самым на его прямом выходе логическую 1, а на инверсном - логический О. С прямого выхода R 5-триггера 14 сигнал Лог.1 поступает на первый вход элемента И 16.

На пятом такте .работы блока 8 с выхода блока 6 на 3) -входы регистров 11 и 12 поступает управляющее число, определяющее амплитуду сигнала станции Б, а с второго выхода вычислителя 5 на управляющий вход блока 8 поступает тактовьй импульс двоичное число 10. При этом на вторые выходы элементов И 16 и 17 поступает сигнал Лог.1, в результате чего на йыходе элемента И 16

406214

появляется логическая 1. Под действием логической 1, поступающей с выхода элемента И 16 на С-вход регистра 11, на выходе регистра 11 записывается число,

соответствующее амплитуде сигнала станции В . Это число поступает на первый вход компаратора 13, на второй вход которого с выхода регистfO pa 12 поступает число, соответствующее амплитуде станции А( Поскольку амплитуда сигнала станции А больше амплитуды сигнала станции Б, на выходе компаратора 13 сохраня 5 ется сигнал Лог.О, который поступает на вход элемента НЕ 15, ас его выхода поступает на 5 -вход Йб-триггера 14, устанавливая тем самым на его .прямом выходе логическую 1, а на инверсном - логический О. С прямого выхода RS-триггера 14 сигнал Лог.1 поступает на первый вход элемента И 16. Аналогичным образом происходит

25 работа блока 8 на шестом, седьмом и т.д. тактах.

Из рассмотренного видно, что, начиная с четвертого такта, на выходе регистра 12, являющегося выходом блока 8, вьделяется наибольшее из поступивших с выхода блока 6 управляющих чисел, косвенно определяющее амплитуду ближней станции на входе аттенюатора 3. Не трудно показать, что при любом другом распределении соотношений амплитуд сигналов станций и В и при другой последовательности

40 приема станхщй не позже, чем на четвертом такте, на выходе блока 8 устанавливается число, соответствующее амплитуде ближней станции на входе аттенюатора 3.

45 Сигнал с выхода блока 8, содержащий информацию об амплитуде сигнала ближней станции поступает на вход блока 9 определения перегрузки. Впредлагаемом устройстве

50 под перегрузкой понимается превышение Dpo сигнала на входе аттенюатора 3 над пороговым уровнем U|) на величину, большую чем Dp, пред, этом случае на выходе

55 блока 6 устанавливается максимальное управляющее число (111111) и, коэффициент передачи аттенюатора 3 становится минимальным.

15

В предлагаемом устройстве факт наступления перегрузки определяется косвенным образом в блоке 9 путем

.сравнения управляющего числа для сигнала ближней станции, вьщелейного блоком 8, с опорным числом, которое формируется в блоке 9 с помощью источника 20 опорного сигнала и соответствует управляющему сигналу 111110, устанавливаемому на выходе блока 6 при превышении амплитуды сигнала на входе аттенюатора 3 над пороговым уровнем на ве, личину, равную Орд--Dp, пред . Следовательно, если амплитуда сигнала ближней станции на входе аттенюатора 3 превьшает пороговый уровень Uy, на величину, большую чем Dp,npej то управляющее число 111111 на выходе блока 6, вьщеленное блоком 8, больше опорного числа 111110, формируемого источником 20. Второе опорное число, формируемое в блоке 9 источником 21, на одну единицу меньше, чем первое, т.е. равно 111100.

Сравнение информационных сигналов с опорными в блоке 9 осуществляется с помощью компараторов 18 и 19. Компараторы 18 и 19 идентичны рассмотренному компаратору 13 блока 8. Сигнал с выхода блока 8 (шестиразрядное двоичное число) поступает на первьй (А) вход компаратора 18 и на второй (Б) вход компаратора 19. На второй вход компаратора 18 с выхода источника 20 опорного сигнала поступает двоичное число 111110, соответствующее управляющему сигналу на выходе блока 6, который устанавливается при превышении входного сигнала аттенюатора 3 над пороговым уровнем U

77,5 дБ и соответстна D

р,преА

вует включению в аттенюаторе 3 пяти Наибольших ступеней аттенюации. На первьй вход компаратора 19 с выхода источника 21 опорного сигнала поступает двоичное число 11110 соответствующее управляющему числу на выходе блока 6. Это число устанавливается при превышении сигнала аттенюатора 3 над пороговьм уровнем на 75 дБ и соответствует включению четьфех наибольших ступеней аттенюадаи в аттенюаторе 3. Компараторы 18 и 19 формируют на своих выходах сигнал Jlor.l в том

144062

16

случае, если число, поступающее на его первый (А) вход, больше числа, поступающего на второй (б) вход. В остальных случаях выходные 5 сигналы компараторов 18 и 19 равны логическому О. Отсюда следует, что входной сигнал компаратора 18 равен логической 1 при ,5 дБ и логическому О - при Dp, $77,5 дБ.

0 Соответственно выходной сигнал компаратора 19 равен логической 1 при-D РО 75 дБ и логическому О при Dpo 75 дБ.

Выходные сигналы компараторов

5 18 и 19 формируют выходной сигнал блока 9 в виде двухразрядного двоичного кода, причем старпий разряд формируется компаратором 19, а младший - компаратором 18, Таким

0 образом на выходе блока 9 при

Dpo 77,5 дБ присутствует код 01, при 75 дБ Dpo 77,5 дБ - код 00, а при DPQ 75 дБ - код 10. Отсюда следует, что рассматриваемому случаю Про t Dp. пред 77,5 дБ соответствуют два выходных кода - 00 и 10.

Эти коды поступают на информационньй вход блока 10. При этом

сигнал с выхода компаратора 18 блока 9 поступает на первьй вход элемента И 22 и на первый управляющий вход ключа 26, а сигнал с выхода

компаратора 19 блока 9 поступает на первьй вход элемента И 23 и на второй управляющий вход ключа 26. На третий управляющий вход ключа 26 поступает сигнал с выхода злемента ИЛИ 29. Ключ 26 управляется трехразрядным двоичным кодом. Состояние младшего разряда этого кода определяется сигналом, поступающим на первьй управляющий вход ключа 26

с первого входа элемента И 22,т.е. с выхода компаратора 18 блока 9. Состояние среднего разряда определяется сигналом, поступающим на второй управляющий вход ключа 26 с

первого входа элемента И 23, т.е. с выхода компаратора 19 блока 9. Состояние старшего разряда определяется сигналом, поступающим на третий управляющий вход ключа 26 с выг

хода элемента ИЛИ 29. Ключ 26 разомкнут при поступпении кодов. 000, 010, 100 и замкнут при поступле

кодов 101, 110.

НИИ 17 Накопительным элементом блока ib является реверсивньЛ М -разрядный () счетчик 25, -который осуществляет накопление счетных импульсов, поступающих на его счетный вход (С-вход) через ключ 26 ,и элеменг 27 задержки с выхода делителя 28 частоты. Первоначально на всех выхо дах счетчика 25 присутствуют сигналы, равные логическому О. Нулевой выходной сигнал счетчика 25 сформирован с помощью управляющего сигнала установки нуля (двоичного числа 01), поступающего в момент включе ния устройства на управляющий вход блока 10 с второго выхода вычислителя 5. При этом сигнал Лог.О поступает на вход делителя 28 частоты, а Лог.1 - на -вход (вход установки нуля) счетчика 25. По этому сигналу на всех М 4 выходах счетчика 25 устанавливаются логиг ческие О, т.е. двоичное чйсло 0000. При поступлений сигнала Лог.6 с выходов счетчика 25 на входы элемента ЮТН 29 на выходе эле мента ИЛИ 29 устанавливается сигнал Лог.О, которьй с выхода элемента ИЛИ 29 поступает на третий зшравляющий вход ключа 26, а на вто рой и первьй входы поступают управляюгше сигналы соответственно с пер вых входов элементов И 23 и 22. В . соответствии с изложенным рассматри ваемому случаю DPQ Dp, пре, соответ ствуют два управляющих кода для клю ча 26 - коды 000 и 010. Под дей ствием кодов 000 и 010 ключ 26 размыкается, размыкая тем самым цепь, по которой на счетный вход (С-вход) счетчика 25 поступают счет ные импульсы. Следовательно, в рассмотренных случаях изменения нулевого состояния счетчика 2Ъ не происхо дит, и на управляющий вход аттенюатора 7 с выхода блока 10 поступает нулевой управляющий сигнал - код 0000, устанавливающий коэффициент передачи аттенюатора 7 равным едини це. Следовательно, в случае, когда Dpo Dp, .e. отсутствует перегрузка, К- 1 и вся регулировка усиления в устройстве осуществляется с пбмощью аттенюатора 3. Рассмотрим случай, когда, например в результате изменения местоположения устройства, превышение Dpc сигнала ближней станции на входе 62 аттенюатора 3 над пороговым уровнем и, становится больше, чем Вр.пред 77,5 дБ, т.е. возникает перегрузка. Такой сигнал не может быть уменьшен до уровня и„ при включении пяти максимальных ступеней аттенюации, дающих ослабление (40+20+ +10+5+2j5) дБ 77,5 дБ, и поэтому в аттенюаторе 3 включаются все шесть ступеней аттенюации, дающие общее ослабление (77,5+1,25) дБ. Такой аттенюации соответствует управляющее двоичное число 111111, появляющееся на выходе блока 6 во время приема сигналов ближней станции. Это число, как было показано, вьщеляется на выходе блока 8, откуда поступает на первый вход компаратора 18 и на второй вход компаратора 19 блока 9. В компараторе 18 число 111111 сравнивается с числсм 11111О, поступающим на второй его вход с источника 20, и поскольку двоичное число 111111 больше 111110, на выходе компара-тора 18 появляется сигнал Лог.1. в компараторе 19 число 111100, поступающее на его первьй вход с источника 21, сравнивается с числом 111111, поступающим на второй вход с входа блока 9, и поскольку двойное число 111100 меньше 111111, на выходе компаратора 19 появляется сигнал Лог.О. Сигналы Лог.1 с выхода компаратора 18 и Лог.О с выхода компаратора 19 образзют код 01 выходного сигнала блока 9. Сигналы Лог.Г и Лог.О с выхода блока 9 поступают соответственно на первый и второй управляющие входы ключа 26 блока 10, на третий управляющий вход которого, как бьто показано, вначале поступает сигнал Лог. О, т.е. поступает код 001. Под действием управляющего кода 001 ключ 26 замыкается, замыкая тем самым цепь для прохождения счетных импульсов на счетный вход счетчика 25. Сигнал Лог.1 с входа блока 10 также поступает на первьй вход элемента А 22, а сигнал Лог.О с входа блока 10 - на первьй вход элемента И 23, При поступлении с вько да делителя 28 частоты на вторые 19 входы элементов И 22 я 23 счетного импульса (Лог.Г) на выходе эле, мента И 22 появляется логическая 1 в результате имеющего место совпадения сигналов Лог.1 на обоих входах элемента И 22. Сигнал Лог.1 с выхода элемента И 22 поступает на 5. -вход (единичный вход) RS -триггера 24, а на его R -вход с выхода элемента И 23 поступает сигнал Лог.О. При поступлении логической 1 на 5-вход RS-триггера 24 на его неинве тирующем выходе, соединенном с входом управления реверсом счетчика 25, появляется логическая 1. Под действием логической 1, поступающей с выхода RS -триггера 24, счетчик 25 устанавливается в режим суммирования счетных импульсов Лог.1, поступающих с выхода делителя 28 частоты через ключ 26 с задержкой, формируемой элементом 27. Элемент 27 задержки предназначен для задержки счетного импульса на время, необходимое для прохождения импульса через элементы И 22 и 23 на вход управления реверсом счетчика 25. Счетные импульсы Лог.Г с выхода делителя 28 частоты поступаю с частотой, как минимум, в 4etbipe раза меньше, чем тактирующие импуль сы, поступающие на управляющий вход блока 10 с второго выхода вычислите 5 в виде двоичного числа 10. Объясняется это тем, что установка коэффициента передачи в аттенюаторе 7 осуществляется после ввделения амплитуды ближней станции в блоке 8, на что требуется четыре тактовых импульса, поступающих с дополнитель ного выхода вычислителя 5 в виде двоичного числа 10. Первый счетный импульс (Лог.1) поступающий на счетный вход счетчика 25,.записывает логическую 1 в младшем разряде, т.е. изменяет вы ходной код счетчика 25 с 0000 на 0001. При этом, в результате появ ления на одном из выходов счетчика 25 логической 1, появляется логическая 1 и на выходе элемента ИЛИ 29, с выхода которого сигнал Лог.Г поступает на третий управляющий вхо ключа 26, изменяя тем самым его управляющий код с 001 на 101, под действием которого ключ 26 оста 62 ется замкнутым. В результате измерения выходного сигнала счетчика 25 с 0000 на 0001 изменяется управляющее число на управляющем входе аттенюатора 7. Под действием управляющего числа 0001, поступающего с выхода блока 10 на управляющий вход аттенюатора 7 при возникновении перегрузки, включается его первая ступень аттенюации, обеспечивающая уменьшение коэффициента передачи на 2,5 дБ. Если такой аттенюадии оказывается недостаточно и по-прежнему сохраняется перегрузка, т.е. .пред 77,5 дБ, то после прихода следующего счетного импульса на С-вход счетчика 25 (с выхода делителя 28 частоты) его состояние изменяется на единицу, в результате чего управляющее число на управляющем входе аттенюатора 7 изменяется с 0001 на 0010. Под действием этого числа включается вторая ступень аттенюации аттенюатора 7, т.е. 5 дБ, уменьшая его коэффициент передачи. Уменьшение коэффициента передачи в аттенюаторе 7 происходит до тех пор, пока не устанавливается соотношение 75 ,5 дБ, соответствующее прекращению перегрузки. В этом случае на выходах компараторов 18 и 19 блока 9 определения перегрузки появляются сигналы,равные логическому О, которые с выходов компараторов 18 и 19 образуют код 00 выходного сигнала блока 9. Сигналы Лог.О с выхода блока 9. поступают на первый и второй управляющие входы ключа 26 блока 10, изменяя его управляющий код с 101 на 100. Под действием этого кода ключ 26 размыкается, не пропуская более счетные импульсы на С -вход счетчика 25 и прекращая тем самым накопление выходного сигнала блока 10 и изменение состояния аттенюатора 7. Рассмотрим случай, когда при включенном аттенюаторе 7 в результате, например, изменения местоположения устройства, превьшение Dpo сигнала ближней станции на входе аттенюатора 3 над пороговые уровнем и не станет ниже 75 дБ (Dpo 75 дБ). При этом на выходе компаратора 18 блока 9 появляется сигнал Лог.О, а на выходе компаратора)19 блока 9 - сигнал Лог,1, которые образуют код 10 выходного сигнала блока 9. и с его выхода поступают соответственно на первьй и второй управляющие вхо ключа 26 блока 10, на третий управляющий вход которого поступает этом случае логическая 1, т.е. поступает код 110. Под действием управляющего кода 110 ключ 26 замыкается, замыкая цепь для прохождения счетных импульсов на счет ный вход счетчика 25. Сигнал Лог с выхода блока 10 также поступает на первый вход элемента И 23, а си нал Лог.О с входа блока 10 - на первый вход элемента И 22. При поступлении с выхода делителя 28 частоты на вторые входы элементов Е 22 и 23 появляется логическая 1 в резул-ьтате имеющего места совпадения сигналов Лог.1 на обоих входах элемента И 23. Сигнал Лог.1 с выхода элемента И 23 поступает на i -вход (нуле вой вход) RS-триггера 24, в резул тате чего на его неинвертирующем выходе, соединенном с входом управ Ленин реверсом счетчика 25, появляется Логический О. Под действием логического О, поступающего с выхода RS -триггера 24, счетчик 25 устанавливается в режим вычитания. При этом при постзтлении на его С -вход счетного импульса (Лог.1) из числа, записанного на выходе счетчика, вы читается единица. В результате при поступлении Счетного импульса упра ляющий код аттенюатора 7 уменьшается на одну единицу в младшем раз ряде. Соответственно с изменением управляющего кода изменяется и коэ фициент передачи аттенюатора 7, увеличиваясь с каждым счетным импульсом на 2,5 дБ. Увеличение коэффициента передачи в аттенюатор 7 происходит до тех пор, пока превьшение D«o сигнала ближней станци на входе аттенюатора 3 над порогов уровнем Uy, не станет 75 дВ Dpp б 77,5 дБ. В этом случае на выходах компараторов 18 и 19 блока 9 о ределения перегрузки появляются сигналы, равные Лог.О, с выходов компараторов 18 и 19 образуют код 00 выходного сигнала блока 9 и поступают на первый и второй управляющие входы ключа 26 блока 10, изменяя его управляющий код с 110 на 100. Под действием этого кода ключ 26 размыкается, не пропуская более счетные импульсы на С -вход счетчика 25, прекращая тем самым отрицательное накопление выходного сигнала блока 10 и изменение состояния аттенюатора 7. Рассмотрим также возможньй случай, когда в результате вьиитания на выходе счетчика 25 устанавливается нулевое число (код 0000), что соответствует максимальному коэффициенту передачи аттенюатора 7 (К О, но при этом сохраняется соотношение Dpg 75 дБ. . В этом случае на выходах компараторов 18 и 19 блока 9 сохраняются соответственно логический О и логическая 1. Сигналы с выходов компараторов образуют код 10 выходного сигнала блока 9. Сигналы Лог.О и Лог.1 с выхода блока 9 поступают соответственно на первьй и второй управляющие входы ключа 26 блока 10, на третий управляющий вход которого поступает Лог.О с выхода элемента ИЛИ 29. Под действием управляющего кода 010 ключ 26 размыкается, не пропуская более счетные импульсы на С -вход счетчика 25, предотвращая тем самым дальнейшее изменение состояния счетчика (т.е. переброс кода с 0000 на 1111)..В этом случае регулирование амплитуды сигналов осуществляется только аттенюатором 3.. В результате совместного дейг ствия аттенюаторов 3 и 7 на вход вычислителя 5 с выхода АЦП 4 поступают сигналы станций А, Б и & отфильтрованные от внеполосных и внутриполосных помех, выравненные по амплитуде и равйые пороговому уровню и и преобразованные в цифровую фор.му. Вычислитель 5 осуществляет измерение временных интервалов между приходом сигналов ведомых станций б и 8 и сигналами ведущей стан1щи А и по измеренным временным интервалам вычисление навигационных параметров. При этом точность измерения ременных интервалов в предлагав23MOM устройстве вьше, чем в известном. Объясняется это тем, что аттенюатор 7 осуществляет только общее для станций А, Б и В изменение коэффициента усиления устро ства, а существующий между сигнала ми станций разбаланс устраняется только раздельной (по станциям) регулировкой коэффициента передачи аттенюатора 3. Предлагаемая регулировка аттенюатора 7 с помощью блоков 8-10 позволяет устранить перегрузку всей входной цепи, а не только режекторного фильтра,ка в известном устройстве, а также 2 исключает появление амшштудноманипулированных помех, возникающих в результате изменения коэффициента передачи аттенюатора 7 (что имеет место в известном устройстве) . Это повышает, по сравнению с известным устройством, динамический диапазон устройства, а также величину подавления -помехи, что приводит к увеличению точности измерения временных интервалов при приеме отличающихся по амплитуде радиоимпульсных-сигналов в условиях воздействия постоянной по амплитуде помехи.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Патент США № 3947849, кл | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Dean W.N.,Roth D.P | |||

| Кипятильник для воды | 1921 |

|

SU5A1 |

| - Navigation (USA), vol | |||

| Прибор для равномерного смешения зерна и одновременного отбирания нескольких одинаковых по объему проб | 1921 |

|

SU23A1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ЧЕРТЕЖЕЙ ДЛЯ ОДНООБРАЗНОЙ РАСКРОЙКИ ПРЕДМЕТОВ ОДЕЖДЫ | 1919 |

|

SU287A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1985-03-07—Публикация

1984-01-04—Подача