ъ

Фиг.1

и

синхр

315

Изобретение относится к измерительной технике и может быть использовано в различных устройствах (в том числе селективных, с преобразованием частоты) полуавтоматического и автоматического измерения и допускового контроля уровней, затуханий, амплитудно-частотных характеристик в логарифмическом масштабе в широком динамическом диапазоне уровней с малой погрешностью и высокой разрешающей способностью.

Целью изобретения является расширение динамического диапазона, повышение разрешающей способности и расширение области применения.

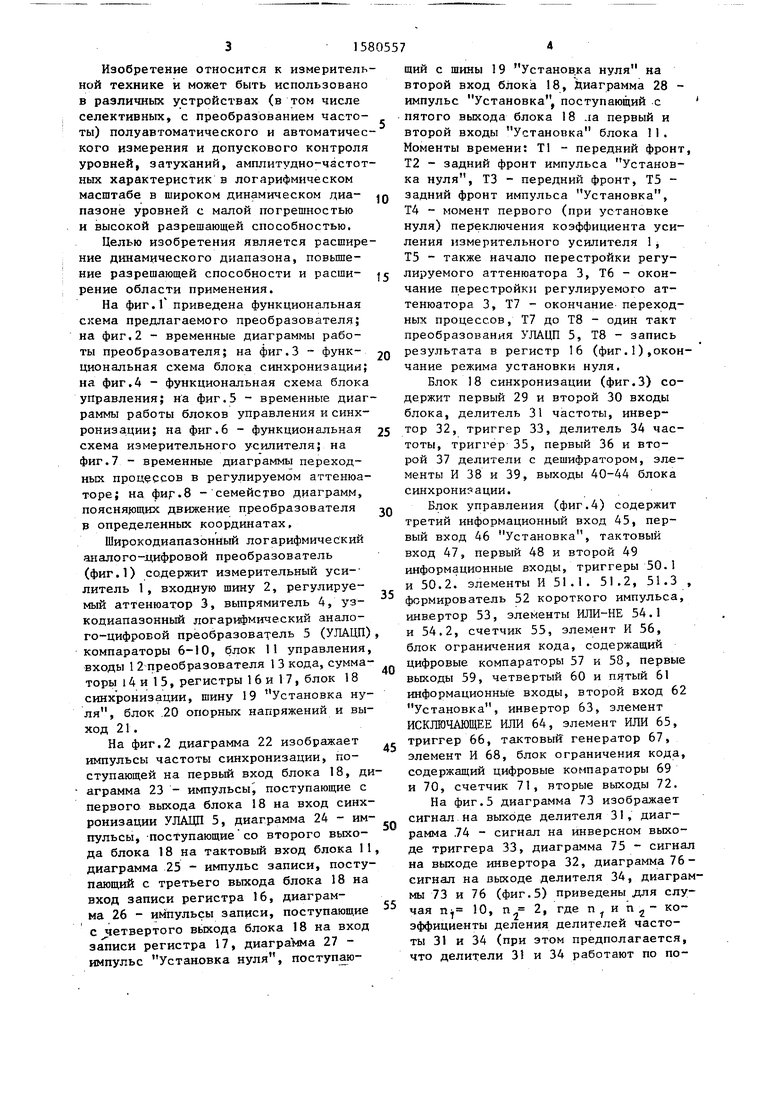

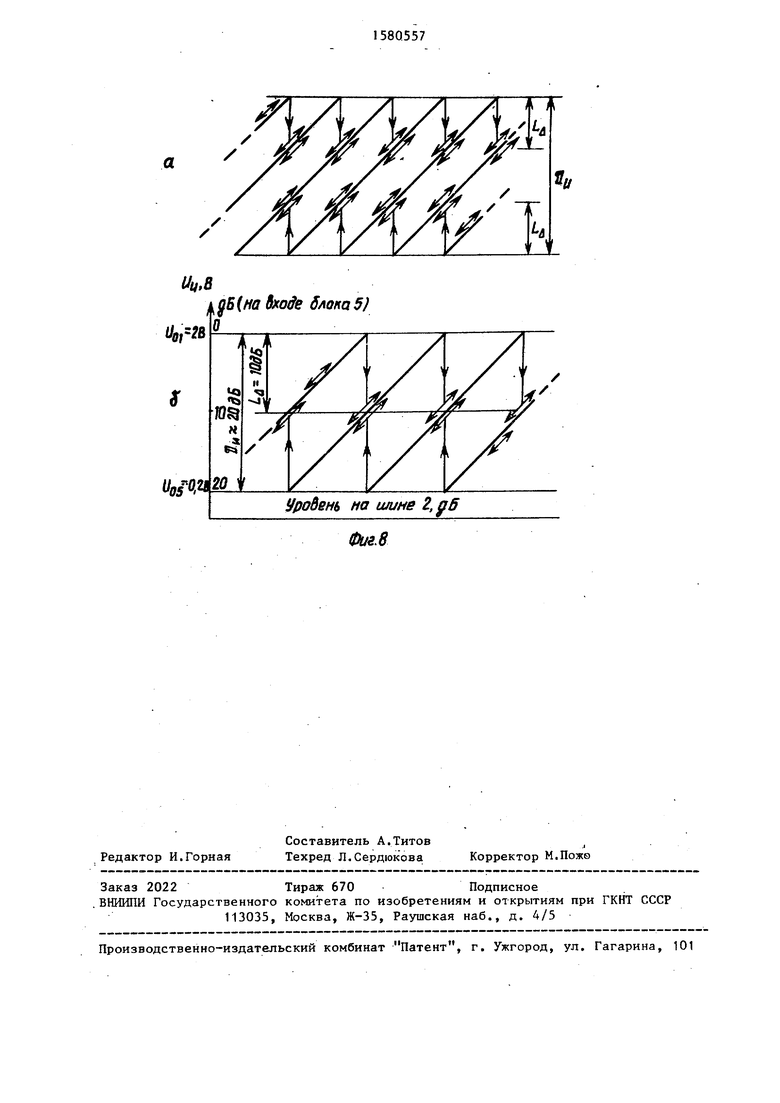

На фиг.1 приведена функциональная схема предлагаемого преобразователя; на фиг.2 - временные диаграммы работы преобразователя; на фиг.З - функциональная схема блока синхронизации; на фиг.4 - функциональная схема блока управления; на фиг.З - временные диаграммы работы блоков управления и синхронизации; на фиг.6 - функциональная схема измерительного усилителя; на фиг.7 - временные диаграммы переходных процессов в регулируемом аттенюаторе; на фиг-8 - семейство диаграмм, поясняющих движение преобразователя В определенных координатах.

Широкодиапазонный логарифмический аналого-цифровой преобразователь (фиг.1) содержит измерительный уси- литель 1, входную шину 2, регулируемый аттенюатор 3, выпрямитель 4, узкодиапазонный логарифмический аналого-цифровой преобразователь 5 (УЛАЦП) компараторы 6-10, блок 11 управления, входы 1 2 преобразователя 1 3 кода,сумматоры 14 и 15, регистры 1 6 и 17, блок 18 синхронизации, шину 19 Установка ну

ля, блок 20 опорных напряжений и выход 21 .

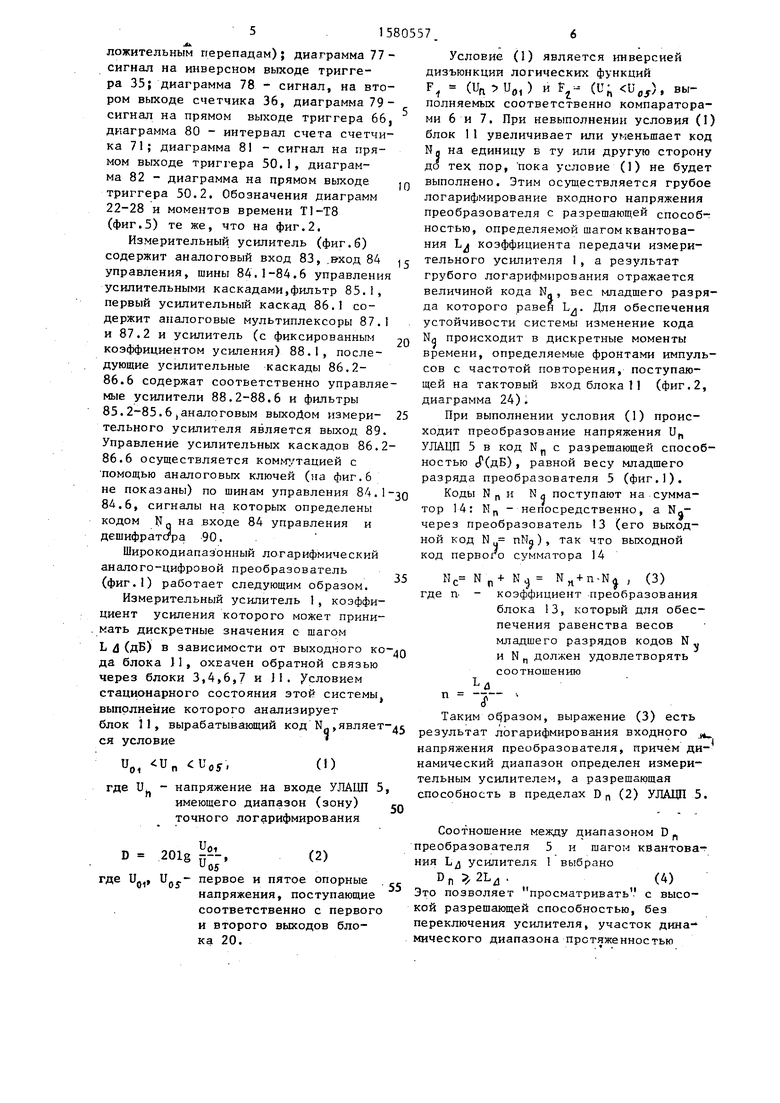

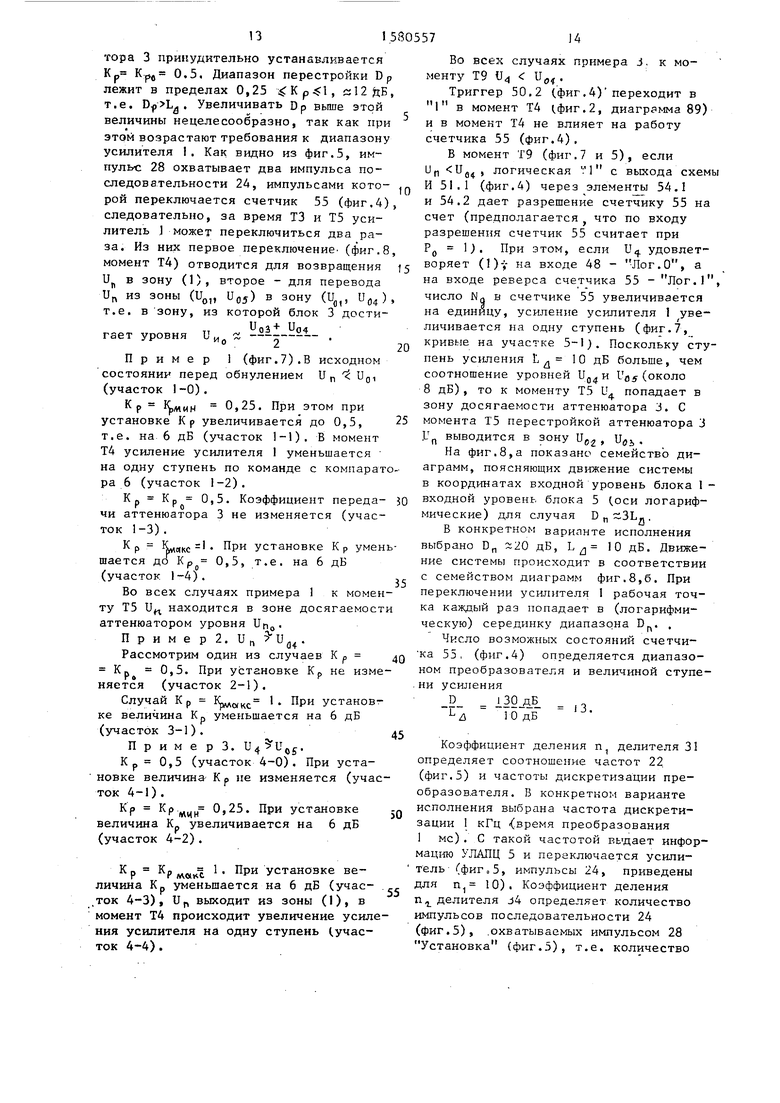

На фиг.2 диаграмма 22 изображает импульсы частоты синхронизации, поступающей на первый вход блока 18, диаграмма 23 - импульсы, поступающие с первого выхода блока 18 на вход синх45

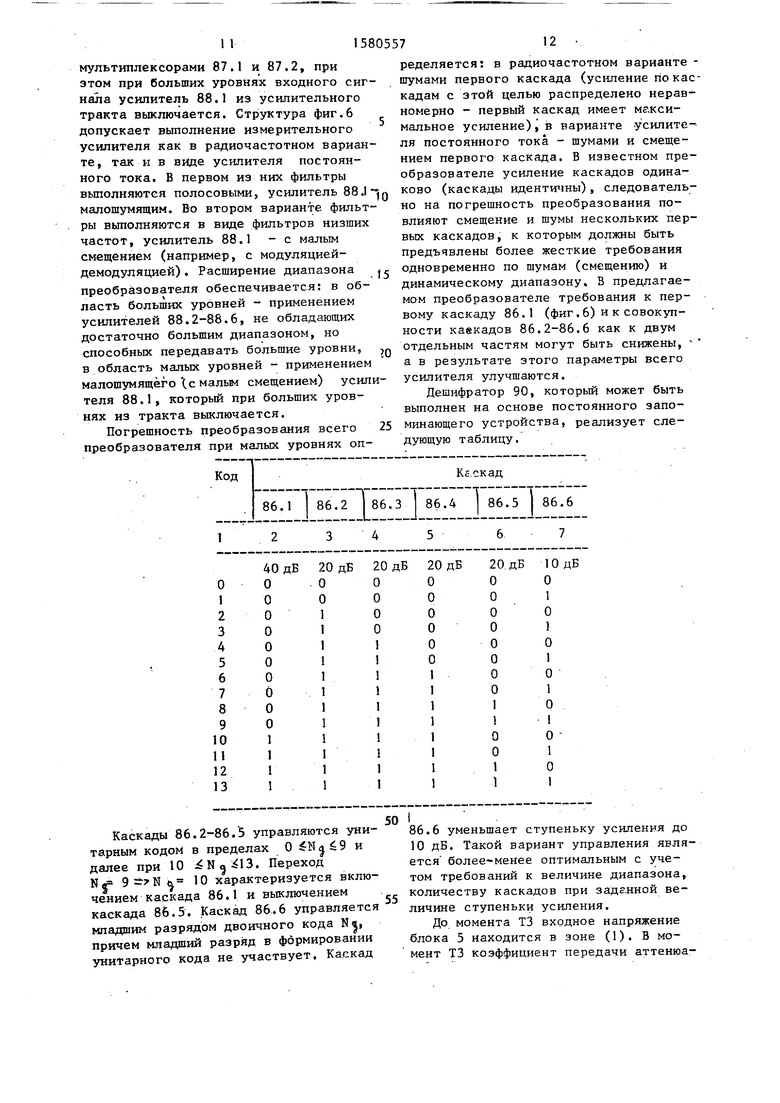

Блок управления (фиг.4) содержит третий информационный вход 45, первый вход 46 Установка, тактовый вход 47, первый 48 и второй 49 информационные входы, триггеры 50.1 и 50.2. элементы И 51.1. 51.2, 51.3 формирователь 52 короткого импульса инвертор 53, элементы ИЛИ-НЕ 54.1 и 54.2, счетчик 55, элемент И 56, блок ограничения кода, содержащий цифровые компараторы 57 и 58, первые выходы 59, четвертый 60 и пятый 61 информационные входы, второй вход 6 Установка, инвертор 63, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 64, элемент ИЛИ 65, триггер 66, тактовый генератор 67, элемент И 68, блок ограничения кода содержащий цифровые компараторы 69 и 70, счетчик 71, вторые выходы 72.

На фиг.5 диаграмма 73 изображает

ронизации УЛАЦП 5, диаграмма 24 - им- сигнал на выходе делителя 31, диагпульсы, поступающие со второго выхода блока 18 на тактовый вход блока 1 1, диаграмма 25 - импульс записи, поступающий с третьего выхода блока 18 на вход записи регистра 16, диаграмма 26 - импульсы записи, поступающие с четвертого выхода блока 18 на вход записи регистра 17, диаграмма 27 - импульс Установка нуля, поступаю55

рамма .74 - сигнал на инверсном выходе триггера 33, диаграмма 75 - сигна на выходе инвертора 32, диаграмма 76 сигнал на выходе делителя 34, диагра мы 73 и 76 (фиг.5) приведены для слу чая п 10, п 2, где nf и п2 ко эффициенты деления делителей частоты 31 и 34 (при этом предполагается что делители 31 и 34 работают по по

0

5

0

5

0

35

40

45

щий с шины 19 Установка нуля на второй вход блока 18, диаграмма 28 - импульс Установка, поступающий с пятого выхода блока 18 ла первый и второй входы Установка блока 11. Моменты времени: Т1 - передний фронт, Т2 - задний фронт импульса Установка нуля, ТЗ - передний фронт, Т5 - задний фронт импульса Установка, Т4 - момент первого (при установке нуля) переключения коэффициента усиления измерительного усилителя 1, Т5 - также начало перестройки регулируемого аттенюатора 3, Т6 - окончание перестройки регулируемого аттенюатора 3, Т7 - окончание переходных процессов, Т7 до Т8 - один такт преобразования УЛАЦП 5, Т8 - запись результата в регистр 16 (фиг.1).окончание режима установки нуля.

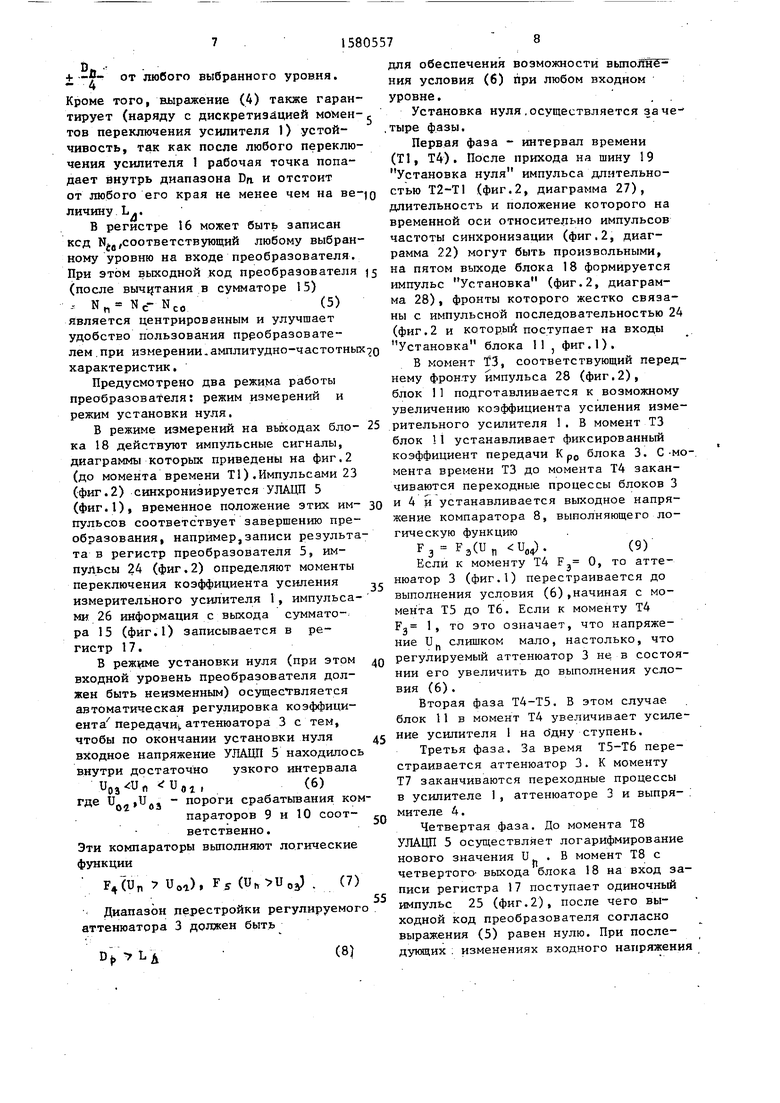

Блок 18 синхронизации (фиг.З) содержит первый 29 и второй 30 входы блока, делитель 31 частоты, инвертор 32, триггер 33, делитель 34 частоты, триггер 35, первый 36 и второй 37 делители с дешифратором, элементы И 38 и 39, выходы 40-44 блока синхрони ации.

Блок управления (фиг.4) содержит третий информационный вход 45, первый вход 46 Установка, тактовый вход 47, первый 48 и второй 49 информационные входы, триггеры 50.1 и 50.2. элементы И 51.1. 51.2, 51.3 , формирователь 52 короткого импульса, инвертор 53, элементы ИЛИ-НЕ 54.1 и 54.2, счетчик 55, элемент И 56, блок ограничения кода, содержащий цифровые компараторы 57 и 58, первые выходы 59, четвертый 60 и пятый 61 информационные входы, второй вход 62 Установка, инвертор 63, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 64, элемент ИЛИ 65, триггер 66, тактовый генератор 67, элемент И 68, блок ограничения кода, содержащий цифровые компараторы 69 и 70, счетчик 71, вторые выходы 72.

На фиг.5 диаграмма 73 изображает

5

рамма .74 - сигнал на инверсном выходе триггера 33, диаграмма 75 - сигнал на выходе инвертора 32, диаграмма 76- сигнал на выходе делителя 34, диаграммы 73 и 76 (фиг.5) приведены для случая п 10, п 2, где nf и п2 коэффициенты деления делителей частоты 31 и 34 (при этом предполагается, что делители 31 и 34 работают по положительным перепадам); диаграмма 77- сигнал на инверсном выходе триггера 35; диаграмма 78 - сигнал, на втором выходе счетчика 36, диаграмма 79- сигнал на прямом выходе триггера 66, диаграмма 80 - интервал счета счетчика 71; диаграмма 81 - сигнал на прямом выходе триггера 50.1, диаграмма 82 - диаграмма на прямом выходе триггера 50.2. Обозначения диаграмм 22-28 и моментов времени Т1-Т8 (фиг.5) те же, что на фиг.2.

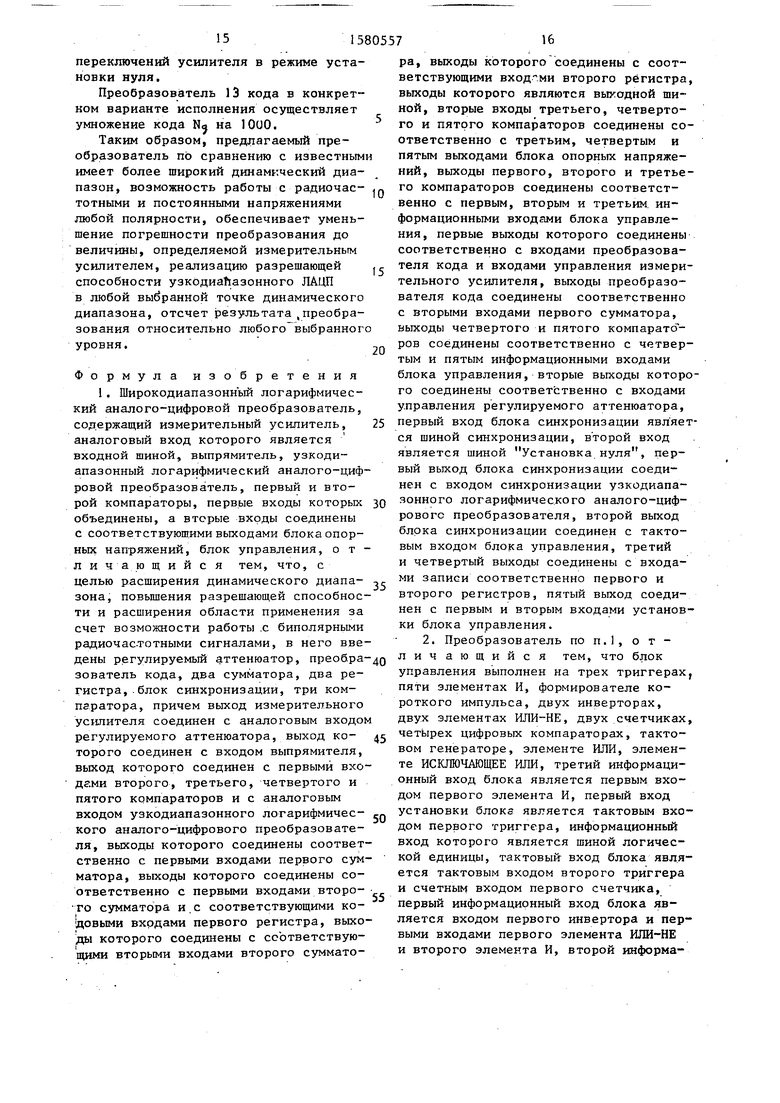

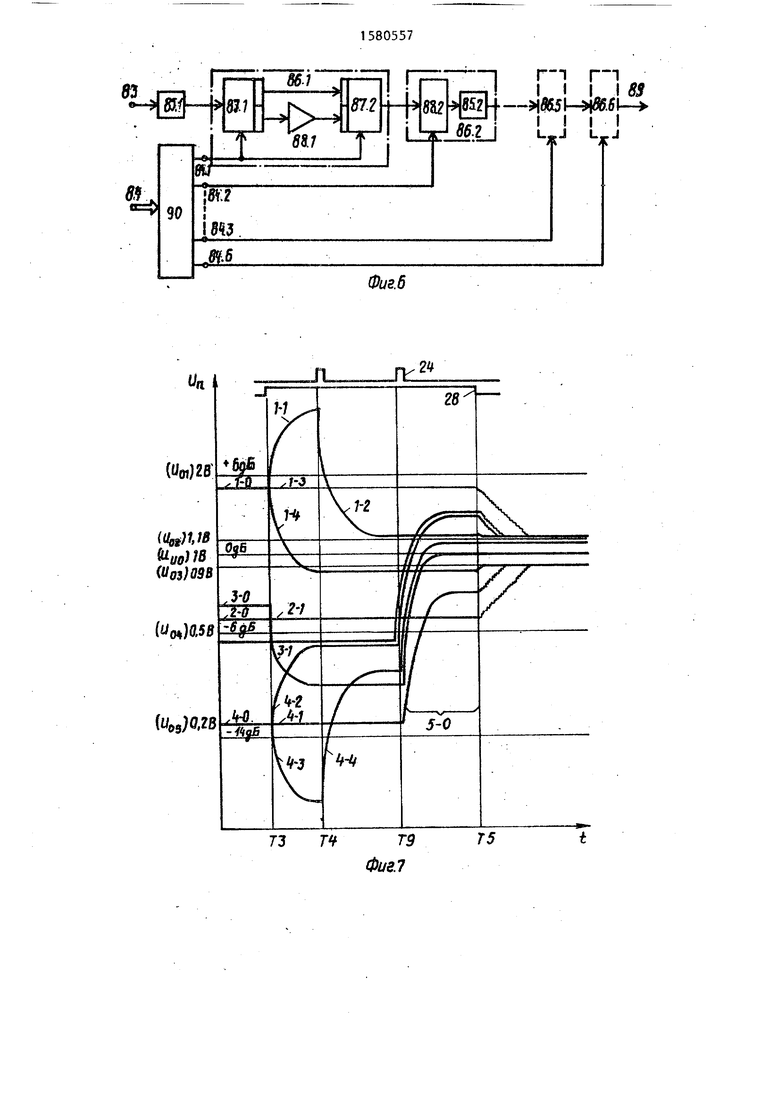

Измерительный усилитель (фиг.6) содержит аналоговый вход 83, .&ход 84 управления, шины 84.1-84.6 управления усилительными каскадами,фильтр 85.1, первый усилительный каскад 86.1 содержит аналоговые мультиплексоры 87.1 и 87.2 и усилитель (с фиксированным коэффициентом усиления) 88.1, последующие усилительные каскады 86.2- 86.6 содержат соответственно управляемые усилители 88.2-88.6 и фильтры 85.2-85.6,аналоговым выходом измерительного усилителя является выход 89. Управление усилительных каскадов 86.2- 86.6 осуществляется коммутацией с помощью аналоговых ключей (на фиг.6 не показаны) по шинам управления 84.1- 84.6, сигналы на которых определены кодом Ng на входе 84 управления и дешифратора 90.

Широкодиапазонный логарифмический аналого-цифровой преобразователь (фиг.) работает следующим образом.

Измерительный усилитель 1, коэффициент усиления которого может принимать дискретные значения с шагом L и (дБ) в зависимости от выходного кода блока 11, охвачен обратной связью через блоки 3,,7 и 1. Условием стационарного состояния этой системы4 выполнение которого анализирует блок 11, вырабатывающий код N,является условие

и01 ип ио5,

(D

где U - напряжение на входе УЛАЦП 5, имеющего диапазон (зону) точного логарифмирования

2018

U

05

(2)

U01, Ufl5.- первое и пятое опорные напряжения, поступающие соответственно с первого и второго выходов блока 20.

0

5

0

5

0

5

0

5

0

5

Условие (I) является инверсией дизъюнкции логических функций

F, - и (и;, выполняемых соответственно компараторами 6 и 7, При невыполнении условия (1) блок 11 увеличивает или уменьшает код N я на единицу в ту или другую сторону до тех пор, пока условие (1) не будет выполнено. Этим осуществляется грубое логарифмирование входного напряжения преобразователя с разрешающей способностью, определяемой шагом квантования L коэффициента передачи измерительного усилителя I, а результат грубого логарифмирования отражается величиной кода N., вес младшего разряда которого равен L. Для обеспечения устойчивости системы изменение кода Ng происходит в дискретные моменты времени, определяемые фронтами импульсов с частотой повторения, поступающей на тактовый вход блока 11 (фиг.2, диаграмма 24).

При выполнении условия (1) происходит преобразование напряжения Un УЛАЦП 5 в код Nn с разрешающей способностью tf (дБ), равной весу младшего разряда преобразователя 5 (фиг.1).

Коды N п и N л поступают на сумматор 14: Мп - непосредственно, a Ng- через преобразователь 13 (его выходной код N пМо), так что выходной код первого сумматора 14

Nc N n+ N Nn+n-N , (3) где п - коэффициент преобразования блока 13, который для обеспечения равенства весов младшего разрядов кодов N

п -5L

i

и Nn должен удовлетворять соотношению

Таким образом, выражение (3) есть результат логарифмирования входного напряжения преобразователя, причем динамический диапазон определен измерительным усилителем, а разрешающая способность в пределах Dn (2) УЛАЦП 5.

Соотношение между диапазоном D n преобразователя 5 и шагом квантования L усилителя 1 выбрано

.(4)

Это позволяет просматривать1 с высокой разрешающей способностью, без переключения усилителя, участок дина- мического диапазона протяженностью

U -- ,- от любого выбранного уровня.

Кроме того, выражение (4) также гарантирует (наряду с дискретизацией момен-, тов переключения усилителя 1) устойчивость, так как после любого переключения усилителя 1 рабочая точка попадает внутрь диапазона Dn. и отстоит

для обеспечения возможности вьшоЛн€ ния условия (6) при любом входном уровне.

Установка нуля.осуществляется заче- ,тыре фазы.

Первая фаза - интервал времени (Т1, ТА). После прихода на шину 19 Установка нуля импульса длительноот любого его края не менее чем на ве-jg стью Т2-Т1 (фиг.2, диаграмма 27),

личину L

и

В регистре 16 может быть записан кед N4fl,соответствующий любому выбранному уровню на входе преобразователя. При этом выходной код преобразователя $ на пятом выходе блока 18 формируется (после вычитания в сумматоре 15) импульс Установка (фиг.2, диаграмдлительность и положение которого на временной оси относительно импульсов частоты синхронизации (фиг.2, диаграмма 22) могут быть произвольными,

N

NC- «со

(5) ма 28), фронты которого жестко связаны с импульсной последовательностью 24 (фиг.2 и который поступает на входы

является центрированным и улучшает удобство пользования преобразователем при измерении„амплитудно-частотныхзо Установка блока 11 } фиг.1). характеристик.В момент ТЗ, соответствующий передПредусмотрено два режима работы нему фронту импульса 28 (фиг.2), преобразователя: режим измерений и блок 11 подготавливается к возможному режим установки нуля.увеличению коэффициента усиления измеВ режиме измерений на выходах бло- 25 рительного усилителя 1. В момент ТЗ ка 18 действуют импульсные сигналы, блок 11 устанавливает фиксированный диаграммы которых приведены на фиг.2 (до момента времени Т1).Импульсами 23 (фиг.2) синхронизируется УЛАЦП 5 (фиг.1), временное положение этих им- 30 и 4 и устанавливается выходное напря- пульсов соответствует завершению пре- жение компаратора 8, выполняющего ло- образования, например,записи результа- гическую функцию та в регистр преобразователя 5, импульсы 24 (фиг.2) определяют моменты переключения коэффициента усиления

коэффициент передачи К р0 блока 3. С-момента времени ТЗ до момента Т4 заканчиваются переходные процессы блоков 3

35

F3 F3(Un Ufl4). (9) Если к моменту Т4 F 0, то атте нюатор 3 (фиг.1) перестраивается до

выполнения условия (6),начиная с момента Т5 до Тб. Если к моменту Т4 РЗ 1, то это означает, что напряжение Un слишком мало, настолько, что регулируемый аттенюатор 3 не в состоянии его увеличить до выполнения условия (6) .

измерительного усилителя 1, импульсами 26 информация с выхода сумматора 15 (фиг.1) записывается в регистр 17.

В режиме установки нуля (при этом входной уровень преобразователя должен быть неизменным) осуществляется автоматическая регулировка коэффици- ента/ передачи аттенюатора 3 с тем, чтобы по окончании установки нуля входное напряжение УЛАЦП 5 находилось внутри достаточно узкого интервала

uoi. 6 где U U03 - пороги срабатывания компараторов 9 и 10 соответственно .

Эти компараторы выполняют логические функции

F4(Un 7 Uoa), Fs () . (7)

Диапазон перестройки регулируемого аттенюатора 3 должен быть

D

(8}

для обеспечения возможности вьшоЛн€ ния условия (6) при любом входном уровне.

Установка нуля.осуществляется заче- ,тыре фазы.

Первая фаза - интервал времени (Т1, ТА). После прихода на шину 19 Установка нуля импульса длительнона пятом выходе блока 18 формируется импульс Установка (фиг.2, диаграмдлительность и положение которого на временной оси относительно импульсов частоты синхронизации (фиг.2, диаграмма 22) могут быть произвольными,

рительного усилителя 1. В момент ТЗ блок 11 устанавливает фиксированный и 4 и устанавливается выходное напря- жение компаратора 8, выполняющего ло- гическую функцию

коэффициент передачи К р0 блока 3. С-момента времени ТЗ до момента Т4 заканчиваются переходные процессы блоков 3

рительного усилителя 1. В момент ТЗ блок 11 устанавливает фиксированный и 4 и устанавливается выходное напря- жение компаратора 8, выполняющего ло- гическую функцию

F3 F3(Un Ufl4). (9) Если к моменту Т4 F 0, то атте нюатор 3 (фиг.1) перестраивается до

выполнения условия (6),начиная с момента Т5 до Тб. Если к моменту Т4 РЗ 1, то это означает, что напряжение Un слишком мало, настолько, что регулируемый аттенюатор 3 не в состоянии его увеличить до выполнения условия (6) .

Вторая фаза Т4-Т5. В этом случае блок 11 в момент Т4 увеличивает усиление усилителя 1 на о дну ступень.

Третья фаза. За время Т5-Т6 перестраивается аттенюатор 3. К моменту Т7 заканчиваются переходные процессы в усилителе 1, аттенюаторе 3 и выпрямителе 4.

Четвертая фаза. До момента Т8 УЛАЦП 5 осуществляет логарифмирование нового значения IL . В момент Т8 с четвертого выхода блока 18 на вход записи регистра 17 поступает одиночный импульс 25 (фиг.2), после чего выходной код преобразователя согласно выражения (5) равен нулю. При последующих изменениях входного напряжения

преобразователя отсчеты результата происходят .от уровня, зафиксированного при установке нуля.

Во время режима обнуления, длящегося с момента Т) до момента Т8 (фиг.2), импульсы записи на регистр 17 с четвертого выхода блока 18 синхронизации не поступают для предотвращезаписи (ф.чг,2 и 5) информации в регистр 17. -Элемент 38 выделяет из последовательности, формируемой на первом выходе делителя 36, один импульс, поступающий через выход 42 на вход записи регистра 16 (фиг.2 и 5, диаграмма 25) .

Блок 1 (фиг.4) работает следующим

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство широкодиапазонного логарифмического аналого-цифрового преобразования | 1988 |

|

SU1571763A1 |

| Система экстремального регулирования | 1985 |

|

SU1352452A1 |

| АНАЛИЗАТОР СПЕКТРА | 1992 |

|

RU2054682C1 |

| Устройство для кодирования звуковых сигналов с инерционным компандированием | 1985 |

|

SU1356233A1 |

| Цифровой коммутатор тока катушки зажигания | 1990 |

|

SU1733674A1 |

| ЦЕЗИЕВЫЙ СТАНДАРТ ЧАСТОТЫ | 1994 |

|

RU2076411C1 |

| Устройство для измерения нелинейности пилообразного напряжения | 1990 |

|

SU1777101A1 |

| Устройство для оценки характеристик узкополосного случайного процесса | 1983 |

|

SU1117650A1 |

| Преобразователь угла поворота вала в код | 1987 |

|

SU1478331A1 |

| Цифровое устройство для управления машиной непрерывного литья заготовок | 1989 |

|

SU1632621A1 |

Изобретение относится к измерительной технике и может быть использовано в различных устройствах (в том числе селективных с преобразованием частоты) полуавтоматического и автоматического измерения и допускового контроля уровней амплитудно-частотных характеристик в логарифмическом масштабе в широком динамическом диапазоне уровней с малой погрешностью и высокой разрешающей способностью. Изобретение позволяет расширить динамический диапазон, повысить разрешающую способность и расширить области применения. Это достигается тем, что в преобразователь, содержащий измерительный усилитель 1, выпрямитель 4, узкодиапазонный логарифмический аналого-цифровой преобразователь 5, компараторы 6-10, блок 20 опорных напряжений, блок 11 управления, введены регулируемый аттенюатор 3, преобразователь 13 кода, сумматоры 14 и 15, регистры 16 и 17, блок 18 синхронизации. 3 з.п. ф-лы, 8 ил., 1 табл.

преобразова- )0 образом.

их переходным Т8 коэффиа 3 остается щего обн уле- ботает так (

диапазон знапределах кос высокой расширяется

Dn м + -г- до

™ 4

20

(Ю) (Ю

25

Код N блока со что счет сигналам дят по п товом вх де разре ходит пр реверса, нуле. Ог счетчика раторы 5 Направлен лом с в ния опред входа 47 ческая режиме и ми 54.1 и в режиме входа 45 геры 50.

протяженностью

D, + Dt.(12)

Это имеет особо важное значение, например, при измерении АЧХ, в част- ности,фильтров, когда необходимо промерить любой участок АЧХ с максимальной разрешающей способностью и минимальной погрешностью.

Блок 18 синхронизации (фиг.1) работает следующим образом.

Делитель 36 (фиг.З) формирует на своих выходах импульсы с длительностью, определяемой периодом частоты синхронизации fCMKXp( поступающей на вход 29) и периодом повторения, определяемым коэффициентом деления nf делителя 31 (диаграммы приведены для п1 10). Работой делителя управляет триггер 33. Наличие инвертора обусловливает опережение передним фронтом импульса 28 переднего фронта импульса 24 (фиг.2 и 5).

Делитель 37 формирует на выходе 44 импульс 28(фиг.2 и5) Установка, дли- тельность которого определяется коэффициентами деления п делителя 31 и п делителя 34 (диаграммы приведены для п 2), а фронты импульса 28 привязаны к последовательности 24 (Фиг.2 и.5).

Элемент 39 по сигналу с тригге30

35

40

45

50

55

Код NJ снимается на выход 59 блока со счетчика 55.Предполагается, что счетчик управляется следующими сигналами: изменения кода происходят по положительным перепадам на так товом входе и логической 1м на входе разрешения, увеличение кода проис ходит при логической единице на вход реверса, уменьшение - при логическом нуле. Ограничение возможных состояни счетчика осуществляют цифровые компа раторы 57 и 58 и элементы 51.2 и 51. Направление счета формируется сигналом с входа 48. Моменты переключения определены фронтами импульсов с входа 47. Разрешение на счет (логи ческая 1 на входе разрешения) в режиме измерений формируется элемент ми 54.1 и 54.2 с входов 48 и 49, а в режиме установки нуля - также с входа 45 элементом 51.1 через триггеры 50.1 и 50.2.

Код снимается с выхода счетчика 7 Разрешение на счет р виде логической единицы формируется триггером 66 (фиг.5, диаграмма 79). Включение три гера 66 происходит в момент ТЗ (фиг.5) по переднему фронту импульса 28 (фиг.2 и 5), выключение триггера 66 осуществляется через элементы 63-65 по достижении напряжением Un. зоны (6) по командам с входов 60 и 61 или через элементы 56, 68, 65,69и70 если код принимает одно из граничных допустимых значений, анализируемых цифровыми компараторами 69 и 70. Направление счета определено сигналом с входа 60 через инвертор 63 (при логической единице на выходе инвертора ко увеличивается). Скорость перестройки зависит от частоты генератора 67. Установка фиксированного коэффициента передачи аттенюатора 3 происходит по импульсу 28 Установка (фиг.2 и 5) с входа 62.

Измерительный усилитель (фиг.6) работает следующим образом.

Переключение усилительного касра 35 прекращает подачу импульсов 26 када 86.1 осуществляется аналоговыми

)0 образом.

(

0

5

0

5

0

5

0

5

Код NJ снимается на выход 59 блока со счетчика 55.Предполагается, что счетчик управляется следующими сигналами: изменения кода происходят по положительным перепадам на тактовом входе и логической 1м на входе разрешения, увеличение кода происходит при логической единице на входе реверса, уменьшение - при логическом нуле. Ограничение возможных состояний счетчика осуществляют цифровые компараторы 57 и 58 и элементы 51.2 и 51.3. Направление счета формируется сигналом с входа 48. Моменты переключения определены фронтами импульсов с входа 47. Разрешение на счет (логическая 1 на входе разрешения) в режиме измерений формируется элементами 54.1 и 54.2 с входов 48 и 49, а в режиме установки нуля - также с входа 45 элементом 51.1 через триггеры 50.1 и 50.2.

Код снимается с выхода счетчика 71. Разрешение на счет р виде логической единицы формируется триггером 66 (фиг.5, диаграмма 79). Включение триггера 66 происходит в момент ТЗ (фиг.5) по переднему фронту импульса 28 (фиг.2 и 5), выключение триггера 66 осуществляется через элементы 63-65 по достижении напряжением Un. зоны (6) по командам с входов 60 и 61 или через элементы 56, 68, 65,69и70, если код принимает одно из граничных допустимых значений, анализируемых цифровыми компараторами 69 и 70. Направление счета определено сигналом с входа 60 через инвертор 63 (при логической единице на выходе инвертора код увеличивается). Скорость перестройки зависит от частоты генератора 67. Установка фиксированного коэффициента передачи аттенюатора 3 происходит по импульсу 28 Установка (фиг.2 и 5) с входа 62.

Измерительный усилитель (фиг.6) работает следующим образом.

Переключение усилительного касП15

мультиплексорами 87.1 и 87.2, при этом при больших уровнях входного сигнала усилитель 88.1 из усилительного тракта выключается. Структура фиг.6 допускает выполнение измерительного усилителя как в радиочастотном варианте, так и в виде усилителя постоянного тока. В первом из них фильтры выполняются полосовыми, усилитель 88 J малошумящим. Во втором варианте фильтры выполняются в виде фильтров низших частот, усилитель 88.1 - с малым смещением (например, с модуляцией- демодуляцией) . Расширение диапазона преобразователя обеспечивается: в область больших уровней - применением усилителей 88.2-88.6, не обладающих достаточно большим диапазоном, но способных передавать большие уровни, в область малых уровней - применением малошумящёго (.с малым смещением) усилтеля 88.1, который при больших уровнях из тракта выключается.

Погрешность преобразования всего преобразователя при малых уровнях оп

далее при 10 . Переход ь Ю характеризуется включением каскада 86.1 и выключением каскада 86.5. Каскад 86.6 управляется младшим разрядом двоичного кода NIJ, причем младший разряд в формировании унитарного кода не участвует. Каскад

5

12

ределяется: в радиочастотном варианте - шумами первого каскада (усиление по каскадам с этой целью распределено неравномерно - первый каскад имеет мгкси- мальное усиление), в варианте усилителя постоянного тока - шумами и смещением первого каскада. В известном преобразователе усиление каскадов одинаково (каскады идентичны), следовательно на погрешность преобразования повлияют смещение и шумы нескольких первых каскадов, к которым должны быть предъявлены более жесткие требования одновременно по шумам (смещению) и динамическому диапазону, В предлагаемом преобразователе требования к первому каскаду 86.1 (фиг.6) и к совокупности кавкадов 86.2-86.6 как к двум отдельным частям могут быть снижены, а в результате этого параметры всего усилителя улучшаются.

Дешифратор 90, который может быть выполнен на основе постоянного запоминающего устройства, реализует следующую таблицу.

ется более-менее оптимальным с учетом требований к величине диапазона, количеству каскадов при задгнной величине ступеньки усиления.

До момента ТЗ входное напряжение блока 5 находится в зоне (1). В момент ТЗ коэффициент передачи аттенюатора 3 принудительно устанавливается

Крв 0.5, Диапазон перестройки D

Kl

лежит в пределах 0,25 ,

т.е. . Увеличивать Dp выше этой величины нецелесообразно, так как пр этом возрастают требования к диапазон усилителя 1. Как видно из фиг.5, импульс 28 охватывает два импульса последовательности 24, импульсами которой переключается счетчик 55 (фиг.4 следовательно, за время ТЗ и Т5 усилитель J может переключиться два раза. Из них первое переключение, (фиг. момент Т4) отводится для возвращения Un в зону (1), второе - для перевода Un из зоны (U01, U05) в зону (Ufl1, U04 т.е. в зону, из которой блок 3 достиU03 + U04 гает уровня U

HO 2 р I (фиг.7).В исходном

01

Приме

состоянии перед обнулением U n U (участок I-0).

Кр К,ииц 0,25. При этом при установке Кр увеличивается до 0,5, т.е. на 6 дБ (участок 1-1). В момент Т4 усиление усилителя 1 уменьшается на одну ступень по команде с компарара 6 (участок 1-2).

К„ Кр 0,5. Коэффициент переда

0 тf

чи аттенюатора 3 не изменяется (участок 1-3).

Кр .::. При установке КР умешается до Кр 0,5, т.е. на 6 дБ (участок 1-4).

Во всех случаях примера 1 к момету Т5 Un находится в зоне досягаемос аттенюатором уровня Un0Пример 2. U п 3-Ua4.

Рассмотрим один из случаев К р К 0,5. При установке Кр не измняется (участок 2-1).

Случай Кр 1. При установке величина К„ уменьшается на 6 дБ (участок 3-1).

П р и м е р 3. ,,.

К- 0,5 (участок 4-0). При установке величина Кр не изменяется (учаток 4-1).

Кр Кр ицн 0,25. При установке величина К„ увеличивается на 6 дБ (участок 4-2).

Кр Кр/Л0(1 1. При установке величина Кр уменьшается на 6 дБ (учас- .ток 4-3), Un выходит из зоны (1), в момент Т4 происходит увеличение усиления усилителя на одну ступень (.участок 4-4) .

Во всех случаях примера J. к моменту Т9 U4 Voi

10

, 15

20

25

30

35

40 45

Триггер 50.2 (фиг.4) переходит в 1м в момент Т4 (.фиг.2, диаграмма 89) и в момент Т4 не влияет на работу счетчика 55 (фиг.4).

В момент Т9 (фиг.7 и 5), если un Ufl4, логическая VI с выхода схемы И 51.1 (фиг.4) через элементны 54.1 и 54.2 дает разрешение счетчику 55 на счет (предполагается f что по входу разрешения счетчик 55 считает при Р0 1). При этом, если . удовлетворяет (1)у на входе 48 - Лог.О, а на входе реверса счетчика 55 .1, число NQ в счетчике 55 увеличивается на единицу, усиление усилителя 1 увеличивается на одну ступень (фиг.7, кривые на участке 5-1). Поскольку ступень усиления Lй 10 дБ больше, чем соотношение уровней Ufl4H Uo5(около 8 дБ), то к моменту Т5 U попадает в зону досягаемости аттенюатора 3. С момента Т5 перестройкой аттенюатора 3 Un выводится в зону U02, U0i.

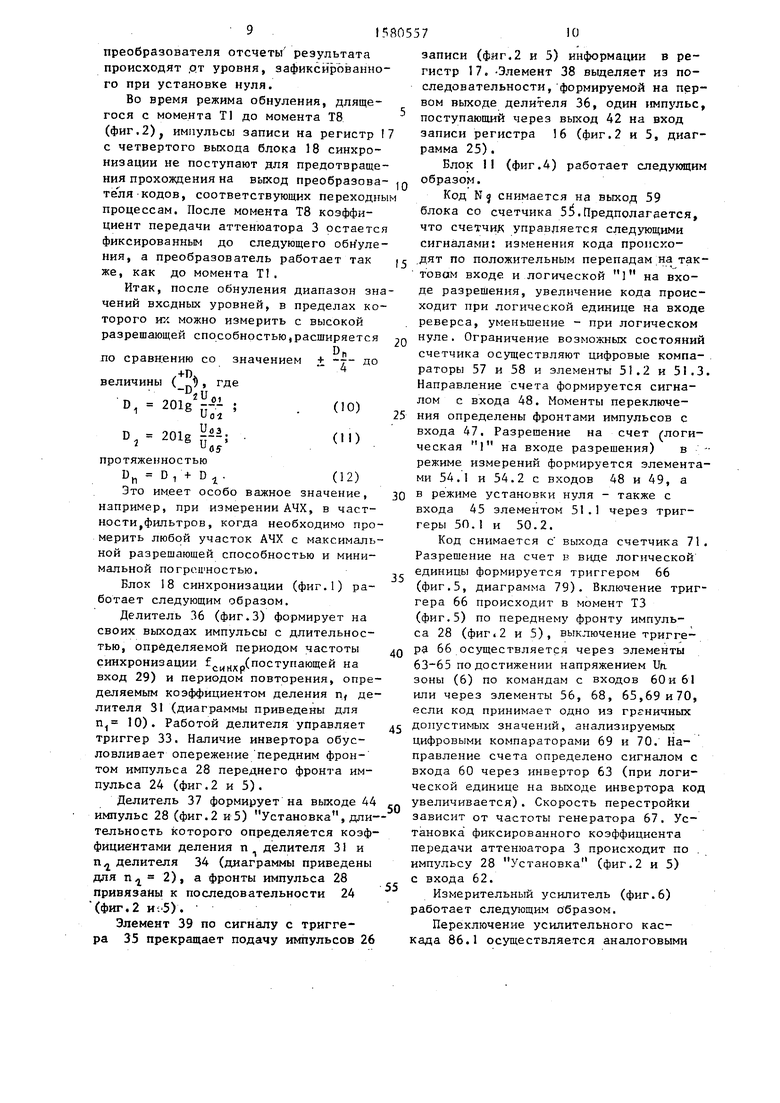

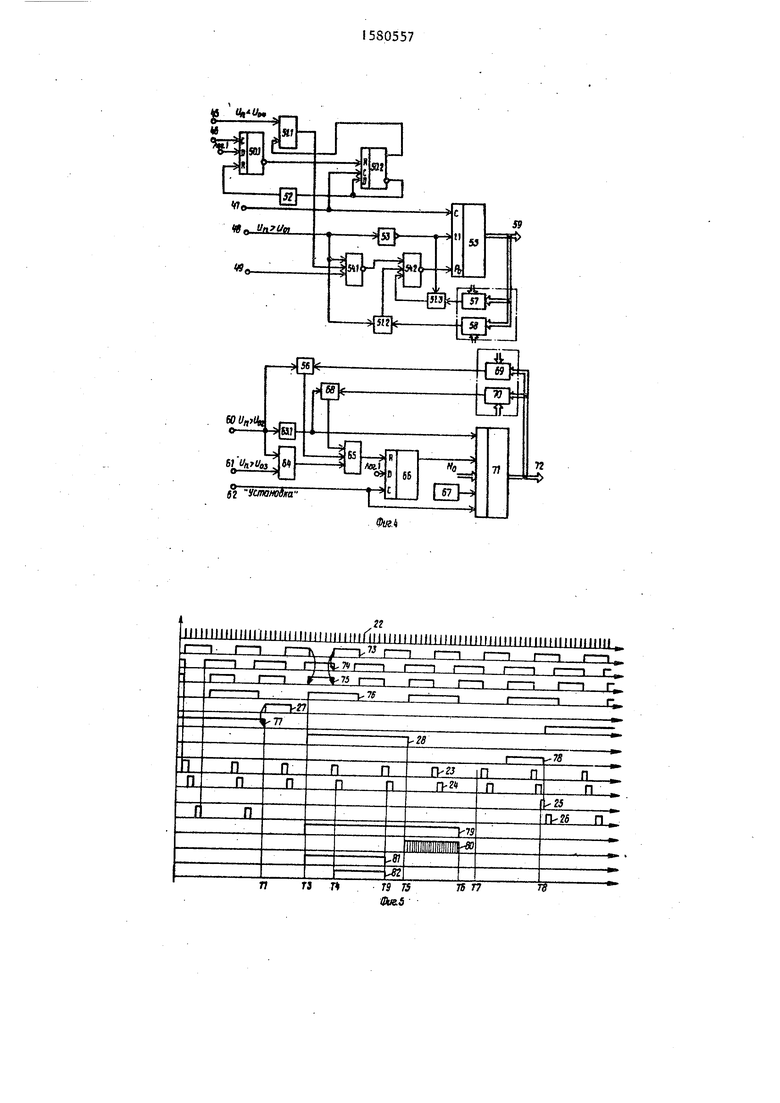

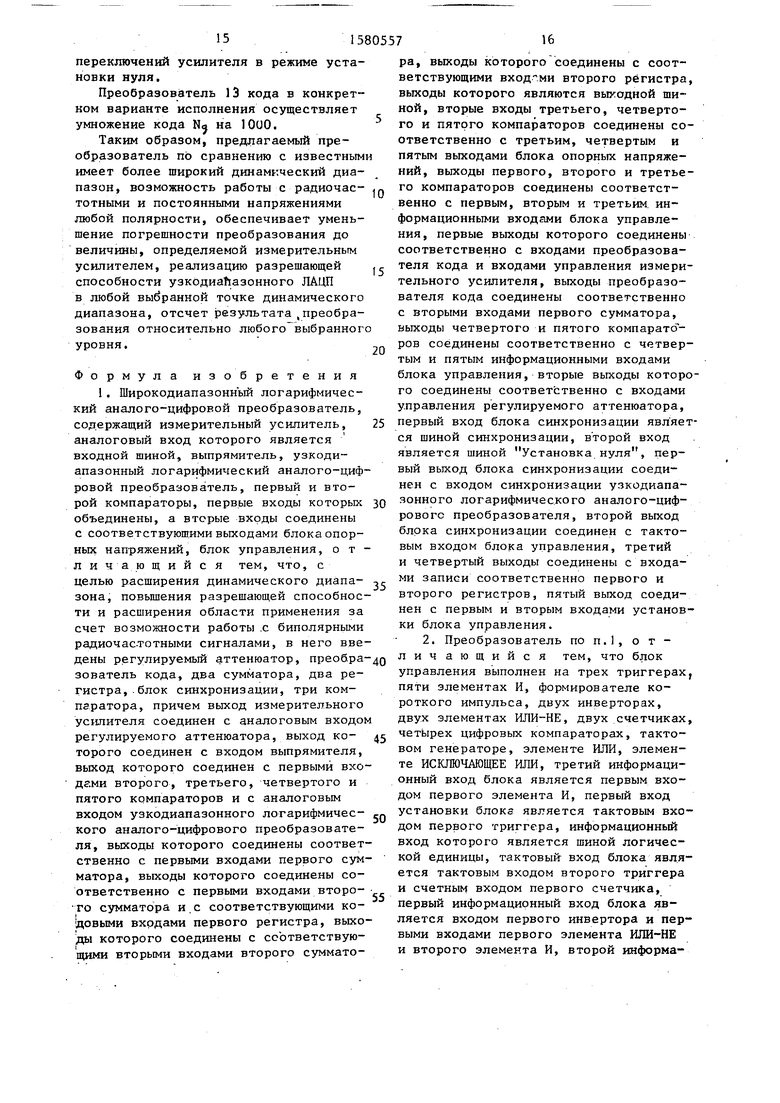

На фиг.8,а показано семейство диаграмм, поясняющих движение системы в координатах входной уровень блока 1 - входной уровень блока 5 (.оси логарифмические) для случая . .

В конкретном варианте исполнения выбрано Dn 20 дБ, L 10 дБ. Движение системы происходит в соответствии с семейством диаграмм фиг.8,б. При переключении усилителя 1 рабочая точка каждый раз попадает в (логарифмическую) серединку диапазона D. .

Число возможных состояний счетчи- ка 55, (фиг.4) определяется диапазоном преобразователя и величиной ступени усиления

D 130 дБ

Л

10 дБ

Коэффициент деления nf делителя 31 определяет соотношение частот 22 (фиг.5) и частоты дискретизации преобразователя. В конкретном варианте исполнения выбрана частота дискретизации 1 кГц {время преобразования 1 мс). С такой частотой выдает информацию УЛАПЦ 5 и переключается усилитель (фиг о 5, импульсы 24, приведены для 1 10). Коэффициент деления пг делителя J4 определяет количество импульсов последовательности 24 (фиг.5), охватываемых импульсом 28 Установка (фиг.5), т.е. количество

1515

переключений усилителя в режиме установки нуля.

Преобразователь 13 кода в конкретном варианте исполнения осуществляет умножение кода М на 1000.

Таким образом, предлагаемый преобразователь по сравнению с известным имеет более широкий динамический диапазон, возможность работы с радиочастотными и постоянными напряжениями любой полярности, обеспечивает уменьшение погрешности преобразования до величины, определяемой измерительным усилителем, реализацию разрешающей способности узкодиапазонного ЛАЦП в любой выбранной точке динамического диапазона, отсчет результата,преобразования относительно любого выбранног

уровня.

Формула изобретения 1 . Широкодиапазонн ый логарифмический аналого-цифровой преобразователь, содержащий измерительный усилитель, 25 аналоговый вход которого является входной шиной, выпрямитель, узкодиапазонный логарифмический аналого-цифровой преобразователь, первый и второй компараторы, первые входы которых 30 объединены, а вторые входы соединены с соответствуюшими выходами блока опорных напряжений, блок управления, отличающийся тем, что, с целью расширения динамического диапа- 35 зона, повышения разрешающей способности и расширения области применения за счет возможности работы с биполярными радиочастотными сигналами, в него введены регулируемый аттенюатор, преобра-дд л и ч зователь кода, два сумматора, два регистра, блок синхронизации, три компаратора, причем выход измерительного усилителя соединен с аналоговым входом регулируемого аттенюатора, выход ко- $5 торого соединен с входом выпрямителя, выход которого соединен с первыми входами второго, третьего, четвертого и пятого компараторов и с аналоговым

ра, выходы которого соединены с соответствующими входами второго регистра, выходы которого являются выходной шиной, вторые входы третьего, четвертого и пятого компараторов соединены соответственно с третьим, четвертым и пятым выходами блока опорных напряжений, выходы первого, второго и третьего компараторов соединены соответственно с первым, вторым и третьим информационными входами блока управления, первые выходы которого соединены соответственно с входами преобразователя кода и входами управления измерительного усилителя, выходы преобразователя кода соединены соответственно с вторыми входами первого сумматора, выходы четвертого и пятого компаратсГ- ров соединены соответственно с четвертым и пятым информационными входами блока управления, вторые выходы которого соединены соответственно с входами управления регулируемого аттенюатора, первый вход блока синхронизации является шиной синхронизации, второй вход является шиной Установка нуля, первый выход блока синхронизации соединен с входом синхронизации узкодиапазонного логарифмического аналого-цифрового преобразователя, второй выход блока синхронизации соединен с тактовым входом блока управления, третий и четвертый выходы соединены с входами записи соответственно первого и второго регистров, пятый выход соединен с первым и вторым входами установки блока управления.

входом узкодиапазонного логарифмичес- 5Q установки блока является тактовым вхокого аналого-цифрового преобразователя, выходы которого соединены соответственно с первыми входами первого сумматора, выходы которого соединены соответственно с первыми входами второ- то сумматора и с соответствующими кодовыми входами первого регистра, выходы которого соединены с соответствующими вторыми входами второго сумматодом первого триггера, информационный вход которого является шиной логической единицы, тактовый вход блока является тактовым входом второго триггера и счетным входом первого счетчика, первый информационный вход блока является входом первого инвертора и первыми входами первого элемента ИЛИ-НЕ и второго элемента И, второй информа16

0

5 0 5 д л и ч 5

ра, выходы которого соединены с соответствующими входами второго регистра, выходы которого являются выходной шиной, вторые входы третьего, четвертого и пятого компараторов соединены соответственно с третьим, четвертым и пятым выходами блока опорных напряжений, выходы первого, второго и третьего компараторов соединены соответственно с первым, вторым и третьим информационными входами блока управления, первые выходы которого соединены соответственно с входами преобразователя кода и входами управления измерительного усилителя, выходы преобразователя кода соединены соответственно с вторыми входами первого сумматора, выходы четвертого и пятого компаратсГ- ров соединены соответственно с четвертым и пятым информационными входами блока управления, вторые выходы которого соединены соответственно с входами управления регулируемого аттенюатора, первый вход блока синхронизации является шиной синхронизации, второй вход является шиной Установка нуля, первый выход блока синхронизации соединен с входом синхронизации узкодиапазонного логарифмического аналого-цифрового преобразователя, второй выход блока синхронизации соединен с тактовым входом блока управления, третий и четвертый выходы соединены с входами записи соответственно первого и второго регистров, пятый выход соединен с первым и вторым входами установки блока управления.

установки блока является тактовым входом первого триггера, информационный вход которого является шиной логической единицы, тактовый вход блока является тактовым входом второго триггера и счетным входом первого счетчика, первый информационный вход блока является входом первого инвертора и первыми входами первого элемента ИЛИ-НЕ и второго элемента И, второй информацнонный вход блока является вторым входом первого элемента ИЛИ-НЕ, инверсный выход первого триггера соединен с входом установки в О второго триггера, прямой выход которого соеди нен с вторым входом первого элемента И, выход которого соединен с третьим входом первого элемента ИЛИ-НЕ, инверсный выход второго триггера сое- динен с его информационным входом и через формирователь короткого импульса с входом установки в О первого триггера, выход первого инвертора соединен с входом реверса первого счетчи ка и с первым входом третьего элемента И, выход первого элемента ИЛИ-НЕ соединен с первым входом второго элемента ИЛИ-HEj, выход второго элемента И соединен с вторым входом зторо- го элемента ИЛИ-НЕ, выход третьего элемента И соединен с третьим входом второго элемента ИЛИ-НЕ, выход которого соединен с входом разрешения первого счетчика, выходы которого являются первыми выходами блока и через первый и второй цифровые компараторы соединены соответственно с вторыми входами третьего и второго элементов И, четвертый информационный вход блока являет-- ся первыми входами четвертого элемента И, элемента ИСКЛЮЧАЮЩЕЕ ИЛИ ичерез второй инвертор соединен с первым входом пятого элемента И и с входом реверса второго счетчика, пятый информационный вход блока соединен с вторым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход установки блока соединен с тактовым входом третьего триггера и с входом установки второго счетчика, выходы четвертого и пятого элементов И соединены соответственно с первым и вторым входами элемента ИЛИ, третий вход которого соединен с выходом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, а выход - с входом установки в О третьего триггера, информационный вход которого является шиной логической единицы, прямой выход третьего триггера соединен с входом разрешения второго счетчика, ус- тановочные входы которого являются шиной фиксированного кода, выход тактового генератора соединен со счетным входом второго счетчика,выходы которого являются вторыми выходами блока и .через третий и четвертый цифровые компараторы соединены соответственно с вторыми входами четвертого и шестого элементов И, вторые входы первого,

второго, третьего и четвертого цифровых кокпараторов являются шинами соответствующих опорных кодов.

Д. Преобразователь по п., о т - личаюшийся тем, что измерительный усилитель выполнен на фильтре, дешифраторе,, шести последовательно соединенных усилительных каскадах, первый усилительный каскад выполнен на двух аналоговых мультиплексорах и . усилителе, второй, третий, четвертый, пятый и шестой усилительные каскады выполнены на последовательно соединенных управляемом усилителе и фильтре, выход фильтра шестого усилительного

каскада является выходом измерительного усилителя, аналоговый вход которого через фильтр соединен с первым входом первого аналогового мультиплексо- ра, первый выход которого соединен с первым входом второго аналогового мультиплексора, второй вход которого через усилитель соединен с вторым выходом первого аналогового мультиплек- JQ сора, второй вход которого и третий вход второго аналогового мультиплексора объединены и соединены с первым выходом дешифратора, выход второго аналогового мультиплексора является вы-

TJ П ТЗ П

ходом первого усилительного каскада, второй, третий, четвертый, пятый и шестой входы дешифратора соединены соответственно с первыми входами управляемых усилителей второго,третьего, четвертого, пятого и шестого усилительных каскадов, входы дешифратора являются входами управления измерительного усилителя, второй вход управляемого усилителя является входом соответствующего усилительного каскада, кроме первого, а выход фильтра - выходом соответствующего усилительно- fro каскада, кроме первого.

75 Т6 77 Т8

Фиг. 2

56fe

п

niliiiiiliiiiimiiHiiiimiiiimriiiimt

и,

(01)23

(

buoW (UOSJOSB

( 3

(U09)Q,2B

Un.B

Б(на dxode блока 5)

| Усилительное устройство | 1985 |

|

SU1259475A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство широкодиапазонного логарифмического аналого цифрового преобразования | 1980 |

|

SU900440A1 |

| i | |||

Авторы

Даты

1990-07-23—Публикация

1988-09-12—Подача