СП S

ю

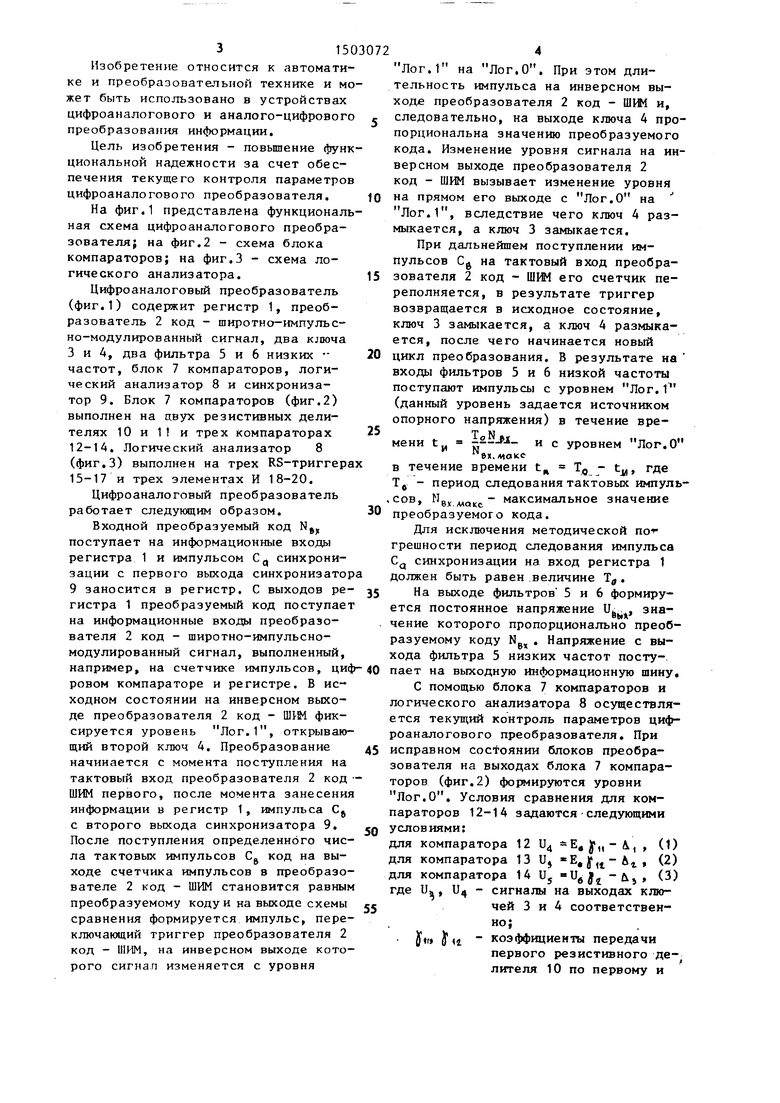

Фие.1

3150

Изобретение относится к автоматике и преобразовательной технике и может быть использовано в устройствах цифроаналогового и аналого-цифрового преобразования информации.

Цель изобретения - повышение функциональной надежности за счет обеспечения текущего контроля параметров цифроаналогового преобразователя,

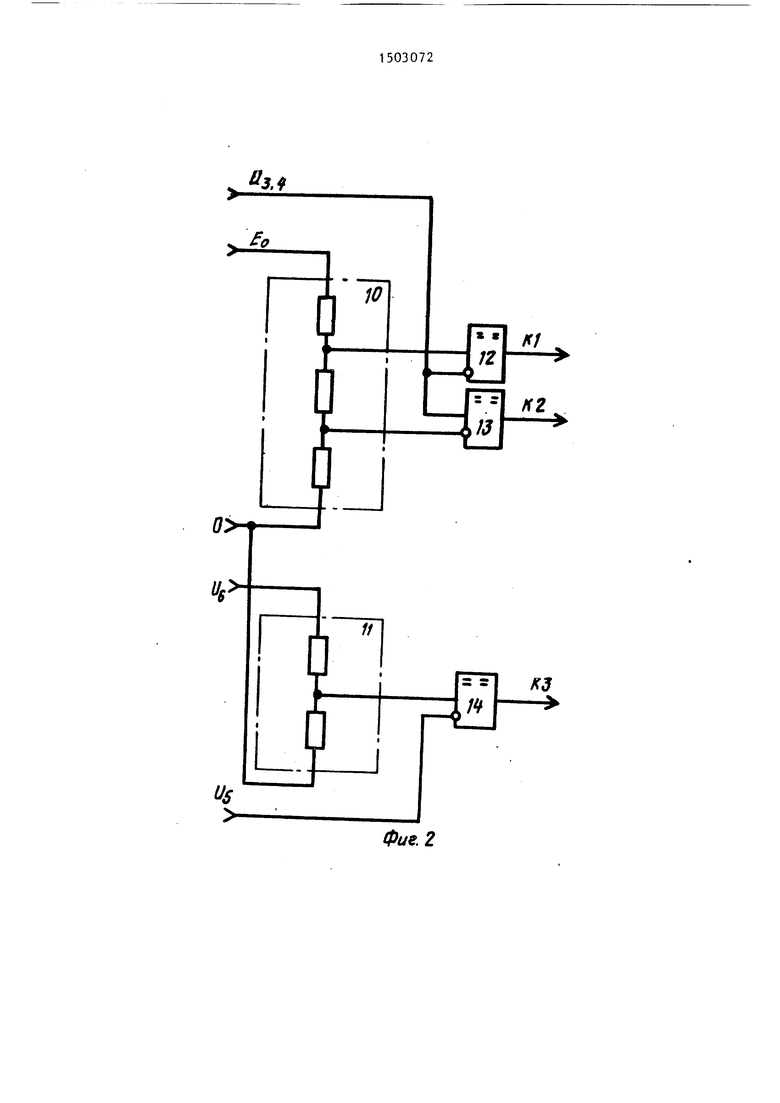

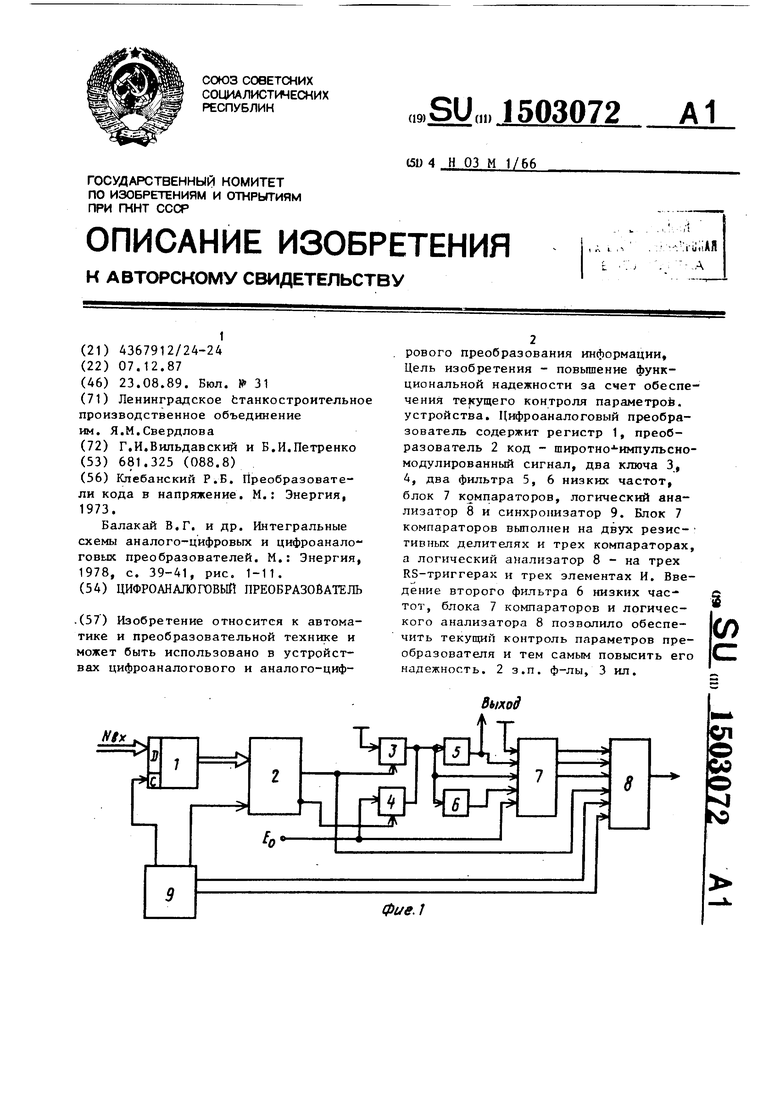

На фиг,1 представлена функциональная схема цифроаналогового преобразователя; на фиг.2 - схема блока компараторов; на фиг.З - схема логического анализатора.

Цифроаналоговый преобразователь (фиг.1) содержит регистр 1, преобразователь 2 код - широтно-импульс- но-модулированный сигнал, два 3 и 4, два фильтра 5 и 6 низких частот, блок 7 компараторов, логический анализатор 8 и синхронизатор 9. Блок 7 компараторов (фиг.2) выполнен на цвух резистивных делителях 10 и 11 и трех компараторах 12-14. Логический анализатор 8 (фиг.З) выполнен на трех RS-триггерах 15-17 и трех элементах И 18-20.

Цифроаналоговый преобразователь работает следующим образом.

Входной преобразуемый код Nj поступает на информационные входы регистра 1 и импульсом Сд синхронизации с первого выхода синхронизатор 9 заносится в регистр. С выходов ре- гистра 1 преобразуемый код поступает на информационные входы преобразователя 2 код - широтно-импульсно- модулированный сигнал, выполненный, например, на счетчике импульсов, циф ровом компараторе и регистре. В исходном состоянии на инверсном выходе преобразователя 2 код - ШШ фиксируется уровень Лог.1, открывающий второй ключ 4. Преобразование начинается с момента поступления на тактовый вход преобразователя 2 код ШИМ первого, после момента занесения информации в регистр 1, импульса Cj с второго выхода синхронизатора 9. После поступления определенного числа тактовых импульсов С код на выходе счетчика импульсов в преобразователе 2 код - ШИМ становится равным преобразуемому коду и на выходе схемы сравнения формируется импульс, переключающий триггер преобразователя 2 код - ШИМ, на инверсном выходе которого сигнал изменяется с уровня

Лог.1 на Лог.О. При этом длительность импульса на инверсном выходе преобразователя 2 код - ШИМ и, следовательно, на выходе ключа 4 пропорциональна значению преобразуемого кода. Изменение уровня сигнала на инверсном выходе преобразователя 2 код - ШИМ вызывает изменение уровня на прямом его выходе с Лог.О на Лог. Г , вследствие чего ключ 4 размыкается, а ключ 3 замыкается.

При дальнейшем поступлении импульсов С на тактовый вход преобразователя 2 код - ШИМ его счетчик переполняется, в результате триггер возвращается в исходное состояние, ключ 3 замыкается, а ключ 4 размыкается, после чего начинается новый цикл преобразования. В результате на входы фильтров 5 и 6 низкой частоты поступают импульсы с уровнем Лог. (данный уровень задается источником опорного напряжения) в течение вреГТ1 и

мени tj, с уровнем Лог. О 6. маке

В течение времени t Тд - t, где Tj - период следования тактовых импульсов, f ev MQKt максимальное значение преобразуемого кода.

Для исключения методической по грешности период следования импульса Cjj синхронизации на вход регистра 1 должен быть равен величине Т.

На выходе фильтров 5 и 6 формируется постоянное напряжение U .., значение которого пропорционально преобразуемому коду Ng. Напряжение с выхода фильтра 5 низких частот поступает на выходную информационную шину,

С помощью блока 7 компараторов и логического анализатора 8 осуществляется текущий контроль параметров цифроаналогового преобразователя. При исправном состоянии блоков преобразователя на выходах блока 7 компараторов (фиг.2) формируются уровни Лог.О. Условия сравнения для компараторов 12-14 задаются следующими условиями:

для компаратора , у,,-,, (1) для компаратора 13 Uj , (2) для компаратора 14 Uj бУг J где и, и - сигналы на выходах ключей 3 и 4 соответственно; У (1 коэффициенты передачи

первого резистивного делителя 10 по первому и

второму выходам соответственно;u,j Д - допустимое отклонение

выходного сигнала ключей 3 и 4 от единичного и нулевого уровней соответственно;

Уг коэффициент передачи второго реэистивного делителя 11; допустимое отклонение

вькодного сигнала фильтра 5 от установившегося значения; и, и - сигналы на выходах

фильтров 5 и 6 низких частот соответственно. Выходные сигналы блока 7 компараторов поступают на .соответствующие входы логического анализатора 8 (фиг.З), в котором формируется сигнал Авария, при наличии уровня Лог,1 хотя бы на одном из выходов блока 7 компараторов, С некоторой задержкой после импульса С, синхронизации, поступающего на вход регистра 1 с первого выхода синхронизатора 9, на его третьем выходе формируется короткий импульс Ср, поступающий на R-входы RS-триггеров 15-17. При наличии уровней Лог . О на S-входах всех RS-триггеров,(что свидетельствует о правильном функционировании всех блоков преобразователя), на инверсных выходах RS-триггеров 15-17 и на выходе элемента И 20 формируются сигналы с уровнем Лог.Г , последнее свидетельствует о правильной работе циф- роаналогового преобразователя.

При нарушении условия (1), например, за счет увеличения сопротивления ключа 4 в замкнутом состоянии, компаратор 12 изменит свое состояние, что приведет к переключению RS-триг- гера 15 и появлению уровня Лог.О на выходе элемента Р1 20. Аналогичный процесс происходит в случае возрастания сопротивления ключа 3 в замкнутом состоянии, при этом переключается . компаратор 13, выходной сигнал которого, поступающий через элемент И 18 на 8-вход RS-триггера 16, обуславливает переключение триггера 16, в результате на выходе элемента И 20 фор- мируется сигнал Авария.

Если при неизменном значении сигналов на входах фильтров 5 и 6 их выходные напряжения становятся неравны

0

ми, то более вероятно нарушение работы фильтра 5 вследствие изменения со- прот1галения линии связи с нагрузкой, вариации сопротивления нагрузки, появления утечек и т.п. При сбоях в работе цифровых блоков 1 и 2 также будут изменяться1И выходные напряжения фильтров 5 и 6. в этом случае (при условии, что инерционность фильтра 6 в несколько раз больше инерционности фильтра 5) легко может быть обнаружено отличие Ug, от контрольного значения (U, ). В обоих, случаях

5 произойдет переключение компаратора 14, выходной сигнал которого поступает на первый вход элемента И 19. На второй вход элемента И 19 с четвертого выхода синхронизатора 9 пос0 тупают импульсы С,, период следования которых существенно больше периода сигнала С. Такое соотношение периодов сигналов Сд и Cj не приводит -к формированию сигнала Авария в те5 чение переходного процесса установления выходного сигнала Upj при смене значения входного кода N х Вы- ходной сигнал элемента И 19 обуславливает состояние RS-триггера 17 и, при появлении Лог,О на выходе триггера 17, наличие сигнала Авария на выходе элемента И 20.

Таким образом, наличие блока 7 компараторов, логического анализатора 8 с соответствующими связями повышает надежность (достоверность результатов) цт1фроаналогового преобразователя .

е

40

Формула изобретения

е

1. Цифроаналоговый преобразова- . тель, содержащий регистр, информационные входы, которого являются входной с шиной преобразуемого кода, вход разрешения записи подключен к первому выходу синхронизатора, второй выход которого соединен с тактовым входом преобразователя код - широтно-им- пульсно-модулированный сигнал, информационные входы которого соединены с соответствующими выходами регистра, а прямой и инверсный выходы подключены к управляющим входам соответственно первого и второго ключей, информационные вхо/;ы которых являются соответственно 1ииной нулевого и шиной единичного потенциала, выход первого ключа об1 единен с выходом

0

второго ключа и соединен с входом первого фильтра низких частот, отличающийся тем, что, с целью повьппения функциональной надежности за счет обеспечения текущего контроля параметров цифроаналого- вого преобразователя, в него введены второй фильтр низких частот, блок

и второй выходы соединены соответственно с неинвертирующим входом первого и инвертирующим входом второго компараторов, инвертирующий вход первого компаратора объединен с неинвертирующим входом второго компаратора и является третьим входом блока, первый вход второго резистив

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРОАНАЛОГОВЫЙ ПРЕОБРАЗОВАТЕЛЬ | 2009 |

|

RU2433528C2 |

| Цифроаналоговый преобразователь | 1989 |

|

SU1735999A1 |

| Цифро-аналоговый преобразователь | 1977 |

|

SU690624A1 |

| ЦИФРОАНАЛОГОВЫЙ ПРЕОБРАЗОВАТЕЛЬ | 2012 |

|

RU2485681C1 |

| АДАПТИВНЫЙ ЛАЗЕРНЫЙ ДОПЛЕРОВСКИЙ ЛОКАТОР | 1990 |

|

RU2012013C1 |

| Многоканальный регулятор температуры | 1991 |

|

SU1783495A1 |

| Способ локальной радиотелефонной связи и система для его осуществления | 1991 |

|

SU1831767A3 |

| Преобразователь код-напряжение с широтноимпульсной модуляцией | 1978 |

|

SU790283A1 |

| Устройство измерения временных интервалов | 1984 |

|

SU1144062A1 |

| Устройство для измерения ширины спектра сигнала радиопередатчиков на различных уровнях | 1988 |

|

SU1576868A1 |

Изобретение относится к автоматике и преобразовательной техники и может быть использовано в устроствах цифроаналогового и аналого-цифрового преоразования информации. Цель изобретения - повышение функциональной надежности за счет обеспечения текущего контроля параметров устройства. Цифроаналоговый преобразователь содержит регистр 1, преобразователь 2 код - широтно-импульсномодулированный сигнал, два ключа 3, 4, два фильтра 5, 6 низких частот, блок 7 компараторов, логический анализатор 8 и синхронизатор 9. Блок 7 компараторов выполнен на двух резистивных делителях и трех компараторах, а логический анализатор 8 - на трех RS-триггерах и трех элементах И. Введение второго фильтра 6 низких частот, блока 7 компараторов и логического анализатора 8 позволило обеспечить текущий контроль параметров преобразователя и тем самым повысить его надежность. 2 з.п. ф-лы, 3 ил.

компараторов и логический анализатор,Q ного делителя является четвертым

входом блока, а выход соединен с инвертирующим входом третьего ком ратора, инвертирующий вход которо является вторым входом блока, вто вход первого резистивного делител объединен с одноименным входом вт рого резистивного делителя и явля ся первым входом блока.

выход которого является выходной шиной Авария, первый, второй, третий, четвертый и пятый входы блока компараторов соединены соответственно с шиной нулевого потенциала, выходом первого фильтра низких частот выходом первого ключа, выходом второго фильтра низких частот и шиной единичного потенциала, первый, второй и третий выходы блока компараторов соединены соответственно с пе вьвч, вторым и третьим входами логического анализатора, четвертый, пя тый и шестой входы которого подключены соответственно к прямому выходу преобразователя код - широтно-им пульсно-модулированный сигнал, к третьему и четвертому выходам синхронизатора, выхбд первого фильтра низких частот является выходной информационной шиной.

ного делителя является четвертым

входом блока, а выход соединен с неинвертирующим входом третьего компаратора, инвертирующий вход которого является вторым входом блока, второй вход первого резистивного делителя объединен с одноименным входом второго резистивного делителя и является первым входом блока.

L

s

12

KJ

кг

/J

F43

КЗ

Фие.г

t/e.J

| Клебанский Р.Б | |||

| Преобразователи кода в напряжение | |||

| М.: Энергия, 1973 | |||

| Балакай В.Г | |||

| и др | |||

| Интегральные схемы аналого-цифровых и цифроанало- говых преобразователей | |||

| М.: Энергия, 1978, с | |||

| Машина для изготовления проволочных гвоздей | 1922 |

|

SU39A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1989-08-23—Публикация

1987-12-07—Подача