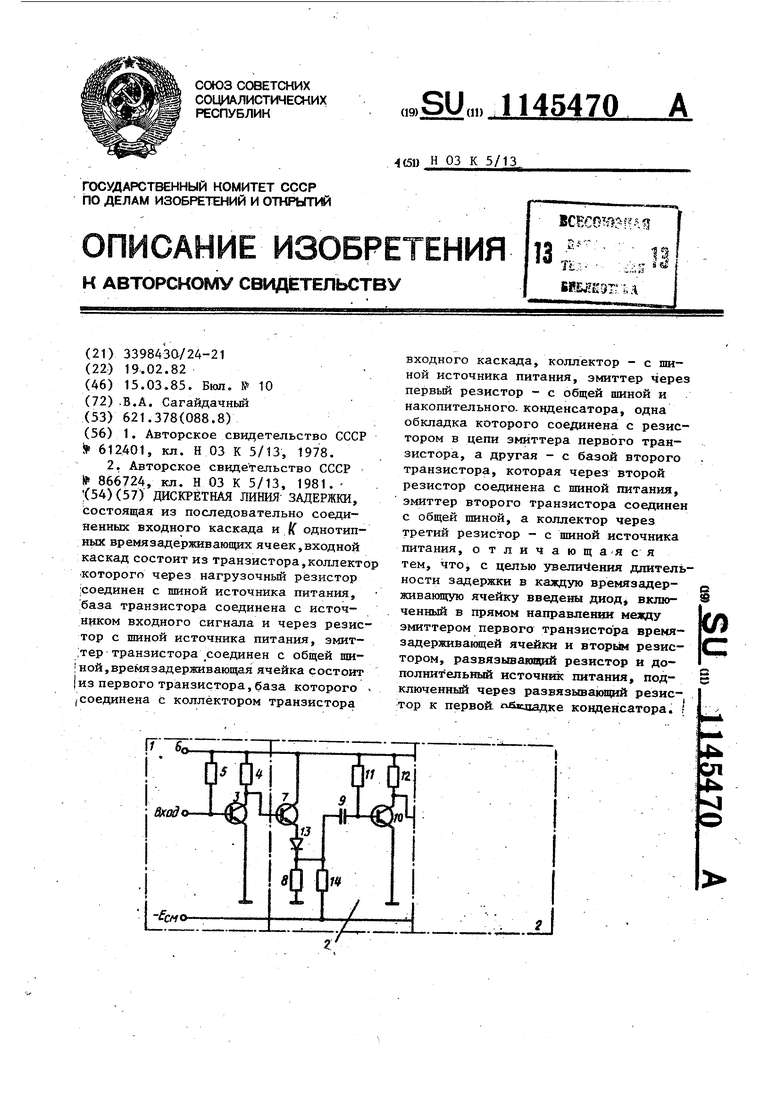

. «11 (чобретеиие относ-.ится к импульсной технике и ире/дназначено для испо.)наиия в средствах автоматики и связи. Известно устройство, содержащее переключатель тока, управляемы вход ным импульсом, интегрирующая КС-цепь конденсатор которой подключен к входу порогового каскада, подсоединенного выходом в входу вьгходного каскада, диоды, резисторы, два зарядноразрядных ключа на транзисторах,, при чем коллекторы указанных транзисторов через диоды соединены с одним из выводов резистора RC-цепи, с другим вьгоодом которого соединены эмиттеры, а базы через резисторы соединены с выходом выходного каскада 13. Недостатком данного устройства является сложность аппаратурного испол нения. Известно устройство, состоящее из последовательно соединенных входного каскада и К однотипных времязадерживащих ячеек, входной каскад состоит из транзистора, коллектор которого через нагрузочный резистор соединен с шиной питания, база транзистора соед нена с источником входного сигнала и через резистор соединена с шиной питания, эмиттер транзистора соединен с общей шиной 5 времязадерживающая ячейка состоит из первого транзистора, база которого соединена с коллек тором транзистора входного каскада, коллектор - с шиной питания, эмиттер - через первый резистор с общей шиной, накопительного конденсатора, одна обкладка которого соединена с резистором в цепи эмиттера первого транзистора, а другая - с базой второго транзистора, которая через второй резистор соединена с шиной питания, эмиттер второго транзистора соединен с общей шиной, а коллектор через третий резистор - с шиной пита ния zj. Недостатком известного устройства являются ограниченные возможности по формированию длительности задержки, обусловленные тем, что сопротивление нагрузочного резистора первого транзистора, определяющее длительность задержки, влияет на уровень запирающего потенциала второго транзистора и не может быть выбрано больше величины, осуществляющей надежное запира ние второго транзистора. 02 Цель настоящего изобретения - увеличение длительности задержки при сохранении уровня нестабильности задержки. Поставленная цель достигается тем, что в устройство содержащее последовательно соединенные входной каскад и К однотипньгх времязадерживающих ячеек, входной каскад состоит из транзистора, коллектор которого через нагрузочный резистор соединен с шиной источника питания, база транзистора соединена с источником входного сигнала и через резистор соединена с шиной источника питания, эмиттер транзистора соединен с общей шиной, времязадерживающая ячейка состоит из первого транзистора база которого соединена с. коллектором транзистора входного каскада, коллектор - с шиной источника питания, эмиттер через первый резистор - с общей шиной, накопительного конденсатора, одна обкладка которого соединена с резистором в цепи эмиттера первого транзистора, а другая - с базой второго транзистора, которая через второй резистор соединена с шиной источника питания, эмиттер второго транзистора соединен с общей шиной, а коллектор через третий резистор - с шиной источника питания, в каждую времязадерживающую ячейку введены диод, включенной в прямом направлении между эмиттером первого транзистора времязадерживающей цепи и вторым резистором, развязывающий резистор и дополнительньй источник питания, подключенньш через развязьюающий резистор к первой обкладке конденсатора. На чертеже представлена принципиальная схема дискретной линии задержки , Дискретная линия за держки состоит из последовательно соединенных входного каскада 1 и К однотипньсх времязадерживающих ячеек 2, входной каскад состоит из транзистора 3, коллектор которого через нагрузочный резистор 4 соединен с шиной источника питания, база которого через резистор 5 также соединена с шиной 6 ис- . точника питания, времязадерживающие ячейки 2 состоят из первого транзистора 7, база которого соединена с коллектором транзистора 3, коллектор с шиной питания, эмиттер черезрезистор 8 - с общей шиной и накопительного конденсатора 9, одна обклад31145

ка которого соединена с резистором 8, а другая - с базой второго транзистора 10, база которого через резистор 11 соединена с шиной источника питания, эмиттер транзистора 10 соединен с общей шиной, а коллектор через третий резистор 12 с шиной источника питания, диода 13 включенного в прямом направлении между змиттером транзистора 7 и резистором 8 в цепи эмиттера транзистора 7, и развязьгоающего резистора 14, через который источник напряжения противоположного питанию знака подключен к катоду диода 13.

Устройство работает следующим образом.

В исходном состоянии транзисторы 3 и 10 насыщены (открыты) за счет токов, протекающих в резисторах 5 и 11, транзистор 7 закрыт и конденсатор 9 разряжен. Входной импульс отрицательной полярности закрьшает транзистор 3, в результате чего на вход транзистора 7 поступает импульс положительной полярности с. амплитудой +ЕК. Транзистор 7 открьщается и начинается заряд конденсатора 9 до напряжения +ЕК, через диод 13 и вход насыщенного транзистора 10.При этом транзистор 10 еще больше насыщается, но состояние последующих каскадов линии не изменяется. По окончании входного импульса транзистор 3 возвращается в открытое, а транзистор 7 закрытое состояния и конденсатор 9 оказывается приложенным правой обкладкой, имеющей отрицательный потенциал, к входу транзистора 10.

Источник обратного смещения отдае возрастающую часть своего потенциала конденсаторной обкйпадке, запирающей транзистор 10.. В течении времени разряда конденсатора 9 транзистор 10 закрыт, что приводит к заряду конденсатора следующей ячейки. Далее процессы повторяются и в результате передний фронт, входного импульса оказывается задержанным в каждой ячейке на время разряда накопительного конденсатора.

Таким образом, предлагаемое устройство обеспечивает использование напряжения обратного смещения по сравнению с известным, что увеличивает длительности задержки в 1,5 раз при том же уровне нестабильности.

| название | год | авторы | номер документа |

|---|---|---|---|

| Ячейка временной задержки импульсов | 1980 |

|

SU945967A1 |

| Электронное реле | 1981 |

|

SU993474A1 |

| Стабилизатор повышенного напряжения постоянного тока | 1982 |

|

SU1086415A1 |

| Электронный ключ | 1982 |

|

SU1056465A1 |

| Устройство задержки | 1981 |

|

SU993473A1 |

| Н. Г. Горбушин и М. Л. Мирианашвили Институт медицинской радиологии АМН СССР | 1970 |

|

SU277419A1 |

| Аналоговое запоминающее устройство | 1978 |

|

SU767844A1 |

| Импульсный генератор | 1973 |

|

SU483774A1 |

| Однотактный стабилизированный преобразователь постоянного напряжения | 1990 |

|

SU1777212A1 |

| Генератор импульсов | 1982 |

|

SU1127100A1 |

ДИСКРЕТНАЯ ЛИНИЯ ЗАДЕРЖКИ, состоящая из последовательно соединенных входного каскада и К однотипных время задерживающих ячеек, входной каскад состоит из транзистора,коллектор которого через нагрузочньй резистор :соединен с шиной источника питания, база транзистора соединена с источником входного сигнала и через резистор с шиной источника питания, эмит,тер транзистора соединен с общей ,времязадерживающая ячейка состоит Iиз первого транзистора,база которого , (Соединена с коллектором транзистора гг входного каскада, коллектор - с шиной источника питания, эмиттер через первый резистор - с общей шиной и накопительного, конденсатора, одна обкладка которого соединена с резистором в цепи змиттера первого транзистора, а другая - с базой второго транзистора, которая через второй резистор соединена с шиной питания, эмиттер второго транзистора соединен с общей шиной, а коллектор через третий резистор - с шиной источника питания, отличающа-яся тем, что, с целью увеличения длительности задержки в каждую времязадерживающую ячейку введены диод включенный в прямом направлении между (П эмиттером первого транзистора вреняС задерживанщей ячейки и вторым резистором, развязывающий резистор и дополнительный источник питания, подключенный через развязывающий резистор к первой г йкоадке конденсатора. |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство задержки импульсов | 1977 |

|

SU612401A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Импульсная линия задержки | 1979 |

|

SU866724A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1985-03-15—Публикация

1982-02-19—Подача