I

Изобретение относится к электронной импульсной технике,. а именно к дискретным устройствам задержки импульсных сигналов, и может найти применение в вычислительной технике, в средствах автоматики и связи.

Известны устройства задержки, содержащие реактивный элемент(RC- или LC-цепь), выходное фиксирующее устройство l .

Однако известные устройства имеют недостаточную стабильность и значительное потребление энергии.

Наиболее близкими по технической сущности к предлагаемому изобретению являются известные импульсные линии задержки,ячейки которых вьтолнены на основе времязадающей RC-цепи и последующего транзисторного ключа в качестве выходного устройства 2 3Однако известные импульсные линий задержки имеют такие недостатки, как максимальное потребление тока от источника в исходном состоянии из-за

насыщенного режима всех транзисторов |линии задержки и нестабильная работа .линии при времени задержки fy,ad ячейки, соизмеримом с временем переходных процессов.

Цель предлагаемого изобретения увеличение длительности задержки ячейки при сохранении уровней ее нестабильности времени задержки и энергопотребления .

to

Указанная цель достигается тем, что в известной импульсной линии задержки, состоящей из входного каскада и однотипных задерживающих ячеек, соединенных последовательно и со15держащих KJBOчeвoй каскад, состоящий из транзистора, нагрузочного резистора и резистора в цепи смещения входа транзистора по питанию, и накопительного конденсатора, одна обкладка

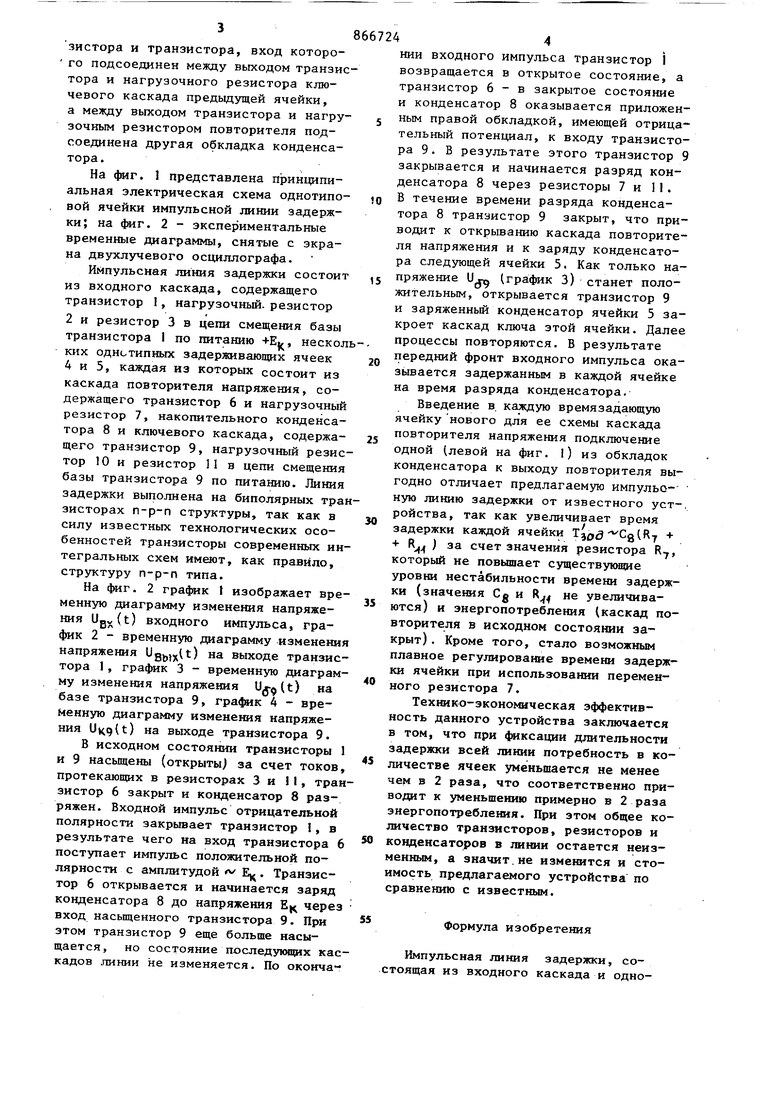

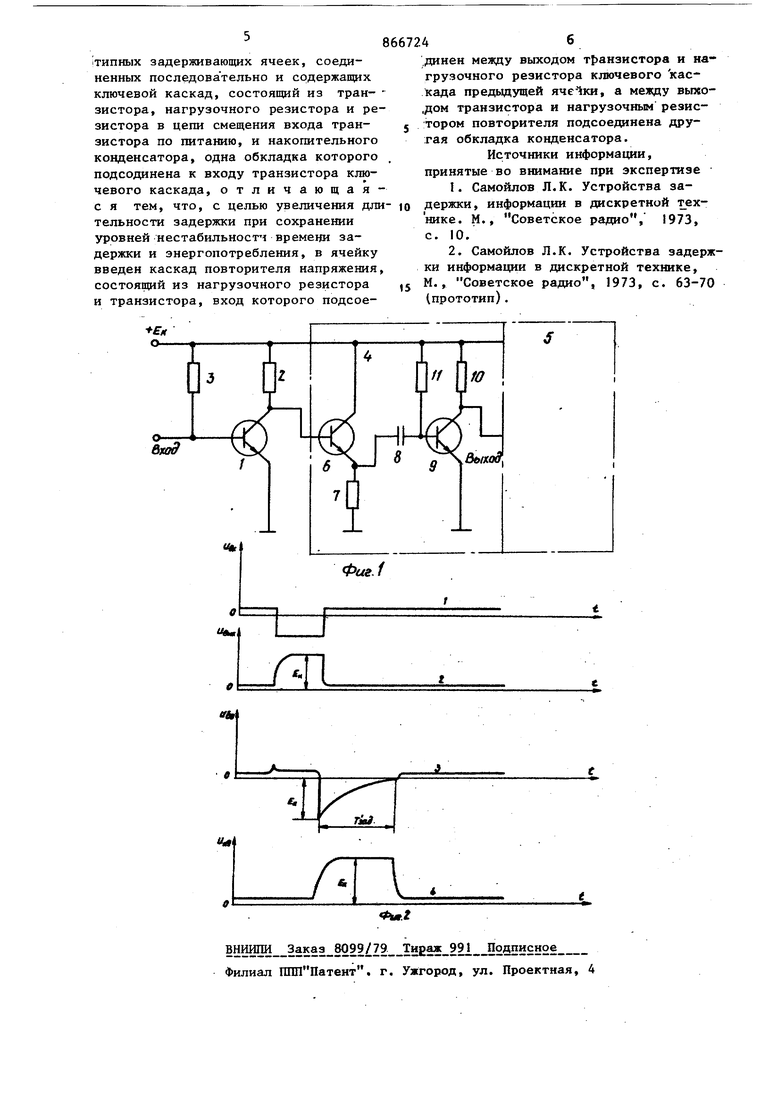

20 которого подсоединена к входу транзистора ключевого каскада, в ячейку введен каскад повторителя напряжеШ1Я, состоящий из нагрузочного резистора и транзистора, вход которого подсоединен между выходом транзистора и нагрузочного резистора ключевого каскада предыдущей ячейки, а между выходом транзистора и нагрузочньп резистором повторителя подсоединена другая обкладка конденсатора. На фиг. 1 представлена принципиальная электрическая схема однотиповой ячейки импульсной линии задержки; на фиг. 2 - экспериментальные временные диаграммы, снятые с экрана двухлучевого осциллографа. Импульсная линия задержки состоит из входного каскада, содержащего транзистор 1, нагрузочный, резистор 2 и резистор 3 в цепи смещения базы транзистора I по питанию .,, нескол ких однотипных задерживающих ячеек 4 и 5, каждая из которых состоит из каскада повторителя напряжения, содержащего транзистор 6 и нагрузочный резистор 7, накопительного конденсатора 8 и ключевого каскада, содержащего транзистор 9, нагрузочный резис тор 10 и резистор П в цепи смещения базы транзистора 9 по питанию. Линия задержки выполнена на биполярных тра зисторах п-р-п структуры, так как в силу известных технологических особенностей транзисторы современных ин тегральных схем имеют, как правило, структуру п-р-п типа. На фиг. 2 график I изображает вре менную диаграмму изменения напряжения Ugv(t) входного импульса, график 2 - временную диаграмму изменени напряжения (t) на выходе транзис тора 1, график 3 - временную диаграм му изменения напряжения U,r9(t) иа базе транзистора 9, график 4 - временную диаграмму изменения напряжения ) нэ выходе транзистора 9. В исходном состояшм транзисторы и 9 насыщены (открыты за счет токов протекающих в резисторах 3 и I, тра зистор 6 закрыт и конденсатор 8 разряжен. Входной импульс отрицательной полярности закрывает транзистор 1, в результате чего на вход транзистора поступает импульс положительной полярности с амплитудой л Ец. Транзистор 6 открывается и начинается заряд конденсатора 8 до напряжения Ъ чере вход насыщенного транзистора 9. При зтом транзистор 9 еще больше насыно состояние последующих ка щается, кадов линии не изменяется. По оконча нии входного импульса транзистор I возвращается в открытое состояние, а транзистор 6 - в закрытое состояние конденсатор 8 оказывается приложенным правой обкладкой, имеющей отрицательный потенциал, к входу транзистора 9 . В результате этого транзистор 9 закрывается и начинается разряд конденсатора 8 через резисторы 7 и 1I. В течение времени разряда конденсатора 8 транзистор 9 закрыт, что приводит к открыванию каскада повторителя напряжения и к заряду конденсатора следующей ячейки 5. Как только напряжение Ur (график 3) станет положительным, открывается транзистор 9 и заряженньй конденсатор ячейки 5 закроет каскад ключа этой ячейки. Далее процессы повторяются. В результате передний фронт входного импульса оказывается задержанным в каждой ячейке на время разряда конденсатора. Введение в. каждую времязадающую ячейку нового для ее схемы каскада повторителя напряжения подключение одной (левой на фиг. 1) из обкладок конденсатора к выходу повторителя выгодно отличает предлагаемую импульо- ную линию задержки от известного уст-, ройства, так как увеличивает время задержки каждой ячейки ((7 + R ) за счет значения резистора который не повышает существующие уровни нестабильности времени задержки (значения Cg и не увеличиваются) и энергопотребления (каскад повторителя в исходном состоянии закрыт) . Кроме того, стало возможным плавное регулирование времени задержки ячейки при использовании переменного резистора 7. Технико-эконо шческая эффективность данного устройства заключается в том, что при 4 ксации длительности задержки всей линии потребность в количестве ячеек уменьшается не менее чем в 2 раза, что соответственно приводит к уменьщению примерно в 2 раза энергопотребления. При этом общее количество транзисторов, резисторов и конденсаторов в линии остается неизменным, а значит.не изменится и стоимость предлагаемого устройства по сравнению с известным. Формула изобретения Импульсная линия задержки, со,стоящая из входного каскада и одно

| название | год | авторы | номер документа |

|---|---|---|---|

| Ячейка временной задержки импульсов | 1980 |

|

SU945967A1 |

| Дискретная линия задержки | 1982 |

|

SU1145470A1 |

| Многофазный генератор регулируемых временных интервалов | 1978 |

|

SU790206A1 |

| Устройство задержки | 1981 |

|

SU993473A1 |

| Формирователь импульсов | 1979 |

|

SU843200A2 |

| Устройство с временной автоматической регулировкой усиления | 1989 |

|

SU1778908A1 |

| Устройство задержки аналоговыхСигНАлОВ | 1979 |

|

SU849424A1 |

| Одновибратор | 1975 |

|

SU552675A1 |

| УСТРОЙСТВО ЗАДЕРЖКИ | 1972 |

|

SU347905A1 |

| Кольцевое пересчетное устройство | 1983 |

|

SU1100731A1 |

Авторы

Даты

1981-09-23—Публикация

1979-12-29—Подача