О

со о

Изобретение относится к радиотехнике и может быть использовано в устройствах частотной селекции.

Цель изобретения - расширение динамического диапазона и уменьшение паразитной модуляции выходного напряжения.

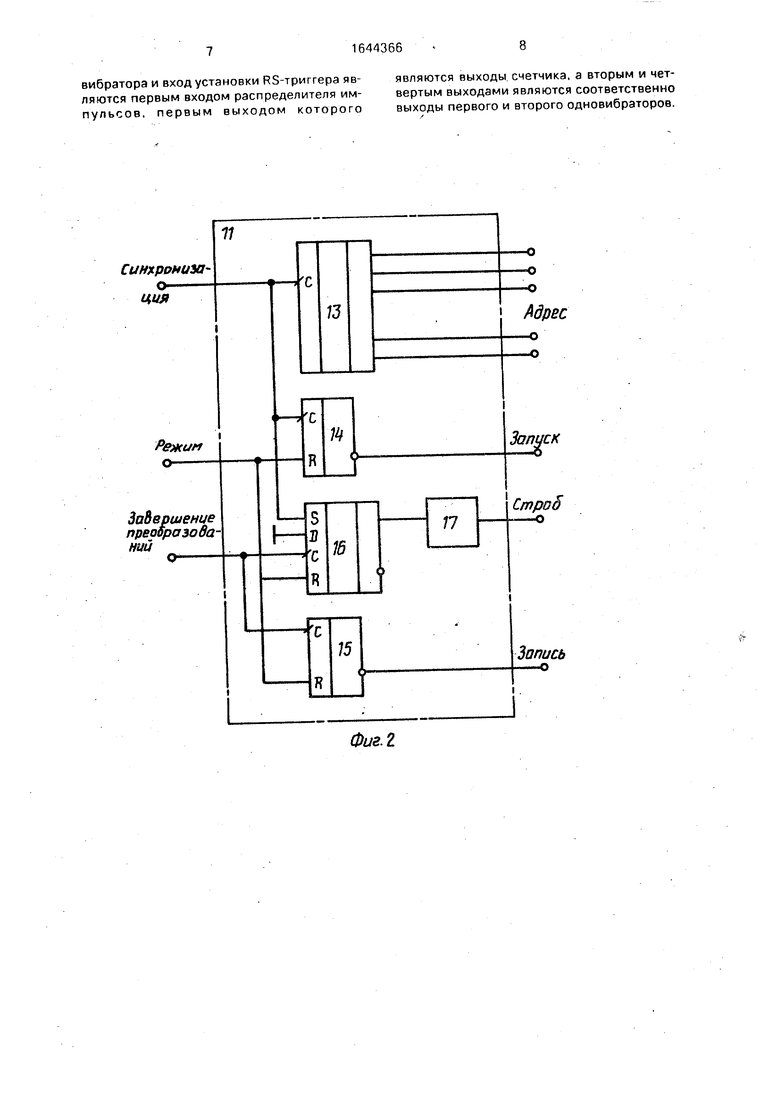

На фиг.1 приведена структурная схема синхронного фильтра; на фнг.2 - схема распределителя импульсов; на фиг.З - эпюры напряжений в характерных точках синхронного фильтра.

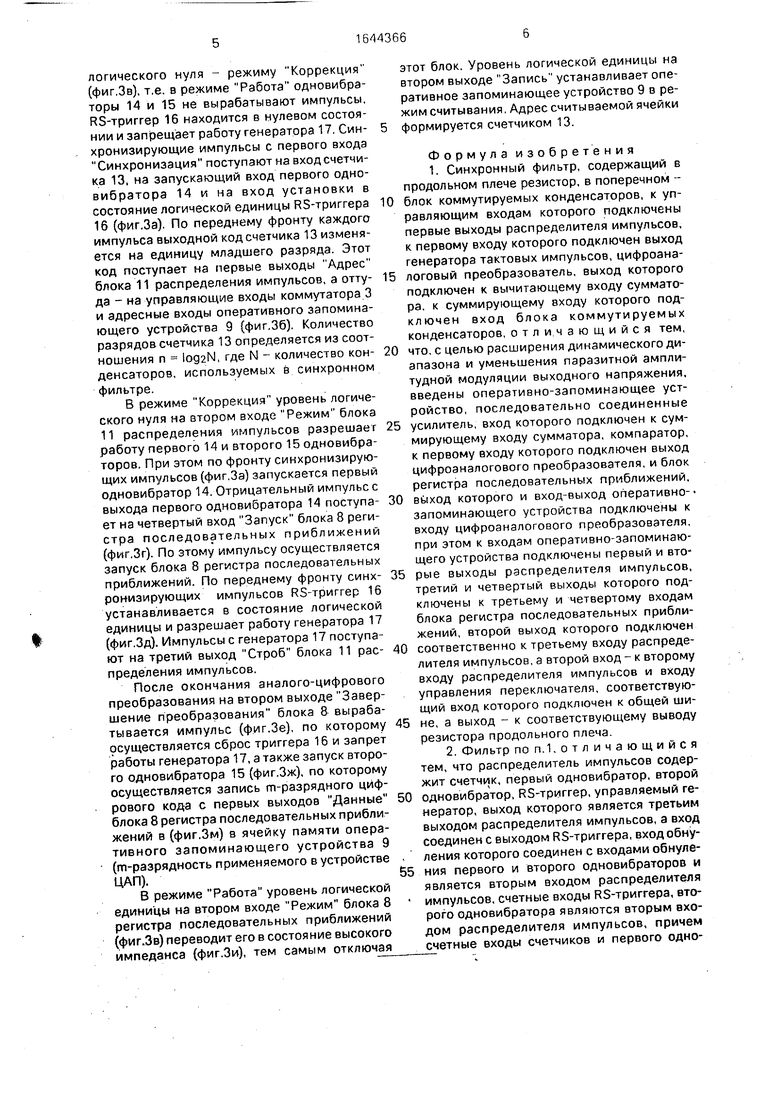

Синхронный фильтр содержит переключатель 1, резистор 2, блок коммутируемых конденсаторов из коммутатора 3 и N конденсаторов 4, сумматор 5, усилитель 6, компаратор 7, блок 8 регистра последовательных приближений, оперативное запоминающее устройство 9, цифроаналоговый преобразователь 10, распределитель 11 импульсов, тактовый генератор 12, а распределитель 11 импульсов содержит счетчик 13, первый одновибратор 14, второй одновиб- ратор 15, RS-триггер 16 и генератор 17.

Синхронный фильтр работает следующим образом.

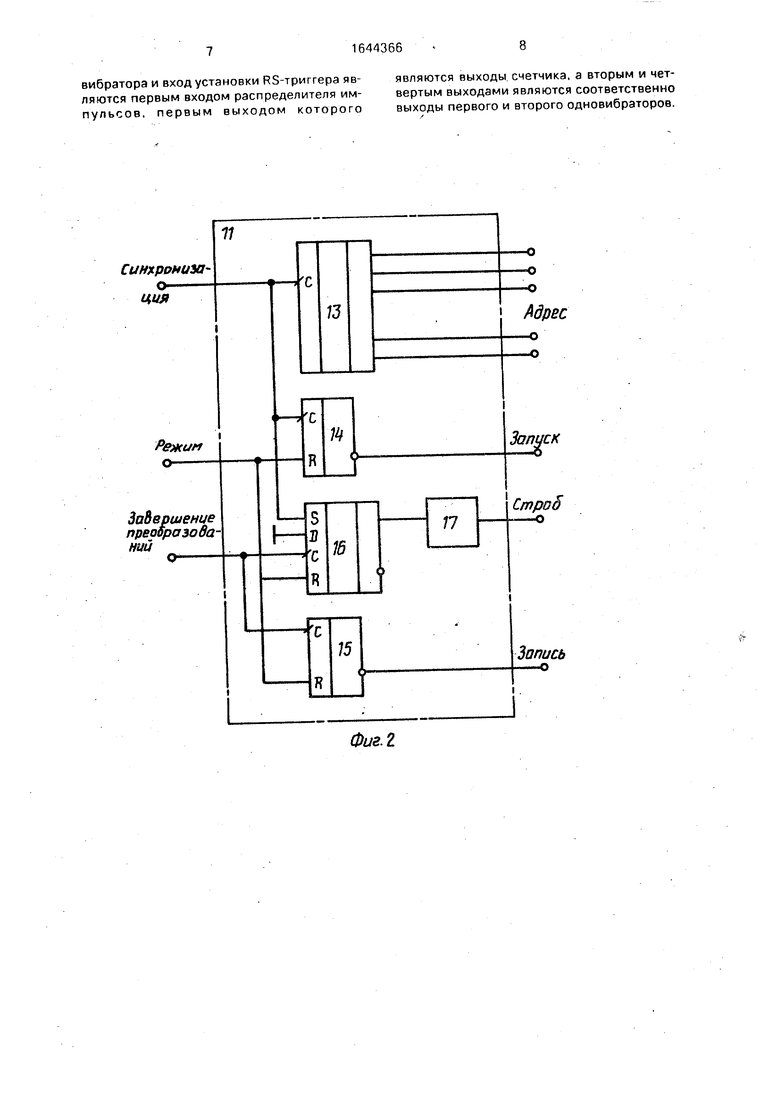

На первый вход распределителя 11 импульсов поступают импульсы с тактового генератора 12 частотой f0 (фиг.За). Синх- ронный фильтр имеет два режима Коррекция и Работа. Выбор режима осуществляется сигналом по входу управления режимом работы (вход Режим, фиг.Зв).

В режиме Коррекция (временной интервал ti - 15, фиг.З) переключатель 1 подключает резистор 2 к общей шине питания. При поступлении на коммутатор 3 с первых выходов распределителя 11 импульсов (выход Адрес, фиг.36) цифрового кода конденсаторы 4i 4к последовательно

подключаются через коммутатор 3 к резистору 2. Конденсаторы 4i4м заряжаются

до уровня помех на соответствующих выходах коммутатора 3 (фиг.Зк). Эти уровни синх- ронно с импульсами синхронизации появляются на выходе коммутатора 3.

Сигнал помехи подается на вход усилителя 6. Усиленный сигнал помехи поступает на второй вход компаратора 7. Компаратор 7, блок 8 регистра последовательных приближений и цифроаналоговый преобразователь 10 образуют аналого-цифровой преобразователь последовательных приближений, работающих под управлением распределителя 11 импульсов. В каждом такте (временные интервалы ti - 13; 13 - 14; и - te, фиг.З) на первых выходах Данные блока регистра последовательных приближений 8 формируется m-разрядный цифровой код, соответствующий аналоговому сигналу на выходе усилителя 6 и пропорциональный

сигналу помехи в этом такте (фиг Зи, временной интервал ta - ta). Сигнал на втором выходе Завершение преобразования (фиг.Зе) блока 8 регистра последовательных приближений свидетельствует об окончании аналого-цифрового преобразования, после чего цифровой код записывается в соответствующую ячейку оперативного запоминающего устройства

0 9. Адрес ячейки формируется распределителем 11 импульсов на первых выходах Адрес (фиг.36). Импульс записи формируется на втором выходе Запись (фиг.Зж) распределителя 11 импульсов после окончания

5 аналого-цифрового преобразования.

Таким образом, в режиме Коррекция в оперативном запоминающем устройстве 9 формируется цифровой эквивалент сигнала помехи управления, воздействующей на

0 конденсаторы 4ч4ы.

В режиме Работа вход синхронного фильтра подключается через переключатель 1 к резистору 2, и, в соответствии с импульсами синхронизации, конденсаторы

5 4i, ..., 4м заряжаются до уровня значений входного сигнала, который воздействует в данный момент времени через резистор 2 и

переключатель 1 на конденсаторы 4i4м.

В этом режиме оперативное запоминающее

0 устройство 9 работает в режиме считывания. Цифровые коды помех, записанные в режиме Коррекция, с выхода оперативного запоминающего устройства 9 подаются на цифровые входы цифроанзлогового пре5 образователя 10, который преобразует их в аналоговый вид.

В режиме Работа первые выходы Данные блока 8 регистра последовательных приближений находятся в высокоимпе0 дансном состоянии и не оказывают влияния на процесс передачи цифровых кодов из оперативного запоминающего устройства 9 на вход цифроаналогового преобразователя. Сигнал помехи с аналогового выхода

5 блока цифроаналогового преобразователя 10 подается на вычитающий вход сумматора 5, на суммирующий вход которого подается смесь сигнала и помехи управления. Коэффициент передачи по инвертирующему вхо0 ду сумматора 5 устанавливается таким, чтобы общий коэффициент передачи и компенсации помехи управления (усилитель 6, компаратор 7, блок 8 последовательных приближений ОЗУ 9, ЦАП 10) был равен еди5 нице.

Блок 11 распределения импульсов работает следующим образом (фиг.2). Уровень логической единицы на втором входе Режим блока 11 распределения импульсов соответствует режиму Работа, а уровень

логического нуля - режиму Коррекция (фиг.Зв), т.е. в режиме Работа одновибра- торы 14 и 15 не вырабатывают импульсы, RS-триггер 16 находится в нулевом состоянии и запрещает работу генератора 17. Синхронизирующие импульсы с первого входа Синхронизация поступают на вход счетчика 13, на запускающий вход первого одно- вибратора 14 и на вход установки в состояние логической единицы RS-триггера 16 (фиг.За). По переднему фронту каждого импульса выходной код счетчика 13 изменяется на единицу младшего разряда. Этот код поступает на первые выходы Адрес блока 11 распределения импульсов, а оттуда - на управляющие входы коммутатора 3 и адресные входы оперативного запоминающего устройства 9 (фиг.Зб). Количество разрядов счетчика 13 определяется из соотношения n log2N, где N - количество конденсаторов, используемых в синхронном фильтре.

В режиме Коррекция уровень логического нуля на втором входе Режим блока 11 распределения импульсов разрешает работу первого 14 и второго 15 одновибра- торов. При этом по фронту синхронизирующих импульсов (фиг.За) запускается первый одновибратор 14. Отрицательный импульс с выхода первого одновибратора 14 поступает на четвертый вход Запуск блока 8 регистра последовательных приближений (фиг.Зг). По этому импульсу осуществляется запуск блока 8 регистра последовательных приближений. По переднему фронту синхронизирующих импульсов RS-триггер 16 устанавливается в состояние логической единицы и разрешает работу генератора 17 (фиг.Зд). Импульсы с генератора 17 поступают на третий выход Строб блока 11 распределения импульсов.

После окончания аналого-цифрового преобразования на втором выходе Завершение преобразования блока & вырабатывается импульс (фиг.Зе), по которому осуществляется сброс триггера 16 и запрет работы генератора 17, а также запуск второго одновибратора 15 (фиг.Зж), по которому осуществляется запись m-разрядного цифрового кода с первых выходов Данные блока 8 регистра последовательных приближений в (фиг.Зм) в ячейку памяти оперативного запоминающего устройства 9 (m-разрядность применяемого в устройстве ЦАП).

В режиме Работа уровень логической единицы на втором входе Режим блока 8 регистра последовательных приближений (фиг.Зв) переводит его в состояние высокого импеданса (фиг.Зи), тем самым отключая

этот блок. Уровень логической единицы на втором выходе Запись устанавливает оперативное запоминающее устройство 9 в режим считывания. Адрес считываемой ячейки формируется счетчиком 13.

Формула изобретения

1.Синхронный фильтр, содержащий в продольном плече резистор, в поперечном -блок коммутируемых конденсаторов, к управляющим входам которого подключены первые выходы распределителя импульсов, к первому входу которого подключен выход генератора тактовых импульсов, цифроаналоговый преобразователь, выход которого подключен к вычитающему входу сумматора, к суммирующему входу которого подключен вход блока коммутируемых конденсаторов, отличающийся тем,

что, с целью расширения динамического диапазона и уменьшения паразитной амплитудной модуляции выходного напряжения, введены оперативно-запоминающее устройство, последовательно соединенные

усилитель, вход которого подключен к суммирующему входу сумматора, компаратор, к первому входу которого подключен выход цифроанэлогового преобразователя, и блок регистра последовательных приближений,

которого и вход-выход оперативно-- запоминающего устройства подключены к входу цифроаналогового преобразователя, при этом к входам оперативно-запоминающего устройства подключены первый и вто

рые выходы распределителя импульсов, третий и четвертый выходы которого подключены к третьему и четвертому входам блока регистра последовательных приближений, второй выход которого подключен

соответственно к третьему входу распределителя импульсов, а второй вход - к второму входу распределителя импульсов и входу управления переключателя, соответствующий вход которого подключен к общей шине, а выход - к соответствующему выводу резистора продольного плеча.

2.Фильтр по п.1. о т л ичающийся тем, что распределитель импульсов содержит счетчик, первый одновибратор, второй

одновибратор, RS-триггер, управляемый генератор, выход которого является третьим выходом распределителя импульсов, а вход соединен с выходом RS-триггера, вход обнуления которого соединен с входами обнуления первого и второго одновибраторов и является вторым входом распределителя импульсов, счетные входы RS-триггера, второго одновибратора являются вторым входом распределителя импульсов, причем счетные входы счетчиков и первого одновибратора и вход установки RS-триггера являются первым входом распределителя импульсов, первым выходом которого

являются выходы счетчика, а вторым и четвертым выходами являются соответственно выходы первого и второго одновибраторов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифроаналоговый преобразователь с автоматической коррекцией нелинейности | 1988 |

|

SU1594699A1 |

| Цифровой регистратор | 1984 |

|

SU1164549A1 |

| Устройство для управления @ -фазным вентильным преобразователем | 1989 |

|

SU1721756A1 |

| Устройство для электронно-лучевой сварки | 1987 |

|

SU1796379A1 |

| Режекторный фильтр | 1987 |

|

SU1429293A2 |

| Устройство для вибросейсморазведки | 1987 |

|

SU1444687A1 |

| Передающее устройство радиотелеметрической установки | 1984 |

|

SU1250853A1 |

| Цифроаналоговый преобразователь | 1989 |

|

SU1735999A1 |

| Устройство для измерения аналоговых величин с автоматическим масштабированием | 1986 |

|

SU1406792A1 |

| ОПЕРАТИВНЫЙ КОНТРОЛЛЕР СУММАРНОЙ МОЩНОСТИ НАГРУЗКИ ГРУППЫ ЭНЕРГОПОТРЕБИТЕЛЕЙ | 1998 |

|

RU2145717C1 |

Изобретение относится к радиотехнике и может быть использовано в устройствах частотной селекции. Цель изобретения - расширение динамического диапазона и уменьшение паразитной модуляции выходного напряжения. Синхронный фильтр содержит переключатель 1, резистор 2, блок коммутируемых конденсаторов, состоящий из коммутатора 3 и N конденсаторов 4, сумматор 5, усилитель 6, компаратор 7, блок 8 регистра последовательных приближений, оперативное запоминающее устройство 9, цифроаналоговый преобразователь 10, распределитель 11 импульсов и тактовый генератор 12В режиме, когда вход синхронного фильтра через переключатель 1 соединен с землей, происходит запись напряжений помехи в оперативное запоминающее устройство 9 Эти сигналы в режиме Работа, пройдя через аналогово-цифровой преобразователь 10, вычитаются из смеси сигнала с помехой в сумматоре 5. Фильтр по п.2 ф-лы отличается выполнением распределителя 11.1 з.п, ф-лы, 3 ил Ё

Фиг. 2

1

±2 Ь

W3

| Синхронный фильтр | 1973 |

|

SU455454A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1991-04-23—Публикация

1988-07-05—Подача