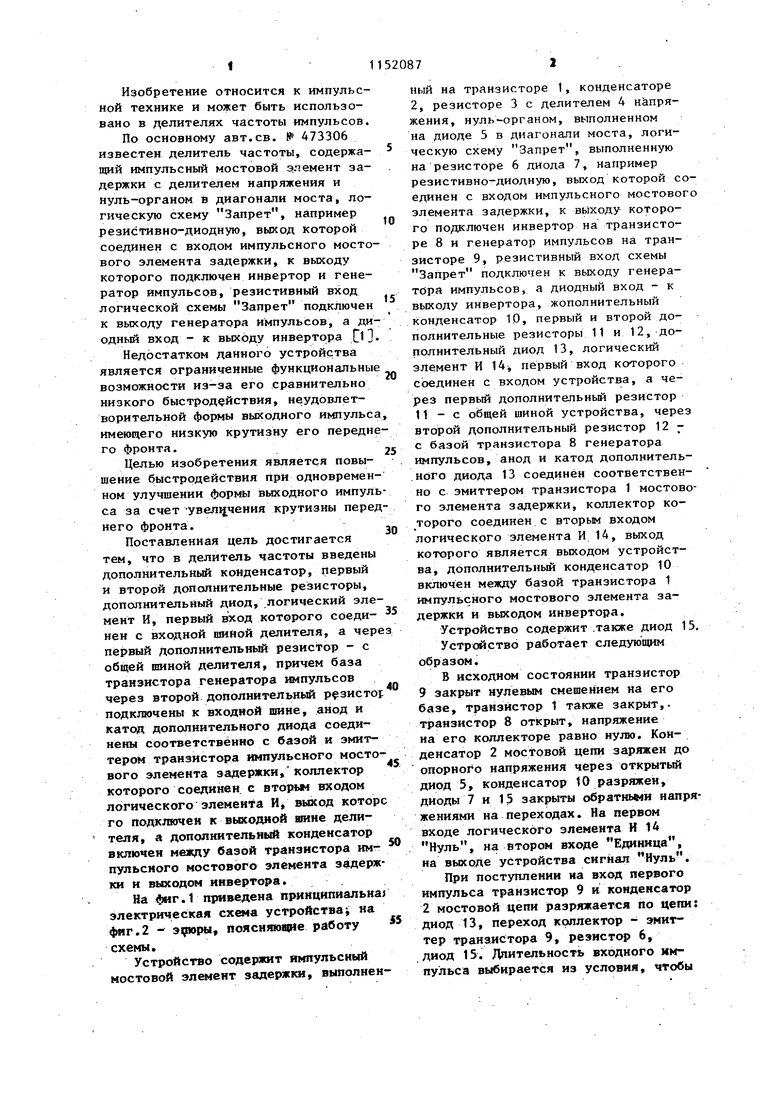

Изобретение относится к импульсной технике и может быть использовано в делителях частоты импульсов. По основному авт.ев, № 473306 известен делитель частоты, содержа щий импульсный мостовой элемент задержки с делителем напряжения и нуль-органом в диагонали моста, логическую схему Запрет, например резистивно-диодную, выход которой соединен с входом импульсного мосто вого элемента задержки, к выходу которого подключен инвертор и генератор импульсов, резистивный вход логической схемы Запрет подключен к выходу генератора импульсов, а ди одный вход - к выходу инвертора СО Недостатком данного устройства является ограниченные функциональны возможности из-за его сравнительно низкого быстродействия, неудовлетворительной формы выходного импульс имеющего низкую крутизну его передн го фронта. Целью изобретения является повышение быстродействия при одновремен ном улучшении формы выходного импул са за счет -увеш чения крутизны пере него фронта. Поставленная цель достигается тем, что в делитель частоты введены дополнительный конденсатор, первый и второй дополнительные резисторы, дополнительный диод, .логический эле мент И, первый вход которого соединей с входной шиной делителя, а чер первый дополнительный резистор - с общей шиной делителя, причем база транзистора генератора импульсов через второй дополнительньй резисто подключены к входной шине, анод и катод дополнительного диода соединены соответственно с базой и эмиттером транзистора импульсного мосто вого элемента задержки, коллектор которого соединен с вторым входом логического элемента И выход котор го подк ночей к выходной шине делителя, я дополнительный конденсатор включен между базой транзистора им пульсного мостового элемента эадерж ки и выходом инвертора. . На фиг.1 приведена принципиальна электрическая схема устройства на .2 - эфоры, поясняющие работу схемы. Устройство содержит импульсный мостовой элемент задержки, выполнен ный на транзисторе 1, конденсаторе 2, резисторе 3 с делителем 4 напряжения, нуль-органом, выполненном на диоде 5 в диагонали моста, логическую схему Запрет, выполненную на резисторе 6 диода 7, например резистивно-диодную, выход которой соединен с входом импульсного мостового элемента задержки, к выходу которого подключен инвертор на транзисторе 8 и генератор импульсов на транзисторе 9, резистивный вход схемы Запрет подключен к выходу генератора импульсов, а диодный вход - к выходу инвертора, жополнительный конденсатор 10, первый и второй дополнительные резисторы 11 и 12, дополнительный диод 13, логический элемент И 14 первый вход которого соединен с входом устройства, а через первый дополнительный резистор 11 - с общей шиной устройства, через второй дополнительный резистор 12 с базой транзистора 8 генератора импульсов, анод и катод дополнительного диода 13 соединён соответственно с эмиттером транзистора 1 мостового элемента задержки, коллектор которого соединен с вторым входом логического элемента И 14, выход которого является вькодом устройства, дополнительный конденсатор 10 включен между базой транзистора 1 импульсного мостового элемента задержки и выходом инвертора. Устройство содержит .также диод 15, Устройство работает следующим образом. В исходном состоянии транзистор 9 закрыт нулевым смещением на его базе, транзистор 1 также закрыт,, транзистор 8 открыт, напряжение на его коллекторе равно нулю. Конденсатор 2 мостовой цепи заряжен до опорного напряжения через открытый диод 5, конденсатор tО разряжен, диоды 7 и 15 закрыты обратньми напряжениями на переходах. На первом входе логического элемента И ТА Нуль, на втором входе Единица, на выходе устройства сигнал Нуль. При поступлении на вход первого импульса транзистор 9 и конденсатор 2 мостовой цепи разряжается по цепн: диод 13, переход коллектор - эмиттер транзистора 9, резистор 6, диод 15. Длительность входного импульса выбирается из условия, чтобы

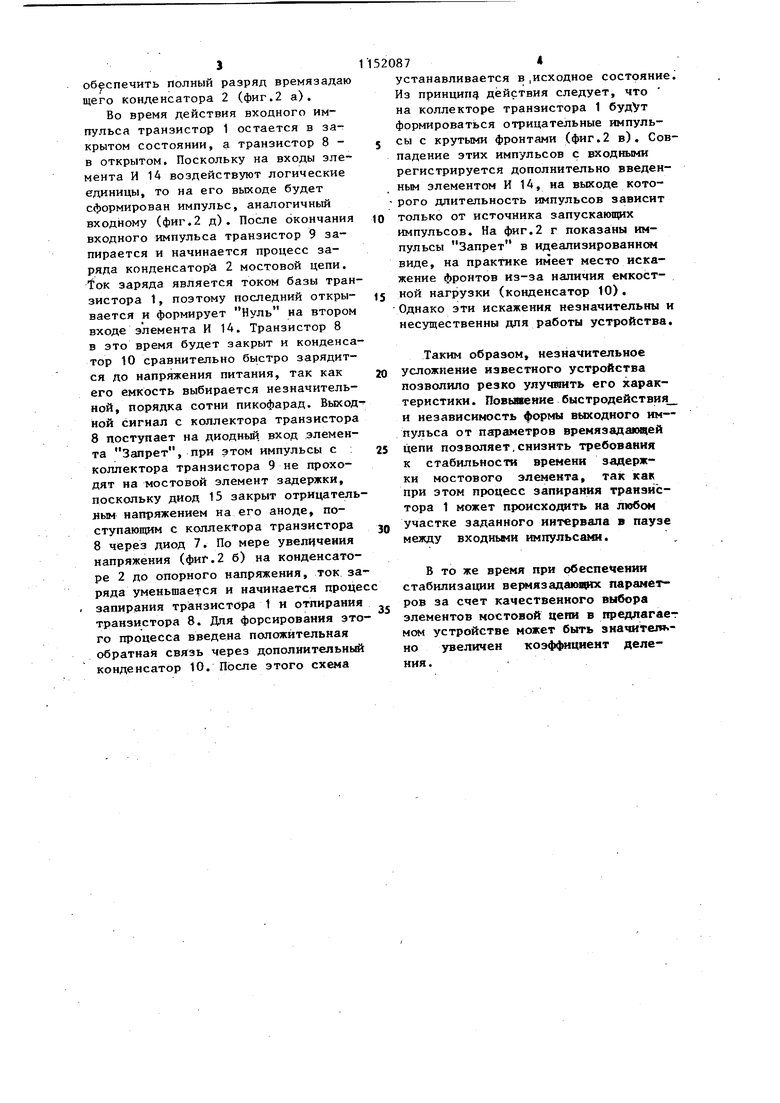

обеспечить полный разряд времязадаю щего конденсатора 2 (фиг.2 а).

Во время действия входного импульса транзистор 1 остается в закрытом состоянии, а транзистор 8 в открытом. Поскольку на входы элемента И 14 воздействуют логические единицы, то на его выходе будет сформирован импульс, аналогичный входному (фиг.2 д). После окончания входного импульса транзистор 9 запирается и начинается процесс заряда конденсатора 2 мостовой цепи. loK заряда является током базы транзистора 1, поэтому последний открывается и формирует Нуль на втором входе элемента И 14. Транзистор 8 в это время будет закрыт и конденсатор 10 сравнительно быстро зарядится до напряжения питания, так как его емкость выбирается незначительной, порядка сотни пикофарад. Выходной сигнал с коллектора транзистора 8 поступает на диодный, вход элемента Запрет, при этом импульсы с коллектора транзистора 9 не проходят на мостовой элемент задержки, поскольку диод 15 закрыт отрицательным напряжением на его аноде, поступающим с коллектора транзистора 8 через диод 7. По мере увеличения напряжения (фиг.2 б) на конденсаторе 2 до опорного напряжения, ток заряда уменьшается и начинается проце запирания транзистора 1 и отпирания транзистора 8. Для форсирования этого процесса введена положительная обратная связь через дополкительньй конденсатор 10. После этого схема

устанавливается в .исходное состояние Из принципу действия следует, что на коллекторе транзистора 1 будУт формироваться отрицательные импульсы с крутыми фронтами (фиг.2 в). Совпадение этих импульсов с входными регистрируется дополнительно введенным элементом И 14, на выходе которого длительность импульсов зависит только от источника запускающих импульсов. На фиг.2 г показаны импульсы Запрет в идеализированном виде, на практике имеет место искажение фронтов из-за наличия емкостной нагрузки (конденсатор 10). Однако эти искажения незначительны и несущественны для работы устройства

Таким образом, незначительное усложнение известного устройства позволило резко улучшить его характеристики . Повьагенне быстродействия и независимость формы выходного импульса от параметров времязадакмцей цепи позволяет,снизить требования к стабильности времени задержки мостового элемента, так как при этом процесс запирания транзистора 1 может происходить на любом участке заданного интервала в паузе между входными импульсами.

В то же время при обеспечении стабилизации ве| |язадаю||0{х параметров за счет качественного выбора элементов мостовой цепи в предлагает мом устройстве может быть значительно увеличен коэффициент деления.

Q

U LTU TTU U

| название | год | авторы | номер документа |

|---|---|---|---|

| Функциональный преобразователь угловых перемещений | 1982 |

|

SU1043679A1 |

| ИМПУЛЬСНЫЙ СТАБИЛИЗАТОР ПОСТОЯННОГО НАПРЯЖЕНИЯ ПОНИЖАЮЩЕГО ТИПА | 1991 |

|

RU2006062C1 |

| Стабилизированный инвертор | 1981 |

|

SU964908A1 |

| Делитель частоты | 1973 |

|

SU473306A1 |

| Стабилизированный выпрямитель | 1990 |

|

SU1781797A1 |

| Переключатель переменного тока | 1986 |

|

SU1354410A1 |

| Стабилизированный источник питания | 1986 |

|

SU1390736A1 |

| Ключевое устройство | 2019 |

|

RU2749278C1 |

| ИМПУЛЬСНЫЙ СТАБИЛИЗАТОР НАПРЯЖЕНИЯ | 2001 |

|

RU2216765C2 |

| Импульсный понижающий стабилизатор постоянного напряжения | 1990 |

|

SU1786477A1 |

ДЕЛИТГЛ. ЧАСТОТЫ по авт. св. № 473306, отличающийс я тем, что, с целью повышения быстродействия при одновременном улучшении формы выходного сигнала за счет увеличения крутизны переднего фронта, в него введены дополнительный конденсатор, первый и второй дополнительные резисторы, дополнительный диод и логический элемент И, первый вход которого соединен с входной шиной делителя, а через первый дополнительный резистор с общей шиной делителя, причем база транзистора генератора импульсов через второй дополнительньй резистор подключена к входной шине, анод и катод дополнитель}юго диода соединены соответственно с базой и эмиттером транзистора импульсного мостового элемента задержки, коллектор которого соединен с вторым входом логического элемента И, выход которого подключен к выходной шине дели(Л теля, а дополнительный конденсатор включен между базой транзистора импульсного мостового элемента задержки и выходом инвертора.

-Eon - 8

Фиг 2

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Делитель частоты | 1973 |

|

SU473306A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1985-04-23—Публикация

1983-08-05—Подача