}23

UflufrJioeuvecxujr элементов

Фе/е. f

pa, резистивный делитель, включенный между выходным выводом и общей шиной, а выходом подключенный к инвертирующему входу компаратора, неинвертирующий вход которого соединен с выходом источника опорного напряжения, DLC-фильтр, конденсатор которого включен между выходным выводом и общей шиной, и входной вывод, отличающийся тем, что, с целью снижения нижнего предела входного напряжения, в него введены третий и четвертый транзисторы p-n-p-типа и пятый транзистор n-p-n-типа, первый, второй, третий и четвертый резисторы, диод, второй логический элемент 2И, первая и вторая интегрирующие RC-цепи, логический элемент 2ИЛИ, инвертор, логический элемент 2И-НЕ, второй RS-триггер, первый и второй буферные элементы с открытыми коллекторными выходами, причем эмиттеры третьего и четвертого транзисторов соединены с входным выводом, коллектор третьего транзистора подключен к входу DLC-фильтра, база третьего транзистора подключена к токозадающей цепи и к коллектору четвертого транзистора, между точкой соединения эмиттеров третьего и четвертого транзисторов и коллектором пятого транзистора включены последовательно соединенные первый и второй резисторы, общая точка которых соединена с базой четвертого транзистора, эмиттер

второго транзистора подключен к общей шине, к которой через диод подключен и эмиттер пятого транзистора, база которого соединена с коллектором первого стора, а через третий резистор - с выводом для подключения источника вспомогатель- ного питания, первая интегрирующая RC- цепь входом подключена к выхбду генератора, а выходом - к первому входу логического элемента 2ИЛИ, второй вход которого соединен с выходом компаратора, второй логический элемент 2И входами подключен к выходам генератора и логического элемента 2ИЛИ, а выходом - к инверсному входу R первого RS-триггера, , коллектор второго транзистора подключен к одному из входов логического элемента 2И-НЕ и к инверсному входу R второго RS-триггера через последовательно соединенные инвертор и вторую интегрирующую RC-цепь - к его Другому входу, а через четвертый резистор - к выводу для подключения источника питания логических элементов, выход логического элемента 2И-НЕ соединен с инверсным ахо- дом S второго RS-триггера, входы буферных элементов, выполненных с инверсией или без инверсии, подключены соответственно к прямому или инверсному выходам второго RS-триггера, а выходы указанных первого и второго буферных элементов подключены соответственно к выходу резистивного делителя и к базе пятого транзистора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Источник вторичного электропитания для сети постоянного напряжения | 1990 |

|

SU1786476A1 |

| ИМПУЛЬСНЫЙ СТАБИЛИЗАТОР ПОСТОЯННОГО НАПРЯЖЕНИЯ ПОНИЖАЮЩЕГО ТИПА | 1991 |

|

RU2006062C1 |

| СТАБИЛИЗАТОР ПОСТОЯННОГО НАПРЯЖЕНИЯ С ИМПУЛЬСНЫМ РЕГУЛИРОВАНИЕМ | 1991 |

|

RU2014646C1 |

| Устройство для определения междуфазных замыканий и замыканий на землю в сетях с изолированной нейтралью напряжением 6-10 кВ | 2022 |

|

RU2788035C1 |

| ДВУХТАКТНЫЙ ТРАНЗИСТОРНЫЙ ИНВЕРТОР | 1993 |

|

RU2046527C1 |

| Электронная приставка к транзисторной системе зажигания | 1991 |

|

SU1800086A1 |

| ПРЕОБРАЗОВАТЕЛЬ ИНЕРЦИАЛЬНОЙ ИНФОРМАЦИИ | 2006 |

|

RU2325620C2 |

| СТАБИЛИЗАТОР ИМПУЛЬСНОЙ МОЩНОСТИ ИЗЛУЧЕНИЯ ДИОДНОГО ЛАЗЕРА | 1995 |

|

RU2103810C1 |

| УСТРОЙСТВО ДЛЯ ЗАЩИТЫ ИНТЕГРАЛЬНЫХ МИКРОСХЕМ ПРИ ПОПАДАНИИ В НИХ ТЯЖЕЛЫХ ЗАРЯЖЕННЫХ ЧАСТИЦ | 2005 |

|

RU2305894C2 |

| Преобразователь постоянного напряжения | 1990 |

|

SU1778900A1 |

Изобретение относится к электротехнике, конкретно - к источникам вторичного электропитания с импульсным регулированием для радиоэлектронных средств.

Наиболее предпочтительная область использования - устройства вычислительной техники и аппаратура, работающие от батареи (аккумулятора) при предъявлении к ним повышенных требований в отношении массо-габаритных характеристик и КПД.

Отставание техники электропитания радиоэлектронной, аппаратуры в части микроминиатюризации относительно общего уровня аппаратуры в значительной мере преодолевается применением микросхем в качестве схем управления стабилизаторами напряжения, разработанных с учетом специфики источников вторичного электропитания.

Известен стабилизатор постоянного на- пряжения, работающий в режиме широтно- импульсной модуляции, содержащий регулирующий транзистор, LCD-фильтр и

схему управления, основу которой составляет микросхема К142ЕП1 - см., например, Справочник Микросхемы для бытовой аппаратуры, М.: Радио и связь, 1989, с.50. Эта микросхема (см. с.48 указанной книги) содержит дифференциальный усилитель, формирователь пилообразного напряжения, работающий с внешней емкостью от внешнего генератора прямоугольного напрйже- ния, широтно-импульсный модулятор, согласующие транзисторы и источник ohop- ного напряжения. Выход широтно-импульс- ного модулятора связан с базой первого согласующего транзистора, эмиттер второго согласующего транзистора подключён к общему проводу схемы, а коллекторы офоих согласующих транзисторов через промежуточный транзистор связаны с базой регулирующего транзистора. Дифференциальный усилитель сравнивает выходное ние с опорным, а широтно-импульсный модулятор выдает импульсы, скважнбсть которых пропорциональна разности между

входным и выходным напряжением стабилизатора при определенном токе нагрузки.

Недостатком стабилизатора является то, что он способен работать лишь при входных напряжениях 10...40 В, что определяется схемотехникой источника опорного напряжения, подключаемого к первичной сети непосредственно. Тем не менее, в технике электропитания радиоэлектронной аппаратуры часто возникает потребность в получении сравнительно низких напряжений (наиболее частот 5 В) при уровнях входного напряжения, максимально приближающихся к требуемым выходным. К недостаткам микросхемы К142ЕП1 относятся также большое количество внешних навесных элементов и необходимость подключения к ней внешнего источника напряжения модуляции, к тому же изолированного.

Наиболее близок к предлагаемому импульсный понижающий стабилизатор постоянного напряжения, содержащий генератор, компаратор, первый логический элемент 2И, входы которого подключены к выходам генератора и компаратора, первый RS-триггер, вход S которого соединен с выходом первого логического элемента 2И, первый транзистор n-p-n-типа, база которого подключена к выходу первого RS-триг- гера, второй транзистор n-p-n-типа, базой соединенный с эмиттером первого транзистора, резистивный делитель, включенный между выходным выводом и общей шиной, а выходом подключенный к инвертирующему входу компаратора, неинвертирующий вход которого соединен с выходом источника опорного напряжения, DLC-фильтр, конденсатор которого включен между выходным выводом и общей шиной, и входной вывод - универсальная подсистема для построения импульсных источников питания фирмы Fairchild (микросхема / A78S40): см. Фолкенберри Л, Применение операционных усилителей и линейных ИС, М.:Мир, 1985, § 10.3.3 на с.311...320. У микросхемы /и A78S40 появился отечественный аналог КР1156ЕУ1, выпускаемый Брянским ПО Кремний.

В понижающем стабилизаторе постоянного напряжения с.315 книги Л.Фолкенберри, рис.10.17а, коллекторы обоих выходных транзисторов соединены между собой и подключены вместе с выводом питания микросхемы к входу, а между эмиттером второго выходного транзистора и выходом устройства включен дроссель, который вместе с конденсатором и внутренним диодом микросхемы образует DLC-фильтр. В схеме управления выход осциллятора и инверсный вход R RS-триггера соединены между собой.

Схема 2И выполняет функцию конъюнкции напряжения осциллятора и компаратора и управляет RS-триггером по S-входу, в то время как R-вход этого триггера обслуживается непосредственно с выхода осциллятора. Силовой ключ открывается всякий раз после установки триггера в единичное со0 стояние от выходного сигнала логического элемента 2И. Закрывается силовой ключ по окончании импульса осциллятора, когда происходит релаксация, занимающая 1/8 часть периода работы широтно-импульсно5 го модулятора -его естественная пауза - см. с.312 книги Л.Фолкенберри.

Отсюда происходит недостаток микросхемы {I A78S40 (КР1156ЕУ1), заключающийся в том, что стабилизация срывается

0 при понижении напряжения первичной сети до величины Unp, равной сумме выходного напряжения и остаточного напряжения, которое может достигать 2,8 В. Столь значительная величина остаточного напряжения

5 объясняется, во-первых, включением выходных транзисторов по схеме Дарлингтона, что было вызвано необходимостью сопряжения управляющего входа силового ключа с триггером, а во-вторых, наличием естест0 венной паузы модулятора, а значит и ключа. Из-за этого недостатка сбои в работе питаемой аппаратуры происходят, если напряжение первичной сети претерпевает провал, входящий в зону остаточного напря5 жения. С другой стороны, если напряжение первичной сети снижается (разряд батареи), доходит до названной зоны, выходное напряжение становится нестабилизированным и также падает. Аппаратура

0 преждевременно теряет работоспособность.

Целью изобретения является снижение нижнего предела входного напряжения (при котором сохраняется стабилизация выход5 ного напряжения).

Поставленная цель -достигается благодаря тому, что в импульсном понижающем стабилизаторе постоянного напряжения, содержащем генератор, компаратор, пер0 вый логический элемент 2И, входы которого подключены к выходам генератора и компаратора, первый RS-триггер, вход S которого соединен с выходом первого логического элемента 2И, первый транзистор п-р-п-ти5 па, база которого подключена к выходу первого RS-триггера, второй .транзистор n-p-ri-типа, базой соединенный с эмиттером первого транзистора, резистивный делитель, включенный между выходным выводом и общей шиной, а выходом подключенный к инвертирующему входу компаратора, неинвертирующий вход которого соединен с выходим источника опорного напряжения, DLC-фйльтр, конденсатор которого включен между выходным выводом и общей шиной, и входной вывод, введены третий и четвертый транзисторы р-п-р-тйпа и пятый транзистор n-p-n-типа, первый, второй, третий и четвертый резисторы, диод, второй логический элемент 2И, первая и вторая интегрирующие RC-цепи, логический элемент 2ИЛИ, инвертор, логический элемент 2И-НЕ, второй RS-триггер, первый и второй буферные элементы с открытыми коллекторными выходами, причем эмиттеры третьего и четвертого транзисторов соединены с входным выводом, коллектор третьего транзистора подключен к входу DLC-фильтра, база третьего транзистора подключена к токозадающей цепи и к коллектору четвертого транзистора, между точкой соединения эмиттеров третьего и четвертого транзисторов и коллектором пятого транзистора включены последовательно соединенные первый и второй резисторы, общая точка которых соединена с базой четвертого транзистора, эмиттер второго транзистора подключен к общей шине, к которой через диод подключен и эмиттер пятого транзистора, база которого соединена с коллектором первого транзистора, а через третий резистор - с выводом для подключения источника вспомогательного питания, первая интегрирующая RC- цепь входом подключена к выходу генератора, а выходом - к первому входу логического элемента 2ИЛИ, второй вход которого соединен с выходом компаратора, второй логический элемент 2И входами подключен к выходам генератора и логического элемента 2ИЛИ, а выходом - к инверсному входу R первого RS-триггера, коллектор второго транзистора подключен к одному из входов логического элемента 2И.-НЕ и к инверсному входу R второго RS-триггера через последовательно соединенные инвертор и вторую интегрирующую RC-цепь - к его другому входу, а через четвертый резистор - к выводу для подключения источника питания логических элементов, выход логического элемента 2И-НЕ соединен с инверсным входом S второго RS-триггера, входы буферных элементов, выполненных с инверсией или без инверсии, подключены соответственно к прямому или инверсному выходам второго RS-триггера, а выходы указанных первого и второго буферных элементов подключены соответственно к выходу резистивного делителя и к базе пятого транзистора.

Сущность изобретение заключается в том, что управление состоянием внешнего регулирующего транзистора, эмиттером подключенным к входному выводу положйтельной полярности; осуществляется через промежуточный транзистор от коллектора выходного транзистора схемы управления, базой подключенного к RS-триггеру этой схемы и в том, что база промежуточного транзистора, к которой кроме указанного выходного транзистора схемы управления подключейа токозадающая цепь, как и выход резистивного делителя, шунтируются буферными элементами с открытыми коллекторами на время

естественной паузы схемы управления, что позволяет избавиться от этой паузы в работе регулирующего транзистора. Определение границ этой паузы, на время которой регулирующий транзистор включается принудител;ьно, ведется путем исследования состояния второго выходного транзистора схемы управления посредством логической части, включающей в себя указанные буферные элементы, RS-триггер, вход R которого управляется с коллектора второго выходного транзистора схемы управления, а по входу S - от схемы формирования импульса переключения по этому входу. Выходное напряжение RS-триггера является входным для

обоих буферных элементов. Выявление границы регулируемой паузы осуществляется введенными в схему управления интегрирующей цепью и логическими элементами (2ИЛИ и вторым 2И) и основано на возврате

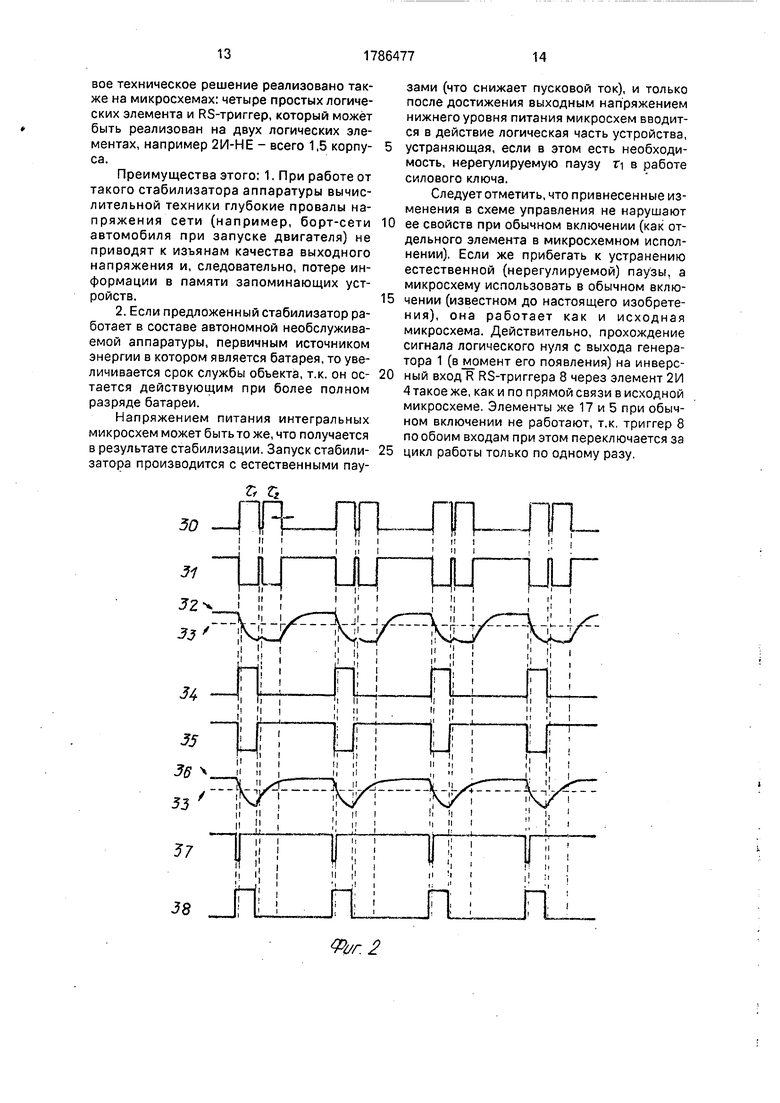

RS-триггера этой схемы в положение, соответствующее закрытому состоянию транзисторов, подключенных к триггеру, после выявления естественной паузы. На фиг. 1 представлена схема предложенного стабилизатора напряжения; на фиг, 2. даны эпюры напряжений в характерных точках схемы.i

Импульсный понижающий стабили$а- тор постоянного напряжения состоит из генератора 1, компаратора 2, первого логического элемента 2И 3, второго логического элемента 2И 4, логического элемента 2ИЛИ 5, логического элемента 2И-НЕ 6, ин- вертора 7, первого RS-триггера 8, у которого вход Р инверсный, второго RS-триггера 9 с обоими инверсными входами, источника опорного напряжения 10, первого 11 и в|то- рого 12 транзисторов типа проводимости n-p-п, третьего 13 и четвертого 14 транЬи- сторов типа р-гг-р, пятого транзистораИб типа проводимости n-p-п, диода 16, первой 17 и второй 18 интегрирующей RC-4eneuj из первого 19, второго 20, третьего 21 и четвертого 22 резисторов, из резистизного делителя 23, DLC-фильтра 24, первого 25 и второго 26 буферных элементов.

Между входом импульсного понижающего стабилизатора и его выходом включены последовательно соединенные транзистор 13 и DLC-фильтр 24. Через рези- стивный делитель 23 выход стабилизатора соединен с инвертирующим входом компаратора 2, неинвертирующий вход которого соединен с выходом источника опорного напряжения 10. Входы элемента 2И 3 подключены к выходам генератора 1 и компаратора 2. Выход компаратора 2 подключен также к первому входу логического элемента 2 ИЛ И 5, а выход генератора 1 подключен к первому входу второго элемента 2И 4 и через интегрирующую цепь 17 - к второму входу логического элемента 2ИЛИ 5, при этом выходы обоих логических элементов 2И подключены ко входам S и R RS-триггера 8. Выход триггера 8 подключен к базе транзистора 11, эмиттер которого соединен с базой транзистора 12. Эмиттер транзистора 12 подключен к общему проводу схемы устройства. Между входным выводом положительной полярности, к которому подключен и эмиттер транзистора 14, и коллектором транзистора 15 включены последовательно соединенные резисторы 19 и 20, общая точка которых подключена к базе транзистора 14. Коллектор транзистора 11 соединен с базой транзистора 15, а через резистор 21 - одновременно с цепью питания схемы управления. Эмиттер транзистора 15 через диод 16 подключен к общему проводу. Коллектор транзистора 12 подключен к одному из входов логического элемента 2И-НЕ 6, через последовательно соединенные инвертор 7 и интегрирующую RC-цепь 18 - к второму входу логического элемента 2И-НЕ 6, а через резистор 22 - к цепи питания логических элементов. Выход логического элемента 2И-НЕ 6 подключен ко входу S триггера 9, вход R которого подключен к общей точке коллектора транзистора 12, резистора 22 и входов логического элемента 6 и инвертора 7. К выходу триггера Q подключены входы буферных элементов 25, 26, а выходы этих элементов соединены соответственно с выходом резистивного делителя 23 и базой транзистора 15.

Эпюры на фиг. 2 показывают напряжения:

27 - на коллекторе транзистора 12.

Временные интервалы т и тг являют собой естественную и регулируемые паузы схемы управления:

28 -на выходе инвертора 7;

29 - на выходе интегрирующей RC-цепи 18. На эпюру 29 наложен уровень 30 логической единицы логического элемента; 31-33 - видеоизменение эпюр 27-29 при

предельно пониженном входном напряжении, когда регулируемая пауза исчезает (Т2 0);

34 - на выходе логического элемента 2И- НЕ 6;

35 - на выходе триггера 9.

Ниже приводится описание работы стабилизатора.

Транзисторы 11. 12 открываются с частотой генератора 1 на время, которое может

изменяться от как угодно малого значения до величины, большей, чем время закрытого состояния транзистора примерно в 8 раз. Соотношение времени открытого и закрытого состояния (широтно-импульсная модуляция) зависит от разности между входным и выходным напряжениями, а также от величины тока нагрузки, причем ко времени закрытого состояния добавляется еще постоянно присутствующая естественная

пауза на время релаксации генератора 1.

Чтобы достичь цель изобретения несмотря на указанную особенность схемы управления нужно обеспечить открытое состояние силового ключа (регулирующего

транзистора 13) во время естественной паузы, т.е. реализовать такой алгоритм управления силовым ключом, чтобы он работал в той же фазе, что и транзисторы 11,12 только на этапах формирования регулируемой паузы. На этапе же прохождения нерегулируемой (естественной) паузы фазы работы транзисторов 11, 12 и силового ключа должны быть противоположными. Однако сделать это известными средствами нельзя, т.к.

при обычном включении схемы управления естественная и регулируемая пауза сливаются и граница между ними неразличима. В настоящем изобретении эта задача решается следующим образом: сигнал с коллектора

транзистора 11 используется для управления силовым ключом, а сигнал с коллектора транзистора 12 -для управления RS-триггером 9. Во время открытого состояния транзистора 11 транзисторы 15

и 14 закрыты. Следовательно, будет открыт транзистор 13. И наоборот, в закрытом состоянии транзистора 11 надлежит быть открытым транзистору 15 (ток его базы проходит через транзистор 21), его коллекторный ток составит ток базы транзистора 14, и последний станет шунтировать переход база-эмиттер транзистора 13, который закрывается. По цепи обратной связи через резистивный делитель 23 выходное напряжение поступает на компаратор 2, где сравнивается с опорным. Компаратор 2 совместно со схемой 2И 3 и триггером 8 формируют управляющий широтно-модулированный сигнал для транзисторов 11 и 12. Дальнейшее взаимодействие транзисторов 11, 15, 14 и 13 образуют обычную цепь автоматического регулирования, характеризующуюся синфазным состоянием транзистора 11 и транзистора 13. Излом фазы регулирования (обеспечение противоположных состояний транзисторов 11 и 13) достигается воздействием на базу транзистора 15 со стороны открытого коллекторного выхода буферного элемента 26.

Во время возникновения паузы (которая начинается с нерегулируемой ее части) появляется положительный перепад напряжения на указанном втором выходе схемы управления (резистор 22 выступает коллекторной нагрузкой транзистора 12)-см. эпюру 27 на фиг. 2. Импульс, представленный на этой эпюре, создается введенной логической частью заявленного устройства дополнительно к исходной .схеме управления, однако начальная его часть - положительный перепад и примыкающая к нему плоская вершина обусловлены релаксацией генератора. Из этой части вырезается импульс синхронизации RS-триггера 9 по входу S. Происходят такие процессы: импульс 27 инвертируется (инвертор 7), интегрируется RC-цепью 18, а затем над полученным после этой цепи напряжением 29 и исходным импульсом 27 выполняется операция конъюнкции с отрицанием (элемент 2И-НЕ 6). Результирующий импульс 34 имеет один и тот же вид независимо от того, будет ли регулируемая пауза в работе транзистора 12 после естественной (нормальной) паузы не будет ( тг 0). Под воздействием синхронизирующего импульса 37 RS-триггер 9 перейдет в состояние выдачи логической единицы на своем выходе Q и откроются выходные транзисторы обоих буферных элементов 25, 26, в результате чего осуществится шунтирование базы транзистора 15 и выхода резистивного делителя 23 (на время данного состояния триггера). Шунтирование базы транзистора 15 приведет к принудительному открыванию транзистора 13, а шунтирование выхода резистивного делителя 23, что равносильно отключению обратной связи, обусловит переключение RS-триггера 8 по входу S сразу же по окончании процесса релаксации генератора 1 и формирование минимальной паузы, т.е. в размере лишь r-i , и таким образом окажется выделенной ее естественная длина (эпюра 35). В момент окончания первой половины импульса 27 на| коллекторе транзистора 12 возникает отрицательный перепад напряжения, которым RS-триггер 9 переводится по входу R в противоположное состояние (на его выходе Q установится логический нуль), и шунтирование буферными элементами 25, 26 вь|хода делителя 23 и базы транзистора 15 прекратится. Если пауза в работе силового

должна быть больше, чем естественна) пауза TI схемы управления, то в этой схеме на выходе компаратора напряжение примет вид логического нуля, и поскольку напряжение на выходе интегрирующей цепи 1t еще

не стало единицей (после появления логической единицы на выходе генератора), будет получен импульс логического нуля на выходе элемента 2ИЛИ 5, а т.к. появление логического нуля на любом входе второго

логического элемента 2И 4 вызывает логический нуль на его выходе то триггер 8 Снова переключится по входу R, и начнется вторая половина импульса 27 (регулируемая пауза). С этого момента силовой ключ (транзистор

13) будет управляться по обычной цег)и обратной связи,. i

Если условия регулирования приводят к паузе (регулируемый ее участок), то она сразу же возобновится, и импульс широтНо-импульсной модуляции силового к люча начнется спустя эту паузу Т2 , появление сигнала о которой на коллекторе транзистора 12 будет опять сопровождаться переключением триггера 9, процессами

шунтирования базы транзистора 15 и;выхо- да резистивного делителя 23, затем опять наступит выход из этого состояния через время Ti и т.д.i

Предложенный понижающий стзбилизатор постоянного напряжения выгодно отличается от прототипа тем, что он способен стабилизировать выходное напряжение при более глубоких провалах (снижениях) напряжения первичной сети вплоть до Јначения Увых + UHac, где обе составляющие суть выходное напряжение стабилизатора) и напряжения насыщения цепи колле|ктор- эмиттер силового ключа (регулирующего транзистора).|

Достигнуто это:|

Преимущества этого: 1. При работе от такого стабилизатора аппаратуры вычислительной техники глубокие провалы напряжения сети (например, борт-сети автомобиля при запуске двигателя) не приводят к изъянам качества выходного напряжения и, следовательно, потере информации в памяти запоминающих устройств.

Напряжением питания интегральных микросхем может быть то же, что получается в результате стабилизации. Запуск стабилизатора производится с естественными паузами (что снижает пусковой ток), и только после достижения выходным напряжением нижнего уровня питания микросхем вводится в действие логическая часть устройства,

устраняющая, если в этом есть необходимость, нерегулируемую паузу т в работе силового ключа.

Следует отметить, что привнесенные изменения в схеме управления не нарушают

ее свойств при обычном включении (как отдельного элемента в микросхемном исполнении), Если же прибегать к устранению естественной (нерегулируемой) паузы, а микросхему использовать в обычном включении (известном до настоящего изобретения), она работает как и исходная микросхема. Действительно, прохождение сигнала логического нуля с выхода генератора 1 (в мюмент его появления) на инверсный вход R RS-триггера 8 через элемент 2И 4 такое же, как и по прямой связи в исходной микросхеме. Элементы же 17 и 5 при обычном включении не работают, т.к. триггер 8 по обоим входам при этом переключается за

цикл работы только по одному разу.

| Микросхемы для бытовой аппаратуры | |||

| Справочник | |||

| М.: Радио и связь, 1983, с.50, Фолкенберри Л | |||

| Применение операционных усилителей и линейных интегральных схем | |||

| М.: Мир, 1985, с.315, рис.10.17а. |

Авторы

Даты

1993-01-07—Публикация

1990-11-20—Подача