первым и вторым информационными входами блока, выход первого шифратора подключен к входу первого дешифратора j первый и второй выходы которого соединены соответственно с нулевым и единичным входами первого триггера третий и четвертый выходы подключены соответственно к единичному входу второго триггера ц к первому входу первого элемента ИЛИ,пятьй выход первого дешифратора соединен с вторым входом первого элемента ИЛИ и с выходом признака конца оператора блока, с нулевьм входо третьего триггера, с первыми входам элементов И первой группы, выходы которых являются информационным выходом блока, выходы первого триггера и первого элемента ИЛИ соединены соответственно с первым и вторым входами первого элемента И, выход которого подключен к перв№( входам элементов И второй группы, к нулевому входу второго триггера и к первому входу второго элемента И, выход которого соединен с первым входом второго элемента ИЛИ, второй вход которого соединен с выходом третьего элемента И, второй вход второго элемента И и первые входы третьего и четвертого элементов И соединены с синхронизирующим входом блока, второй вход третьего элемента И соединен с выходом цятого элемента И, выход подключен к второму входу второго элемента ИЛИ, выход которого соединен с входом сдвига первого регистра, входы разрядов которого соединены соответственно с выходами элементов ИЛИ первой группы, выходы разрядов первого регистра соединены соответственно с вторыми входами элементов И первой группы, единичный вход третьего триггера является входом признака блока, выход третьего триггера подключен к второму входу четвертого элемента И, выход которого является синхронизируюйида выходом блокаj выход второго триггера соединен с установочным входом четвертого триггера и с первьм входом пятого элемента И, второй вход которого соединен с выходом четвертого триггера, а эькод подключен к первьм входам элементов И третьей группы, вторые входы которых соединены с выходом узла памяти, выходы

элементов И первой и третьей групп соединены соответственно с входами элементов ИЛИ первой группы, вторые входы элементов И второй группы соединены с первым информационньм входом блока, блок шифрации последовательности специальных разделителей содержит второй, третий и четвертый регистры, второй и третий шифраторы, второй дешифратор, пятый и шестой триггеры, с шестого по одиннадцатый элементы И, первый коммутатор, элемент НЕ, четвертую и пятую группы элементов И, вторую группу элементов ИЛИ, третий, четвертьй и пятый элементы ШШ, причем информационный вход второго регистра является первым информационньм входс с блока, второй информационный вход которого соединен с первьми входами второго и третьего шифраторов, выходы разрядов второго регистра подключены к вторым входам второго и третьего шифраторов и к первым входам элементов И четвертой группы, вторые входы которых соединены с выходом третьего элемента ИЛИ, а вьпсоды подключены к первьм входам элементов ИЛИ второй группы, вторые входы которых соединены с первым выходом третьего шифратора, а выходы подключены соответственно к информационному входу третьего регистра, вход сдвига которого соединен с выходом четвертого элемента ШШ, выхода разрядов третьего регистра соединены с первьми входами элементов И пятой группы, единичный вход пятого триггера является входом признака блока, а выход подключен к первому входу шестого элемента И, второй вход которого является синхронизируюпрм входом блока, выход шестого элемента И подключен к синхронизирующему входу четвертого регистра и к первым входам седьмого, восьмого и девятого элементов И, выход старшего разряда четвертого регистра соединен с вторым входом седьмого элемента И, с нулевым входом шестого триггера, с входом элемента НЕ, выходкоторого подключен к второму входу девятого элемента И, вьрсод шестого триггера соединен с вторым входом восьмого элемента И и с разрешающим входом коммутатора, первый и второй входы которого соединены соответственно с выходами седьмого и восьмого элементов И, выход коммутатора под-ключен к входу сдвига второго регистра, второй выход третьего шиф ратора соединен с информационньм входом четвертого регистра, третий выход подключен к единичному входу шестого триггера, выход второго шиф ратора соединен с входом второго дешифратора,первый выход которого соединен с первыми входами десятого элемента И и третьего элемента ИЛИ, второй вход которого и первый вход одиннадцатого элемента И подключены к выходу пятого элемента ИЛИ, вторы входы десятого и одиннадцатого элементов И соединены с выходом девятого элемента И, выходы подключены соответственно к входам четвертого элемента ИЛИ, второй выход второго дешифратора подключен к разрешающему входу третьего шифрато ра и к первому входу пятого элемента ИЛИ, третий выход соединен с нулевым входом пятого триггера, вторы ми входами пятого элемента ИЛИ и элементов И пятой группы, с выходом признака конца оператора блока, выходы элементов И пятой группы являются информадионньм выходом бло ка, блок вьщеления служебных символов содержит пятый и шестой регистры, четвертый шифратор, третий дешифратор, седьмой триггер, с двенад цатого по пятнадцатый элементы И, шестую и седьмую группы элементов И шестой и седьмой элементы ИЛИ и второй коммутатор, информационный вход которого соединен с выходами разрядов пятого регистра, выходы разрядов шестого регистра соединены с первыми входами .элементов И шестой и седьмой групп и с первым входом четвертого шифратора, второй вход которого является вторым информационным входом блока, первый информационный вход которого соединен с информационньм входом шестого регистра, вход сдвига которого подключен к выходу двенадцатого эле мента И, единичный вход седьмого триггера является входом признака блока, выход седьмого триггера подключен к первому входу тринадцатого элемента И, второй вход которого является синхронизирующим входом блока, а выход подключен к первым входам двенадцатого, четьфнадцатого и пятнадцатого элементов И, выход четвертого шифратора соединен с входом третьего дешифратора, первьй выход которого подключен к первому входу шестого элемента ИЛИ, к вторым входам четырнадцатого элемента И и элементов И седьмой группы, второй выход третьего дешифратора подключен к второму входу шестого элемента ШШ и к первому входу седьмого элемента ИЛИ, выход которого соединен с вторыми входами пятнадцатого элемента И и элементов И шестой группы,с первым разрешаюпщм входом второго коммутатора и с третьим управляющим входом блока, третий выход третьего дешифратора соединен с третьим входом шестого элемента ИЛИ, с вторым разрешающим входом коммутатора и с вторым управляющим выходом блока, выход пятнадцатого элемента И является первым управляющим выходом блока, четвертый выход третьего дешифратора подключен к второму входу седьмого элемента ИЛИ, к нулевому входу седьмого триггера и к выходу признака Разделитель блока, выход четырнадцатого элемента И соединен с входом сдвига пятого регистра, выходы разрядов которого соединены с информационным входом второго коммутатора,выход элементов И шестой группы является первьш информационным выходом блока, первьй и второй выходы второго коммутатора явЛ5Потся соответственно вторым и третьим информационными выходами блока, выход шестого элемента: ИЛИ соединен с вторым входом двенадцатого элемента И.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для лексического анализа метамикроассемблера | 1982 |

|

SU1034043A1 |

| Устройство для лексического анализа символьного текста | 1984 |

|

SU1187173A1 |

| Устройство для параметрической автогенерации символьного текста | 1985 |

|

SU1439621A1 |

| СИСТЕМА ДЛЯ ШИФРАЦИИ И ДЕШИФРАЦИИ КОМАНД | 1991 |

|

RU2043699C1 |

| Устройство для контроля текстовой информации | 1983 |

|

SU1328817A1 |

| УСТРОЙСТВО ДЛЯ ОБЪЕДИНЕНИЯ ЛЕКСИЧЕСКИХ МНОЖЕСТВ | 1990 |

|

RU2022354C1 |

| Система для сопряжения терминалов с вычислительной машиной | 1987 |

|

SU1529232A1 |

| Устройство синтаксически управляемого перевода | 1986 |

|

SU1399767A1 |

| Устройство для диагностики неисправностей многоярусных пирамидальных схем | 1980 |

|

SU980084A1 |

| Устройство для редактирования алфавитно-цифровой информации на экране видеоконтрольного блока | 1983 |

|

SU1254460A1 |

УСТРОЙСТВО ДЛЯ ЛЕКСИЧЕСКОГО АНАЛИЗА МЕТАТРАНСЛЯТОРА, содержащее регистр ввода, информационный вход которого является информационным входом устройства, блок памяти кода алфавита и генератор синхроимпульсов, отличающееся тем, что, с целью расширения функциональных возможностей за счет увеличения числа анализируемых языков программирования, в него введен блок шифрации последовательности простых разделителей, блок шифрации последовательности специальных разделителей, блок выполнения смежных символов, блоки памяти разделителей, меток и идентификаторов, выход каждого из которых является соответствующим выходом устройства, выходы разрядов регистра ввода соединены с первым информационным входом блока шифрации последовательности простых разделителей, синхронизирующий, информационный выходы и выход признака конца оператора которого соединены соответственно с входом сдвига регистра ввода, с первым информационным входом и входом признака блока шифрации последовательности специальных разделителей, информационный вход и выход признака конца оператора которого соединены соответственно с первым информационным входом и входом признака блока выделения служебных символов, выход признака Разделитель которого соединен с входом признака блока шифрации последовательности простых разделителей, первый, второй и третий управляющие входы блока вьщеления служебных символов соединены соответственно с входами разрешения (Л записи блока памяти разделителей, блока памяти меток и блока памяти идентификаторов, информационные входы которых соединены соответственно с первым, вторым и третьим информационньми выходами блока выделения служебных символов, синхроел низирующие и вторые информационные Од вхады блоков шифрации последовасо ю со тельности простых разделителей, шифрации последовательности специальных разделителей и блока вцделения служебных символов соединены соответственно с выходом генератора синхросигналов и с выходом блока памяти кода алфавита, причем блок шифрации последовательности простых разделителей содержит первый регистр, группы элементов И, первый дешифратор, триггеры, узел памяти, элементы И, ИЛИ, первую группу элементов ИЛИ и первый шифратор, входы которого соединены соответственно с

Г

Изобретение относится к вычислительной технике и может быть использовано для лексического анализа в трансляторах с языком программирования, которые производят анализ операторов и, если все правильно, формируют последовательности команд Известно устройство дпя обработки выражений языков программировани содержащее блок управления, арифметический блок, триггеры занятости, блок стековой памяти операндов, счетчик операндов, регистры операндов, блок формирования адресов и операндов, блок стековой памяти управляющих символов, счетчик управляюищх символов, индикатор нуля,бло анализа управляюпдагх символов,счётчи индексных позиций и регистр номера массива ClI. Основном недостатком аппаратно реализованного в устройстве грамматического разбора программы на базовые элементы является жесткая привязанность к языку программирования и выбранной системе кодирования символов для представления их в машине. Программно реализованный грамматический разбор пpoгpaм ы на базовые элементы (метки, вдентификаторы, ключевые слова, разделители) характеризуется, кроме того, низким быстродействием лексического анализа. Наиболее близким по технической сущности к предлагаемому является устройство для лексического анализа метамикроас.семблера, содержащее блок управления, включающий генератор синхроимпульсов, два регистра, информационный вход первого из которых, является информационным вхо дом устройства,выход второго регистра является информас(ионным выходом устройства, шифратор, комму татор и блок памяти номера алфавита причем выход первого регистра соеди нен с первыми входами шифратора и коммутатора,.выход шифратора соединен с входом блока управления, первьй - четвертый выходы которого сое динены соответственно с вторым и третьим входами коммутатора,, с первым входом второго регистра и с управляю1чим входом первого регистра, выход коммутатора соединен с вторьм входом второго регистра, выход блок памяти номера алфавита соединен с вторым входом шифратора 2}. Однако в свя зи с широким распространением микропроцессорных наборов больших интегральных-схем (БИС) 9 и с появлением множества языков программирования (таких как ассемблеры, языки высокого уровня), ориентированных на различные системы кодирования символов, необходиМО создание универсального устройства для лексического анализа программ, которое можно быстро приспособить к новой системе кодирования и новому языку. Описанное устройство является аппаратной реализацией блока лексического анализа метамикроассемблера, которое не может быть использовано для обработки выражений и других конструкций, используемых в языках высокого уровня, так как оно кодирует разделители одним кодом. Цель изобретения - расширение функциональных возможностей устройства за счет увеличения числа анализ1фуемьг с языков программирования. Поставленная цель достигается тем, что в устройство для лексического анализа метатранслятора, содержащее регистр ввода, информационный вход которого является информационным входом устройства, блок памяти кода алфавита и генератор синхроимпульсов, введен блок шифрации последовательности простых разделителей, блок шифрации последовательности специальных разделителей, блок выделения смежных символов, блоки памяти разделителей, меток и идентификаторов, выход каждого из которых является соответствующим выходом устройства, выходы разрядов регистра ввода соединены с первым информационным входом блока шифрации последовательности простых разделителей, синхронизирующий, информационный выходы и выход признака конца оператора которого соединень соответст- венно с входом сдвига регистра ввода, с первьм информационным входом и входом признака блока шифрации последовательности специальных разделителей, информационный вход и выход признака конца оператора которого соединены соответственно с первым информационньй входом и входом признака блока вьщеления служебных символов, вькод признака Разделитель которого соединен с входом признака блока шифрации последовательности простых разделителей, первьй, второй и третий управляющие входы блока вьщеления

служебных символов соединены соответственно с входами разрешения записи блока памяти разделителей, блока памяти меток и блока памяти идентификаторов, информационные вхо- 5 ды которых соединены соответственно с первым, вторым и третьим информационными выходами блока выделения служебных символов, синхронизирующие и вторые информационные входы Ю блоков пгафрации последовательности простых разделителей, шифрации последовательности специальных разделителей и блока вьзделения служебных символов соединены соответствен- 15 но с выходом генератора синхросигналов и с выходом блока памяти кода алфавита, причем блок шифрации последовательности простых разделителей содержит первый регистр, группы 20 элементов И, первый дешифратор, триггеры, узел памяти, элементы И, ИЛИ, первую группу элементов ИЛИ и первьш шифратор, входы которого соединены соответственно с первым и 25 вторым информационньми входами блока, выход первого шифратора подключен к входу первого дешифратора, первый и второй выходы которого соединены соответственно с нулевым и единич- 30 ным входами первого триггера, третий и четвертый выходы подключены соответственно к единичному входу второго триггера и к первому входу, первого элемента ИЛИ, пятый jj выход первого дешифратора соединен с вторым входом первого элемента ИЛИ и с выходом признака конца оператора блока, с нулевым входом третьего триггера, с первыми вко-до дами элементов И первой группы, выходы которых являются информационным выходом блока, выходы первого триггера и первого элемента ИЛИ соединены соответственно 45 с первым и вторым входами первого элемента И, выход которого подключен к первым входам элементов И второй группы, к нулевому входу второго триггера и к первому входу 50 второго элемента И, выход которого соединен с первым входом второго элемента ИЛИ, второй вход которого соединен с выходом третьего элемента И, второй вход второго эле- -j мента И и первые входы третьего и четвертого элементов И соединены с синхронизирующим входом блока.

второй вход третьего элемента И соединен с выходом пятого элемента И, выход подключен к второму входу второго элемента ИЛИ, выход которого соединен с входом сдвига первого регистра, входы разрядов . которого соединены соответственно с выходами элементов ИЛИ первой группы, выходы разрядов первого регистра соединены соответственно с вторьми входами элементов И первой группы, единичный вход третьего триггера является входом признака блока, вьгход третьего триггера подключен к второму входу четвертого элемента И, выход которого является синхронизирующим выходом блока, выход второго триггера соединен с установочным входом четвертого триггера и с первым входом пятого элемента И, второй вход которого соединен с выходом четвертого триггера , а выход подключен к первым входам элементов И третьей группы, вторые входы которых соединены с выходом узла памяти, выходы элементов И первой и третьей групп соединены соответственно с входами элементов ИЛИ первой группы, вторые входы-элементов И второй группы соединены с первым информационным входом блока, блок шифрации последовательности специальных разделителей содержит второй, третий и четвертый регистры, второй и третий шифраторы, второй дешифратор, пятый и шестой триггеры, с шестого по одиннадцатьй элементы И, первый коммутатор, элемент НЕ, четвертую и пятую группы элементов И, вторую группу элементов ИЛИ, третий, четвертьй и пятый элементы ИЛИ,причем информационный вход второго регистра является первым информационным входом блока, второй информационный вход которого соединен с первыми входами второго и третьего шифраторов , выходы разрядов второго регистра подключены к вторым входам второго и Третьего шифраторов и к первым входам элементов И четвертой группы, вторые входы которых соединены с выходом третьего элемента ИЛ а выходы подключены к первьм входам элементов ИЛИ второй группы, вторые входы которых соединены с первьм выходом третьего шифратора, а выходы подключены соответственно к информационному входу третьего регистра, вход сдвига которого соединен с выходом четвертого элемента ИЛИ, выходы разрядов третьего регистра соединены с первыми входами элементов И пятой группы, единичный вход пятого триггера является входом признака блока, а выход подключен к первому входу шестого элемента И, второй вход которого является синхронизирующим входом блока, выход шестого элемента И подключен к синхронизирующему входу четвертого регистра и к первьм входам седьмого, восьмого и девятог элементов И, выход старшего разряда четвертого регистра соединен с вторьм входом седьмого элемента И, с нулевьм входом шестого триггера, с входом элемента НЕ, выход которого подключен к второму входу девятого элемента И, вьвсод шестого триггера соединен с вторым входсм восьмого элемента И и с разрешающим входом коммутатора, первый и второй входы которого соединены соответственно с выходами седьмого и восьмого элементов И, выход коммутатора подключен к входу сдвига второго регистра, второй вь1ход третьего шифратора соединен с информационным входом четвертого регистра, третий выход подключен к единичному входу шестого триггера, выход второго шифратора соединен с входом второго дешифратора, первый выход которого соединен с первьв4и входами десятого элемента И и третьего элемента ИЛИ, второй вход которого и первьй вход одиннадцатого элемента И подключены к выходу пятого элемента ИЛИ, вторые входы десятого и одиннадцатого элементов И соединены с выходом девятого элемента И, выходы подключены соответственно к входам четвертого элемента ИЛИ, второй выход второго дешифратора подключен к разрешающему входу третьего шифратора, и к первому входу пятого элемента ИЛИ, третий выход соединен с нулевьм входом пятого триггера, вторыми входами пятого элемента ИЛИ и элементов И пятой группы, с выходом признака конца оператора блока, выходы элементов И пятой группы являются информационным выходом блока, блок вьщеления служебных символов

153329 ,

содержит пятый и шестой регистры, четвертый шифратор, третий дешифратор, седьмой триггер, с двенадцатого по пятнадцатый элементы И, 5 шестую и седьмую группы элементов И, шестой и седьмой элементы ИЛИ и второй коммутатор, информационный вход которого соединен с выходами разрядов пятого регистра,

10 выходы разрядов шестого регистра соединены с первыми входами элементов И шестой и седьмой групп и с первым входом четвертого шифратора, второй вход которого является

«5 вторым информационньм входом блока, первый информационный вход которого соединен с информационньм входом шестого регистра, вход сдвига которого подключен к выходу двенадцато20го элемента И, единичный вход седьмого триггера является входом признака блока, выход седьмого триггера подключен к первому входу тринадцатого элемента И, второй вход кото25рого является синхронизирующим входом блока, а выход подключен к пер-, вьм входам двенадцатого, четырнадцатого и пятнадцатого элементов И, выход четвертого шифратора соединен

30 с входом третьего дешифратора, первый выход которого подключен к первому входу шестого элемента ШШ, к вторым входам четырнадцатого элемента И и элементов И седьмой группы, 5 второй В1ыход третьего дешифратора подключен к второму входу Шестого элемента ИЛИ и к первому входу седьмого элемента ШШ, выход которого соединей с вторыми входами пятнад

40 цатого элемента И и элементов И шестой группы, с первым разрешанидим входом второго коммутатора и с третьим управляющим входом блока, третий выход третьего дешифратора

5 соединен с третьим входом шестого

элемента ИЛИ, с вторым разрешающим входом коммутатора и с вторым управляющим выходом блока, выход пятнад„J цатого элемента И является первым управляющим выходом блока, четвертый выход третьего дешифратора подключен к второму входу седьмого элемента ИЛИ, к нулевому входу седьмого , триггера « к выходу признака Разделитель блока, выход четьгрнадцатого элемента И соединен с входом сдвига пятого регистра, выходы разрядов которого соединены с информационным

входом второго коммутатора, выход элементов И шестой группы является первым информационным выходом блока первый и второй выходы второго коммутатора являются соответственно вторым и третьим информационньи и выходами блока, выход шестого элемента ИЛИ соединен с вторым входом двенадцатого элемента И.

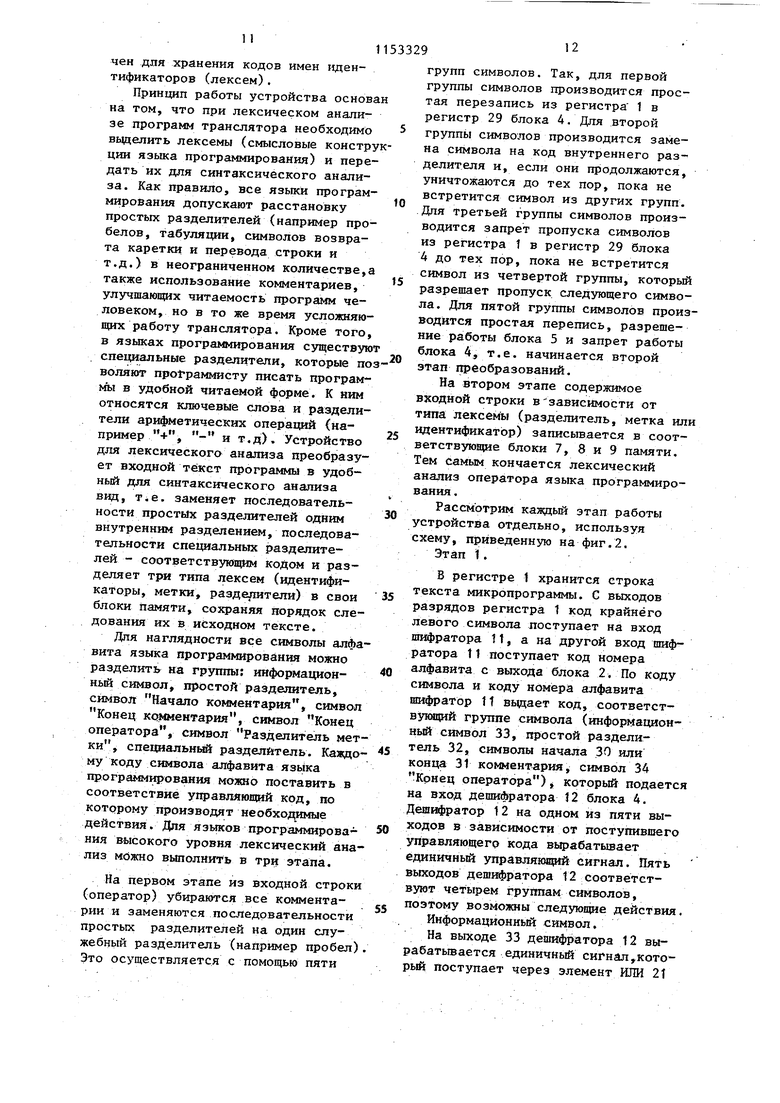

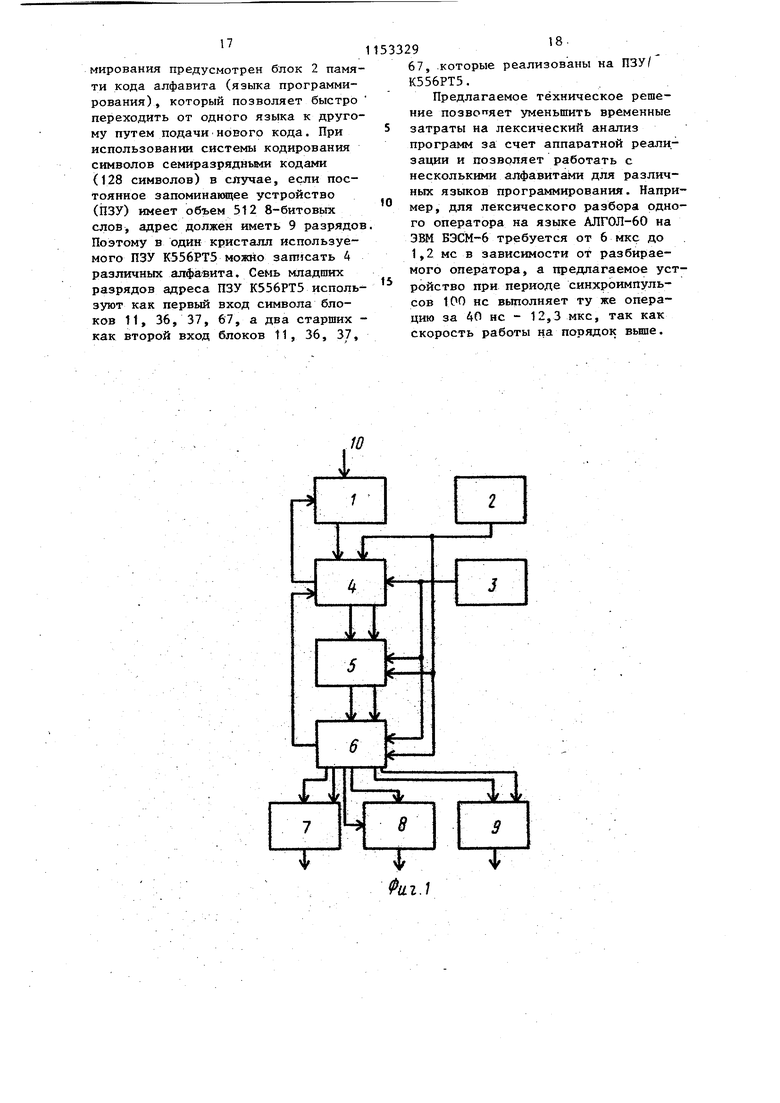

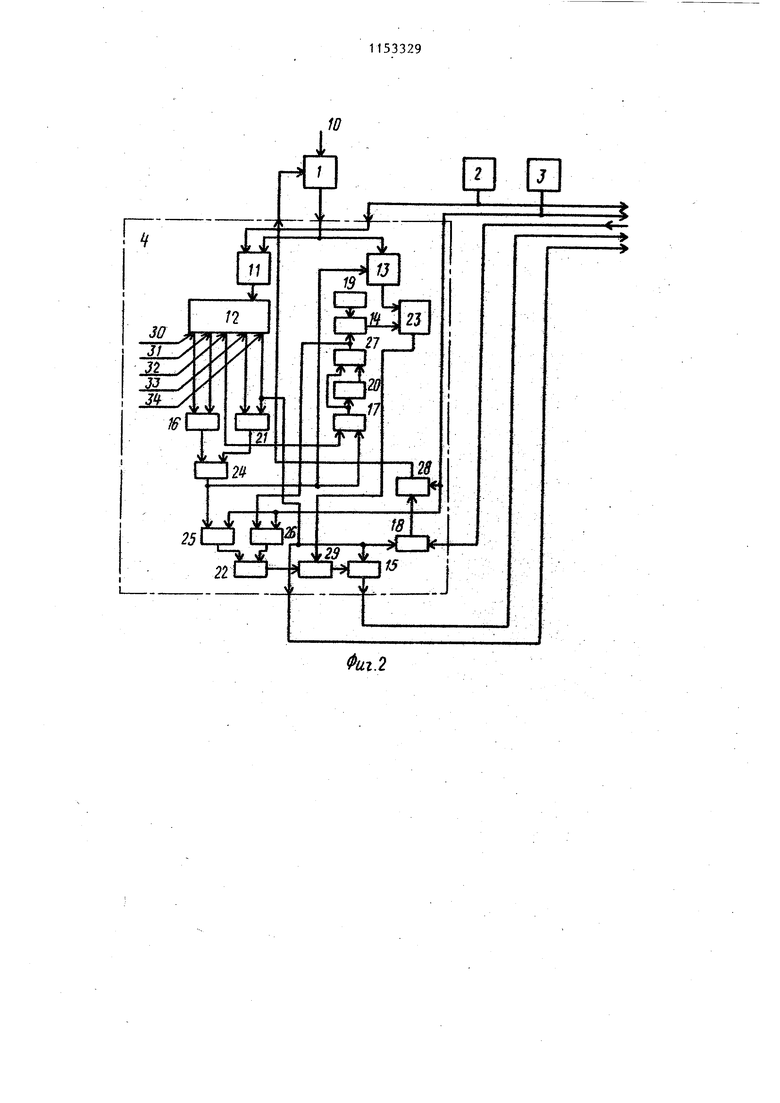

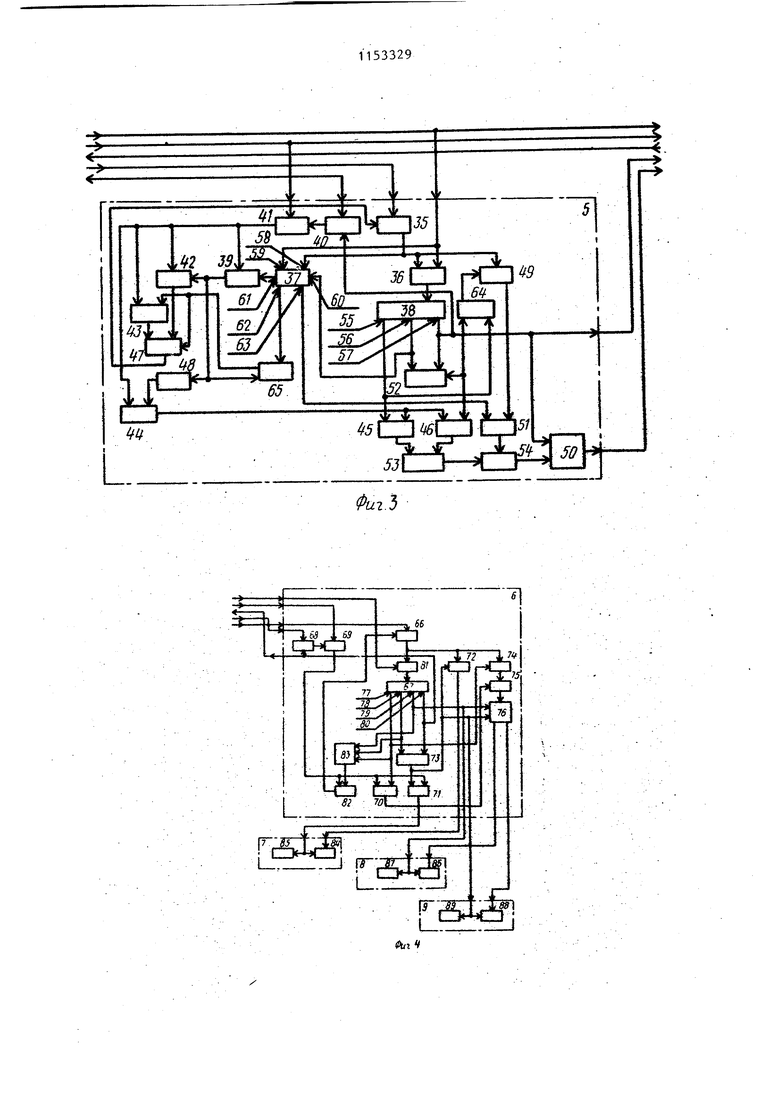

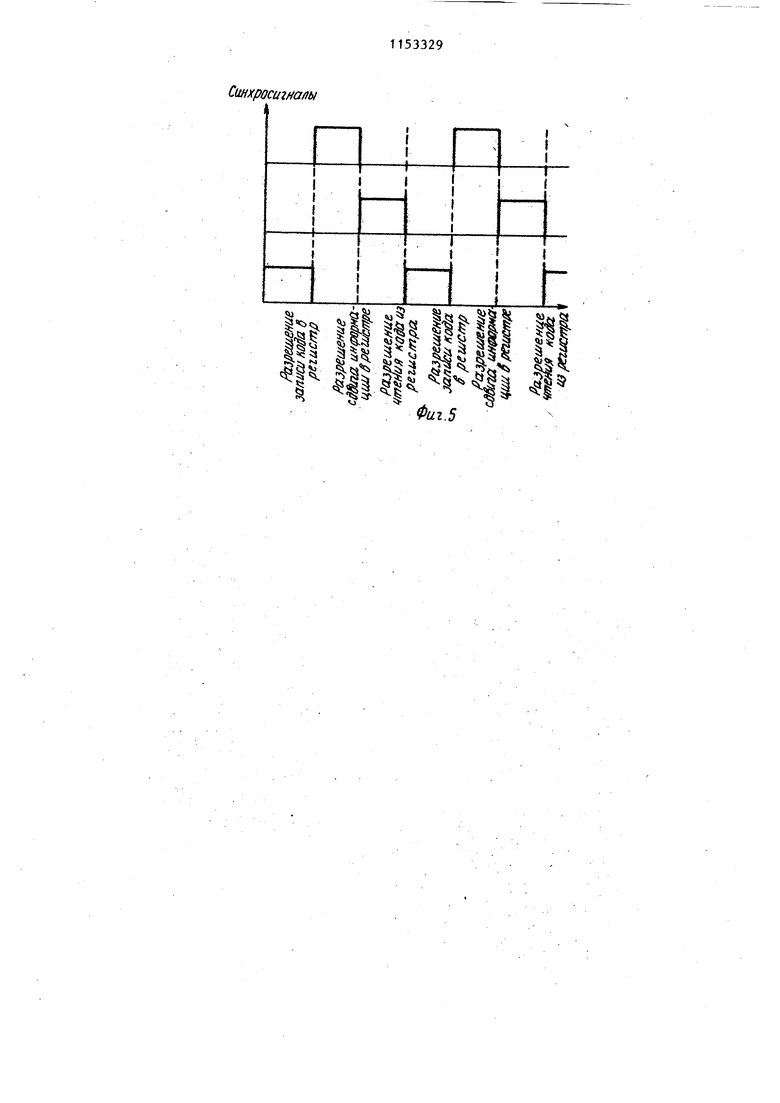

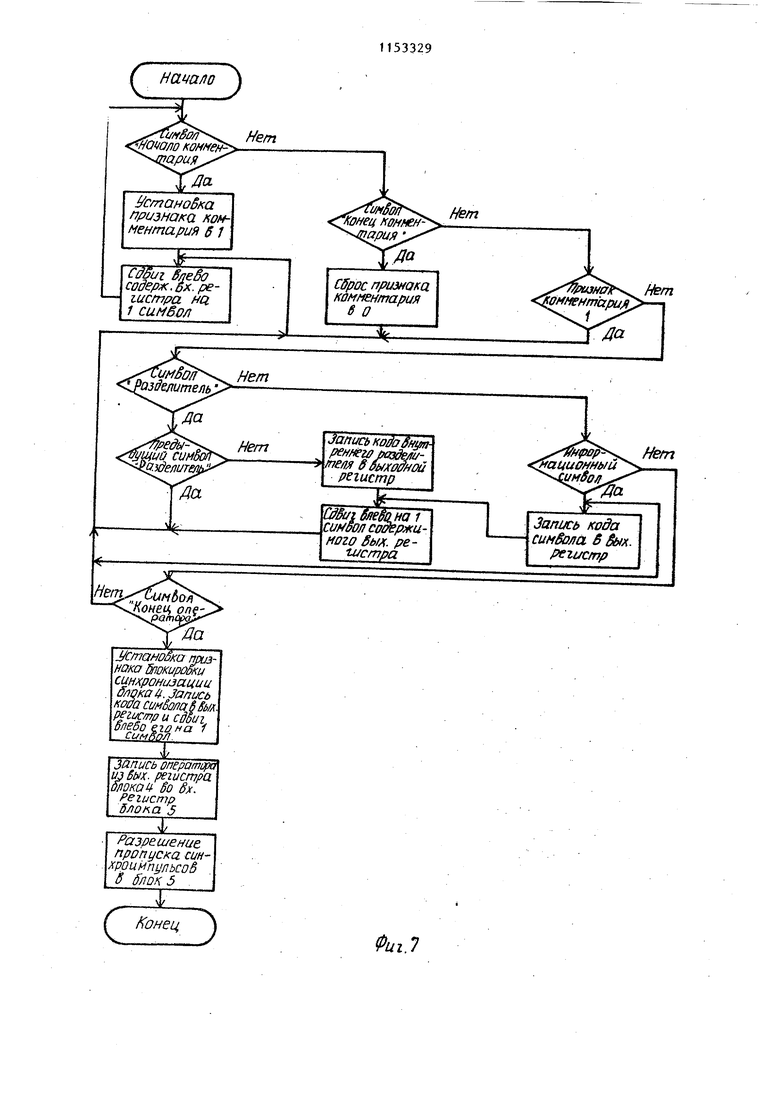

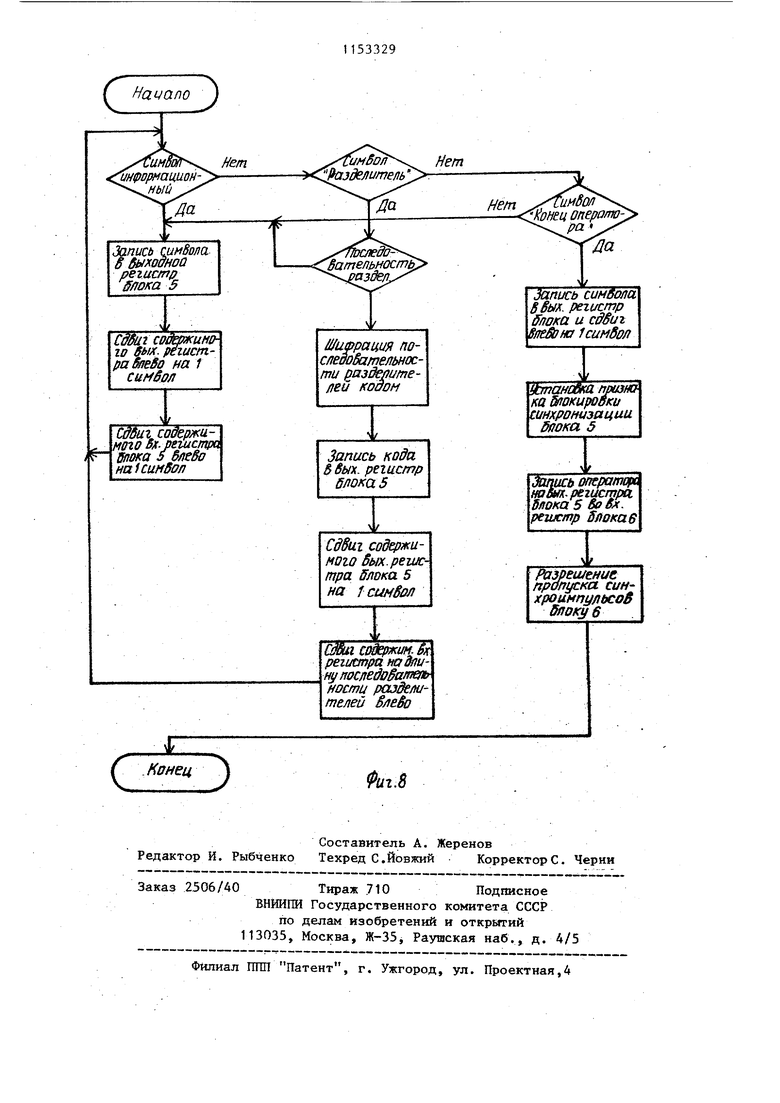

На фиг.1 приведена блок-схема устройства , на фиг.2 - схема блока шифрации последовательности простых разделителей; на фиг.З - схема блока шифрации последовательности спец разделителей; на фиг.4 - схемы блока вьщеления символов и блоков памяти; на фиг.5 - пример эпюр напряжений генератора синхроимпульсов на фиг.6 - алгоритм работы устройства; на фиг. 7 - алгоритм работы блока шифрации последовательности простых разделителей; на фиг. 8 алгоритм работы блока шифрации последовательности специальных разделителей.

Устройство содержит регистр 1 ввода, блок 2 памяти кода алфавита, генератор 3 синхроимпульсов, блок 4 шифрации последовательности простых разделителей,, блок 5 шифрации последовательности специальных разделителей, блок 6 вьщеления служебных символов, блок 7 памяти разделителей, блок 8 памяти меток, блок 9 памяти идентификаторов, вход 10 устройства, шифратор 11, дешифратор t2, группы элементов И 13-15, триггеры 16-18, узел 19 памяти, триггер 20, элементы ИЛИ 21 и 22, группу элементов ИЛИ 23, элементы И 24-28, регистр 29, выход 30 Начало комментария, выход 31 Конец комментария, выход 32 Простой разделитель, выход 33 Информационный символ, выход 34 Конец оператора, регистр 33, шифраторы 36 и 37, дешифратор 38, регистр 39, триггер 40, элементы И 41-46, коммутатор 47, элемент НЕ 48, группу элементов И 49,50,группу элементов ИЛИ 51, элементы ШШ 52 и 53, регистр 54, выход 55 Информационный символ, выход 56 Простой разделитель, выход 57 Конец оператора, вход 58 последовательности символов, вход 59 алфавита, вход 60 разрешения, выход 61 числа сдвигов, выход 62 управления, выход 63

кода последовательности разделителей, элемент ИЛИ 64, триггер 65, регистр 66, дешифратор 67, триггер 68, элементы И 69-71, группу

элементов И 72, элемент ИЛИ 73, группу элементов И 74, регистр 75, коммутатор 76, выход 77 Информационный символ, выход 78 Конец оператора, выход 79 Разделитель

метки, выход 80 Разделитель, шифратор 81, элемент И 82, элемент ШШ 83, регистр 84, счетчик 85, регистр 86, счетчик 87, регистр 88 и счетчик 89.

Регистр 1 устройства предназначен для хранения строки (или строк), содержащей один оператор языка программирования, и может быть собран на сдвигающих регистpax. Блок 2 памяти кода алфавита

предназначен для хранения кода номера алфавита, который может меняться в процессе работы (например, при переходе от латинского алфавита к

русскому и наоборот) и может быть собран на регистрах. Блок 4 шифрации последовательности простых разделителей предназначен для преобразования последовательности байтовых кодов (представляющих собой простые разделители типа Пробел, Табуляция, Возврат каретки, Перевод строки ) в один байтовый код, а также для исключения из

строки оператора комментария.Влок 5 шифрации последовательности специальных разделителей предназначен для преобразования последовательности байтовых кодов, (представляющих

собой специальные рааделителя

языка гфограммирования типа ключевых слов разделителей, напр1вдер Ч; « ..(« пу, и т.д., и последовательности разделителей (например )) код. Данное преобразование позволяет сжать информацию из )1, удобной для человека, в форму, удобную для машины.

Блок 6 вьщеления служебных симмолов (идентификаторов, меток н разделителей) предназначен для извлечения из входной строки текста програ1«в 1 идентификаторов, меток и

разделителей в соответствующую ему память с сохранением порядка следования в операторе. Блок в па1етти меток предназначен для хранения кодов имен меток в операторе. Блок 9 памяти идентификаторов предназначен для хранения кодов имен идентификаторов (лексем). Принцип работы устройства основа на том, что при лексическом анализе программ транслятора необходимо вьщелить лексемы (смысловые констру ции язьжа программирования) и передать их для синтаксического анализа. Как правило, все языки программирования допускают расстановку простых разделителей (например пробелов, табуляции, символов возврата каретки и перевода строки и т.д.) в неограниченном количестве,а также использование комментариев, улучшающих читаемость прогрш м человеком, но в то же время усложняющих работу транслятора. Кроме того, в языках программирования сзпцествую специальные разделители, которые по воляют npot-paMMHCTy писать программы в удобной читаемой форме. К ним относятся ключевые слова и разделители арифметических операций (например +, - и т.д). Устройство для лексического анализа преобразует входной текст программы в удобньй для синтаксического анализа виц. Tie. заменяет последовательности простых разделителей одним внутренним разделением, последовательности специальных разделителей - соответствующим кодом и разделяет три типа лексем (идентификаторы, метки, разделители) в свои блоки Памяти, сохраняя порядок следования их в исходном тексте. Для наглядности все символы алфа вита языка программирования можно разделить на группы; информационньй символ, простой разделитель, символ Начало комментария, символ Конец комментария, символ Конец оператора, символ Разделитель мет ки, специальный разделитель. Каядо му коду символа алфавита языка программирования можно поставить в соответствие управляющий код, по которому производят необходимые действия. Для языков программировав ния высокого уровня лексический ана лиз можно выполнить в три этапа. На первом этапе из входной строки (оператор) убираются все комментарии и заменяются последовательности простых разделителей на один служебный разделитель (например пробел Это осуществляется с помощью пяти групп символов. Так, для первой группы символов производится простая перезапись из регистра 1 в регистр 29 блока А, Для второй группы символов производится замена символа на код внутреннего разделителя и, если они продолжаются, уничтожаются до тех пор, пока не встретится символ из других групп. Для третьей группы символов производится запрет пропуска символов из регистра t в регистр 29 блока 4 до тех пор, пока не встретится символ из четвертой группы, который разрешает пропуск следующего символа. Для пятой группы символов производится простая перепись, разрешение работы блока 5 и запрет работы блока 4, т.е. начинается второй этап преобразований. На втором этапе содержимое входной строки взависимости от типа лексемы (разделитель, метка или идентификатор) записывается в соответствующие блоки 7, 8 и 9 памяти. Тем самым кончается лексический анализ оператора языка программирования . Рассмотрим каждый этап работы устройства отдельно, используя схему, приведенную на фиг.2. Этап К В регистре 1 хранится строка текста микропрограммы. С выходов разрядов регистра 1 код крайнего левого символа поступает на вход шифратора It, а на другой вход щифратора t1 поступает код номера алфавита с выхода блока 2. По коду символа и коду номера алфавита шифратор t1 вьщает код, соответствуниций группе символа (информационный символ 33, простой разделитель 32, символы начала 30 или конца 31 комментария, символ 34 Крнец оператора) которьй подается на вход дешифратора 12 блока 4. Дешифратор 12 на одном из пяти выходов в зависимости от поступившего управляющего кода вырабатывает единичньй управляющий сигнал. Пять выходов дешифратора 12 соответствуют четырем группам символов, поэтому возможны следующие действия. Информационный символ, На выходе 33 дешифратора 12 вырабатывается единичный сигнал,который поступает через элемент ИЛИ 21 на вход элемента И 24. В зависимости от состояния триггера 16, который определяет, комментарий это или нет, возможны два варианта действий:1 . Да, это комментарий. Тогда на выходе триггера 16, а следовательно, и на выходе элемента И 24 появляется нулевой сигнал, который поступает на вход группы элементов И 13 и запрещает пропуск кода символа из регистра 1 в регистр 29. Нулевой сигнал с элемента И 24 пост пает на вход элемента И 25 и запрещает пропуск синхросигнала с блока 3 на регистр 29, по которому произв дится сдвиг информации. В то же время элемент И 26 закрыт, так как на выходе 32 дешифратора 12 вьфабатывается нулевой сигнал, который через элементы 17, 20 и 27 поступае на вход элемента И 26. Записи символа в регистр 29 не происходит в связи с тем, что на выходе элемента И 26, а следовательно, и на входе регистра 29 присутствует нулевой сигнал. Синхроимпульс с блока 3 поступает на вход регистра 1, по которому происходит сдвиг информации на один символ. После сдвига синхроимпульс разрешает вьщавать информацию с вькода шифратора 11 на вход дешифратора 12. 2. Нет, это не комментарий. Тогда на выходе триггера 16, а след вательно, и на выходе элемента 24 появляется единичный сигнал, которы поступает на вход группы элементов И 13, разрешая пропуск кода символа из регистра 1 в регистр 29 на вход триггера 17 (хранителя информации о последовательности разделителей) , устанавливая его в нулевое состояние, на вход элемента И 25, разрешая пропуск синхроси нала с блока 3 через элементы И 25 ИЛИ 22 на вход регистра 29, по которому происходит запись кода сим1зола в крайние правые разряды регис ра 29, а затем сдвиг информации влево на символ содержимого, а также сдвиг влево на символ содерж мого регистра 1. Это выполняется только при установке триггера 16 в положение Не комментарий (Hia инверсном выходе триггера 16 - еди ничньй сигнал). Если это не первый разделитель, то элемент И 27 выраб 14 . 9 тьшает нулевой сигнал, .запрещающий запись кода разделителя в регистр 29, и происходит только сдвиг влево содержимого регистра 1 на один символ. Символ Начало комментария. На выходе 30 дешифратора 12 блока 4 вырабатывается единичный сигнал, который поступает на вход триггера 16 и устанавливает его в. нулевое состояние. Тем самым запрещается запись символов в регистр 29 с помощью блокировки элемента И 24 до тех пор, пока не появится символ Конец комментария, по которому на выходе 31 дешифратора 12 блока 4 вырабатьшается единичный сигнал, который поступает на вход триггера 16 и устанавливает его выход в единичное состояние. Тем самьм разрешается работа всех элементов устройства. Символ Конец оператора. На выходе 34 дешифратора 12 блока 4 появляется единичный сигнал, который поступает на вход установки в нуль триггера 18, запрещая пропуск синхросигналов через элемент И 28 на вход сдвига регистра 1. Кроме того, единичный сигнал с выхода 34 поступает через блоки 21, 24, 25 и 22 на вход .регистра 29,разрешая сдвиг информации, и через блоки 21, 24, 13 и 23, разрешая запись кода в регистр 29, а также разрешает запись информации из регистра 29 через группы элементов И 15 в регистр 35 блока 5 и синхроиизацшо работы блока 5 за счет установки в единичное состояние триггера 40, который разрешает пропуск синхросигнала из блока 3 через элемент И 41 на элементы блока 5. Этап 2. С выхода регистра 35 код кра:йнего лбвого символа поступает на вход шифратора 36, на другой вход которого поступает код номера алфавита с выхода блока 2. По коду символа и коду номера алфавита шифратор 36 выдает код, соответствуюп ий группе символа информационный символ 55, Простой разделитель 56, Конец оператора 57), который подается на вход дешифратора 38.Дешифратор на одном из трех выходов в зависимости от поступающего управляющего кода вырабатьшает единичный управляющий сигнал. Три вых да дешифратора 38 соответствуют трем группам символов, поэтому воз можны следунмцие действия. Информационный символ. На выходе 55 дешифратора 38 вырабатывается единичный сигнал, который поступает на вход элемента И 43 и разрешает запись кода символа через элементы И 49 в регистр 54, а также пропуск синхросигнала через элемент ИЛИ 53 на вход сдвига регистра 54. После это производится сдвиг содержимого регистров 35 и 54 на один символ. Символ Простой разделитель. На выходе 56 дешифратора 38 блока 5 вырабатьшается единичный сигнал, который разрешает работу шифр тора 37 (вход 60). Шифратор 37 ста вит в соответствии с кодом последо тельности разделителей (код болывой рядности) байтовый код и признак обнаружения заданной последовательности. С выхода 63 вшфратора 37 код поступает через элементы ИЛИ 5f на вход регистра 54 для записи. С выхо 62 шифратора 37 код поступает на вход установки триггера 65, который вьщает сигнал разрешения работы на элемент И 43 и коммутатор 47 для управления сдвигом содержш ого регистра 35 на k символов. Это осуществляется следующим образом. С вы хода 61 шифратора 37 унитарный код поступает в регистр 39. Старший раз ряд регистра 39 управляет работой элементов И 42, 43. Если в старшем разряде регистра 39 единица, то элемент И 42 пропускает синхросигнал на вход коммутатора 47, который пропускает его на вход сдвига регистра 35, а на элемент И 44 поступает нулевой сигнал, который блокирует пропуск синхросигнала на регистр 54; Если в старшем разряде регистра 39 нуль, го он поступает н вход сброса триггера 63, KoTopi запрещает сдвиг на fc символов регистра 35 при единичном сдвиге регистра 54 и разрешает обычную синхронизацию 1 в I. Таким образом, осуществляется сдвиг на i символов при найденной последовательности, а при ненайденной осуществляется простая запись кода разделителя в регистр 54 и сдвиг на один 29 символ содержимого регистров 35 и 54. Символ Конец оператора. На выходе 57 дешифратора 38 появляется единичный сигнал, который разрешает запись символа в регистр 54 через элементы И 49 и ИЛИ 51, устанавливает триггер 40 в нулевое состояние, тем самым блокируя пропуск синхроимпульсов в блок 5 и разрешая вывод содержимого регистра 54 через элементы И 50 в регистр 66 блока 6. Этап 3. С выхода регистра 66 код символа поступает на шифратор 81, который формирует управляющий код для дешифратора 67. Дешифратор 67 на одном из четырех выходов формирует единичный сигнал, который и управляет работой блока 6. Четыре выхода де1 гфратора 67 соответствз т четырем группам символов, поэтому возможны следующие действия. Ш|формационный символ. На выходе 77 дешифратора 67 находится единичньй сигнал, который поступает на элементы И 70 и 74 и разрешает запись кода символа в регистр 75, а затем сдвиг содерЯсимого регистров 66 и 73. Символ Конец оператора. На выходе 78 дешифратора 67 находится единичный сигнал, который разрешает запись кода разделителя в блок 7 памяти разделителей и запись содержимого регистра 75 через ко№1утатор 76 в блок 9 памяти иденткфикаторов, а также блокирует свою синхронизацию и включает синхронизацшо блока 4, Символ Раздешггель метки. На выходе 79 дешифратора 67 ваходите единичный сигнал, разрешает запись содержимого регистра 75 через коммутатор 76 в блок 8 памяти меток. Символ Разделитель. На выходе 80 MemHtt aTopa 67 находится единичный сигнал, который разрешает запись кода разделителя в блок 7 памяти разделителей и запись содержимого регистра 75 через коммутатор 76 в блок 9 памяти идентификаторов. Лля работы с несколькими алфавитами для разных языков программирования предусмотрен блок 2 памя ти кода алфавита (языка программирования) , который позволяет быстро переходить от одного языка к друго му путем подачи нового кода. При использовании системы кодирования символов семиразрядньми кодами (128 символов) в случае, если постоянное запоминаницее устройство (ПЗУ) имеет объем 512 8-битовых слов, адрес должен иметь 9 разрядо Поэтому в один кристалл используемого ПЗУ К556РТ5 можно записать 4 различных алфавита. Семь младших разрядов адреса ПЗУ К556РТ5 исполь зуют как первый вход символа блоков 11, 36, 37, 67, а два старших как второй вход блоков t1, 36, 37,

i 9 67, .которые реализованы на ПЗУ/ К556РТ5. Предлагаемое техническое решение позволяет уменьшить временные затраты на лексический анализ программ за счет аппаратной реализации и позволяет работать с несколькими алфавитами для различных языков программирования. Например, для лексического разбора одного оператора на языке АЛГОЛ-60 на ЭВМ БЭСМ-6 требуется от 6 мкс до 1,2 мс в зависимости от разбираемого оператора, а предлагаемое устройство при периоде синхроимпульсов 100 НС вьтолняет ту же операцию за 40 НС - 12,3 МКС, так как скорость работы на порядок вьш1е.

Фиг.Ъ

Сш1хроси2напы

CffSaz 6лебо на1 символ содерж. 6btx. регистра

Sufрация пвсяе. Вательмязтр{ тплтйбайтобынкодом

{Индикация ошиВки

Запись байтотго кода 8 память

fta e flumtМй

Сдвиг памяти разделителей на 1Ъайт

С KoHei4

стп&т б : . рожлатети

Нет

Нет

janucb Ko jSwmНетpefifffiff ро шНет

J maHOuKo тизнока окиро& и синхронизации лока. Janucb коаа симьола68шl ii mp и сдбиг блебо его и а i Симпо

ЗЯпись оператора из бых. регистра

SflOKQ So 6)(. Регистр 5л о к а 5

JL.

Разрешение пропуска санхрриипупьсоВ5 fflDf 5 .

IZI-II

с Конец j

Фиг

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для обработки выражений языков программирования | 1974 |

|

SU519715A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для лексического анализа метамикроассемблера | 1982 |

|

SU1034043A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-04-30—Публикация

1983-10-24—Подача