(5) УСТРОЙСТВО для ДИАГНОСТИКИ НЕИСПРАВНОСТЕЙ МНОГОЯРУСНЫХ ПИРАМИДАЛЬНЫХ СХЕМ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для диагностики НЕиСпРАВНОСТЕй МНОгОяРуСНыХ пиРАМидАльНыХСХЕМ | 1978 |

|

SU798849A1 |

| Устройство для перезапуска вычислительного комплекса при обнаружении сбоя | 1988 |

|

SU1541608A1 |

| Устройство для управления реконфигурацией резервированной вычислительной системы | 1991 |

|

SU1837296A1 |

| Устройство для вычисления спектра Фурье | 1983 |

|

SU1121678A1 |

| Устройство для прерывания программ | 1982 |

|

SU1072045A1 |

| Устройство для контроля цифровых узлов | 1984 |

|

SU1231506A1 |

| Устройство для диагностики группы линейных последовательностных машин | 1977 |

|

SU708354A1 |

| Устройство для моделирования сетевых графов | 1983 |

|

SU1151979A1 |

| Устройство для оценки профессиональной пригодности операторов автоматизированных систем управления | 1984 |

|

SU1244697A2 |

| Устройство для имитации неисправностей | 1987 |

|

SU1444775A1 |

1

Изобретение относится к вычислр тельной технике и может быть использовано в схемах контроля и диагностики неисправностей многоярусных пирамидальных схем в изделиях радиоэлектронной аппаратуры.

Известно устройство для диагностики неисправностей многоярусных пирамидальных схем, содержащее регистры наборов входного, положительного и отрицательного результатов, дешифратор, группы конъюнктивных и дизъюнктивных элементов, схему фиксации результата проверки, триггер управления, регистры номера яруса и элемента СПНедостатком устройства является

то, что при числе ярусов пирамидальной схемы равном четырем и более время поиска неисправностей свертки становится значительным, что отрицательно сказывается на быстродействий устройства.

Кроме того, требование иметь в соответствие каждому набору отрицательного исхода определенный набор положительного исхода приводит к увеличению дополнительного оборудования устройства.

Наиболее близким по технической сущности к предлагаемому является устройство для диагностики неисправ10ностей многоярусных пирамидальных схем, содержащее логические элементы И, ИЛИ, НЕ, регистр номера матрицы, схему фиксации результата проверки,

ts триггер управления, сумматор по модулю Р, даа счетчика с Р-устойчивыми состояниями, три дешифратора с двумя группами Р-выходных шин каждый и группы схем сравнений, причем выходы

20 счетчиков и Сумматора соединены со входами дешифраторов, выходы которых соединены с первыми входами схем сравнения. На вторые входы схем соавнении поданы выходы матриц пирамидальной схемы. Каждому состоянию счетчиков и сум матора соответственно оС , 1 , на выходах дешифраторов соответствуют позиционные коды d,t,jj, f, где J - ) rnodP -a di- ) mod Выходы дешифраторов, соединены со входами матриц нижнего яруса пирамидальной схемы таким образом, что на выходе каждой матрицы присутствует сигнал, определяющий остаток вида. oL,X,P,Xr. Неисправность матрицы вь ражается в несоответствии позиционных кодов на ее выходе и выходе дешифратора, соединенного со схемой сравнения, которая подключена к данной матрице. Если в матрице имеется неисправность, то при подаче на ее входы кодов, вызывающих работу неисправных цепей матрицы, и кода на схему срав нения, соответствующего выходному сигналу матрицы, схема сравнения выдает сигнал ошибки, который устанавливает соответствующий триггер регистра номера матрицы в 1 и остана ливает работу счетчиков. Номер неисправной матрицы однозначно определяется состоянием регистра номера матрицы. Если матрица представляет собой группу РхР двухвходовых элементов И, то при значении Р 7/5 их число состав ляет значительную величину (например при Р 7 число элементов И в матрице равно 7 X 7 ), поэтому возникает необходимость определения адрес неисправного элемента в матрице. Известное устройство не позволяет определить адрес неисправного элемен та в матрице, что увеличивает время его поиска при устранении неисправности. Цель изобретения - увеличение раз решающей способности диагностики за счет определения неисправности с точ ностью дд элемента матрицы. Поставленная цель достигается тем, что в устройство для диагностики неисправностей многоярусных пирамидальных схем, содержащее п схем сравнения, блок приоритета, регистр результата, регистр номера неисправной матрицы, триггер управления, пер вый элемент И, первый и второй счетчики .по модулю Р, сумматор по модулю Р, первый, второй и третий дешифра94 причем первая группа входов п схем сравнения является группой входов устройства, выход каждой схемы сравнения соединен с соответствующим входом блока приоритета, первая и вторая группы выходов блока приоритета соединены соответственно с группой входов регистра номера неисправной матрицы и с группой входов регистра результата, выход которого соединен с нулевым входом триггера управления, установочный вход устройства соединен со входом обнуления сумматора по модулю Р, первого и второго счетчиков по модулю Рис единичным входом триггера управления, выход кот;рро го соединен с первым входом первого элемента И, тактовый вход устройства соединен со вторым входом первого элемента И, выход которого соединен со счетным входом первого счетчика по модулю Р. выход переполнения первого счетчика по модулю Р соединен со счетным входом второго счетчика по модулю Р и первым входом сумматора по модулю Р, второй вход которого соединен с выходом переполнения второго счетчика по модулю Р, выходы первого, второго и третьего дешифраторов образуют группу выходов устройства и соединены со вторыми входами соответствующих схем сравнения, в устройство введены формирователь импульсов, второй, третий , пятый элементы И, первая. вторая, третья и четвертая группы элементов И, первая и вторая группы элементов ИЛИ, семь элементов ИЛИ, элемент НЕ, первый, второй, третий, четвертый, пятый и шестой триггеры, регистр номера строки и регистр номера столбца, шифратор, причем выход регистра результата соединен с первым входом второго элемента И,выход которого через формирователь импульсов соединен с первыми входами третьего,четвертого и пятого элементов И, выход каждого из которых соединен, соответственно со входом первого, второго и третьего дешифраторов, выход триггера управле-чи ния соединен со вторым входом второго элемента И, информационные выходы сумматора по модулю Р, первого и второго счетчиков по модулю Р соединены соответственно со вторыми входами пятого, третьего и .четвертого элементов И, прямая и инверсная группы выходов каждого дешифратора соединены с соответствующей группой информационных входов шифратора, выходы схем сравнения группы соединены со входами соответствующих элементов ИЛИ, выходы первого, второго, третьего, четвертого, пятого и шестого элементов ИЛИ, соединены с единичными входами соответственно первого, второго, третьего, четвертого, пятого и шестого триггеров, выходы которых соединены с соответствующими входами шифратора выходы пятого и шестого триггеров,соединены соответственно с первым и вторым входами седьмого элемента ИЛИ выход которого через элемент НЕ соединен с первыми входами элементов И первой и второй групп, выход седьмого элемента ИЛИ соединен с первыми входами элементов И третьей и четвертой групп, первая и вторая группы выходов шифратора, выходы элементов И первой и второй групп соединены соответственно с первым, вторым, третьим и четвертым входами соответствующих элементов ИЛИ первой группы, третья и четвертая группы выходов шифратора и выходы элементов И третьей и четвертой групп соединены соответственно с первым, вторым, третьим и четвертым входами соответствующих элементов ИЛИ второй группы, пятая группа выходов шифратора соединена со вторыми входами соответствующих элементов И первой и третьей групп, шестая группа выходов шифратора со единена со вторыми входами соответствующих элементов И второй и четвертой групп, выходы элементов ИЛИ первой и второй групп соединены со входами регистров номера строки и столбца соответственно.

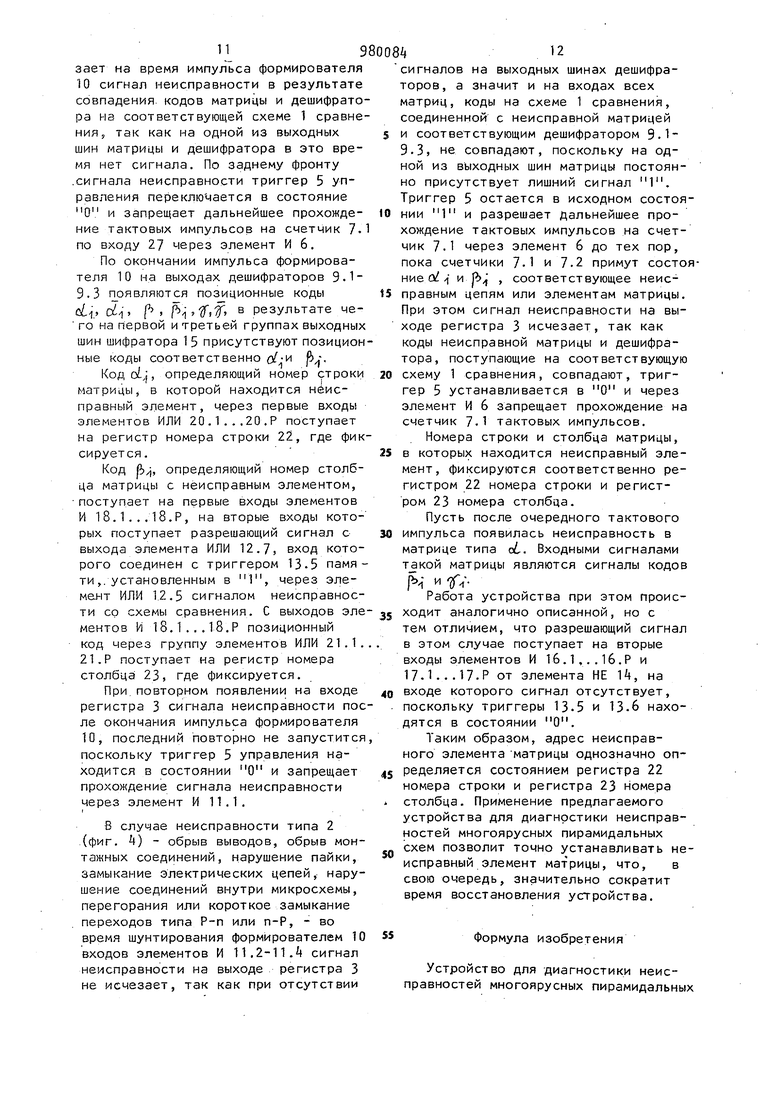

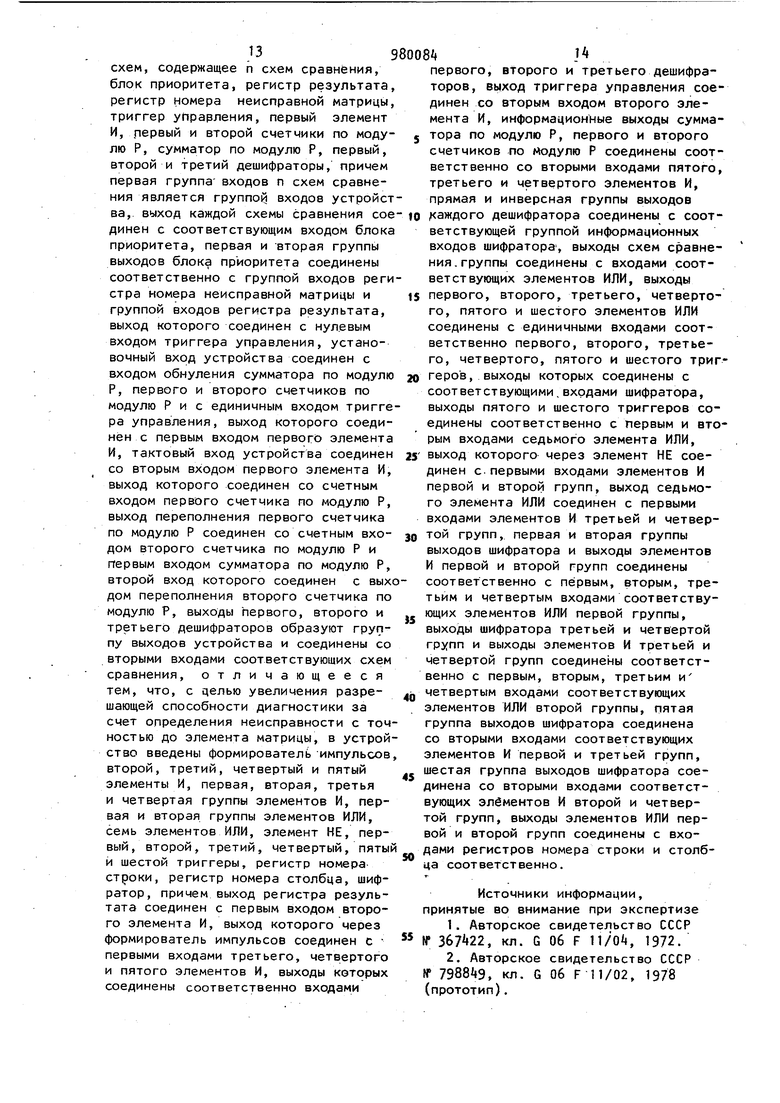

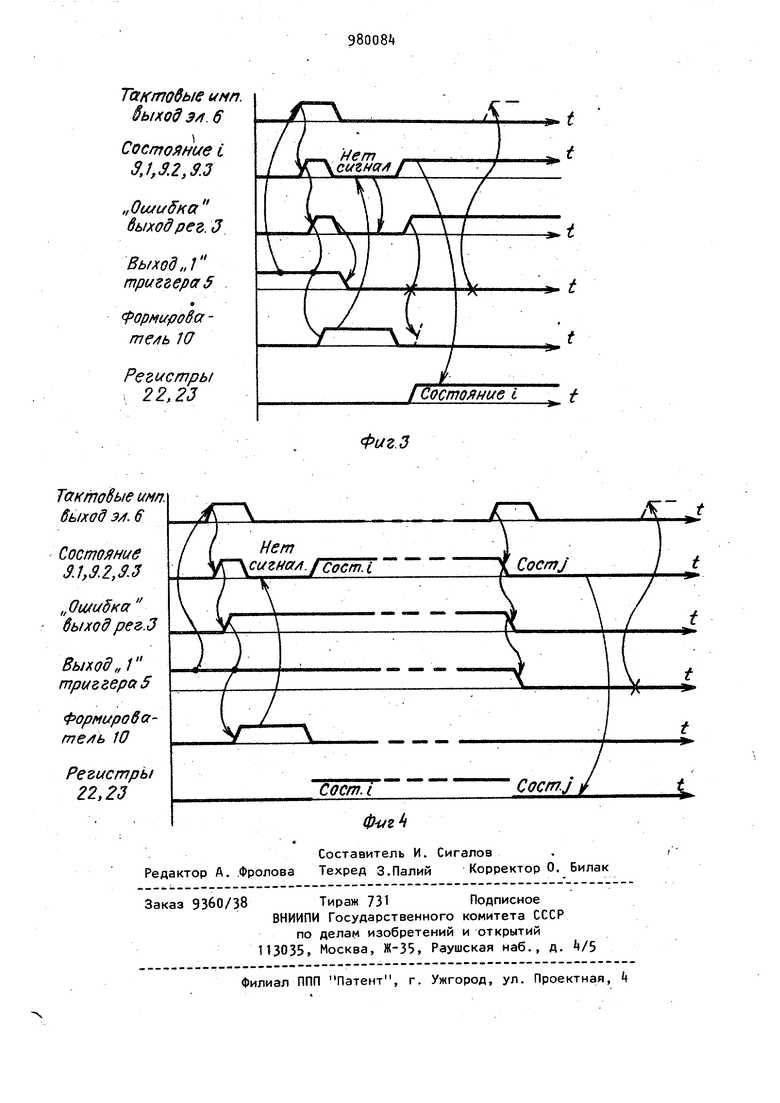

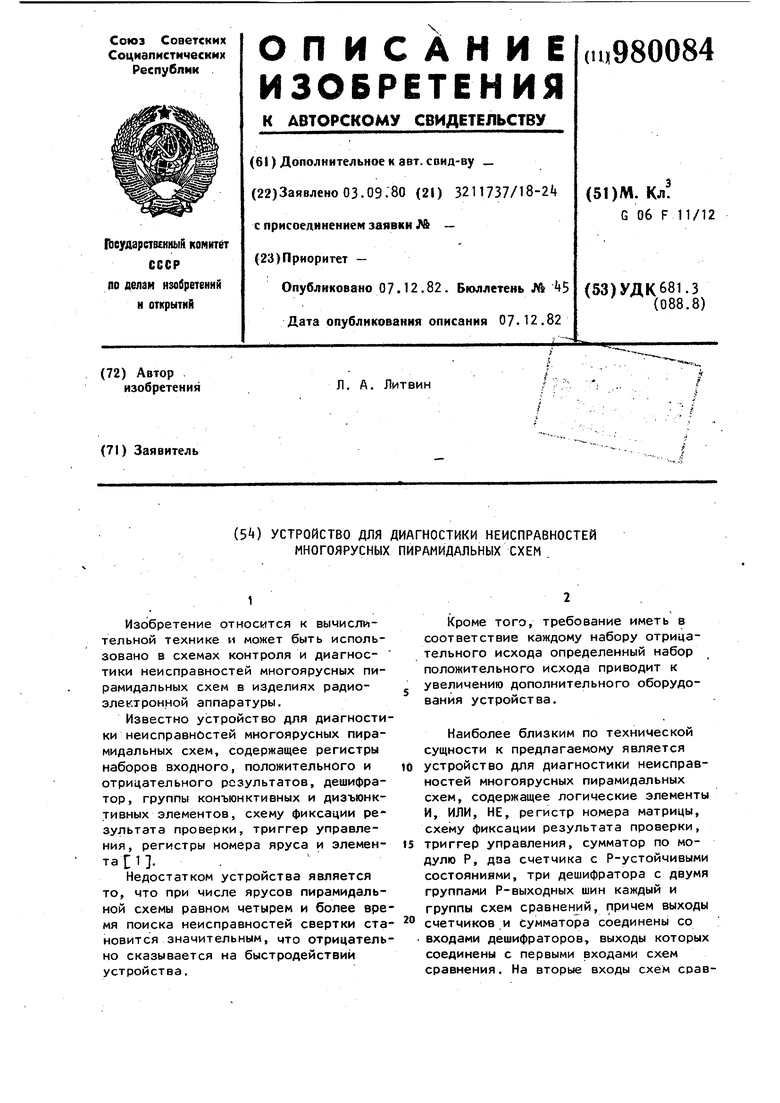

На фиг. 1 представлена блок-схема предлагаемого устройства , на фиг. 2 блок-схема блока 2 приоритета; на фиг. 3 и - временные диаграммы работы для случаев неисправности типа 1 и 2.

Устройство содержит п схем 1 сравнения, блок 2 приоритета, регистр 3 результата, регистр номера неисправной матрицы, триггер 5 управления, первый элемент И 6, первый 7.1 и второй 7-2 счетчики по модулю Р сумматор 8 по модулю Р, первый, второй и третий дешифраторы 9.1 9-2, и 9.3 формирователь 10 импульсов, второй, третий, четвертый и пятый элементы И 11.1, 11.2, 11.3 и 11., семь элементов ИЛИ 12.1, 12.2, 12.3,

Блок 2 приоритета содержит К элементов ИЛИ 28.1...28К, К-1 элементов НЕ 29.1...29К-1, К-1 групп элементов И 30, где К - количество пирамидальной схемы. Количество элементов И 30 в каждой группе в отдельности определяется количеством матриц в каждом ярусе пирамидальной схемы, начиная со второго нижнего..Всего

зо.1...зо.й.. и У|

элементов И 30

Элементы устройства соединены следующим образом.

Группа 25 входов устройства соединена с выходами матриц многоярусной пирамидальной схемы.

Выход регистра 3 соединен с нулевым входом триггера 5 и первым входом элемента И 11.1.

Единичный выход триггера 5 соединен со вторым входом элемента И П.1 и первым входом элемента И 6, второй вход которого соединен с тактовым входом 27, а выход - со счетным входом счетчика 7.1, выход переполнения KOTopQ.ro соединен со счетным входом счетчика 7.2 и первым входом сумматора 8.

Первые входы элементов И 11.2 11. соединены соответственно с информационными выходами счетчиков 7.1 7.2 и сумматора 8, а вторые входы с выходом формирователя 10, вход которого соединен с выходом элемента И 11.1.

Выходы элементов И 11.2 - 11.4 соединены соответственно .с входами дешифраторов 9.1-9.3, прямые и инверсные группы выходов которых соединены с информационной группЬй входов шифратора 15 и являются группой выходов 2Ц.

Управляющий вход шифратора 15 соединен соответственно с выходами триггеров 13.1-13.6. Выходы схем сравнения группы, соответствующие , прямым и инверсным выходам дешифратора 9.1 соединены с соответствующими входами элементов ИЛИ 12.1 и 12.2 соответственно. Выходы схем сравнения группы, соответствующие прямым и инверсным выходам дешифратора 9.2, соединены с соответствующим входами элементов ИЛИ 12.3 и 12. соответственно. Выходы схем сравнения, соответ ствующие прямым и инверсным выходам дешифратора 9..3, соединены с соответ ствующими входами элементов ИЛИ 12.5 и 12.6 соответственно. Выход каждогоеэлемента ИЛИ 12.112.6 соединен с единичным входом три гера 13.1, 13.2,. 13.3, 13.i, 13.5 и 13.6 соответственно. Выходы триггеров 13.5 и 13.6 соединены соответственно с первым и вторым входом элемента ИЛИ 12.7, выход которого через элемент 1 соединен с первыми входам элементов И 16.1...16.Р и 17.1...17. Выход элемента ИЛИ 12,7 соединен с первыми входами элементов И 18.1.... 18.Р и 19.К .. 19. Р. Каждый выход шиф ратора 15, соответствующий прямому и инверсному выходам дешифратора 9.1 .каждый выход элемента И групп 16.1.. 16.Р и 17.1...17.Р соединены соответ ственно с первым, вторым, третьим и четвертым входами соответствующего элемента ИЛИ группы 20 .К . .20. Р. Каж дый выход шифратора соответствующий прямому и,инверсному выходу дешифратора 9.3, каждый выход элемента И групп 18.1...18.Р и 19.1...19.Р соединены соответстЁенно с первым, вторым, третьим, и четвертым входами .соответствующего элемента ИЛИ группы 21.1...21.Р. Выходы шифратора 15, соответствующие прямым выходам дешифратора 9.2, соединены со вторыми входами соответствующих элементов И групп 16.1.. .16.Р и 18.1,..18. Выходы шифратора 15, соответствующие инверсным выходам дешифратора 9.2, соединены со вторыми входами соответ ствующих элементов И групп 1f;1... 17.Р и 19.1... 19.Р. Выходы элементов ИЛИ групп 20.1...20.Р и 21.1...21.Р соединены со входами регистров 22 и 23 соответственно. Первые входы п схем 1 сравнения являются группой входов 25, единичный вход триггера 5, установочные входы счетчиков 7. 7.2 и сумматора 9 8 соединены с установочным входом 2б, а второй вход элемента И 6 соединен с тактовым входом 27. Входы первого элемента ИЛИ 28.1 соединены с выходами схем 1 сравнеНИИ подключенных к выходам риц нижнего (первого) яруса, а с соответствующими входами регистра Ц, Выходы элементов И 30 каждой из К-1 групп в отдельности соединены с входами соответствующего ей элемента ИЛИ 28, выход которого соединен со входом элемента НЕ 29, подключенного своим выводом к одному из входов каждого элемента И 30 последующих групп, считая в направлении от нижних к верхним ярусам. Выход каждого элемента И 30 соединен с соответствующим входом регистра , выходы элементов ИЛИ 28 соединены со входами регистра 3. Устройство работает следующим образом. Назначение блока 2 приоритета следующее. Появление неисправности в матрице любого яруса пирамидальной схемы вызывает появление ошибки в матрицах, связанных с ней, всех последующих старших ярусов. Блок 2 блокирует появление ошибки на всех последующих выходах, отдавая приоритет ошибке с яруса, в котором находится источник ошибки - неисправная матрица. Каждому состоянию счетчиков 7.1, 7.2 и сумматора 8 соответственно oL , f) и на .выходе дешифраторов 9.1, 9.2 и 9.3 соответствует позиционный код cL,, p,f,Jff (. 3(ci4|b)OdP. Выходы дешифраторов 9..3, представляющие каждый прямую и инверсную группу по Р шин в каждой, соединены со входами матриц нижнего (первого) яруса таким образом, что на выходе ка)дой матрицы пирамидальной схемы присутствует сигнал вида oi , ot , р, , Р Т однозначно определяющий входные сигналы матрицы согласно следующим тождествам: (.jb4-f)ynodPi )mou Р, (i-f3) ,|Ь - ) modP; 7 (oL+ mod P; Э .98 Выход каждой матрицы соединяется с первым входом соответствующей ей схемы 1 сравнения, на второй вход ко торой подается соответствующая выходу матрицы одна из групп выходных mViH дешифраторов 9.1, 9.2 и 9.3 oL И11и ci , или (Ъ или |Ъ , или У или Шифратор 15 представляет собой обычную схему шифрации позиционного На информационной группе входов шифратора 15 присутствуют сигналы дешиф раторов 9.1 9.3 соответственно oL и oL, и , , определяемые состоянием счетчиков 7.1, 7.2 и сумматора 8. Каждой из шести комбинаций позиционного кода, условно обозначенных oi- , Д , /Ь . i . 9 и f , а двух определенных группах шин шифратора 15 соответствуют позиционные коды, определяемые следующими соотношени я коду pt-соответствуют и коду ofр и f, коду |Ь - ot и , коду fb - o и f, коду - - d и , коду -о1 и 1 В поз. шифратора 15 фиг. 1 косым отрезками линий условно изображены диоды, включенные между вертикальны ми информационными горизонтальными управляющими шинами шифратора. Поля ность включения диодов зависит от полярности принятых рабочих сигналов. Матрица контролируемой пирамидал ной схемы представляет собой квадратную матрицу, состоящую из Р стро Р столбцов и содержит Р двухвходовые элементы И. Для получения остатка на первый и второй входы матрицы подают позицион ный Р разрядный код строки и-столбца соответственно.. Пер вые входы элементов И каждой .строки в отдельности соединены с шиной разряда позиционного кода строки, имеющего одноименный со строкой номер, а вторые входы элементов И каждого столбца в отдельности соединены с шиной разряда позиционного кода столбца, имеющего одноименный со столбцом номер. Выходы элементов И, определякнцих одинаковые остатки, объединены Р.входовыми схемами исключающее ИЛИ, :выходы которых являются Р-разрядным йыходом матрицы. Из двух позиционных кодов, подаваемых на входы матрицы, кодом строк является код, обозначаемый буквой, стоящей первой по алфавиту. Например 4- 10 для кодов /Ь , р и кодами строки являются соответственно of, у&. Матрицы, на выходе которых присутствует позиционный код вида d, сС. , / } J Т называть матрицами типа ot , 5 , jb , , 0г| -jp, соответственно. Неисправность матрицы выражается в отсутствии сигнала 1 на проверяемой в данный момент выходной шине матрицы, что является неисправностью типа 1, или появлением лишнего сигнала 1 на одной из выходных шин, не соответствующей входным сигналам матрицы, что является неисправностью типа 2. Появление неисправности приводит к несовпадению позиционных кодов, поступающих на схему сравнения от матрицы и соответствующего дешифратора, в результате чего на выходе схемы сравнения появляется сигнал неисправности (атрицы. Работа устройства начинается по сигналу на шине 26, устанавливающему триггер 5 в единичное состояние и счетчики 7.1 и 7.2 в нулевое состояние. Пусть после очередного тактового импульса, поступившего по входу 27 элемента И 6, состояние счетчиков 7.1 и 7.2 и сумматора 8 установилось соответственно ot , jb, i и при этом в одной из матриц типа появилась неисправность. Сигнал неисправности со схемы сравнения, подключенной к данной матрице, через элемент ИЛИ 12.5 устанавливает в 1 триггер 13.5 памяти в результате чего на управляющем входе шифратора 15 присутствует шестиразрядный позиционный код, обозначенный . Этот же сигнал неисправности, поступая через блок 2 и регистр 3, передним фронтом через элемент И П.1 на втором входе которого присутствует сигнал разрешения с триггера 5, запускает формирователь 10, который формирует импульс, на время которого запрещается прохождение сигналов со счетчиков 7.1, 7.2 и сумматора 8 через элементы И 11.2-11.А на дешифраторы 9.1-9.3, в результате чего на выходных шинах дешифраторов сигналы отсутствуют. Точка фиг. 3 и обозначает разрешающее воздействие, а к(эестик - запрещаюцее. В случае неисправности типа 1 (фиг, 3) на выходеiрегистра 3 исчезает на время импульса формирователя 10 сигнал неисправности в результате совпадения кодов матрицы и дешифратора на соответствующей схеме 1 сравнения, так как на одной из выходных шин матрицы и дешифратора в это время нет сигнала. По заднему фронту .сигнала неисправности триггер 5 управления переключается в состояние О и запрещает дальнейшее прохождение тактовых импульсов на счетчик 7. по входу 27 через элемент И 6,

По окончании импульса формирователя 10 на выходах дешифраторов 9.19.3 появляются позиционные коды С/.1, cZv Г результате чего на первой и третьей группах выходных шин шифратора 15 присутствуют позиционные коды соответственно of-и ,

Код Ы,|, определяющий номер строки матрицы; в которой находится н исправный элемент, через первые входы элементов ИЛИ 20.1...20.Р поступает на регистр номера строки 22, где фиксируется.

Код ft, определяющий номер столбца матрицы с неисправным элементом, поступает на первые входы элементов И 18.1...18.Р, на вторые входы которых поступает разрешающий сигнал с выхода элемента ИЛИ 12.7, вход которого соединен с триггером 13.5 памяти,. установленным в 1, через элемент ИЛИ 12.5 сигналом неисправности со схемы сравнения. С выходов эле ментов И 18.1...18.Р позиционный код через группу элементов ИЛИ 21.1. 2.Р поступает на регистр номера столбца 23, где фиксируется. При, повторном появлении на входе регистра 3 сигнала неисправности пос ле окончания импульса формирователя 10, последний повторно не запустится поскольку триггер 5 управления находится в состоянии О и запрещает прохождение сигнала неисправности через элемент И 11.1. В случае неисправности типа 2 (фиг. ) - обрыв выводов, обрыв монтажных соединений, нарушение пайки, замыкание электрических цепей, нарушение соединений внутри микросхемы, перегорания или короткое замыкание переходов типа Р-п или п-Р, - во время шунтирования формирователем 10 входов элементов И 11.2-11.А сигнал неисправности на выходе регистра 3 не исчезает, так как при отсутствии

сигналов на выходных шинах дешифраторов, а значит и на входах всех матриц, коды на схеме 1 сравнения, соединенной с неисправной матрицей и соответствующим дешифратором 9.1 9.3, не совпадают, поскольку на одной из выходных шин матрицы постоянно присутствует лишний сигнал 1. Триггер 5 остается в исходном состоянии 1 и разрешает Дальнейшее прохождение тактовых импульсов на счетчик 7.1 через элемент 6 до тех пор, пока счетчики 7.1 и 7.2 примут состоние Ck /f и Р , соответствующее неисправным цепям или элементам матрицы. При этом сигнал неисправности на выходе регистра 3 исчезает, так как коды неисправной матрицы и дешифратора, поступающие на соответствующую схему 1 сравнения, совпадают, триггер 5 устанавливается в О и через элемент И 6 запрещает прохождение на счетчик 7.1 тактовых импульсов.

Номера строки и столбца матрицы, в которых находится неисправный элемент, фиксируются соответственно регистром 22 номера строки и регистром 23 номера столбца.

Пусть после очередного тактового импульса появилась неисправность в матрице типа об. Входными сигналами такой матрицы являются сигналы кодов .

Работа устройства при этом происходит аналогично описанной, но с тем отличием, что разрешающий сигнал в этом случае поступает на вторые входы элементов И 1б.1,..1б.Р и 17.1...17.Р от элемента НЕ 14, на входе которого сигнал отсутствует, поскольку триггеры 13.5 и 13.6 находятся в состоянии О Таким образом, адрес неисправного элемента матрицы однозначно определяется состоянием регистра 22 номера строки и регистра 23 номера столбца. Применение предлагаемого устройства для диагностики неисправностей многоярусных пирамидальных схем позволит точно устанавливать неисправный элемент матрицы, что, в свою очередь, значительно сократит время восстановления устройства. Формула изобретения Устройство для диагностики неисправностей многоярусных пирамидальных 139800 схем, содержащее п схем сравнения, блок приоритета, регистр результата, регистр номера неисправной матрицы, триггер упрарления, первый элемент И, первый и второй счетчики по модулю Р, сумматор по модулю Р, первый, второй и третий дешифраторы, причем первая группа входов п схем сравнения является группо входов устройства,. выход каждой схемы сравнения сое- to динен с соответствующим входом блока приоритета, первая и вторая группы выходов блока приоритета соединены соответственно с группой входов реги стра номера неисправной матрицы и группой входов регистра результата, выход которого соединен с нулевым входом триггера управления, установочный вход устройства соединен с входом обнуления сумматора по модулю Р, первого и второго счетчиков по модулю Рис единичным входом тригге ра управления, выход которого соединен с первым входом первого элемента И, тактовый вход устройства соединен со вторым входом первого элемента И, выход которого соединен со счетным входом первого счетчика по модулю Р, выход переполнения первого счетчика по модулю Р соединен со счетным входом второго счетчика по модулю Р и первым входом сумматора по модулю Р, второй вход которого соединен с вых дом переполнения второго счетчика по модулю Р, выходы первого, второго и третьего дешифраторов образуют группу выходов устройства и соединены со вторыми входами соответствующих схем сравнения, отличающееся тем, что, с целью увеличения разрешающей способности диагностики за счет определения неисправности с точ ностью до элемента матрицы, в устрой ство введены формировател4импульсов второй, третий, четвертый и пятый элементы И, первая, вторая, третья и четвертая группы элементов И, первая и вторая группы элементов ИЛИ, семь элементов ИЛИ, элемент НЕ, перВЫИ, второй, третий, четвертый, пяты и шестой триггеры, регистр номерастроки, регистр номера столбца, шифратор, причем выход регистра результата соединен с первым входом второго элемента И, выход которого через формирователь импульсов соединен с первыми входами третьего, четвертого и пятого элементов И, выходы которых соединены соответственно входами J J первого, второго и третьего дешифраторов, выход триггера управления сов динен со вторым входом второго элемента И, информационные выходы сумматора по модулю Р, первого и второго счетчиков по модулю Р соединены соответственно со вторыми входами пятого, третьего и четвертого элементов И, прямая и инверсная группы выходов аждого дешифратора соединены с соответствующей группой информационных входов шифратора , выходы схем сравнения, группы соединены с входами соответствующих элементов ИЛИ, выходы первого, второго, третьего, четвертого, пятого и шестого элементов ИЛИ соединены с единичными входами соответственно первого, второго, третьего, четвертого, пятого и шестого триггеров, выходы которых соединены с соответствующими.входами шифратора, выходы пятого и шестого триггеров соединены соответственно с первым и вторым входами седьмого элемента ИЛИ, выход которого через элемент НЕ соединен с первыми входами элементов И первой и второй групп, выход седьмого элемента ИЛИ соединен с первыми входами элементов И третьей и четвертой групп, первая и вторая группы выходов шифратора и выходы элементов И первой и второй групп соединены соответственно с первым, вторым, третьим и четвертым входами соответствующих элементов ИЛИ первой группы, выходы шифратора третьей и четвертой групп и выходы элементов И третьей и четвертой групп соединены соответственно с первым, вторым, третьим и четвертым входами соответствующих элементов ИЛИ второй группы, пятая группа выходов шифратора соединена со вторыми входами соответствующих элементов И первой и третьей групп, шестая группа выходов шифратора соединена со вторыми входами соответствующих элементов И второй и четвертой групп, выходы элементов ИЛИ первой и второй групп соединены с входами регистров номера строки и столбца COOT ветст венно. Источники информации, принятые во внимание при экспертизе 1,Авторское свидетельство СССР № , кл. G Об F 11/Oi, 1972. 2.Авторское свидетельство СССР ff 798849, кл. G Об F 11/02, 1978 (прототип).

24

25

li Н

. ОУ

1ч il

«2

V i I

S4

il

1

xRa

II

- II

«SI

«S

Авторы

Даты

1982-12-07—Публикация

1980-09-03—Подача